# Reliable On-Chip Voltage Regulation for Sustainable and Compact IoT and Heterogeneous Computing Systems

Longfei Wang University of South Florida Tampa, Florida longfei@mail.usf.edu Selçuk Köse University of South Florida Tampa, Florida kose@usf.edu

#### ABSTRACT

As an essential part of modern power delivery networks, on-chip voltage regulation consisting of multiple distributed voltage regulators provides the required power and voltage levels for localized load circuits. The harsh application environment of internet of things (IoT) and heterogeneous computing systems including, but not limited to, high temperature and large load current variations, can lead to significant and uneven performance degradations of on-chip voltage regulators due to aging. Investigating sustainable on-chip voltage regulation schemes considering the lifetime of different distributed voltage regulators becomes imperative. Furthermore, techniques to mitigate the aging induced voltage regulator degradations can consume the scarce on-chip area resource. In this work, a new reliable on-chip voltage regulation technique is explored to simultaneously mitigate the performance degradation and reduce the area cost of distributed on-chip voltage regulators to achieve sustainable and compact design and satisfy the needs of different IoT and heterogeneous computing systems considering the interactions among different regulators. A brief survey of reliable design challenges and potential solutions is also provided.

#### **KEYWORDS**

On-chip voltage regulation; reliability; internet of things; heterogeneous computing

#### ACM Reference Format:

Longfei Wang and Selçuk Köse. 2018. Reliable On-Chip Voltage Regulation for Sustainable and Compact IoT and Heterogeneous Computing Systems. In *GLSVLSI '18: 2018 Great Lakes Symposium on VLSI, May 23–25, 2018, Chicago, IL, USA*. ACM, New York, NY, USA, 6 pages. https://doi.org/10.1145/3194554. 3194602

#### **1** INTRODUCTION

The increasing number of internet connected devices enables more advanced applications such as smart homes and smart cities beyond conventional stand-alone smart devices [34]. Efficient social systems can be constructed with the support of vast deployment of internet of things (IoT) devices and the integration of heterogeneous computing systems [28]. Besides the popularity of IoT

GLSVLSI '18, May 23-25, 2018, Chicago, IL, USA

© 2018 Association for Computing Machinery.

ACM ISBN 978-1-4503-5724-1/18/05...\$15.00

https://doi.org/10.1145/3194554.3194602

devices, challenging design requirements such as power efficiency, cost, security, and reliability are also emerging. Similarly, there are open research problems such as workload partitioning, task mapping, and thermal and power management [5, 8, 26] for performance and energy efficiency improvement of heterogeneous computing systems.

On-chip voltage regulation, as an essential part of both IoT and heterogeneous computing systems, can greatly affect most of these design concerns. Considerable amount of research has been performed to improve the power efficiency of on-chip voltage regulators [9, 15, 29, 38] and further the energy efficiency of the underlying microprocessors [6]. Meanwhile, voltage regulators have been leveraged as a low overhead solution to enhance the security of the load circuits [16, 21, 37, 48–54]. On the other hand, reliability issue of on-chip voltage regulator has recently drawn attention [3, 32, 41–43]. However, as the application environment and load current demand of different IoT devices and different portion of heterogeneous computing systems can vary a lot, a homogeneous methodology by designing voltage regulators for the worst case scenario may lead to an over-design problem, which potentially increases the area and cost of devices.

While intensive technology scaling has enabled increasingly outstanding circuit performance, transistor aging induced circuit performance degradation has also become more dramatic [2]. A large circuit delay can be introduced and even circuit failure can occur [46]. Transistor aging induced circuit performance degradation is a strong function of temperature, electrical stress, and the amount of time the transistor is under stress. It is thus important to consider the variations of these parameters within IoT and heterogeneous computing systems to achieve the targeted design specifications. Furthermore, the reliability design constraints can be relaxed within a certain portion of a chip that has less degree of aging to reduce the total area cost or to spare additional area for heavily aged regions.

Techniques to mitigate aging induced voltage regulator performance degradations are investigated. As on-chip voltage regulation with distributed voltage regulators becomes prominent in recent design paradigms [18, 22, 36, 39, 40, 42], reliable on-chip voltage regulation within the context of distributed voltage regulators is also explored. Furthermore, reliable on-chip voltage regulation considering the varying application environment and lifetime requirement of IoT devices and heterogeneous computing systems is discussed.

The rest of the paper is organized as follows. Background information regarding on-chip voltage regulation, IoT devices, and heterogeneous computing systems is introduced in Section 2. Major transistor aging mechanisms and aging-aware on-chip voltage regulators are discussed in Section 3. Reliable on-chip voltage regulation

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by otherwise, and ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

for sustainable and compact designs is investigated in Section 4. Conclusion is offered in Section 5.

## 2 BACKGROUND

On-chip voltage regulation provides certain advantages as compared to off-chip implementations such as reduced voltage noise, fast dynamic voltage and frequency scaling (DVFS) capability, reduced number of power/ground pins, more compact design, and reduced power loss due to parasitic impedance, which serves as an ideal power supply solution for IoT and heterogeneous computing systems.

## 2.1 Internet of things

IoT covers a wide range of application domains such as smart home, smart city, wearable device, automotive industry, agriculture, and health care [33]. Different applications may impose different lifetime requirements. Furthermore, even with the same lifetime requirement, the aging speed of functional circuits within IoT devices can be quite different. For example, it would be acceptable to have a lifetime requirement of only five years for smart home devices such as Amazon Echo and Google Home, since functions of these devices may quickly run out of date as technology advances and replacement of them can be effortless. It would be, however, more desirable to set a lifetime target of more than ten years for implantable medical devices to reduce potentially costly and painful operations.

On the other hand, temperature sensors for IoT applications may experience quite challenging environmental changes. A digital temperature sensor with a wide industrial temperature range of -40°C ~ 150°C [12], may operate around room temperature or near the low/high temperature boundaries. Individual transistors age much faster in high temperature operations as discussed in Section 3. The desired circuit level performance such as accuracy of the temperature sensor may degrade faster as well within a high temperature environment. For two identical temperature sensors with quite different operating temperatures, performance degradations between them can also significantly vary after a five-year period. In order to have similar performance degradation and operate with acceptable accuracy, temperature sensors operating mostly in higher temperature may need to be designed with a higher level of reliability standard at design time. Similarly, for low temperature operations, reliability constraint can be relaxed to reduce cost or design complexity.

## 2.2 Heterogeneous computing systems

Increasing number of IoT devices generates huge amount of data that needs to be processed by microprocessors. These data can be transmitted to specialists or servers for analysis. However, the transmission bandwidth and latency can limit the applications [1]. Edge computing has become a promising way to directly equip IoT devices with sufficient computation capability to overcome data transmission induced bandwidth, latency, and energy consumption limitations [1]. The emerging edge computing necessitates heterogeneous computing systems at either chip-level or network-level [1]. As IoT devices can have different functions and data characteristics, design requirements for IoT microprocessors also vary a lot. Such varying demands can be fulfilled with chip-level solution with heterogeneous cores on a single chip or network-level approach with different cores for different devices [1]. Regardless of chip-level or network-level strategy, the existence of heterogeneity demands heterogeneous on-chip power delivery among different cores or different part of the chip.

# 2.3 On-chip voltage regulation

On-chip voltage regulation is widely adopted in processors [9, 14, 36], energy harvesting devices [7, 24, 27, 29], and wearable devices [30, 44, 45], enabling various IoT applications. Three commonly used voltage regulator topologies including buck or boost converter, switched-capacitor (SC) converter, and low dropout regulator (LDO) cover most IoT application scenarios due to their respect advantages. A buck converter can achieve high power conversion efficiency over a wide load current range and voltage conversion ratios [29, 30] while a boost converter is needed for certain energy harvesting applications [17, 47] due to low input voltage levels. SC converters gain popularity due to the easiness of integration and higher power density over inductive approach. LDOs can achieve sub-ns response time and are adopted in the most recent IBM POWER8 and POWER9 processors [14, 36].

Although a single voltage regulator is typically implemented for most applications, distributed on-chip voltage regulation [14, 18, 22, 36–40, 42], where multiple parallel voltage regulators are distributed across the chip, has recently drawn significant attention. Better voltage noise performance and fast localized load response can be achieved. By adaptively turning on/off some of the distributed voltage regulators, a high power conversion efficiency can be obtained over a wide dynamic load range [37, 38]. It also provides a degree of freedom to mitigate hot spots on a certain chip and simultaneously optimize power efficiency, on-chip temperature, and voltage noise profile [19, 20].

# 3 RELIABLE ON-CHIP VOLTAGE REGULATION

Despite the advantages of on-chip voltage regulation, less attention has been paid to the reliability issues and aging induced on-chip voltage regulator performance degradations especially within IoT and heterogeneous computing system applications. To realize reliable on-chip voltage regulation, it is essential to first understand major transistor aging mechanisms and mitigate their side effects on individual voltage regulators.

# 3.1 Transistor aging mechanisms

Major transistor aging mechanisms include bias temperature instability (BTI), hot carrier injection (HCI), time dependent dielectric breakdown (TDDB), and electromigration (EM) [46]. BTI, which includes positive BTI (PBTI) for NMOS transistors and negative BTI (NBTI) for PMOS transistors, is the dominant reliability concern among others [11, 25, 35]. NBTI (PBTI) is caused by negatively (positively) applied transistor gate to source voltage  $V_{gs}$  and it can introduce significant threshold voltage  $V_{th}$  degradations. BTI induced  $V_{th}$  degradation is related to the generated Si/SiO<sub>2</sub> interface traps when electrical stress is applied [4].  $|V_{th}|$  increases when electrical stress is applied and partially recovers when electrical stress

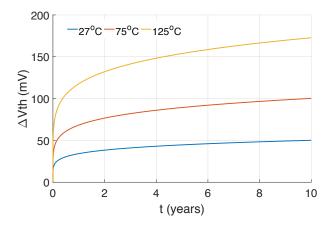

Figure 1: NBTI induced threshold voltage degradation with different temperature.

is removed. BTI induced  $|V_{th}|$  degradation with time t and activity factor  $\alpha$  can be expressed as [35]

$$\Delta V_{th} = \chi K_{lt} \sqrt{C_{ox}(|V_{gs}| - |V_{th}|)} e^{\frac{-E_a}{kT}} (\alpha t)^{\frac{1}{6}}$$

(1)

where  $\alpha$  is the percentage of time the transistor is under stress and k, T, and  $C_{ox}$  are Boltzmann constant, temperature, and the oxide capacitance, respectively.  $K_{lt}$  and  $E_a$  are fitting parameters to match the model with experimental data [35]. As  $\alpha$  is included in the model, the BTI recovery effect is already considered.

Utilizing the PMOS transistor parameters in 32 nm metal gate, high-*k* strained-Si CMOS technology from PTM model library [10], which is typically used in the literature for reliability study [2, 13, 25, 35], NBTI induced  $V_{th}$  degradation under different temperature is demonstrated in Fig. 1. As shown in Fig. 1, more than 150 mV  $V_{th}$ degradation can be introduced within a ten-year time frame with a temperature of 125°C. Even with a room temperature of 27°C, 50 mV  $V_{th}$  degradation can be introduced. NBTI induced  $\Delta V_{th}$  can be significant as compared to the initial value of 491.55 mV.

Transistor V<sub>th</sub> degradation can further lead to circuit level performance degradations. As demonstrated in [3], aging can induce degradation of current sensing accuracy of multiphase buck converter, mismatches between each phase, and degradation of power efficiency. Important performance metrics of a digital LDO (DLDO), including maximum current supply capability, load response time, and magnitude of the transient voltage droop, are shown to experience significant degradation as the power transistor array ages [41]. Experimental results in [43] also demonstrate side effects of aging on LDO DC performance and electromagnetic interference (EMI) immunity level. Local hotspots near voltage regulators can occur and further lead to transistor breakdown, top metal rupture, and even system level malfunction [32]. Furthermore, within an on-chip power delivery network consisting of many distributed individual voltage regulators, unbalanced current sharing among different voltage regulators can occur due to parasitic on-chip power grid resistance mismatches. This unbalanced current distribution causes different aging speed of metal wires connected to each voltage regulator due to electromigration (EM) induced wear-out [42]. The mean time to failure (MTTF) of metal wires which provide larger

current can be much less than those providing less current. This phenomenon may lead to the earlier failure of the whole on-chip power delivery network [42]. Thus, a reliability-aware design approach should be adopted and reliability enhancement techniques need to be investigated for on-chip voltage regulators.

#### 3.2 Aging-aware on-chip voltage regulators

A rotational phase shedding scheme for multiphase buck converters is proposed in [3] to mitigate the aging induced efficiency degradation especially under light load. For conventional multiphase buck converters, only one phase can be active under light load. For medium and heavy load conditions, additional phases are activated. The conventional phase activation scheme imposes too much electrical stress on a certain phase  $P_1$  among all the N phases ( $P_1$  to  $P_N$ ) as  $P_1$  is always activated at light load condition. The phase shedding scheme [3] rotationally turns on one of the N phases to make sure that electrical stress can be evenly distributed among all the phases at light load condition. The scheme may not work well under all the load current conditions as it is only activated at light load. A decoding methodology to decide which portion of the power transistor array to be turned on is proposed in [32] to mitigate or eliminate the hotspots generated by DLDOs. The power transistor array is divided into *n* rows and *m* columns. One power transistor in a certain row and middle column is turned on first and the one in the adjacent column and next row is activated as load current increases. A code rotation scheme is formed to spread the current distribution under all load conditions. The implementation cost of the proposed scheme is not clear and it may also introduce side effects on DLDO performance such as increased output voltage ripple. A lightweight aging mitigation scheme for DLDO is proposed in [41]. Instead of utilizing the conventional bidirectional shift register, a unidirectional shift register is proposed by simple modifications of the control circuit. The proposed NBTI-aware DLDO works well under arbitrary load conditions with little side effects on the performance of DLDO as the number of power transistors activated/deactivated per clock cycle remains the same. The power and area overhead incurred by the proposed technique are also negligible. Within the context of distributed on-chip voltage regulation, an effective current balancing scheme is proposed in [42] that can be applied to most regulator types which need a reference voltage to operate. Through balancing the current distribution among all the regulators, EM induced metal wear-out effects can be minimized.

## 4 RELIABLE VOLTAGE REGULATION FOR SUSTAINABLE AND COMPACT DESIGN

Besides aging mitigation techniques for individual on-chip voltage regulator needs to be considered to fully exploit the benefits of reliable on-chip voltage regulation. Seen from (1), temperature effects on  $\Delta V_{th}$  can be more significant than  $\alpha$  and  $|V_{gs}|$ . Thus, thermal management techniques can be essential for reliable on-chip voltage regulation. Thermally aware on-chip voltage regulation is investigated in [19] by turning on/off distributed voltage regulators in a thermally aware fashion. A nearly optimal chip-wide temperature profile can be achieved and up to  $20^{\circ}$ C maximum temperature

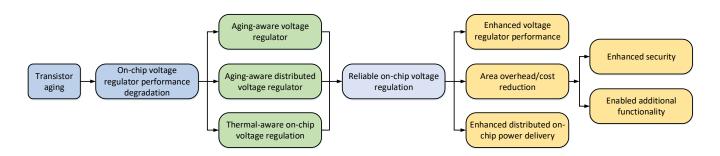

Figure 2: Road map to reliable on-chip voltage regulation for sustainable and compact design.

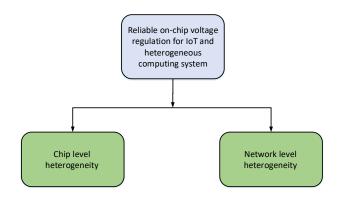

Figure 3: Reliable on-chip voltage regulation for IoT and heterogeneous computing systems.

reduction can be obtained as compared to a voltage noise optimal approach. The benefits of temperature reduction regarding reliability can be prominent as shown in Fig. 1. Furthermore, it is also important to consider different load current profile of each voltage regulator. It is demonstrated in [3, 31] that light and medium load current are consumed most of the time for mobile and microprocessor applications. However, voltage regulators need to be designed for the maximum load current supply capability, which may lead to varying aging speed of different voltage regulator portions [41] or individual voltage regulators. Balancing load current distribution among each power transistor, distributed voltage regulator, and different functional blocks through, respectively, reliability enhancement techniques [3, 32, 41], balanced current sharing schemes[36, 42], and reconfigurable voltage regulation [23, 31] can be beneficial. The road map to achieve reliable on-chip voltage regulation is summarized in Fig. 2.

Furthermore, different portions (functional block) of a chip can have quite different load current and temperature profiles. As investigated in [19, 41], the representative temperature profile among a load store unit, an execution unit, an instruction fetch unit, an instruction scheduling unit, and a cache can vary from 62°C to 90°C. The maximum load current varies from 1.356A to 12.092A. On the other hand, for IoT applications where various devices are connected to the Internet, temperature and load current profile vary at the network level. It is thus necessary to consider the heterogeneity characteristics at both the chip level and network level, as shown in Fig. 3 to implement reliable on-chip voltage regulation for IoT and heterogeneous computing systems. On-chip voltage regulator design simultaneously considering temperature, load current, and lifetime requirement, needs to be adopted for reliable on-chip voltage regulation.

Benefits of reliable on-chip voltage regulation can be manifold as summarized in Fig. 2. Reliability enhancement techniques for individual voltage regulators directly translate into improved voltage regulator performance such as reduced steady state output voltage ripple, faster load response, and lower voltage noise characteristics. Enhanced individual voltage regulator performance further strengthens distributed on-chip power delivery benefits and helps achieve faster and more accurate DVFS capability. Also, aging-aware on-chip voltage regulator can essentially reduce the area/power overhead needed for mitigation of aging induced voltage regulator performance degradation. For example, the NBTIaware DLDO proposed in [41] only induces ~ 2.6% area overhead and achieves up to 43.2% DLDO performance degradation mitigation. A conventional DLDO designed in an aging-unaware fashion may need extra decoupling capacitors to achieve the equivalent performance after aging. The area overhead of deploying an additional decoupling capacitor can be much larger than that induced by implementation of NBTI-aware DLDO. Reliable on-chip voltage regulation by adopting a heterogeneous on-chip power delivery network design at both the chip level and network level further reduces the area cost of on-chip voltage regulators. Not only sustainable and compact IoT and heterogeneous computing systems can be realized through reliable on-chip voltage regulation, but also significant area savings can be reaped. As area can be a stringent resource for IoT applications, area savings can be leveraged for enhanced security performance and even added functionality. Increased battery capacity, more number of voltage regulators, and reduced fabrication cost can also be enabled.

#### 5 CONCLUSION

Reliable on-chip voltage regulation is investigated to realize sustainable and compact IoT and heterogeneous computing systems. The characteristics of IoT devices necessitate the embedded application of heterogeneous computing features and on-chip voltage regulation provides an optimal power supply solution for such systems with enhanced security. Transistor aging induced threshold voltage increase can lead to on-chip voltage regulator performance degradations. Aging mitigation techniques for individual voltage regulators as well as thermal-aware on-chip voltage regulation are critical nodes on the road map to reliable on-chip voltage regulation. Heterogeneous voltage regulators tailored for the special needs of different functional blocks of a certain chip and even different portions of the IoT network enable significant area overhead savings, which further translate into enhanced security, improved power delivery performance, and additional functionality.

### ACKNOWLEDGMENTS

This work is supported in part by the National Science Foundation CAREER award under Grant CCF-1350451 and by a Cisco Research Award.

#### REFERENCES

- [1] Tosiron Adegbija, Anita Rogacs, Chandrakant Patel, and Ann Gordon-Ross. 2018. Microprocessor optimizations for the Internet of Things: a survey. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 37, 1 (Jan. 2018), 7–20. https://doi.org/10.1109/TCAD.2017.2717782

- [2] Innocent Agbo, Mottaqiallah Taouil, Daniel Kraak, Said Hamdioui, Halil Kukner, Pieter Weckx, Praveen Raghavan, and Francky Catthoor. 2017. Integral impact of BTI, PVT variation, and workload on SRAM sense amplifier. *IEEE Transactions Very Large Scale Integration (VLSI) Systems* 25, 4 (April 2017), 1444–1454. https: //doi.org/10.1109/TVLSI.2016.2643618

- [3] Youngkook Ahn, Inho Jeon, and Jeongjin Roh. 2014. A multiphase buck converter with a rotating phase-shedding scheme for efficient light-load control. *IEEE Journal of Solid-State Circuits* 49, 11 (Nov. 2014), 2673–2683. https://doi.org/10. 1109/JSSC.2014.2360400

- [4] M.A. Alam and S. Mahapatra. 2005. A comprehensive model of PMOS NBTI degradation. *Microelectronics Reliability* 45, 1 (2005), 71 – 81. https://doi.org/10. 1016/j.microrel.2004.03.019

- [5] Shoukat Ali, Tracy D. Braun, Howard Jay Siegel, and Anthony A. Maciejewski. 2001. Heterogeneous computing. *Encyclopedia of Distributed Computing* Kluwer Academic (2001).

- [6] Toke M. Andersen, Florian Krismer, Johann W. Kolar, Thomas Toifl, Christian Menolfi, Lukas Kull, Thomas Morf, Marcel Kossel, Matthias Brandli, and Pier Andrea Francese. 2017. A 10 W on-chip switched capacitor voltage regulator with feedforward regulation capability for granular microprocessor power delivery. *IEEE Transactions Power Electronics* 32, 1 (Jan. 2017), 378–393. https://doi.org/10.1109/TPEL.2016.2530745

- [7] Hansraj Bhamra, Jui-Wei Tsai, Yu-Wen Huang, Quan Yuan, Jay V. Shah, and Pedro Irazoqui. 2017. A sub-mm<sup>3</sup> wireless implantable intraocular pressure monitor microsystem. In *International Solid-State Circuits Conference*.

- [8] Ganapati Bhat, Yier Jin, Ali K. Unver, and Umit Y. Ogras. 2018. Algorithmic optimization of thermal and power management for heterogeneous mobile platforms. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* 26, 3 (March 2018), 544–557. https://doi.org/10.1109/TVLSI.2017.2770163

- [9] Edward A. Burton, Gerhard Schrom, Fabrice Paillet, Jonathan Douglas, William J. Lambert, Kaladhar Radhakrishnan, and Michael J. Hill. 2014. FIVR-fully integrated voltage regulators on 4th generation Intel core SoCs. In *Proceedings of the IEEE International Applied Power Electronics Conference and Exposition.*

- [10] Yu Cao. 2011. Predictive technology model for robust nanoelectronic design. Springer.

- [11] Tuck-Boon Chan, John Sartori, Puneet Gupta, and Rakesh Kumar. 2011. On the efficacy of NBTI mitigation techniques. In Proceedings of the Design, Automation and Test in Europe Conference & Exhibition.

- [12] European Editors. 2013. How to interface sensors to the internet of things. (Oct. 2013). Retrieved Feb, 2018 from https://www.digikey.com/en/\articles/techzone/2013/oct/how-to-interface-sensors-to-the-internet-of-things

- [13] Jianxin Fang and Sachin S. Sapatnekar. 2013. The impact of BTI variations on timing in digital logic circuits. *IEEE Transactions on Device and Materials Reliability* 13, 1 (Jan. 2013), 277–286. https://doi.org/10.1109/TDMR.2013.2237910

- [14] Christopher Gonzalez, Michael Floyd, Eric Fluhr, Phillip Restle, Daniel Dreps, Michael Sperling, Rahul Rao, David Hogenmiller, Christos Vezyrtis, Pierce Chuang, Daniel Lewis, Ricardo Escobar, Vinod Ramadurai, Ryan Kruse, Juergen Pille, Ryan Nett, Pawel Owczarczyk, Joshua Friedrich, Jose Paredes, Timothy Diemoz, Saiful Islam, Donald Plass, and Paul Muench. 2018. The 24-Core

POWER9 processor with adaptive clocking, 25-Gb/s accelerator links, and 16-Gb/s PCIe Gen4. *IEEE Journal of Solid-State Circuits* 53, 1 (Jan. 2018), 91–101. https://doi.org/10.1109/JSSC.2017.2748623

- [15] Yong-Min Ju, Se-Un Shin, Yeunhee Huh, Sang-Hui Park, Jun-Suk Bang, Ki-Duk Kim, Sung-Won Choi, Ji-Hun Lee, and Gyu-Hyeong Cho. 2017. A hybrid inductorbased flying-capacitor-assisted step-up/step-down DC-DC converter with 96.56% efficiency. In International Solid-State Circuits Conference.

- [16] Monodeep Kar, Arvind Singh, Sanu Mathew, Anand Rajan, Vivek De, and Saibal Mukhopadhyay. 2017. Improved power-side-channel-attack resistance of an AES-128 core via a security-aware integrated buck voltage regulator. In *International Solid-State Circuits Conference.*

- [17] Janko Katic, Saul Rodriguez, and Ana Rusu. 2018. A high-efficiency energy harvesting interface for implanted biofuel cell and thermal harvesters. *IEEE Transactions on Power Electronics* 33, 5 (May 2018), 4125–4134. https://doi.org/10. 1109/TPEL.2017.2712668

- [18] Ahmed Waheed Khan, Tanya Wanchoo, Gokhan Mumcu, and Selçuk Köse. 2017. Implications of distributed on-chip power delivery on EM side-channel attacks. In Proceedings of the IEEE International Conference on Computer Design.

- [19] S. Karen Khatamifard, Longfei Wang, Weize Yu, Selçuk Köse, and Ulya R. Karpuzcu. 2017. Thermogater: thermally-aware on-chip voltage regulation. In Proceedings of the IEEE International Symposium on Computer Architecture (ISCA).

- [20] Selçuk Köse. 2014. Thermal implications of on-chip voltage regulation: upcoming challenges and possible solutions. In Proceedings of the IEEE/ACM Design Automation Conference (DAC).

- [21] Selçuk Köse. 2017. Efficient and secure on-chip reconfigurable voltage regulation for IoT devices. In Proceedings of the ACM/IEEE Great Lakes Symposium on VLSI.

- [22] Selçuk Köse and Eby G. Friedman. 2012. Distributed on-chip power delivery. IEEE Journal on Emerging and Selected Topics in Circuits and Systems 2, 4 (Dec. 2012), 704–713. https://doi.org/10.1109/JETCAS.2012.2226378

- [23] Woojoo Lee, Yanzhi Wang, and Massoud Pedram. 2015. Optimizing a reconfigurable power distribution network in a multicore platform. *IEEE Transactions* on Computer-Aided Design of Integrated Circuits and Systems 34, 7 (July 2015), 1110-1123. https://doi.org/10.1109/TCAD.2015.2396998

- [24] Chao-Chieh Li, Min-Shueh Yuan, Chih-Hsien Chang, Yu-Tso Lin, Chia-Chun Liao, Kenny Hsieh, Mark Chen, and Robert Bogdan Staszewski. 2017. A 0.2V trifilar-coil DCO with DC-DC converter in 16nm FinFET CMOS with 188dB FOM, 1.3kHz resolution, and frequency pushing of 38MHz/V for energy harvesting applications. In International Solid-State Circuits Conference.

- [25] Mohamed Mounir Mahmoud, Norhayati Soin, and Hossam A. H. Fahmy. 2014. Design framework to overcome aging degradation of the 16 nm VLSI technology circuits. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 33, 5 (May 2014), 691–703. https://doi.org/10.1109/TCAD.2014.2299713

- [26] Sparsh Mittal and Jeffrey S. Vetter. 2015. A survey of CPU-GPI heterogeneous computing techniques. *Journal ACM Computing Surveys (CSUR)* 47, 4 (2015), 1–35. https://doi.org/10.1145/2788396

- [27] Phillip Nadeau, Mark Mimee, Sean Carim, Timothy K. Lu, and Anantha P. Chandrakasan. 2017. Nanowatt circuit interface to whole-cell bacterial sensors. In *International Solid-State Circuits Conference*.

- [28] Yuichi Nakamura, Hideyuki Shimonishi, Yuki Kobayashi, Kozo Satoda, Yashuhiro Matsunaga, and Dai Kanetomo. 2017. Novel heterogeneous computing platforms and 5G communications for IoT applications. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design.

- [29] Arun Paidimarri and Anantha P. Chandrakasan. 2017. A buck converter with 240pW quiescent power, 92% peak efficiency and a 2x10<sup>6</sup> dynamic range. In International Solid-State Circuits Conference.

- [30] Young-Jun Park, Ju-Hyun Park, Hong-Jin Kim, Hocheol Ryu, SangYun Kim, YoungGun Pu, Keum Cheol Hwang, Youngoo Yang, Minjae Lee, and Kang-Yoon Lee. 2017. A design of a 92.4% efficiency triple mode control DC-DC buck converter with low power retention mode and adaptive zero current detector for IoT/wearable applications. *IEEE Transactions on Power Electronics* 32, 9 (Sept. 2017), 6946–6960. https://doi.org/10.1109/TPEL.2016.2623812

- [31] Divya Pathak, Houman Homayoun, and Ioannis Savidis. 2017. Smart grid on chip: work load-balanced on-chip power delivery. *IEEE Transactions Very Large Scale Integration (VLSI) Systems* 25, 9 (Sept. 2017), 2538–2551. https://doi.org/10. 1109/TVLSI.2017.2699644

- [32] Pradipta Patra, Ramnarayanan Muthukaruppan, and Sumedha Mangal. 2015. A reliable digitally synthesizable linear drop-out regulator design for 14nm SOC. In Proc. IEEE Symposium on Nanoelectronic and Information Systems (iNIS).

- [33] Rahul. 2016. IoT applications spanning across industries. (Jan. 2016). Retrieved Feb, 2018 from https://www.ibm.com/blogs/internet-of-things/ iot-applications-industries/

- [34] Sandip Ray, Yier Jin, and Arijit Raychowdhury. 2016. The changing computing paradigm with internet of things: A tutorial introduction. *IEEE Design and Test of Computers* 33, 2 (Feb. 2016), 76–96. https://doi.org/10.1109/MDAT.2016.2526612

- [35] Daniele Rossi, Vasileios Tenentes, Sheng Yang, Saqib Khursheed, and Bashir M. Al-Hashimi. 2016. Reliable power gating with NBTI aging benefits. *IEEE Transactions Very Large Scale Integration (VLSI) Systems* 24, 8 (Aug. 2016), 2735–2744. https://doi.org/10.1109/TVLSI.2016.2519385

- [36] Zeynep Toprak-Deniz, Michael Sperling, John Bulzacchelli, Gregory Still, Ryan Kruse, Seongwon Kim, David Boerstler, Tilman Gloekler, Raphael Robertazzi, Kevin Stawiasz, Timothy Diemoz, George English, David Hui, Paul Muench, and Joshua Friedrich. 2014. Distributed system of digitally controlled microregulators enabling per-core DVFS for the POWER8<sup>TM</sup> microprocessor. In International Solid-State Circuits Conference.

- [37] Orhun Aras Uzun and Selçuk Köse. 2014. Converter-gating: a power efficient and secure on-chip power delivery system. *IEEE Journal on Emerging and Selected Topics in Circuits and Systems* 4, 2 (June 2014), 169–179. https://doi.org/10.1109/ JETCAS.2014.2315880

- [38] Orhun Aras Uzun and Selçuk Köse. 2014. Regulator-gating methodology with distributed switched capacitor voltage converters. In *IEEE Computer Society Annual Symposium on VLSI*.

- [39] Inna P. Vaisband and Eby G. Friedman. 2016. Stability of distributed power delivery systems with multiple parallel on-chip LDO regulators. *IEEE Transactions* on Power Electronics 31, 8 (Aug. 2016), 5625–5634. https://doi.org/10.1109/TPEL. 2015.2493512

- [40] Inna P. Vaisband, Renatas Jakushokas, Mikhail Popovich, Andrey V. Mezhiba, Selçuk Köse, and Eby G. Friedman. 2016. On-chip power delivery and management, Fourth Edition. Springer.

- [41] Longfei Wang, S. Karen Khatamifard, Ulya R. Karpuzcu, and Selçuk Köse. 2018. Mitigation of NBTI induced performance degradation in on-chip digital LDOs. In Proceedings of the Design, Automation and Test in Europe Conference & Exhibition.

- [42] Longfei Wang, S. Karen Khatamifard, Orhun Aras Uzun, Ulya R. Karpuzcu, and Selçuk Köse. 2017. Efficiency, stability, and reliability implications of unbalanced current sharing among distributed on-chip voltage regulators. *IEEE Transactions Very Large Scale Integration (VLSI) Systems* 25, 11 (Nov. 2017), 3019–3022. https: //doi.org/10.1109/TVLSI.2017.2742944

- [43] Jianfei Wu, Alexandre Boyer, Jiancheng Li, Sonia Ben Dhia, and Rongjun Shen. 2013. Characterization of changes in LDO susceptibility after electrical stress. *IEEE Transactions on Electromagnetic Compatibility* 55, 5 (Oct. 2013), 883–890. https://doi.org/10.1109/TEMC.2013.2242471

- [44] Taiyang Wu, Fan Wu, Jean-Michel Redoute, and Mehmet Rasit Yuce. 2017. An autonomous wireless body area network implementation towards IoT connected healthcare applications. *IEEE Access* 5 (June 2017), 11413–11422.

- [45] Long Yan, Jerald Yoo, Binhee Kim, and Hoi-Jun Yoo. 2010. A 0.5-uV $_{rms}$  12-uW wirelessly powered patch-type healthcare sensor for wearable body sensor

network. IEEE Journal of Solid-State Circuits 45, 11 (Nov. 2010), 2356–2365. https://doi.org/10.1109/JSSC.2010.2065831

- [46] Hyunbean Yi, Tomokazu Yoneda, Michiko Inoue, Yasuo Sato, Seiji Kajihara, and Hideo Fujiwara. 2011. A failure prediction strategy for transistor aging. *IEEE Transactions Very Large Scale Integration (VLSI) Systems* 20, 11 (Nov. 2011), 1951–1959. https://doi.org/10.1109/TVLSI.2011.2165304

- [47] Kye-Seok Yoon, Sung-Wan Hong, Jun-Suk Bang, Sang-Han Lee, Sung-Won Choi, and Gyu-Hyeong Cho. 2017. A 1452-% power extraction improvement energy harvesting circuit with simultaneous energy extraction from a piezoelectric transducer and a thermoelectric generator. In 2017 Symposium on VLSI Circuits.

- [48] W. Yu and S. Kose. [n. d.]. Exploiting Voltage Regulators to Enhance Various Power Attack Countermeasures. *IEEE Transactions on Emerging Topics in Computing* ([n. d.]), 1. https://doi.org/10.1109/TETC.2016.2620382

- [49] Weize Yu and Selçuk Köse. 2015. Time-delayed converter-reshuffling: an efficient and secure power delivery architecture. *IEEE Embedded Systems Letters* 7, 3 (Sept. 2015), 73–76. https://doi.org/10.1109/LES.2015.2433175

- [50] Weize Yu and Selçuk Köse. 2016. Charge-withheld converter-reshuffling (CoRe): a countermeasure against power analysis attacks. *IEEE Transactions on Circuits* and Systems II: Express Briefs 63, 5 (May 2016), 438–442. https://doi.org/10.1109/ TCSII.2015.2505261

- [51] Weize Yu and Selçuk Köse. 2016. A voltage regulator-assisted lightweight AES implementation against DPA attacks. *IEEE Transactions on Circuits and Systems I: Regular Papers* 63, 8 (Aug. 2016), 1152–1163. https://doi.org/10.1109/TCSI.2016. 2555810

- [52] Weize Yu and Selçuk Köse. 2017. False key-controlled aggressive voltage scaling: a countermeasure against LPA attacks. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 36, 12 (Dec. 2017), 2149–2153. https: //doi.org/10.1109/TCAD.2017.2682113

- [53] Weize Yu and Selçuk Köse. 2017. Security-adaptive voltage conversion as a lightweight countermeasure against LPA attacks. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* 25, 7 (July 2017), 2183–2187. https://doi.org/10. 1109/TVLSI.2017.2670537

- [54] Weize Yu, Orhun Aras Uzun, and Selçuk Köse. 2015. Leveraging on-chip voltage regulators as a countermeasure against side-channel attacks. In Proceedings of the IEEE/ACM Design Automation Conference.