### Grids in Very Large Scale Integration Systems

by

Albert Çiprut

Submitted in Partial Fulfillment

of the

Requirements for the Degree Doctor of Philosophy

Supervised by Professor Eby G. Friedman

Department of Electrical and Computer Engineering

Arts, Sciences and Engineering

Edmund A. Hajim School of Engineering and Applied Sciences

University of Rochester Rochester, New York 2019

# Dedication

This work is dedicated to my mother, Jacqueline Gabay Çiprut, and in memory of my father, Erol Çiprut.

# Table of Contents

| Bi         | iogra:          | phical Sketch ix               |   |  |

|------------|-----------------|--------------------------------|---|--|

| A          | Acknowledgments |                                |   |  |

| <b>A</b> l | Abstract        |                                |   |  |

| Co         | ontri           | outors and Funding Sources xvi | ί |  |

| Li         | List of Tables  |                                |   |  |

| Li         | st of           | Figures xviii                  | ί |  |

| 1          | Intr            | oduction 1                     |   |  |

|            | 1.1             | My Thesis                      | - |  |

|            | 1.2             | Motivation                     | , |  |

|            | 1.3             | The Grid                       | F |  |

|            | 1.4             | Outline                        | , |  |

| 2 | Grie | ds in Integrated Systems                                     | 12 |

|---|------|--------------------------------------------------------------|----|

|   | 2.1  | Density                                                      | 14 |

|   | 2.2  | Regularity                                                   | 18 |

|   | 2.3  | Path Diversity                                               | 22 |

|   | 2.4  | Computational Efficiency                                     | 26 |

|   | 2.5  | Summary                                                      | 28 |

| 3 | Nor  | n-Volatile Resistive Crossbar Arrays                         | 30 |

|   | 3.1  | Non-Volatile Resistive Devices                               | 32 |

|   |      | 3.1.1 Device Parameters                                      | 37 |

|   |      | 3.1.2 Applications                                           | 39 |

|   | 3.2  | Non-Volatile Resistive Memory System                         | 41 |

|   | 3.3  | Challenges                                                   | 44 |

|   |      | 3.3.1 Write Operations                                       | 44 |

|   |      | 3.3.2 Read Operations                                        | 46 |

|   |      | 3.3.3 Selectors                                              | 48 |

|   | 3.4  | Summary                                                      | 51 |

| 4 | On-  | Chip Power Delivery with Fully Integrated Voltage Regulators | 52 |

|   | 4.1  | Low Dropout Voltage Regulator                                | 59 |

|   | 12   | Fully Integrated On Chin I DO Regulators                     | 61 |

|   | 4.3  | Stabili | ty Analysis                                            | 63  |

|---|------|---------|--------------------------------------------------------|-----|

|   |      | 4.3.1   | Effect of Output Capacitance on LDO Stability          | 66  |

|   |      | 4.3.2   | Improving LDO Performance                              | 69  |

|   | 4.4  | Summa   | ary                                                    | 70  |

| 5 | Mod  | deling  | Size Limitations of Resistive Crossbar Array With Cell |     |

|   | Sele | ectors  |                                                        | 73  |

|   | 5.1  | Models  | s of Crossbar Array Design Parameters                  | 75  |

|   |      | 5.1.1   | Driver size                                            | 76  |

|   |      | 5.1.2   | Voltage degradation across selected cell               | 79  |

|   |      | 5.1.3   | Read margin                                            | 84  |

|   | 5.2  | Enhan   | cement of Nonlinearity Factor                          | 87  |

|   |      | 5.2.1   | Driver size                                            | 89  |

|   |      | 5.2.2   | Voltage degradation across selected cell               | 90  |

|   |      | 5.2.3   | Read margin                                            | 92  |

|   | 5.3  | Design  | Requirements for Varying Array Size                    | 93  |

|   |      | 5.3.1   | Driver Resistance                                      | 94  |

|   |      | 5.3.2   | Voltage Degradation and Device Nonlinearity            | 95  |

|   |      | 5.3.3   | Read operation                                         | 96  |

|   | 5.4  | Design  | Of A Crossbar Array Based On These Models              | 98  |

|   | 5.5  | Summ    | ary.                                                   | 100 |

| 6 | Ene  | Energy Efficient Write Scheme for Non-Volatile Resistive Crossbar |                                                    |     |  |

|---|------|-------------------------------------------------------------------|----------------------------------------------------|-----|--|

|   | Arr  | ays wi                                                            | th Selectors                                       | 102 |  |

|   | 6.1  | Write                                                             | Operations                                         | 106 |  |

|   | 6.2  | Energ                                                             | y Models                                           | 108 |  |

|   |      | 6.2.1                                                             | Energy Efficient Bias Scheme                       | 113 |  |

|   |      | 6.2.2                                                             | Impact of Nonlinearity Factor                      | 116 |  |

|   |      | 6.2.3                                                             | Write Pulse Width                                  | 117 |  |

|   | 6.3  | Energ                                                             | y Efficienct Hybrid Write Scheme                   | 119 |  |

|   |      | 6.3.1                                                             | Optimal Choice of Bias Scheme                      | 121 |  |

|   |      | 6.3.2                                                             | Overhead and Challenges                            | 126 |  |

|   | 6.4  | Summ                                                              | nary                                               | 128 |  |

| 7 | Stal | bility (                                                          | of On-Chip Power Delivery Systems with Multiple Lo | w   |  |

|   | Dro  | pout 1                                                            | Regulators                                         | 131 |  |

|   | 7.1  | Stabil                                                            | ity of Parallel Connected LDOs                     | 133 |  |

|   | 7.2  | Existi                                                            | ng Work                                            | 136 |  |

|   | 7.3  | Evalua                                                            | ating the Stability of Multiple LDOs               | 138 |  |

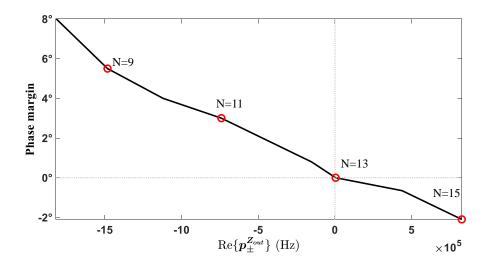

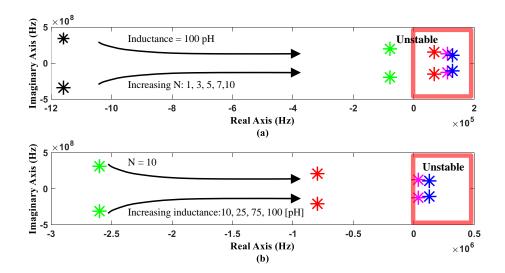

|   |      | 7.3.1                                                             | Effect of Number of LDOs on Grid Stability         | 140 |  |

|   |      | 7.3.2                                                             | Source of Instability                              | 142 |  |

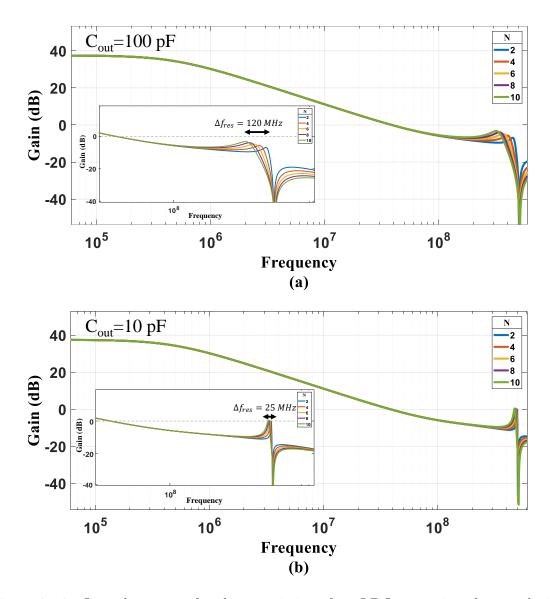

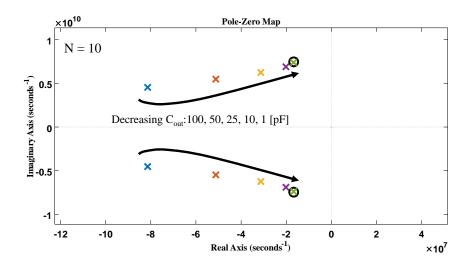

|   |      | 7.3.3                                                             | Degradation of Resonant Frequency                  | 146 |  |

|   |      | 7 3 4                                                             | Condition for Stability                            | 151 |  |

|    | 7.4  | Effect  | of Design Parameters on Grid Stability                   | 154 |

|----|------|---------|----------------------------------------------------------|-----|

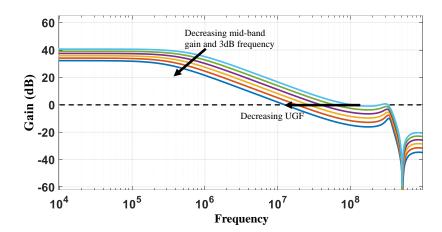

|    |      | 7.4.1   | LDO Design Parameters                                    | 155 |

|    |      | 7.4.2   | Power Grid Parameters                                    | 161 |

|    | 7.5  | Summ    | ary                                                      | 165 |

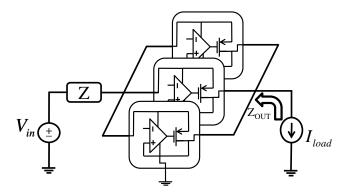

| 8  | Dist | ribute  | ed Pass Gates in Power Delivery Systems with Digital Lov | N   |

|    | Dro  | pout I  | Regulators                                               | 167 |

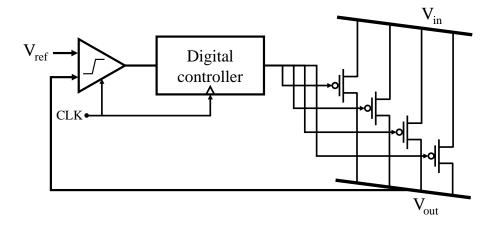

|    | 8.1  | Distrib | buted Pass Gates                                         | 169 |

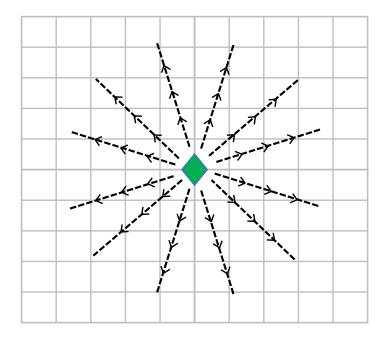

|    |      | 8.1.1   | Grid Centroid                                            | 170 |

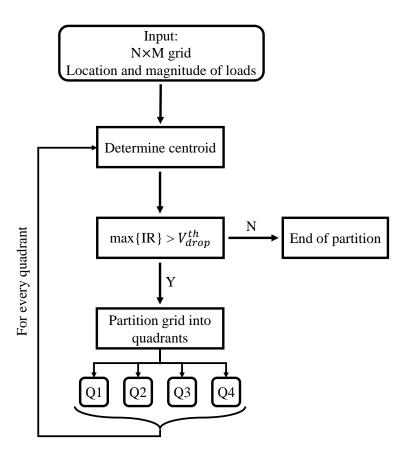

|    |      | 8.1.2   | Proposed Heuristic                                       | 172 |

|    | 8.2  | Power   | Grid Analysis                                            | 176 |

|    |      | 8.2.1   | Distribution Topologies                                  | 176 |

|    |      | 8.2.2   | Comparison of Pass Gate Distribution Topologies          | 178 |

|    | 8.3  | Summ    | ary                                                      | 184 |

| 9  | Con  | clusio  | ns                                                       | 186 |

| 10 | Futı | ıre Wo  | ork                                                      | 190 |

|    | 10.1 | RowH    | ammer Effect                                             | 191 |

|    | 10.2 | RowH    | ammer Effect in Nonvolatile Resistive Arrays             | 192 |

|    | 10.3 | Propos  | sed Research Direction                                   | 194 |

|    | 10.4 | Summ    | arv                                                      | 196 |

|   | ٠ | • | • |

|---|---|---|---|

| V | 1 | 1 | 1 |

| Bibliography                                          | 198 |

|-------------------------------------------------------|-----|

| Appendix A Derivation of Switching Energy Consumption | 216 |

| Appendix B Off-chip Power Delivery Network            | 218 |

## Biographical Sketch

Albert (Avi) Çiprut received the Bachelor of Science degree in Electronics Engineering from Sabanci University, Istanbul, Turkey in 2013, and the Master of Science degree in Electrical Engineering from the University of Rochester, Rochester, New York in 2016. He was an intern with the Power Team, Google Inc., Mountain View, California in 2016. His current research interests include memory systems based on emerging memory technologies, on-chip power delivery systems, and electronic design automation. The following publications are a result of the work conducted during his doctoral study.

#### Journal papers

A. Ciprut and E. G. Friedman, "Energy Efficient Write Scheme for Non-Volatile Resistive Crossbar Arrays with Selectors," *IEEE Transactions on Very Large* Scale Integration Systems, Vol. 26, No. 4, pp. 711–719, April 2018.

- A. Ciprut and E. G. Friedman, "Modeling Size Limitations of Resistive Crossbar Array with Cell Selectors," *IEEE Transactions on Very Large Scale Integration* Systems, Vol. 25, No. 1, pp. 286–293, January 2017.

- A. Ciprut and E. G. Friedman, "Stable On-Chip Power Delivery Systems with Multiple Low Dropout Regulators," *IEEE Transactions on Very Large Scale Integration Systems* (in press).

- A. Ciprut and E. G. Friedman, "Distributed Pass Gates in Power Delivery Systems with Digital Low Dropout Regulators," *IEEE Transactions on Very Large Scale Integration Systems* (in submission).

#### Conference papers

- A. Ciprut and E. G. Friedman, "Hybrid Write Bias Scheme for Non-Volatile Resistive Crossbar Arrays," Proceedings of the IEEE International Symposium on Circuits and Systems, pp. 1–5, May 2018.

- A. Ciprut and E. G. Friedman, "On the Write Energy of Non-Volatile Resistive Crossbar Arrays with Selectors," Proceedings of the IEEE International Symposium on Quality Electronic Design, pp. 184–188, March 2018.

- A. Ciprut and E. G. Friedman, "On the Stability of Distributed On-Chip Low Dropout Regulators," Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, pp. 217–220, August 2017.

• A. Ciprut and E. G. Friedman, "Design Models of Resistive Crossbar Arrays with Selector Devices," *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 1250–1253, May 2016.

#### Patent

• A. Ciprut and E. G. Friedman, "Energy Efficient Write Scheme for Non-Volatile Resistive Crossbar Arrays with Selectors," 2017 (disclosed).

## Acknowledgments

In this section, I would like to thank and express my gratitude towards a number of people who have made my Ph.D. experience worthwhile and supported my efforts in realizing the works embodied in this dissertation. First, I thank my advisor and mentor Professor Eby G. Friedman for giving me the chance and the opportunity to pursue this intellectual journey under his supervision. His teachings significantly influenced my thought process, having a major positive effect both on this dissertation and me as a person. As time goes by, I realize how lucky I am to have worked with him.

I thank Professor Engin Ipek, Professor Zeljko Ignjatovic, and Professor Marc D. Porosoff for serving on my proposal and defense committees. Their valuable feedback has improved this dissertation. I would also like to express my gratitude to Professor Yonathan Shapir for serving as the chairperson in my defense committee.

I thank Gregory Sizikov for providing the opportunity to work with him at Google.

This internship experience taught me the value and importance of working with people like Gregory who can retain a continuous positive attitude that motivates and empowers.

I would like to thank my colleagues (in no particular order): Tahereh, Abdu, Gleb, Kanisha, Rassulisha, Boris, Alex, Inna, Ravi, and Mohammad. These people were like a second family to me here in Rochester. In addition, I would like to thank Ruth Ann Williams, for the amazing blueberry cakes as well as the interesting conversations and viewpoints that she has shared with us.

I thank many friends for the great moments I get to keep forever. After all, it's all about the moments. Your friendship has carried this Ph.D./Rochester experience to a whole new level of amazingness and I thank you all for that.

I thank my family, especially my mother and my little brother, for their continuous support throughout my lifetime. Your love was a critical source of fuel that kept me going through this challenging experience. I can't imagine how it would have been without your presence.

Lastly, I want to express my deep gratitude to this country, the United States of America, for opening its doors and providing the opportunity to better myself in ways which would hardly be possible otherwise.

### Abstract

With transistor scaling, the process in which high performance, very large scale integrated (VLSI) systems are engineered has changed due to significant interconnect resistance, noise, and coupling effects. One common design solution that has not changed however has been the grid, a structural topology that enhances different characteristics of a VLSI system, such as area, reliability, and design complexity. In this dissertation, the fundamental role of a grid structure in VLSI systems is explored and a set of design challenges in grid-based circuits are addressed; specifically, the design challenges of nonvolatile resistive memory arrays and on-chip power grids with integrated linear voltage regulators.

The dissertation starts by introducing the characteristics of a grid structure and the influence of grids on different aspects of integrated systems, such as power delivery networks, memory systems, digital logic, and automated routing. The following chapters address a set of challenges in grid-based systems, continuing with the computational complexity of designing nonvolatile resistive memories as well as the write energy of these memory arrays. A set of closed-form expressions that intuitively model the size limitation of nonvolatile resistive memories with cell selectors are described to relax the computational requirements. Furthermore, the write energy of resistive memory arrays is explored, and models estimating the write energy are presented. Based on the insights gained from these models, an energy efficient bias scheme is proposed to reduce the write energy.

Moreover, the stability of on-chip power grids in the presence of multiple linear voltage regulators is evaluated. The decreasing stability of a power grid when increasing the number of regulators is described. The integration challenges of digital linear regulators with resistive power grids is also discussed. A methodology to distribute the pass transistors of a digital linear regulator is proposed to mitigate voltage variations across a grid.

The benefits of a grid topology in complex integrated systems often comes at a cost of various design challenges. This dissertation provides insight into the complex relationship between grids and VLSI systems.

### Contributors and Funding Sources

This work was supervised by a dissertation committee consisting of Professor Eby G. Friedman (advisor), Professor Zeljko Ignjatovic, and Professor Engin Ipek of the Department of Electrical and Computer Engineering, and Professor Marc D. Porosoff of the Department of Chemical Engineering. All of the work described in the dissertation was completed by the student with support from Professor Eby G. Friedman.

This work was supported by the U.S.-Israel Binational Science Foundation under Grant No. 2012139, the National Science Foundation under Grant Nos. CCF-1329374, CCF-1526466, CNS-1548078, and CCF-1716091, the Intel Collaborative Research Institute for Computational Intelligence (ICRI-CI), IARPA under Grant No. W911NF-14-C-0089, AIM Photonics under Award No. 059447-007, the Singapore Ministry of Education Tier 2 under Grant No. MOE2014-T2-2-105, and by grants from Cisco Systems, Qualcomm, and OeC.

## List of Tables

| 3.1 | Summary of typical device parameters [72,75]               | 38  |

|-----|------------------------------------------------------------|-----|

| 5.1 | Parameters for read operation                              | 83  |

| 5.2 | Design parameters                                          | 99  |

| 5.3 | Varying array sizes to satisfy $V_{cell}/V_{write} = 0.75$ | 99  |

| 6.1 | Summary of parameters for write operation                  | 111 |

| 8.1 | Mean of distributions                                      | 183 |

| 8.2 | Variance of distributions                                  | 183 |

| B 1 | Off-chip parasitic impedances                              | 218 |

# List of Figures

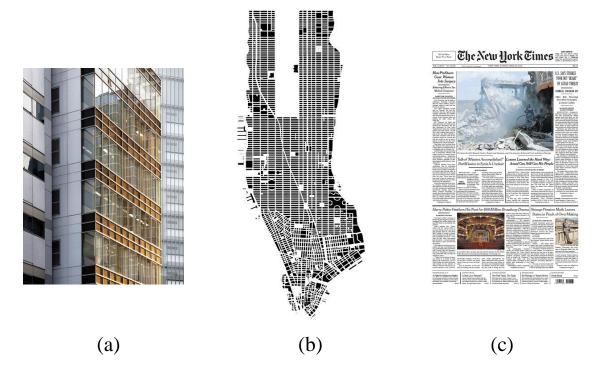

| 1.1 | Grid systems are used in a variety of design and engineering problems,      |    |

|-----|-----------------------------------------------------------------------------|----|

|     | (a) architecture, (b) Manhattan gridiron plan, and (c) graphic design       |    |

|     | of the New York Times.                                                      | 4  |

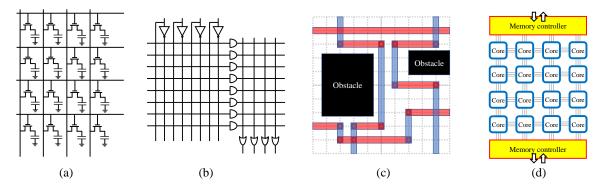

| 1.2 | Repeated cell structures forming a grid in die photographs, (a) Intel       |    |

|     | 4004, and (b) IBM Power9 processor                                          | 5  |

| 1.3 | Grid based IC design, (a) DRAM memory array, (b) programmable               |    |

|     | logic array (PLA), (c) interconnect routing, and (d) mesh-based net-        |    |

|     | work for communication within multicore microprocessors                     | 6  |

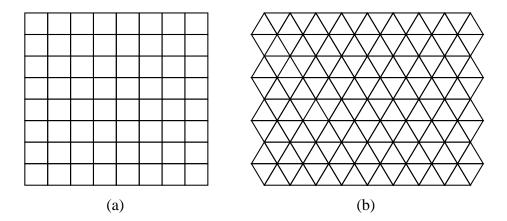

| 2.1 | Grid structures, (a) square grid, and (b) triangular grid                   | 13 |

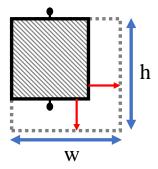

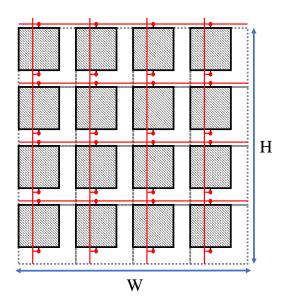

| 2.2 | Top view of a unit memory cell with a cell height of $h$ and width of $w$ . | 15 |

| 2.3 | Placement of memory cells within a grid structure for higher density.       | 16 |

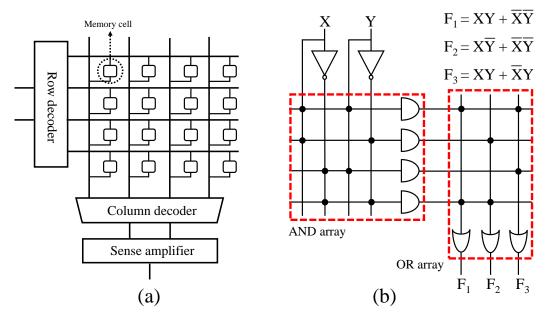

| 2.4 | Examples of grid structure in integrated circuits for high density, (a)     |    |

|     | memory array, and (b) programmable logic array (PLA)                        | 17 |

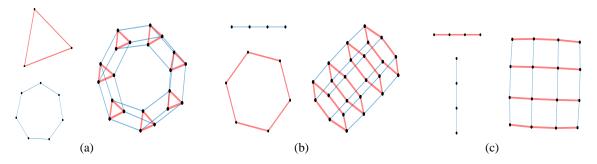

| 2.5  | Graph Cartesian product of two generators produces a regular graph,     |    |

|------|-------------------------------------------------------------------------|----|

|      | (a) triangle graph and heptagon, (b) path graph and hexagon, and (c)    |    |

|      | two path graphs producing a grid graph                                  | 19 |

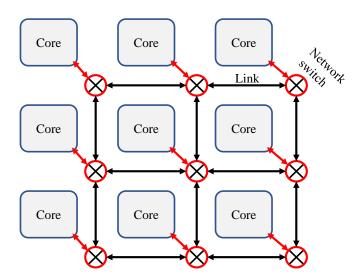

| 2.6  | Regularity of a network-on-chip (NoC) based on a mesh topology          | 20 |

| 2.7  | Redundancy insertion in PLAs to enhance yield. The regular structure    |    |

|      | of a PLA supports fault tolerant circuits                               | 21 |

| 2.8  | Alternate paths between two points within a mesh improve robustness     |    |

|      | and reduce the effective parasitic impedance between the source and     |    |

|      | sink                                                                    | 23 |

| 2.9  | Power delivery networks, (a) tree structured, and (b) mesh-based topol- |    |

|      | ogy                                                                     | 24 |

| 2.10 | Effective resistance across a grid (between marked points) with respect |    |

|      | to grid density, assuming an equal number of rows and columns           | 25 |

| 2.11 | Routing multiple pins, (a) regular grid with uniform lengths, and (b)   |    |

|      | Hanan grid                                                              | 27 |

| 3.1  | Crossbar array structure                                                | 30 |

| 3.2  | A 2 x 2 resistive crossbar array                                        | 31 |

| 3.3  | Switching mechanism of RRAM, (a) set operation, and (b) reset oper-     |    |

|      | ation [68]                                                              | 33 |

| n 4  |                                                                         |    |

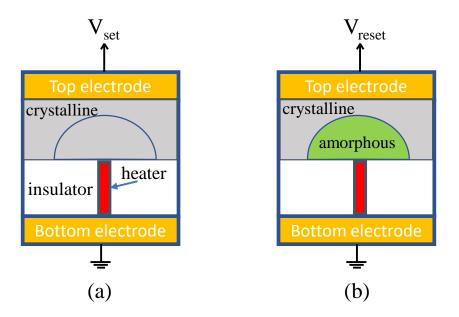

| 3.4  | Switching mechanism of PCM, (a) set operation, and (b) reset operation. | 34 |

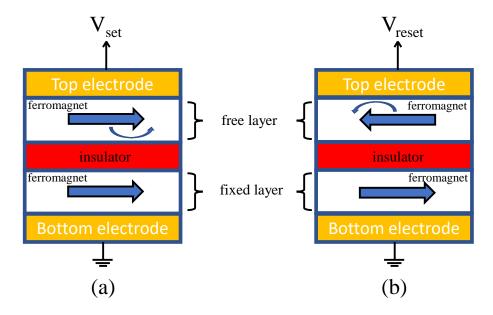

| 3.5  | The switching mechanism of MRAM, (a) set operation, and (b) reset             |    |

|------|-------------------------------------------------------------------------------|----|

|      | operation                                                                     | 35 |

| 3.6  | Two types of MRAM switching mechanisms, (a) field assisted switching          |    |

|      | and (b) spin-transfer-torque (STT)                                            | 36 |

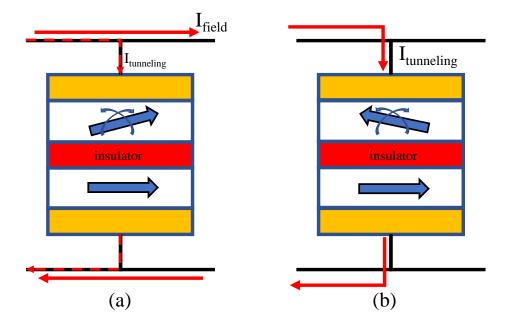

| 3.7  | Smallest memory cell matched to the metal pitch with an area of $4F^2$ .      | 38 |

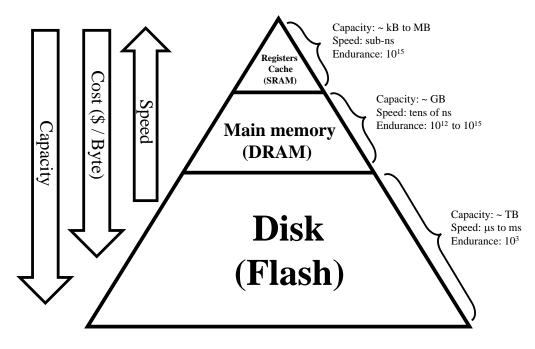

| 3.8  | Memory hierarchy of a computer system [43]                                    | 39 |

| 3.9  | An MRAM based main memory from Everspin Technologies [76]                     | 40 |

| 3.10 | PCM and RRAM based SSDs, (a) Intel–Micron [77], and (b) Toshiba               |    |

|      | [78]                                                                          | 41 |

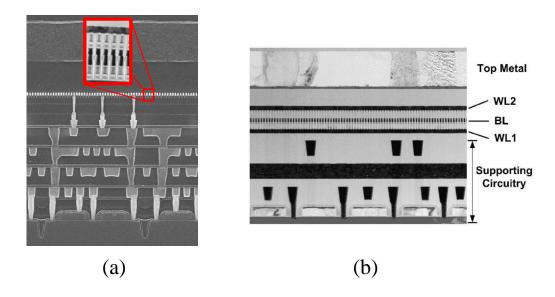

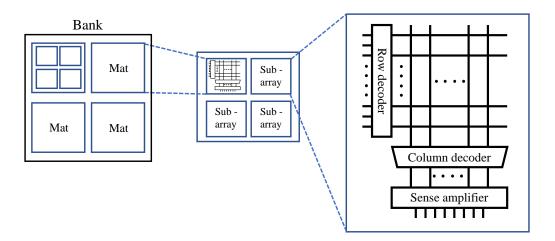

| 3.11 | Typical memory system with the peripheral circuitry forming a bank            |    |

|      | of multiple crossbar arrays [79]                                              | 42 |

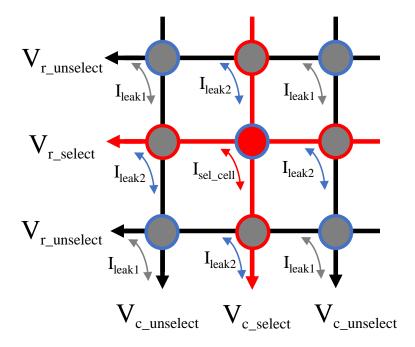

| 3.12 | Leakage currents within a resistive crossbar array due to biased unse-        |    |

|      | lected cells                                                                  | 45 |

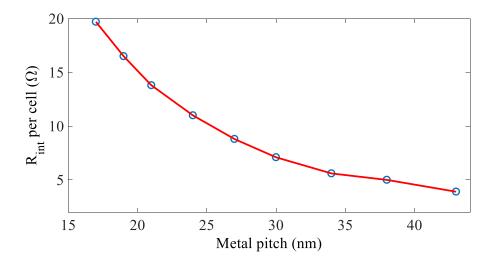

| 3.13 | Variation of interconnect resistance with respect to the metal pitch [82].    | 46 |

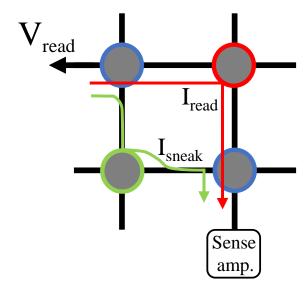

| 3.14 | The alternative path through the unselected rows and columns gener-           |    |

|      | ates sneak path currents, lowering the read margin                            | 47 |

| 3.15 | MOSFET as a selector to increase the $I_{on}/I_{off}$ ratio of a memory cell. | 48 |

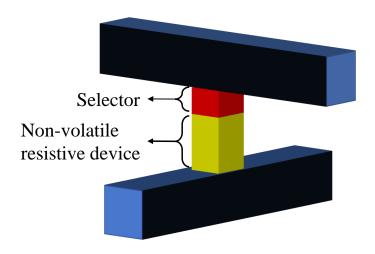

| 3.16 | A non-volatile resistive cell incorporating a two terminal selector device.   | 49 |

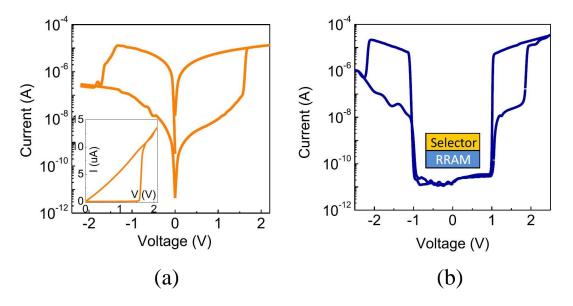

| 3.17 | The effect of a selector device, (a) selectorless bipolar RRAM, and (b)       |    |

|      | bipolar RRAM integrated with a selector [85]                                  | 50 |

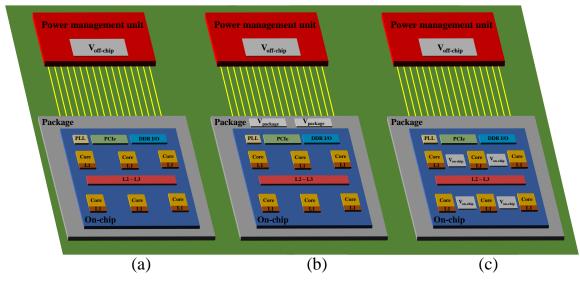

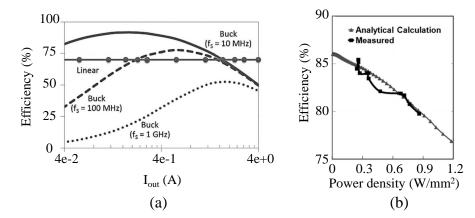

| 4.1 | Regulator to die distance, (a) physically distant high efficiency off-chip  |    |

|-----|-----------------------------------------------------------------------------|----|

|     | regulator, (b) in-package voltage regulator, and (c) multiple point-of-     |    |

|     | load on-chip voltage regulators producing heterogeneous voltages            | 53 |

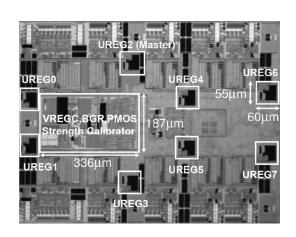

| 4.2 | Fully integrated on-chip voltage regulators, (a) eight distributed volt-    |    |

|     | age regulators across an IBM DDR3 I/O core [89], and (b) integrated         |    |

|     | power management on a cellular mobile IC from ST Ericsson [87]              | 55 |

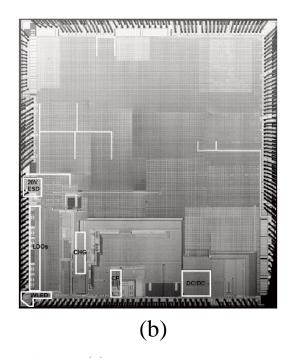

| 4.3 | Power efficiency of voltage regulators for different conversion ratios,     |    |

|     | (a) switched-capacitor converter with 2 volt input voltage [91], (b)        |    |

|     | switching buck regulator with 1.5 volt input voltage [92], and (c) linear   |    |

|     | regulator with 1.1 volt input voltage [90]                                  | 57 |

| 4.4 | The effect of the output current on power conversion ratios, (a) switch-    |    |

|     | ing buck regulator and linear regulator [95], and (b) switched-capacitor    |    |

|     | converter [91]                                                              | 58 |

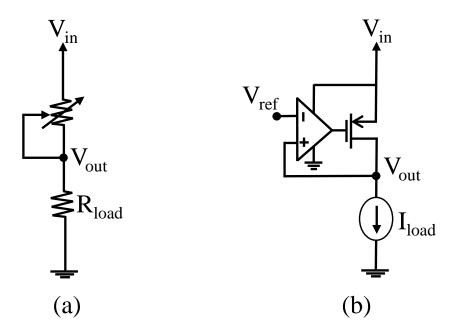

| 4.5 | Linear regulator, (a) simplified representation, and (b) practical circuit. | 59 |

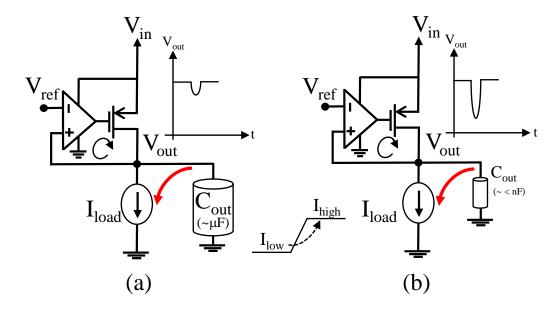

| 4.6 | Linear regulator, (a) with large output capacitor, and (b) with small       |    |

|     | output capacitor                                                            | 62 |

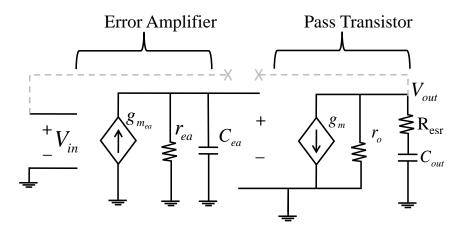

| 4.7 | Small–signal model of an LDO regulator                                      | 63 |

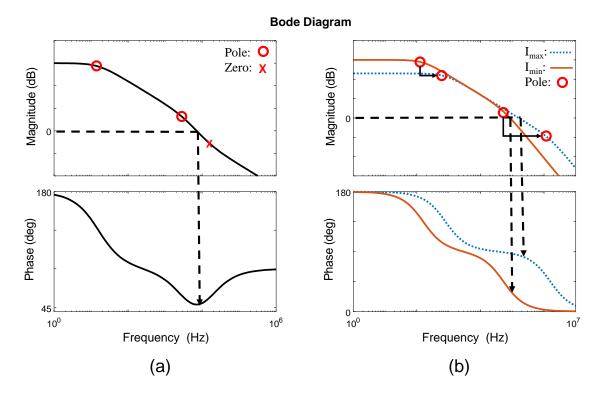

| 4.8 | Frequency response of an LDO regulator, (a) large output capacitor,         |    |

|     | and (b) small output capacitor                                              | 66 |

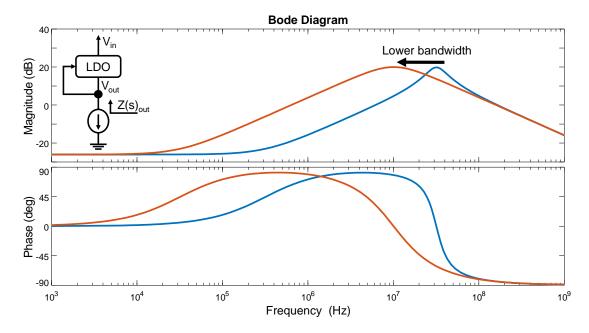

| 4.9  | Closed loop frequency response of the output impedance. The ESR                   |    |

|------|-----------------------------------------------------------------------------------|----|

|      | of $C_{out}$ is ignored. Decreasing the bandwidth of the error amplifier          |    |

|      | increases the output impedance, increasing the voltage droop                      | 68 |

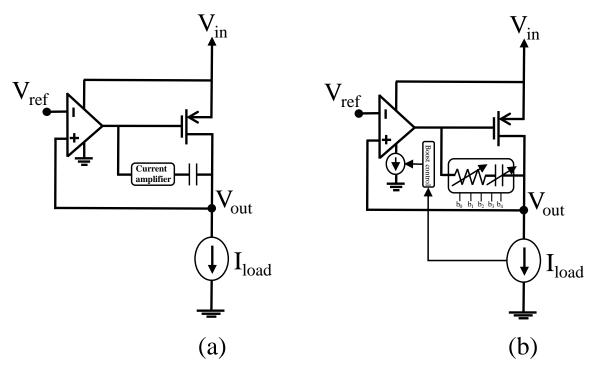

| 4.10 | Different LDO topologies, (a) slew-rate enhancement using current am-             |    |

|      | plifier [99], and (b) adaptive RC compensation with an adaptive boost             |    |

|      | technique [104]                                                                   | 70 |

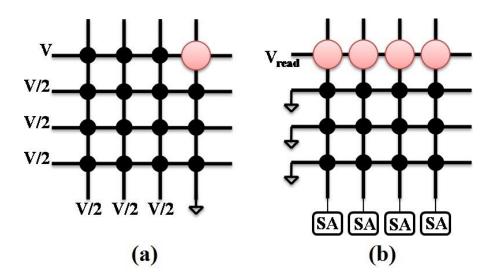

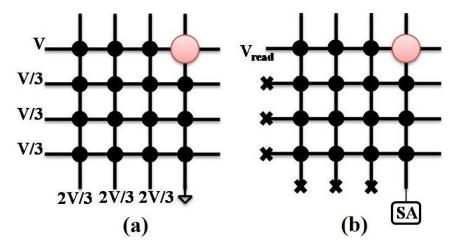

| 5.1  | Biasing scheme for a crossbar array when (a) writing to a cell, (b)               |    |

|      | reading from a cell                                                               | 75 |

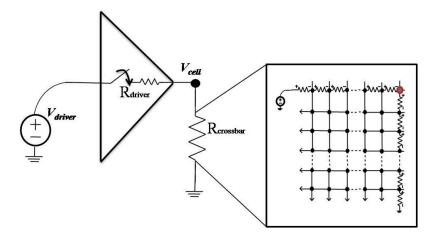

| 5.2  | Driver circuit                                                                    | 76 |

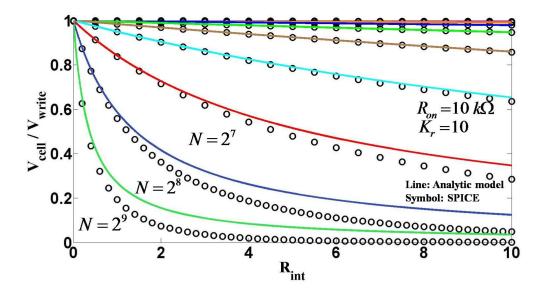

| 5.3  | Circuit model of crossbar array during a write operation                          | 80 |

| 5.4  | Ratio of the voltage drop across the worst case selected cell to the              |    |

|      | driver voltage during a write operation                                           | 81 |

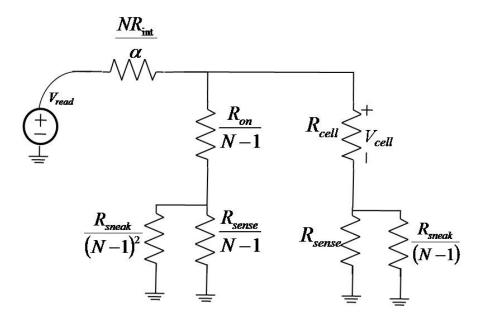

| 5.5  | The circuit model of the crossbar array during a read operation where             |    |

|      | $R_{sense}$ is the input resistance of the sense amplifier and $R_{sneak}$ is the |    |

|      | sneak path resistance of the resistive memory cells between the (un)selecte       | d  |

|      | column(s) and unselected rows                                                     | 82 |

| 5.6  | Ratio of the voltage drop across the worst case selected cell to the              |    |

|      | driver voltage during a read operation                                            | 84 |

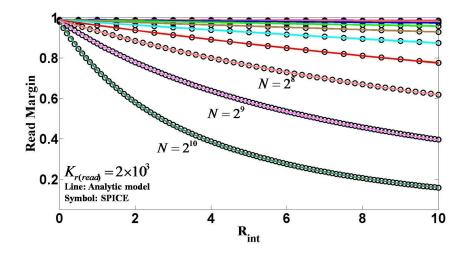

| 5.7  | Comparison of the read margin between the analytic model and simu-                |    |

|      | lation.                                                                           | 86 |

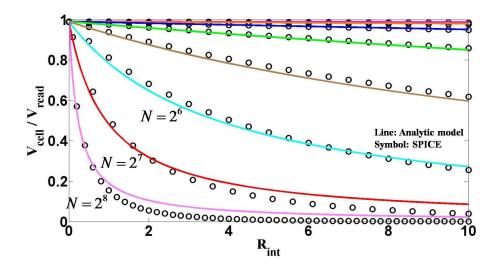

| 5.8  | Enhancing cell nonlinearity for (a) write operation with $V/3$ biasing                          |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | scheme, and (b) read operation with floating biasing scheme                                     | 87  |

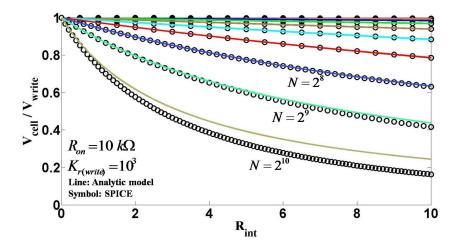

| 5.9  | Ratio of the voltage drop across the worst case selected cell to the                            |     |

|      | driver voltage during a write operation under the $V/3$ biasing scheme.                         | 91  |

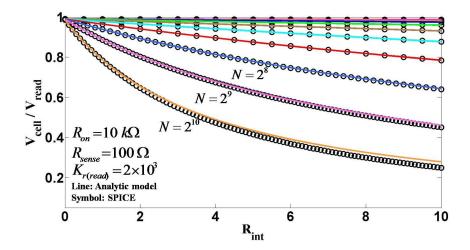

| 5.10 | Ratio of the voltage drop across the worst case selected cell to the                            |     |

|      | driver voltage during a read operation under the floating biasing scheme.                       | 91  |

| 5.11 | Comparison of the read margin between the model and simulation for                              |     |

|      | the floating biasing scheme.                                                                    | 93  |

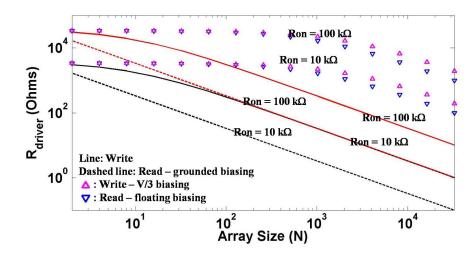

| 5.12 | Analytic model of driver resistance with respect to varying array sizes                         |     |

|      | for $K_r = 10$ , $K_{r(write)} = 2 \times 10^3$ , and $K_{r(read)} = 10^3$ that satisfies       |     |

|      | $\frac{V_{driver}}{V_{read}} = \frac{4}{3}.$                                                    | 94  |

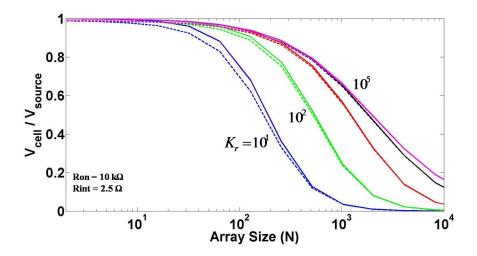

| 5.13 | Voltage degradation vs. array size where $V_{source} = V_{write}$ (solid lines)                 |     |

|      | and $V_{source} = V_{read}$ (dashed lines). $R_{sense} = 100 \ \Omega. \ . \ . \ . \ . \ . \ .$ | 96  |

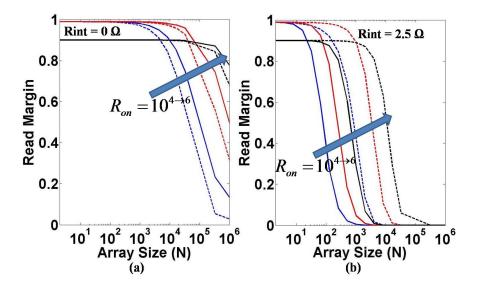

| 5.14 | Read margin with respect to array size based on the parameters listed                           |     |

|      | in Table 5.1 for (a) $R_{int}=0~\Omega,$ and (b) $R_{int}=2.5~\Omega.$ The solid                |     |

|      | lines describes the grounded biasing scheme whereas the dashed lines                            |     |

|      | describes the floating biasing scheme                                                           | 98  |

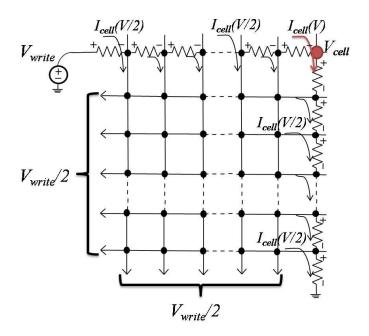

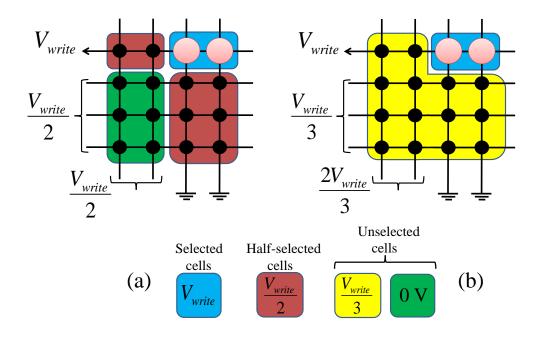

| 6.1  | Bias schemes for a two bit write operation, (a) $V/2$ bias scheme, and                          |     |

|      | (b) $V/3$ bias scheme                                                                           | 106 |

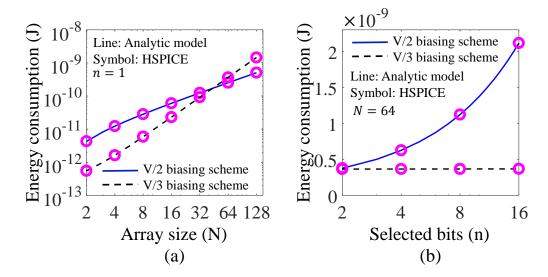

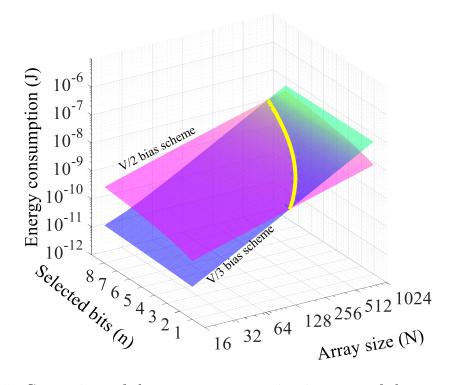

| 6.2 | Energy consumption of a crossbar array with respect to (a) array size,                 |     |

|-----|----------------------------------------------------------------------------------------|-----|

|     | and (b) number of selected cells, assuming $R_{on}=10^4~\Omega,~R_{off}=10^7$          |     |

|     | $\Omega, K_{V/2} = 20, K_{V/3} = 1,000, \text{ and } V_{write} = 2 \ V. \ldots \ldots$ | 111 |

| 6.3 | Effect of the number of selected cells on the energy consumption of a                  |     |

|     | crossbar array for the $V/2$ and $V/3$ bias schemes, assuming $K_{V/2}=20$             |     |

|     | and $K_{V/3} = 1,000$                                                                  | 112 |

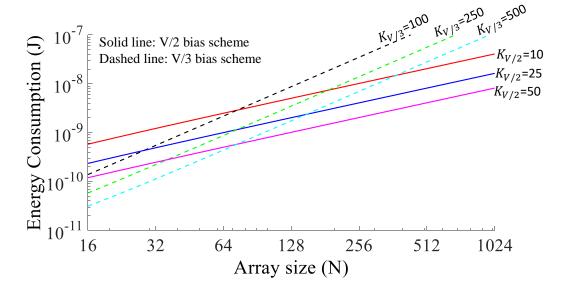

| 6.4 | Effect of the nonlinearity factor on the energy consumption of a cross-                |     |

|     | bar array for the $V/2$ and $V/3$ bias schemes, assuming $n=4.$                        | 113 |

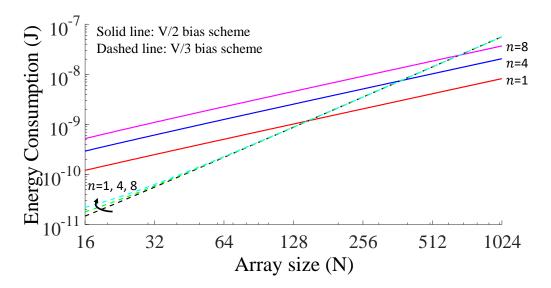

| 6.5 | Comparison of the energy consumption in terms of the array size and                    |     |

|     | number of selected cells for the $V/2$ and $V/3$ bias schemes, assuming                |     |

|     | $K_{V/2} = 20$ and $K_{V/3} = 1,000$                                                   | 114 |

| 6.6 | Energy savings of the $V/3$ bias scheme as compared to the $V/2$ bias                  |     |

|     | scheme assuming the same parameters listed in Fig. 6.5. The solid                      |     |

|     | line is the contour where the energy consumption between the two bias                  |     |

|     | schemes is equal                                                                       | 115 |

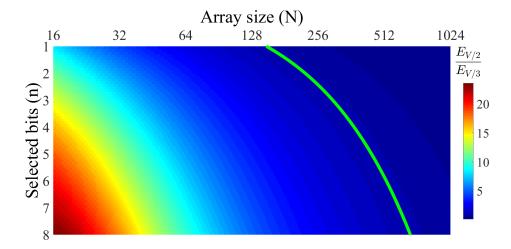

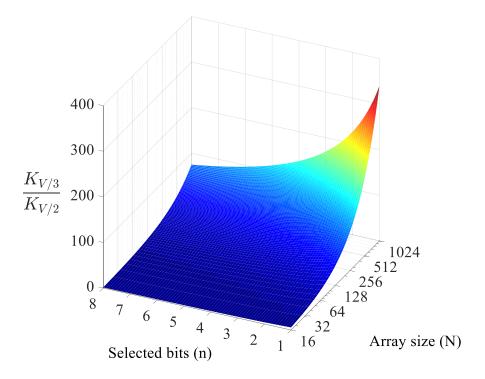

| 6.7 | Ratio of the nonlinearity factors $K_{V/3}$ to $K_{V/2}$ to maintain equal energy      |     |

|     | consumption for the $V/2$ and $V/3$ bias schemes in terms of the array                 |     |

|     | size and number of selected cells                                                      | 116 |

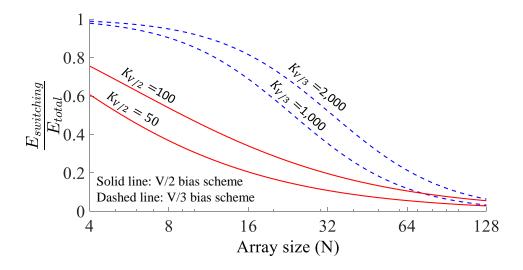

| 6.8 | Ratio of the switching energy to the total energy in terms of the array                |     |

|     | size, $R_{on} = 10^4 \Omega$ , $R_{off} = 10^6 \Omega$ , and $n = 4$                   | 118 |

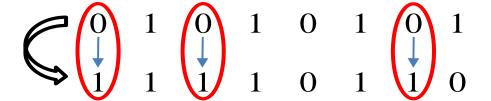

| 6.9  | Writing an eight bit word. Four bits of the new string are the same              |     |

|------|----------------------------------------------------------------------------------|-----|

|      | as the old string; however, only three bits are selected since one bit           |     |

|      | requires a reset whereas the other three bits require a set operation            | 120 |

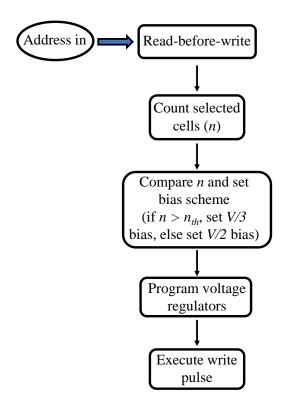

| 6.10 | Steps during the proposed energy efficient write scheme                          | 121 |

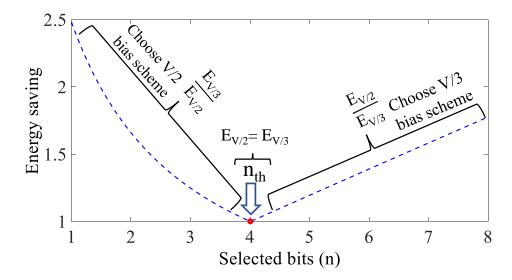

| 6.11 | Energy improvement in terms of the number of selected cells, assuming            |     |

|      | $N=128,K_{V/2}=20,{\rm and}K_{V/3}=345.$ The proposed write operation            |     |

|      | chooses the most energy efficient bias scheme based on the number of             |     |

|      | selected cells $n$ with respect to $n_{th}$                                      | 122 |

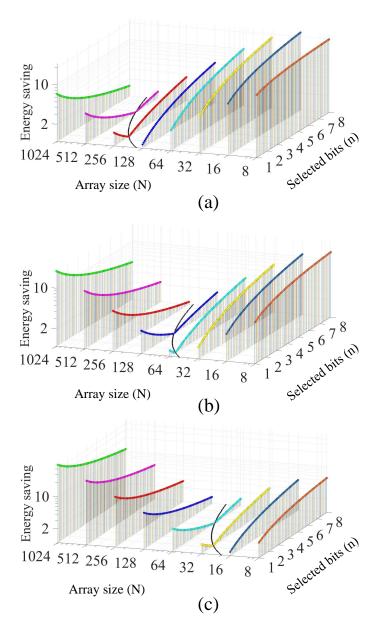

| 6.12 | Energy savings for different array sizes and number of selected cells            |     |

|      | considering, (a) $K_r = 1000/20$ , (b) $K_r = 345/20$ , and (c) $K_r = 345/50$ . | 123 |

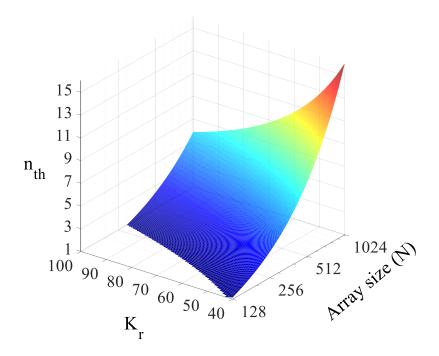

| 6.13 | Number of selected cell in which the energy for both bias schemes are            |     |

|      | equal with respect to $K_r$ and the array size $N$                               | 125 |

| P 1  |                                                                                  |     |

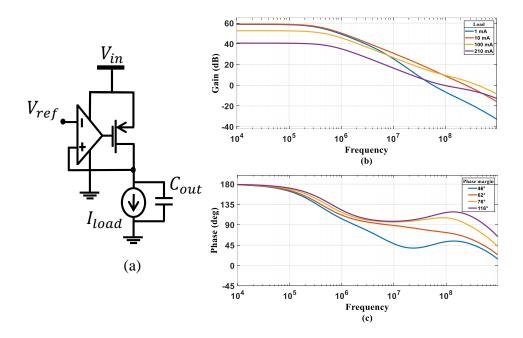

| 7.1  | Linear regulator used to analyze the stability of multiple connected             |     |

|      | LDOs, (a) conventional low dropout regulator, and (b) Bode plot of a             |     |

|      | regulator under different load conditions                                        | 133 |

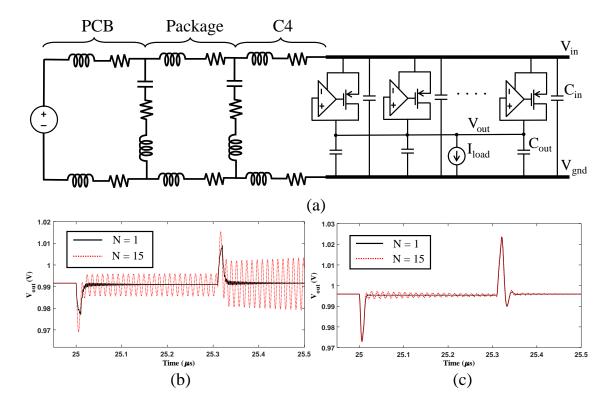

| 7.2 | Comparison of single LDO to multiple connected LDOs sharing a com-     |     |

|-----|------------------------------------------------------------------------|-----|

|     | mon power grid, (a) power delivery network with an input voltage of    |     |

|     | 1.2 volts and an output voltage of 1 volt, (b) transient response to a |     |

|     | load varying from 175 mA to 210 mA in 10 ns considering one and 15 $$  |     |

|     | LDOs, and (c) transient response to a load varying from 1 mA to 3      |     |

|     | mA in 10 ns considering one and 15 LDOs. The parasitic impedances      |     |

|     | are listed in Table B.1 in the Appendix. The input and output capac-   |     |

|     | itance are, respectively, 1 nF and 50 pF per LDO. The load current as  |     |

|     | well as the input and output capacitors proportionally increase with   |     |

|     | the number of regulators. Each regulator therefore operates under the  |     |

|     | same load conditions and AC characteristics (see Fig. 7.1b)            | 135 |

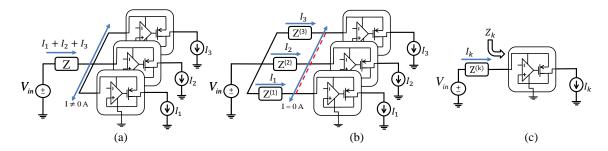

| 7.3 | Model of a power delivery system with parallel connected LDOs. The     |     |

|     | impedance of the power delivery network observed from the input of     |     |

|     | the LDOs is represented as a lumped impedance Z, (a) multiple LDOs     |     |

|     | attached to the same power grid, and (b) the grid impedance split per  |     |

|     | LDO, and (c) each LDO is separated based on the corresponding grid     |     |

|     | impedance at the input of the LDO                                      | 139 |

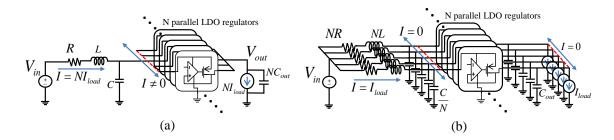

| 7.4 | Model of a power delivery system with parallel connected LDOs, (a)         |     |

|-----|----------------------------------------------------------------------------|-----|

|     | with an off-chip parasitic impedance, and (b) distribution of the para-    |     |

|     | sitic impedance when the LDOs operate under the same load conditions       |     |

|     | [158]. The quiescent current of the LDOs is assumed to be negligibly       |     |

|     | small                                                                      | 141 |

| 7.5 | Reduction of parallel connected LDOs operating under the same load         |     |

|     | conditions [158]                                                           | 141 |

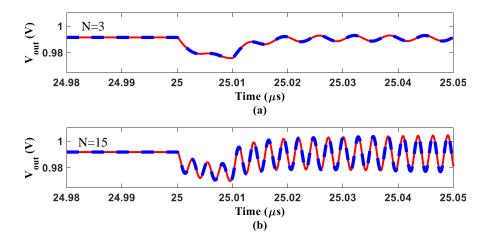

| 7.6 | Transient simulation of multiple connected LDO regulators where the        |     |

|     | solid line describes the circuit shown in Fig. 7.4a and the dashed line    |     |

|     | describes the circuit shown in Fig. 7.5, (a) three LDOs, and (b) 15        |     |

|     | LDOs                                                                       | 142 |

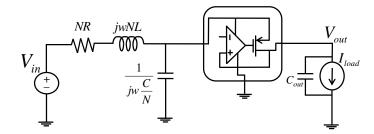

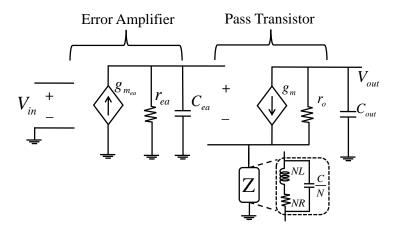

| 7.7 | Small-signal model of the simplified circuit shown in Fig. 7.5 [158]. $$ . | 143 |

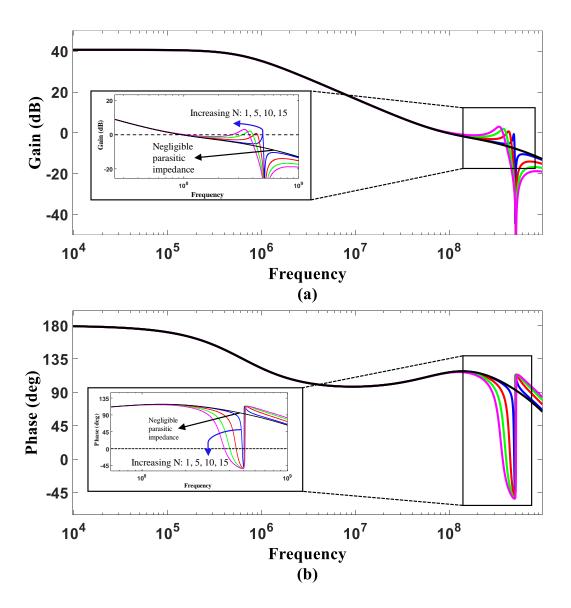

| 7.8 | Bode plot of circuit model shown in Fig. 7.5. The effect of an increasing  |     |

|     | number of parallel LDOs, (a) open loop gain, and (b) phase. With five      |     |

|     | parallel LDOs, the open loop gain rises above 0 dB beyond the initial      |     |

|     | unity gain frequency, producing an unstable system. $C=1$ nF, $L=$         |     |

|     | 100 pH, $R=100~\mu\Omega,C_{out}=50$ pF, and $I_{load}=210$ mA per LDO     | 145 |

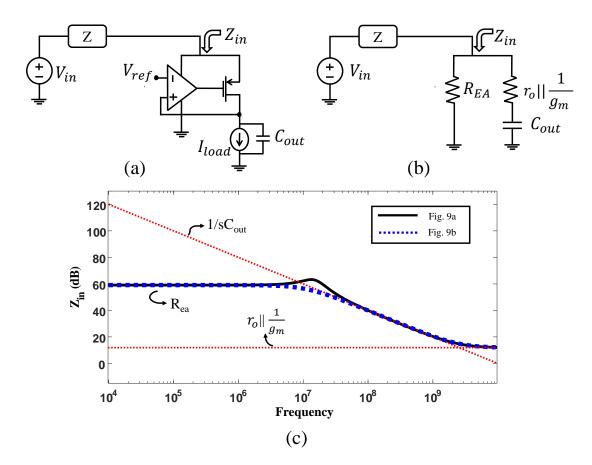

| 7.9 | Input impedance, (a) considering the LDO regulator, (b) model of the       |     |

|     | input impedance as an $RC$ circuit, and (c) comparison of the magni-       |     |

|     | tude of the input impedances                                               | 148 |

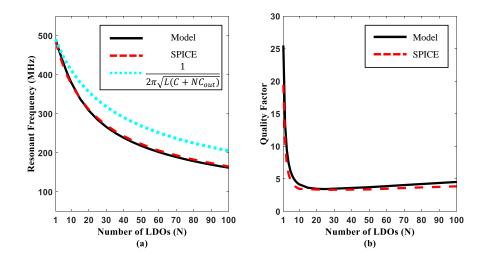

| 7.10 | Effect of different number of LDO regulators, (a) resonant frequency,          |     |

|------|--------------------------------------------------------------------------------|-----|

|      | and (b) quality factor, based on the circuit characteristics considered        |     |

|      | in Fig. 7.8. The model is based on the small-signal circuit shown in           |     |

|      | Fig. 7.7                                                                       | 150 |

| 7.11 | Output impedance of multiple LDOs sharing a common load                        | 152 |

| 7.12 | Decreasing phase margin shifts the complex poles of the output impedance       | е   |

|      | $p_{\pm}^{Z_{out}}$ to the RHP                                                 | 154 |

| 7.13 | Open loop transfer characteristics of an LDO assuming the simulation           |     |

|      | setup shown in Fig. 7.8, (a) a large output capacitance, and (b) a small       |     |

|      | output capacitance                                                             | 156 |

| 7.14 | Complex poles of the open loop transfer function $\mathcal{H}(s)$ become equal |     |

|      | to the complex zeros with decreasing output capacitance                        | 157 |

| 7.15 | Reduction in the open loop gain of the LDO significantly lowers the            |     |

|      | UGF. Decreasing the mid-band gain from 40 dB to 32 dB reduces the              |     |

|      | UGF (considering the first 0 dB crossing) from 100 MHz to 12 MHz.              | 158 |

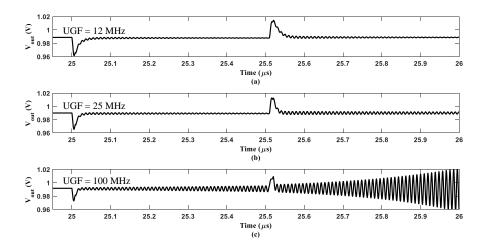

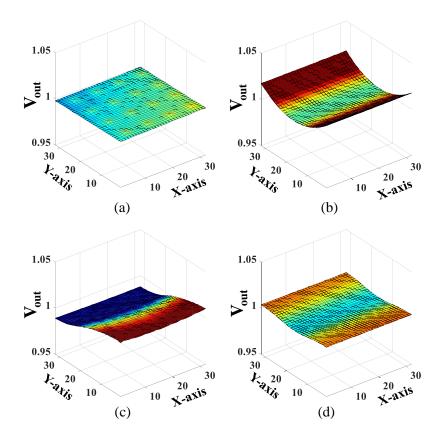

| 7.16 | Effect of the UGF on the output power grid shared by ten LDOs, (a)            |     |

|------|-------------------------------------------------------------------------------|-----|

|      | UGF at 12 MHz, (b) UGF at 25 MHz, and (c) UGF at 100 MHz.                     |     |

|      | An output capacitance of 100 pF and an input capacitance of 1 nF              |     |

|      | per LDO is considered with the off-chip power grid described in the           |     |

|      | Appendix. A total load variation from 1.75 A to 2.1 A is assumed              |     |

|      | (equally divided among the LDOs)                                              | 159 |

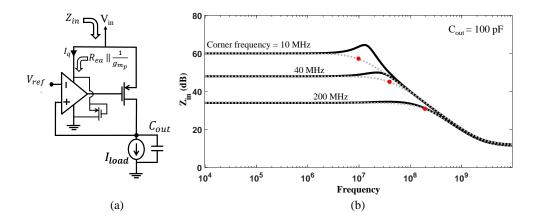

| 7.17 | Increasing the corner frequency of $ Z_{in} $ reduces the interaction between |     |

|      | the input and output power grids over a wider range of frequencies, (a)       |     |

|      | LDO with an additional pull-up transistor to reduce the resistance of         |     |

|      | the error amplifier $R_{ea}$ observed from the input power network, and (b)   |     |

|      | different corner frequencies of $ Z_{in} $ under a fixed output capacitance   |     |

|      | by increasing the quiescent current $I_q$ of the LDO                          | 160 |

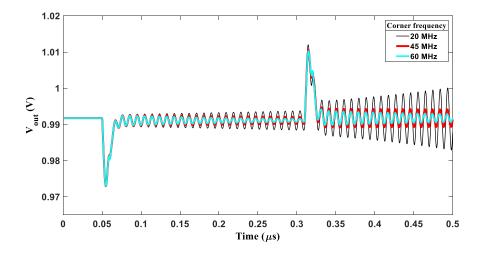

| 7.18 | Increasing the corner frequency of $Z_{in}$ reduces the interaction of the    |     |

|      | output capacitance with the input power grid, improving the stabil-           |     |

|      | ity of the power delivery network. The same power delivery network            |     |

|      | described in Fig. 7.15 is assumed with a UGF of 100 MHz                       | 161 |

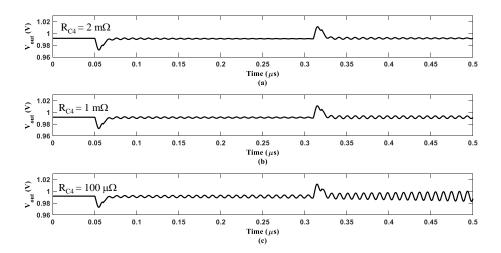

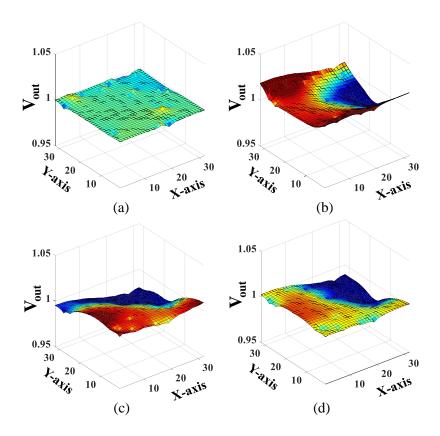

| 7.19 | C4 parasitic resistance $R_{C4}$ is increased to reduce the quality factor                       |     |

|------|--------------------------------------------------------------------------------------------------|-----|

|      | and improve the stability of the power grid. Transient response of the                           |     |

|      | output grid considering, (a) $R_{C4}=2~\text{m}\Omega$ , (b) $R_{C4}=1~\text{m}\Omega$ , and (c) |     |

|      | $R_{C4} = 0.1 \text{ m}\Omega$ . The power delivery network and parasitic impedances             |     |

|      | are listed in the Appendix with a load variation of 1.75 A to 2.1 A                              |     |

|      | evenly distributed among the ten LDOs. The resonant frequency is                                 |     |

|      | 112 MHz                                                                                          | 163 |

| 7.20 | Pole movement of the output impedance at the driving point, (a) con-                             |     |

|      | sidering single and multiple LDOs, and (b) several C4 parasitic induc-                           |     |

|      | tances                                                                                           | 164 |

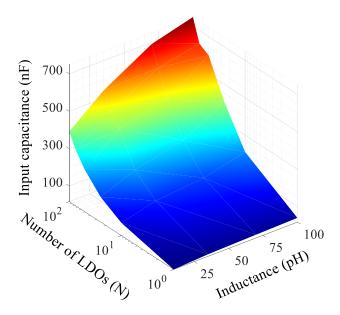

| 7.21 | Effect of inductance and number of LDOs on the input capacitance                                 |     |

|      | required to prevent a phase shift of more than $45^o$ at the resonant                            |     |

|      | frequency (considering the circuit characteristics used in Fig. 7.5)                             | 165 |

| 8.1  | A digital low dropout regulator                                                                  | 168 |

| 8.2  | Pass gates located at the centroid of a grid to source the distributed                           |     |

|      | load currents                                                                                    | 170 |

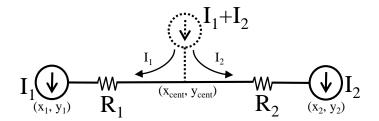

| 8.3  | Centroid of two load currents                                                                    | 171 |

| 8.4 | Iterative process for determining the centroid of three load currents, (a)     |     |

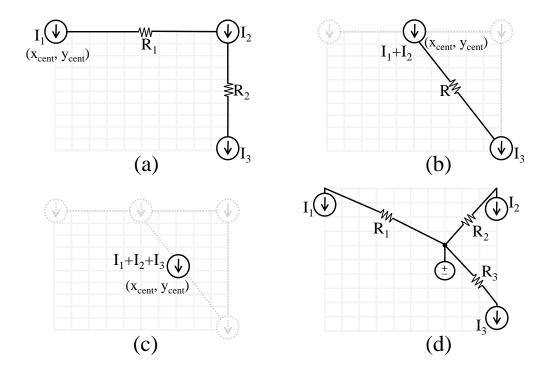

|-----|--------------------------------------------------------------------------------|-----|

|     | the centroid is initially assigned to load current $I_1$ , (b) a new centroid  |     |

|     | between $I_1$ and $I_2$ is determined and replaces the old centroid, (c) a new |     |

|     | centroid is determined between the current centroid and $I_3$ , replacing      |     |

|     | the old centroid, and (d) the final centroid is replaced by a source           |     |

|     | connected to the load currents                                                 | 173 |

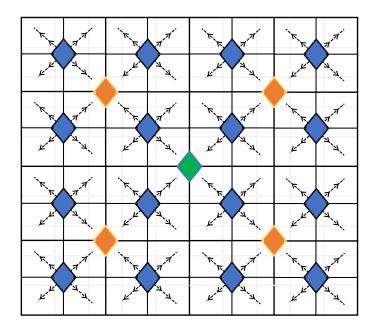

| 8.5 | Recursive process to determine multiple centroids                              | 174 |

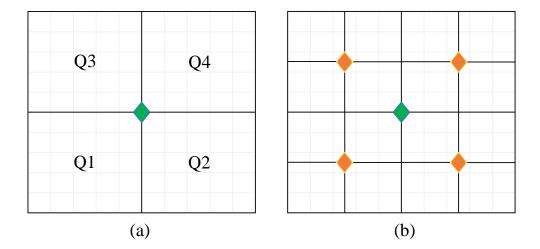

| 8.6 | Iterative process for determining the location of the quadrant centroids,      |     |

|     | (a) power grid divided into four quadrants, and (b) a centroid is placed       |     |

|     | within each quadrant. A diamond represents an individual centroid              | 175 |

| 8.7 | A power grid composed of 16 regions with separate centroids                    | 175 |

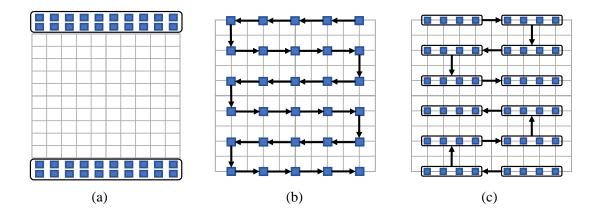

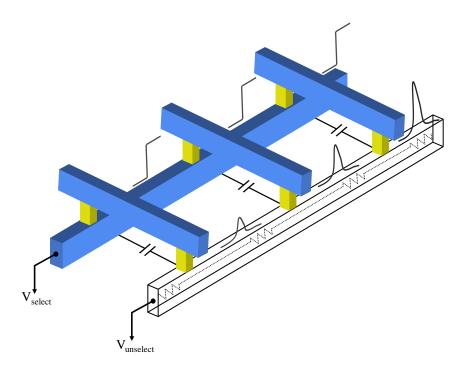

| 8.8 | Different pass gate distribution topologies, (a) top-bottom [96, 150],         |     |

|     | (b) daisy chain [172], and (c) distribution from [169]                         | 177 |

| 8.9 | Power grid analysis assuming a uniform load distribution, (a) pro-             |     |

|     | posed centroid-based distribution topology, (b) top-bottom topology            |     |

|     | [96, 150], (c) daisy chain topology [172], and (d) distribution topology       |     |

|     | from [169]                                                                     | 179 |

| 8.10 | Power grid analysis considering nonuniform load distribution, (a) pro-  |     |

|------|-------------------------------------------------------------------------|-----|

|      | posed centroid-based distribution topology, (b) top-bottom topology     |     |

|      | [96,150], (c) daisy chain topology [172], and (d) distribution topology |     |

|      | from [169]                                                              | 181 |

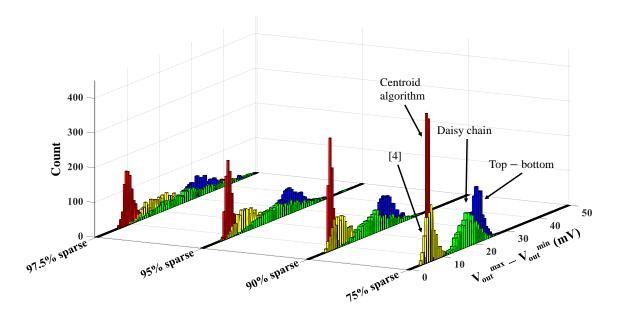

| 8.11 | Monte Carlo simulations evaluating the difference between the maxi-     |     |

|      | mum and minimum voltage across a power grid considering four dif-       |     |

|      | ferent pass gate distribution topologies                                | 182 |

| 10.1 | Noise coupling from a selected row to an unselected adjacent row        | 193 |

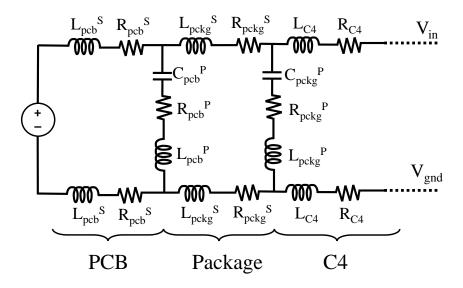

| B.1  | Off-chip power delivery network model considered in Sections 7.1 and    |     |

|      | 7.4 [165]                                                               | 219 |

# Chapter 1

## Introduction

"The forest is magnificent, yet it contains no perfect trees."

- Gye Fram

### 1.1 My Thesis

Grids (or meshes) are common geometric structures used throughout the design of very large scale integration (VLSI) systems, such as high performance microprocessors, due to the ordered structure that eases circuit scalability, lowers design complexity, improves performance, increases transistor density, and enhances reliability.

#### 1.2 Motivation

The exponential growth in the complexity and compute power of VLSI digital systems has significantly enhanced human civilization [1]. This increasing growth in compute power supported by algorithmic discoveries have enabled tackling difficult problems that were once thought to be unsolvable [2, 3]. The demand for computational power however has yet to cease, continuously pushing the semiconductor industry to design and manufacture ever more complex VLSI systems [4, 5].

From the very first practical microprocessors, such as the Intel 4004, to the latest and most advanced examples, such as the IBM Power9, there has always been tremendous challenges in the design, development, manufacture, and test of these highly complex systems [6–10]. While the Intel 4004 contained a few thousand transistors in 1971 [6], there was little support from electronic design automation (EDA) tools. Structured and automated placement and routing tools started to appear in the early 1980's, years after the development of the first microprocessors [11]. To develop complex integrated circuits (IC) in the late 1960's and early 1970's, companies utilized a large number of engineers and technicians to manually craft and optimize these circuits [12]. Alternatively, modern microprocessors often contain many tens to hundreds of billions of transistors. These integrated circuits are significantly more expensive to develop and manufacture despite the support provided by advanced EDA tools [13]. This increased design challenge is primarily due to reliability and noise

coupling issues in deeply scaled technology nodes as well as the increased functional complexity of advanced ICs that even the most capable EDA tools have difficulty in tackling [13–16].

A vast number of engineers spend countless hours developing complex ICs based on a variety of principles and guidelines to manage the complexity of designing these VLSI systems. In the early days of IC development, area and speed were the primary criteria shaping these design principles. The successful continuation of transistor scaling relaxed some of these initial design criteria, such as area, and enabled massive computational power which reinforced complex design procedures. Scaling however has also brought challenges that have not yet been considered, such as process (manufacturing) variability and thermal reliability. As a result, the design guidelines and tools have evolved over time [12,17]. Today, the primary critera shaping design principles and guidelines are speed, power, reliability, signal integrity, and security [18,19]. While the process in which complex ICs are engineered continues to change, one particular topology has been used throughout the development of integrated systems; the grid.

In Section 1.3, the concept of grids and the relationship of grids to VLSI systems are reviewed. Those aspects of VLSI systems that rely on grid structures are described. In Section 1.4, an outline of this dissertation is provided, summarizing the following chapters.

### 1.3 The Grid

The grid is a set of intersecting horizontal and vertical lines forming an ordered structure (as described in greater detail in Chapter 2). Grids embody a rich set of properties, such as regularity, modularity, scalability, and density. Many applications over a wide range of disciplines use grids to tackle different kinds of problems and challenges, as illustrated in Fig. 1.1 [20–22]. From architecture to city planning to

Figure 1.1: Grid systems are used in a variety of design and engineering problems, (a) architecture, (b) Manhattan gridiron plan, and (c) graphic design of the New York Times.

graphic design, grids are used for a variety of reasons. For example, graphic designers adopt grids in newspapers, websites, and other media platforms to organize

content in a structured and compact fashion [23]. In city planning, grids are used to enhance scalability, efficiently use space, and ease transportation [24]. In architecture and construction, grid systems form efficient supporting structures to equally distribute carried loads while benefiting from structural redundancy to improve robustness against failures [25].

Similarly, VLSI systems have exploited grid structures, as shown in Fig. 1.2 [26,27]. Grids have been used in integrated systems since the early days of IC design.

Figure 1.2: Repeated cell structures forming a grid in die photographs, (a) Intel 4004, and (b) IBM Power9 processor.

One of the first microprocessors, the Intel 4004, included an on-chip memory laid out in a grid structure (see Fig. 1.2a). The grid, shown in Fig. 1.2a, is a DRAM memory array formed of three transistor cells [7,28]. The use of grids in memories has led to high density, low cost, and reliable ICs. In contrast, the initial development of logic circuits lacked design guidelines and were implemented in more of a random fashion [29]. With transistor scaling, circuit complexity has increased while density and yield

has become more critical. Early logic circuits were therefore not as reliable and dense as memories [29].

To match the yield and density of memory ICs, structured design methodologies for the logic gates have been developed [30]. The use of grids has been extended to many other parts of an IC other than memory, from logic to interconnect to network communication within multicore systems, as shown in Fig. 1.3 [31–34]. To provide

Figure 1.3: Grid based IC design, (a) DRAM memory array, (b) programmable logic array (PLA), (c) interconnect routing, and (d) mesh-based network for communication within multicore microprocessors.

a more efficient structure to logic circuits, programmable logic arrays (PLA) were developed [32]. These circuits enable memory-like, structured logic circuits, forming grid-based functional units. The fixed structure of a PLA however has come at a cost of reduced design flexibility, lowering performance. Initially, this structured design approach was preferred to improve circuit density despite suboptimal performance. With the advent of advanced EDA methodologies however other structured design

techniques such as standard cell-based circuits are usually preferred [31]. Interconnects in VLSI systems consider rectilinear routes where each metal layer is typically directed along a preferred axis (horizontal or vertical direction) [35]. Automated routing tools use a grid topology as a guideline to generate these interconnects, each aligned with the grid (see Fig. 1.3c) [33]. While diagonal routing reduces interconnect length and increases performance, grid-based rectilinear routing is mostly preferred due to the greater computational efficiency [33, 35]. Since a complex VLSI system can contain many billions of nodes, computationally tractable heuristic approaches are preferred over optimal but computationally expensive techniques. In multicore VLSI systems, the cores are typically connected within a mesh structure [34, 36–39]. The regularity of mesh-based multicore networks support scaling the number of cores [37–39]. Scalability of the network becomes critical as the number of on-chip cores increases. This increase in multicores is due to on-chip thermal and power constraints, pushing the development of highly parallel architectures to improve computational efficiency under a fixed power budget [40].

In addition to these aforementioned applications, grids have been considered in a variety of other aspects of a VLSI system such as the on-chip power delivery and clocking networks, and field programmable gate arrays (FPGAs) (see Chapter 2) [18, 41, 42]. The applicability and influence of grids across a wide range of design methodologies in VLSI systems have resulted in the physically structured and ordered

layout found in modern VLSI systems (see Fig. 1.2b). The seminal influence of grids in high performance ICs stem from the need to manage these highly complex systems. Fundamentally, the grid system forms a set of rules, creating a framework to effectively manage complexity, allowing the formation of tractable design solutions. The grid system is therefore an inseparable design element in the development of complex integrated systems.

#### 1.4 Outline

In this dissertation, applications of grid structures to VLSI systems are examined in Chapter 2, beginning with the definition and attributes of grids. The grid offers different properties that can enhance speed, power, reliability, and density in VLSI systems. The influence of grids in the IC design process, such as power delivery, clock distribution networks, memory systems, programmable logic arrays, and automated routing, is discussed.

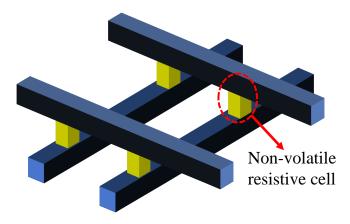

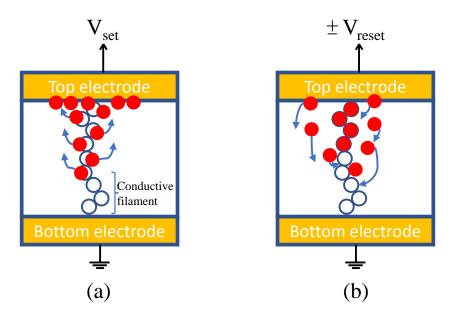

In Chapter 3, different types of nonvolatile resistive memories are reviewed. The working mechanisms of resistive RAM (RRAM), phase change memory (PCM), and magnetoresistive RAM (MRAM) are explained. These devices exhibit different strengths and weaknesses and are therefore used in different types of memory systems (e.g., cache, main memory, or disk). Similar to charge-based memories, such as DRAM,

SRAM, and flash, nonvolatile resistive memories are physically based on a grid structure. The advantages and challenges of grids (i.e., crossbars) and mitigation techniques, such as including selector devices, are discussed.

In Chapter 4, on-chip power delivery systems with integrated voltage regulators are reviewed. The power delivery network is typically structured as a grid. This network is supported by multiple on-chip voltage regulators in high performance ICs to reduce power consumption via dynamic voltage scaling (DVS). Different types of voltage regulators along with the advantages and disadvantages are described. The working mechanism of low dropout (LDO) voltage regulators is discussed with an emphasis on regulator stability.

In Chapter 5, closed-form expressions that model critical metrics of nonvolatile resistive crossbar arrays are provided. These crossbar arrays are widely considered as a likely memory technology that will replace DRAM and flash memory. The performance and capacity of resistive crossbar arrays are however limited due to sneak paths and the parasitic interconnect resistance within the grid. To reduce computational time and provide intuitive design guidelines, a set of compact closed-form expressions modeling these aforementioned limitations is described.

The modeling approach discussed in Chapter 5 is extended in Chapter 6 to evaluate the write energy consumption of nonvolatile resistive crossbar arrays. The write energy of resistive memory arrays are described, considering data dependencies and bias schemes. Moreover, a hybrid, energy efficient write scheme utilizing multiple bias schemes is proposed to decrease the write energy based on the number of selected cells.

In Chapter 7, the stability of on-chip power delivery networks with multiple integrated capacitorless LDO regulators is explored. As the number of on-chip LDOs that share a common grid grows, the stability of the power delivery network degrades. This effect is primarily due to the decreasing resonance frequency with increasing number of LDO regulators. The degradation of grid stability is intuitively described, and an expression that relates stability to the number of LDOs is provided.

Moreover, the challenges of integrating digital LDOs within an on-chip power grid is described in Chapter 8. In a power delivery system with distributed pass transistors, the flow of current depends upon the physical location of the pass transistors, which can have a major effect on the power noise. A methodology to distribute the pass gates of a digital LDO is proposed based on grid centroids. The proposed distribution topology is compared to earlier topologies in terms of steady state IR drops within a power grid.

Lastly, a summary and concluding remarks of this dissertation are offered in Chapter 9, and future research directions are described in Chapter 10. The effect of noise coupling among adjacent rows and columns in a resistive memory array is explained. In deeply scaled technologies where the interconnect pitch is small, capacitive coupling can disturb the memory cells along the unselected lines. This reliability issue, similar to the RowHammer problem, is discussed in greater detail.

# Chapter 2

# Grids in Integrated Systems

"The grid system is an aid, not a guarantee. It permits a number of possible uses and each designer can look for a solution appropriate to his personal style. But one must learn how to use the grid; it is an art that requires practice."

- Josef Müller-Brockmann, Grid Systems in Graphic Design, 1981

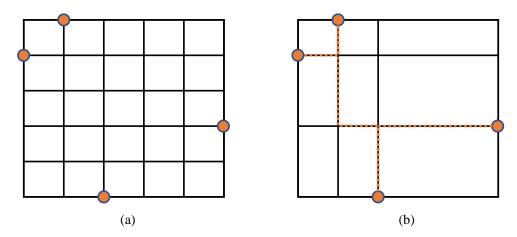

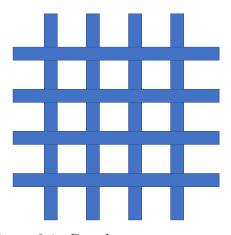

Grids are common structures within integrated systems such as memories [43], logic arrays [30], power delivery networks [44], networks-on-chip (NoC) [45], and automated layout [46]. The grid structure provides several benefits to different aspects of VLSI circuits. Depending upon the application, grids can be used to form an orderly structure to improve scalability and robustness, enhance density, or reduce computational time. A grid is a geometric structure formed of similar tiles, such as a square, rectangle, or triangle, tightly packed together, as shown in Fig. 2.1. A tile is a substructure that is copied multiple times to form a larger and regular structure. In

Figure 2.1: Grid structures, (a) square grid, and (b) triangular grid.

this dissertation, a grid is considered to be composed of a tile of squares or rectangles (see Fig. 2.1a) that need not be uniform. Note that the term, grid, is interchangeably used with the word, mesh.

The grid structure offers several properties often favored in complex integrated systems. These traits are density, regularity, and path diversity. Density is critical in VLSI systems due to limited die area. Since area is the primary factor determining cost and fabrication yield [29, 47], ICs are typically crammed with as many transistors as possible to enable a multitude of computational capabilities under a fixed area constraint. Regularity is highly desired in VLSI systems since regular structures are easier to scale, fabricate, design, and test [42, 48]. Regular structures produce more predictable results. Path diversity is the number of paths between two connected points. Structures including redundancy (e.g., redundant communication links or metal interconnects) against a variety of failures, such as faulty ineterconnects or

congested communication networks [47,49], improve the overall robustness and yield of VLSI systems. In addition, grid structures are utilized by fast algorithms, enabling the computationally efficient automation of the VLSI design process, such as interconnect layout (see Section 2.4).

In this chapter, these properties of a grid useful to the development of VLSI systems are considered. In Section 2.1, the grid as an enabling structure for dense VLSI systems is described. In Section 2.2, a discussion on the regularity of grids and application to high density circuits is provided. In Section 2.3, the path diversity of grids and the relationship to system robustness is explained. In Section 2.4, the role of grids in automated layout is described. In Section 2.5, a summary of this chapter is offered.

### 2.1 Density

Density has different meanings depending upon the field (e.g., linear algebra [50], graph theory [51]). In this dissertation, density describes the total area occupied by the transistors in terms of the total on-chip area. An integrated circuit is dense if significant on-chip area is utilized by transistors. Density is critical to VLSI systems since the greater the number of transistors, the more functionality that can be

provided. In addition, die area is a major factor affecting cost. Larger dies also typically produce lower yield. Circuits that utilize significant die area at high density are therefore highly favored.

Grids form compact layouts, efficiently using on-chip area. These structures are therefore common in VLSI circuits, particularly those circuits requiring extremely high density such as memory arrays. For illustrative purposes, consider an arbitrary memory cell, as shown in Fig. 2.2. A memory cell is a circuit or device that stores a

Figure 2.2: Top view of a unit memory cell with a cell height of h and width of w.

single bit of information, either a 0 or a 1. The shaded box represents the memory cell with two pins enabling either a write or read operation from/to the cell. The total cell area,  $h \cdot w$ , is the area occupied by the memory circuit, as constrained by the design rules of a particular technology node<sup>1</sup>. Considering an overall on-chip area of  $H \cdot W$  (H and W are, respectively, the height and width of the on-chip area), the total number of memory cells in this area cannot be more than  $\frac{H \cdot W}{h \cdot v}$ . The layout structure

<sup>&</sup>lt;sup>1</sup>Every component in an IC has a minimum physical separation from another neighboring component to mitigate manufacturing errors.

with the greatest number of cells naturally forms a grid structure, as illustrated in Fig. 2.3. A grid is therefore the most common structure in those circuits requiring high density.

Figure 2.3: Placement of memory cells within a grid structure for higher density.

An exemplary memory array is depicted in Fig. 2.4a [43]. A memory array also requires additional peripheral circuits such as row and column decoders to function properly. Memory systems consist of multiple arrays rather than a single large array since the performance of the memory decreases as the array size grows [52]. A memory IC therefore consists of multiple sub-arrays as well as peripheral circuits to support read and write operations.

The grid structure in memories provides superior circuit density as compared to logic circuits designed in a more random fashion. A similarly structured, grid-based design approach has therefore been applied to logic circuits [30]. One of the early

examples of a logic oriented grid structure was the programmable logic array (PLA), as shown in Fig. 2.4b [29, 32, 53]. The PLA is a one time programmable circuit

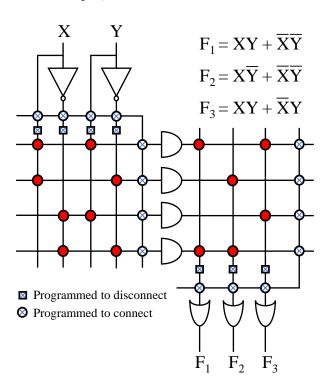

Figure 2.4: Examples of grid structure in integrated circuits for high density, (a) memory array, and (b) programmable logic array (PLA).

that computes multiple Boolean logic functions using two arrays; an AND array and an OR array. These arrays are programmed by placing a short at a crosspoint to connect a horizontal line to a vertical line. The inputs, initially passing through the AND array, are fed to a large AND gate. The OR array transmits the output of the AND gates to the OR gates. As a result, multiple boolean functions in the form of sum-of-products is obtained (see  $F_1$ ,  $F_2$ , and  $F_3$  shown in Fig. 2.4b). The PLA consumes significantly less area as compared to random logic, improving both density and performance.

Density was a particularly major concern in the early days of the semiconductor industry when the transistor channel length was on the order of a few micrometers. PLAs were therefore a highly favorable design approach. Today, however, area is less of a concern due to advanced technology nodes where transistor channel lengths range from a few tens of nanometers to a few nanometers [18]. Moreover, with the advent of advanced layout tools, logic circuits based on standard cells are commonly used, limiting the use of PLAs to a few specialized applications such as finite state machines [54–56]. Since capacity remains critical in memory systems, grid structures are still in common use in memory circuits.

### 2.2 Regularity

Grids are also used due to the structural regularity. Regular structures are preferred in VLSI systems due to the ease of fabrication and scalability. The definition of regularity in [57] for structural analysis is described here. A regular structure consists of multiple similar substructures applied in a repetitive fashion (e.g., see Fig. 2.1).

A structure represented as a graph G(V, E), formed of a set of vertices V and edges E, is regular if G(V, E) is a graph product of two or three subgraphs, also known as generators [57]. The graph Cartesian product is used to illustrate the formation of regular structures from two generators. The graph Cartesian product of two graphs  $G_1(V_1, E_1) \square G_2(V_2, E_2)$  is the graph formed of the set of vertices  $V_1$

$X V_2 = \{(x_i, y_j) | x_i \in V_1, y_j \in V_2\}$  with edges between a pair of vertices  $(x_i, y_j)$  and  $(x_i', y_j')$  if and only if  $(y_j, y_j')$  is an edge of  $G_2$  when  $x_i = x_i'$  and  $(x_i, x_i')$  is an edge of  $G_1$  when  $y_j = y_j'$  [51]. The graph Cartesian product copies the graph  $G_1$  for every node of  $G_2$  (and vice versa) [51], as illustrated in Fig. 2.5. Note that a generator

Figure 2.5: Graph Cartesian product of two generators produces a regular graph, (a) triangle graph and heptagon, (b) path graph and hexagon, and (c) two path graphs producing a grid graph.

is replicated for every node of the second generator, thereby forming a repetitive structure that is called regular. Similarly, a grid can be formed of two path graph<sup>2</sup> generators, as shown in Fig. 2.5c. The grid graph is therefore regular and consists of repetitive tiles.

Regularity in circuits and systems has several benefits, one of which is scalability. A regular structure is scalable due to the repetitive nature that supports additional structural elements (e.g., nodes in a graph, or rows or columns in an array). The repetitive substructure provides a guideline for integrating additional tiles into a regular structure (e.g., a new node connects to the head or tail of a path graph

<sup>&</sup>lt;sup>2</sup>A path graph is a set of nodes connected in series, forming a path-like structure.

to preserve the sequential order). Scaling is critical to VLSI systems since circuits need to accommodate an increasing number of transistors in evolving generations of technology nodes to improve speed, reduce power, increase yield, and/or increase functional and memory capacity. Scalable circuits leverage the increasing number of transistors without significant changes in topology or design methodology. In contrast, circuits that are difficult to scale need to be significantly re-designed to accommodate the additional circuitry, increasing design time and cost.

An exemplary regular and scalable on-chip structure is the mesh-based network-on-chip (NoC), as shown in Fig. 2.6a [45]. With increasing number of transistors,

Figure 2.6: Regularity of a network-on-chip (NoC) based on a mesh topology.

multiple cores integrated onto a single die has become feasible [38]. The number of on-chip cores has reached several tens of cores in today's commercial products and continues to improve computational performance under a fixed power budget [58–61]. A scalable network topology, such as a mesh topology, is therefore preferred to accommodate the increasing number of cores without re-designing the communication network in evolving generations of microprocessors [45].

Furthermore, regularity simplifies the addition of redundancy to improve fault tolerance and yield. VLSI systems typically contain redundant elements to tolerate fabrication failures. For example, an additional column or row can be inserted into

Figure 2.7: Redundancy insertion in PLAs to enhance yield. The regular structure of a PLA supports fault tolerant circuits.

a memory or programmable logic array to replace a faulty column or row [47]. An exemplary PLA circuit with a redundant row and column is shown in Fig. 2.7 [62,63]. The redundant rows and columns (initially disconnected) are connected to the AND

and OR arrays to replace faulty connections after testing the circuit whereas the faulty lines (initally connected) are disconnected from the arrays<sup>3</sup> [47]. Note that redundancy insertion in arrays requires low area due to the regularity of the grid. In contrast, random logic does not exhibit a structured pattern, making the insertion of redundancy more difficult [47]. Random logic therefore requires significantly greater area as compared to a grid-based circuit topology.

## 2.3 Path Diversity

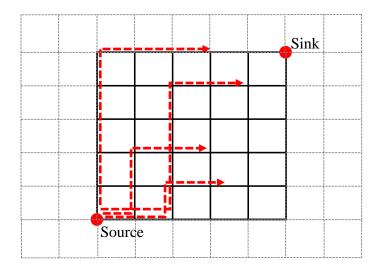

Path diversity is the number of paths connecting two points. Grid structures are used to reliably communicate within networks. In a grid, a multitude of alternate paths often exist. Different alternative paths supported by a grid is illustrated by the example shown in Fig. 2.8. The high path diversity within dense grids enhances the robustness of connected paths against failures such as electromigration, fabrication defects, and/or congestion. The number of paths between two points on a grid (assuming only upward and rightward directions) separated by n rows and m columns is

$$\binom{m+n}{n} = \frac{(m+n)!}{(n!)(m!)}.$$

(2.1)

Path diversity therefore significantly increases with the number of rows and columns.

The multitude of paths within a grid enhances several aspects of VLSI systems. One

<sup>&</sup>lt;sup>3</sup>One possible approach to disconnecting faulty lines is using fusible links. Fusible links, initially shorted, can be blown to form an open circuit [47].

Figure 2.8: Alternate paths between two points within a mesh improve robustness and reduce the effective parasitic impedance between the source and sink.

important example is the power delivery network. A power delivery network consists of metal interconnects spanning a VLSI circuit delivering the current necessary to billions of loads to successfully operate an IC [44].

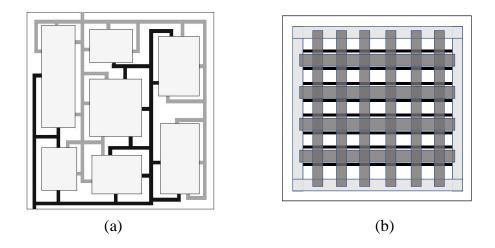

Two interconnect topologies are commonly used to delivery power; tree and mesh, as shown in Fig. 2.9 [18,64]. The preferable topology of a power delivery network within an IC depends upon the total current, maximum voltage noise, and available metal layers. A tree structured power network was often used in early microprocessors where the current delivered to an IC is small and the wide metal interconnects exhibited negligible parasitic resistance [26]. Tree structured power networks are however susceptible to failure since a single interconnect fault along a path in a tree can produce an open circuit between the power supply and the circuit, catastrophically

Figure 2.9: Power delivery networks, (a) tree structured, and (b) mesh-based topology. increasing the output impedance of the network. Tree structured power networks are therefore unsuitable for delivering power in modern high performance VLSI systems where the total current is on the order of hundreds of amperes and the interconnect resistance needs to be below milliohms.

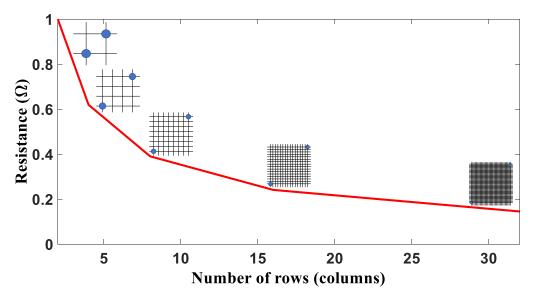

Alternatively, a grid structured power network improves robustness against interconnect failures since alternative paths within a grid can replace the faulty interconnects. Furthermore, the abundance of alternate paths reduces the effective parasitic

resistance between the current loads and the source of power, as illustrated in Fig.

2.10. The number of paths significantly increases as additional rows and columns

are inserted, greatly lowering the resistance between the source and load. Similarly, the detrimental effects of interconnect failures are mitigated by greater path

diversity. The maximum grid density (number of rows or columns, or interconnect

Figure 2.10: Effective resistance across a grid (between marked points) with respect to grid density, assuming an equal number of rows and columns.

width) however depends upon the available metal resources as well as physical design rules. On-chip metal resources are typically limited, requiring careful management and distribution among the data signals, decoupling capacitance, shield lines, and clock networks to satisfy performance and signal integrity requirements. The available metal resources however can be effectively managed with grids. Since the grid is also a regular structure, the metal resources (number of rows or columns and interconnect widths) are easier to manage than a power network formed of an irregular structure. Grids are therefore the dominant interconnect topology to delivery power across complex integrated systems.

### 2.4 Computational Efficiency

Grids are often used in electronic design automation; specifically, to route an IC. Grid-based routing improves computational performance as opposed to gridless routing [33]. During net routing, a grid is superimposed over the routing region (see Fig. 1.3c). Depending upon the type of routing (global or detailed), the grid edges represent routing tracks where interconnects are allowed [33,64]. The interconnects are placed on these available tracks connecting different terminals while considering potential obstacles (e.g., signal pins, I/Os) and minimizing cost (such as interconnect length).

A critical metric characterizing routing quality is the average length of the interconnect [46]. Long interconnects produce larger parasitic impedances. Routers therefore typically search for the shortest path between pins (or terminals). Grid-based routing requires less computational time to solve the single source shortest path problem. The run time of the single source shortest path problem for an arbitrary graph with positive edge lengths can be as low as O(Elog(V)) (based on the Dijkstra algorithm) [65]. If the graph is a grid of uniform length, the complexity for solving the shortest path problem can decrease to linear time O(V) (based on the Hadlock algorithm) [66].

Multi-pin routing is another problem considered in automated layout tools. The problem of determining the shortest tree connecting multiple terminals is described as

a Steiner problem [67]. Since on-chip metal interconnects are directional (horizontal or vertical depending upon the metal layer), the rectilinear distance (also known as the Manhattan distance or taxi cab metric) between nets is considered as a primary metric. As a result, the shortest routing cost connecting multiple pins is described as the minimum rectilinear Steiner tree (MRST) problem. A Hanan grid is a type

Figure 2.11: Routing multiple pins, (a) regular grid with uniform lengths, and (b) Hanan grid.

of grid that efficiently solves the MRST problem. A Hanan grid is a grid formed by vertical and horizontal lines passing through a set of vertices, as shown in Fig. 2.11. Based on the Hanan theorem, a Hanan grid is guaranteed to contain an MRST that connects these vertices [67]. A uniform grid can therefore be reduced to a Hanan grid to minimize the search space of the available paths connecting a set of terminals [46].

### 2.5 Summary