# **Power Delivery in High Current 3-D Systems**

by

Kan Xu

Submitted in Partial Fulfillment

of the

Requirements for the Degree

Doctor of Philosophy

Supervised by

Professor Eby G. Friedman

Department of Electrical and Computer Engineering

Arts, Sciences and Engineering

Edmund A. Hajim School of Engineering and Applied Sciences

University of Rochester

Rochester, New York

2020

# Dedication

This work is dedicated to my parents, Jianping Guo and Huisheng Xu.

# Table of Contents

|                                                               |          |

|---------------------------------------------------------------|----------|

| Biographical Sketch                                           | ix       |

| Acknowledgments                                               | xii      |

| Abstract                                                      | xv       |

| Contributors and Funding Sources                              | xvii     |

| List of Tables                                                | xviii    |

| List of Figures                                               | xx       |

| <b>1 Introduction</b>                                         | <b>1</b> |

| 1.1 Industrial revolutions and computer systems . . . . .     | 3        |

| 1.2 Power delivery network within a computer system . . . . . | 7        |

| 1.3 Outline . . . . .                                         | 13       |

|                                                                          |           |

|--------------------------------------------------------------------------|-----------|

| <b>2 Power Delivery Networks in High Performance 2-D and 3-D Systems</b> | <b>21</b> |

| 2.1 Power delivery network for high performance processors . . . . .     | 24        |

| 2.1.1 On-chip power noise . . . . .                                      | 24        |

| 2.1.2 Breakdown of on-chip multilayer power delivery networks . .        | 27        |

| 2.1.3 Modeling and efficient simulation of power grid . . . . .          | 34        |

| 2.2 Power delivery networks for 2.5-D and 3-D systems . . . . .          | 39        |

| 2.2.1 2.5-D power delivery network . . . . .                             | 42        |

| 2.2.2 3-D power delivery network . . . . .                               | 44        |

| 2.2.3 Power and ground TSV . . . . .                                     | 47        |

| 2.3 Summary . . . . .                                                    | 53        |

| <b>3 Challenges in High Current 2-D and 3-D systems</b>                  | <b>56</b> |

| 3.1 High current challenges at the PCB and package levels . . . . .      | 61        |

| 3.1.1 “Last inch” power loss . . . . .                                   | 63        |

| 3.1.2 Electromigration challenges . . . . .                              | 66        |

| 3.1.3 Advanced cooling systems . . . . .                                 | 70        |

| 3.2 High current challenges of on-chip 2-D and 3-D power networks . .    | 72        |

| 3.3 Summary . . . . .                                                    | 74        |

| <b>4 Power Noise in Advanced FinFET Technology Nodes</b>                 | <b>76</b> |

|          |                                                              |            |

|----------|--------------------------------------------------------------|------------|

| 4.1      | Standard cell-based power network . . . . .                  | 79         |

| 4.1.1    | Hierarchy of power grids . . . . .                           | 81         |

| 4.1.2    | Standard cell based power rails . . . . .                    | 82         |

| 4.2      | Circuit model . . . . .                                      | 83         |

| 4.2.1    | Load model . . . . .                                         | 84         |

| 4.2.2    | Rail model . . . . .                                         | 86         |

| 4.2.3    | Striping of power rail . . . . .                             | 87         |

| 4.3      | Characterization of power noise . . . . .                    | 89         |

| 4.3.1    | Power noise components . . . . .                             | 90         |

| 4.3.2    | Different technology nodes . . . . .                         | 94         |

| 4.4      | Power noise suppression . . . . .                            | 96         |

| 4.4.1    | Additional global power metal layers . . . . .               | 96         |

| 4.4.2    | Stripes technique . . . . .                                  | 98         |

| 4.4.3    | Graphene interconnects . . . . .                             | 99         |

| 4.4.4    | Scaling of local power rails . . . . .                       | 101        |

| 4.4.5    | Metalization schemes for advanced technology nodes . . . . . | 103        |

| 4.5      | Summary . . . . .                                            | 104        |

| <b>5</b> | <b>EMI Challenge in 2.5-D System with High Voltage VRs</b>   | <b>106</b> |

| 5.1      | LLC resonant converter . . . . .                             | 109        |

| 5.1.1    | Sinusoidal current generation . . . . .                      | 109        |

|          |                                                                        |            |

|----------|------------------------------------------------------------------------|------------|

| 5.1.2    | Operation of the LLC resonant converter . . . . .                      | 112        |

| 5.1.3    | Performance evaluation . . . . .                                       | 113        |

| 5.2      | Performance degradation due to high step down ratio . . . . .          | 116        |

| 5.3      | LLC resonant converter with distributed topology . . . . .             | 119        |

| 5.4      | Near field EMI in SiP environment . . . . .                            | 124        |

| 5.4.1    | EMI background . . . . .                                               | 125        |

| 5.4.2    | EMI evaluation setup in SiP environment . . . . .                      | 126        |

| 5.4.3    | Simulation results and analysis . . . . .                              | 129        |

| 5.5      | Summary . . . . .                                                      | 134        |

| <b>6</b> | <b>Power Noise and EMI in VR Top and Bottom Placements</b>             | <b>135</b> |

| 6.1      | Top and bottom placement . . . . .                                     | 138        |

| 6.2      | Package design specifications . . . . .                                | 141        |

| 6.3      | EMI and power noise evaluation . . . . .                               | 144        |

| 6.4      | Package layer comparison . . . . .                                     | 152        |

| 6.5      | Summary . . . . .                                                      | 155        |

| <b>7</b> | <b>Insertion Loss Due to Placement of Multiple Waveguide Crossings</b> | <b>157</b> |

| 7.1      | Previous Work . . . . .                                                | 161        |

| 7.2      | Placement of multiple waveguide crossings . . . . .                    | 163        |

| 7.2.1    | Example one . . . . .                                                  | 164        |

|          |                                                                             |            |

|----------|-----------------------------------------------------------------------------|------------|

| 7.2.2    | Example two                                                                 | 166        |

| 7.2.3    | Example three                                                               | 169        |

| 7.3      | Discussion                                                                  | 170        |

| 7.4      | Case Study of an 8 x 8 GWOR ONoC Router                                     | 173        |

| 7.5      | Summary                                                                     | 176        |

| <b>8</b> | <b>Design Guidelines for RDL-Based Power Networks</b>                       | <b>177</b> |

| 8.1      | Background and previous work                                                | 181        |

| 8.2      | RDL with different 3-D manufacturing methods                                | 184        |

| 8.2.1    | RDL within different TSV fabrication processes                              | 184        |

| 8.2.2    | RDL with different 3-D stacking topologies                                  | 192        |

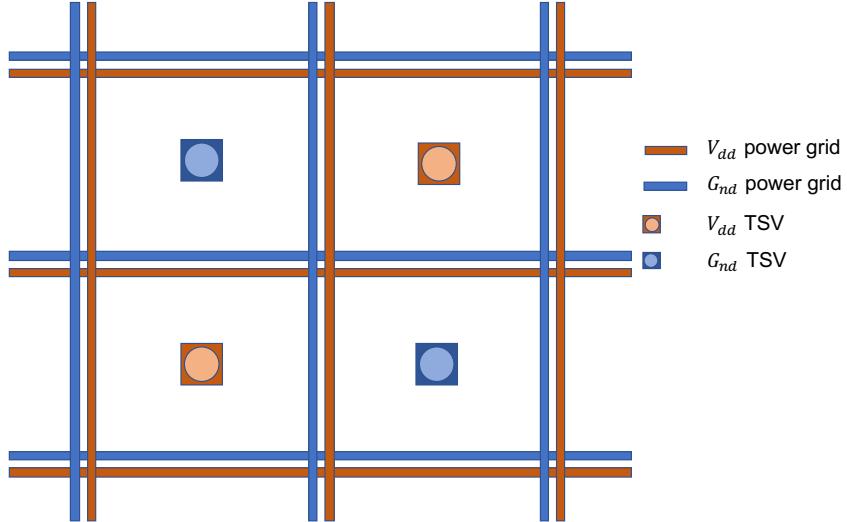

| 8.3      | Grid-Based RDL in 3-D ICs                                                   | 199        |

| 8.3.1    | Grid-based P/G RDL model                                                    | 200        |

| 8.3.2    | Comparison between grid-based RDL and P2P RDL                               | 204        |

| 8.4      | Summary                                                                     | 211        |

| <b>9</b> | <b>Parasitic Impedance Aware Power Delivery for Voltage Stacked Systems</b> | <b>213</b> |

| 9.1      | Background and previous work                                                | 215        |

| 9.1.1    | Challenges of load imbalances in voltage stacked systems                    | 216        |

| 9.1.2    | Existing work on mitigating load imbalances                                 | 223        |

|           |                                                                                                     |            |

|-----------|-----------------------------------------------------------------------------------------------------|------------|

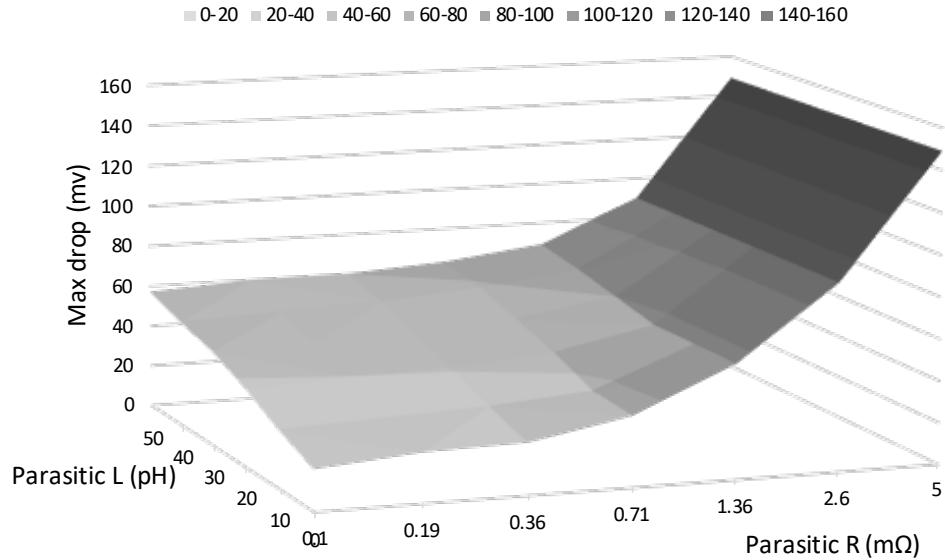

| 9.2       | Performance degradation due to parasitic impedances . . . . .                                       | 225        |

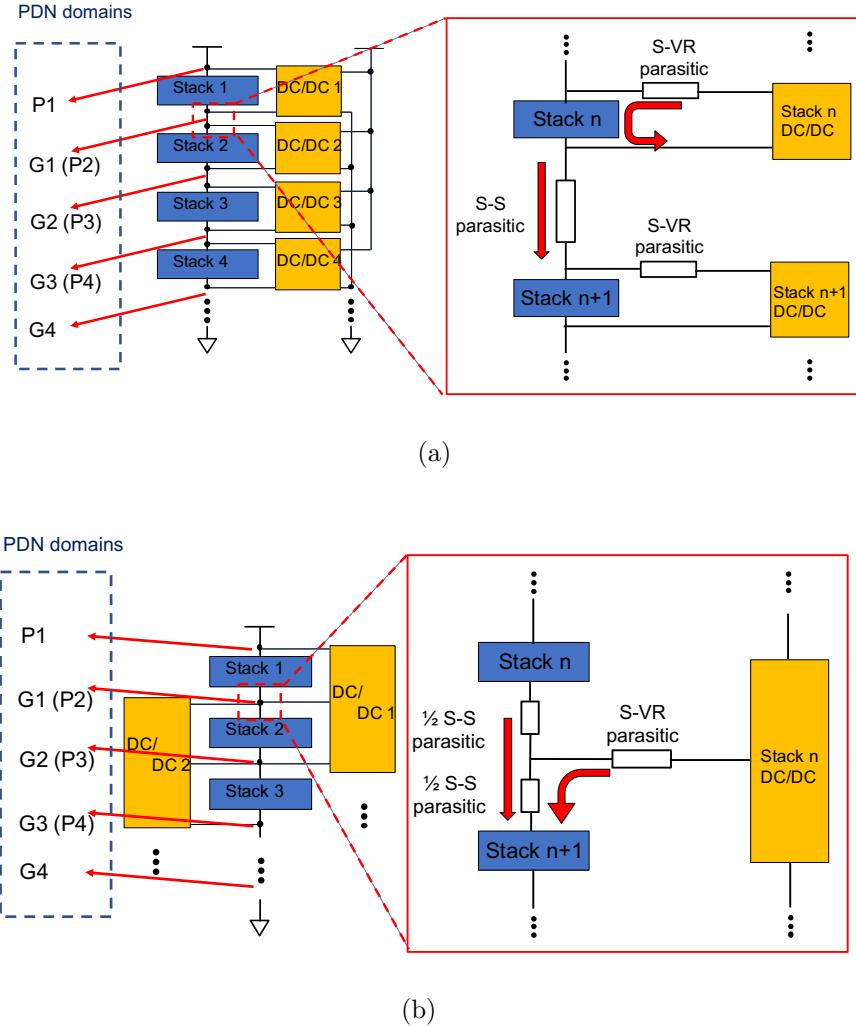

| 9.3       | Power delivery network of voltage stacked differential power processing systems . . . . .           | 229        |

| 9.3.1     | Power delivery network of voltage stacked systems . . . . .                                         | 230        |

| 9.3.2     | Power delivery network for DPP systems . . . . .                                                    | 235        |

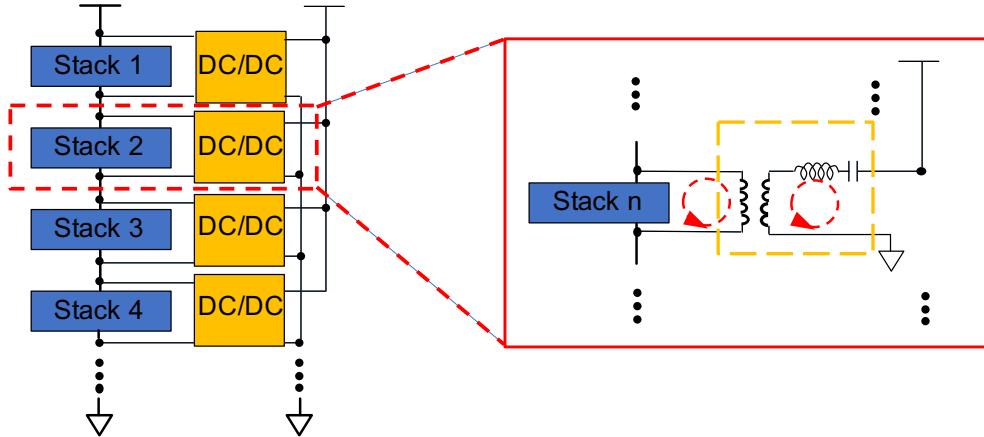

| 9.3.3     | Resonant converter-based stack-to-bus topology . . . . .                                            | 240        |

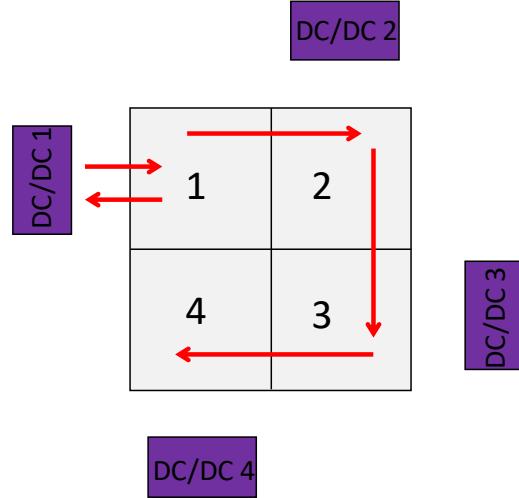

| 9.4       | Tile-based power delivery network for voltage stacked systems . . . . .                             | 243        |

| 9.5       | Summary . . . . .                                                                                   | 250        |

| <b>10</b> | <b>Conclusions</b>                                                                                  | <b>251</b> |

| <b>11</b> | <b>Future Work</b>                                                                                  | <b>256</b> |

| 11.1      | Comparison between stack-to-bus and stack-to-stack topologies for voltage stacked systems . . . . . | 257        |

| 11.2      | Combination of voltage stacking within 3-D ICs . . . . .                                            | 262        |

|           | <b>Bibliography</b>                                                                                 | <b>267</b> |

# Biographical Sketch

Kan Xu was born in Anyang, Henan Province, China. He received the Bachelor of Science degree in electrical engineering from North China University of Water Resources and Electric Power, Zhengzhou, China, 2012, and the Master of Science degree in electrical and computer engineering from the University of Rochester, Rochester, New York, in 2015. He interned with the Power Integrity Team at Google Inc., Mountain View, California in 2019. He is currently completing the Ph.D. degree in electrical engineering from the University of Rochester, Rochester, New York, under the supervision of Prof. Eby G. Friedman. His current research interests include on-chip and package level power delivery networks for high current HPC systems, voltage stacking for high power VLSI systems, 3-D integration, and optical waveguides.

The following publications are a result of work conducted during his doctoral study.

## **Journal papers**

1. K. Xu, B. Vaisband, G. Sizikov, X. Li and E. G. Friedman, “EMI Suppression

With Distributed LLC Resonant Converter for High-Voltage VR-on-Package,” *IEEE Transactions on Components, Packaging and Manufacturing Technology*, pp. 263 - 271, February 2020.

2. R. Bairamkulov, K. Xu, M. Popovich, J. S. Ochoa, V. Srinivas and E. G. Friedman, “Power Delivery Exploration Methodology based on Constrained Optimization,” *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 39, No. 9, September 2020 (in press).

3. K. Xu, B. Vaisband, G. Sizikov, X. Li and E. G. Friedman, “Power Noise and Near-Field EMI of High-Current System-in-Package With VR Top and Bottom Placements,” *IEEE Transactions on Components, Packaging and Manufacturing Technology*, Vol. 9, No. 4, pp. 712 - 718, April 2019.

4. K. Xu, R. Patel, P. Raghavan and E. G. Friedman, “Exploratory Design of On-Chip Power Delivery for 14, 10, and 7 nm and Beyond FinFET ICs,” *Integration, the VLSI Journal*, Vol. 61, pp. 11 - 19, March 2018.

5. K. Xu and E. G. Friedman, “Insertion Loss Due to Placement of Multiple Waveguide Crossings,” (in submission).

6. K. Xu and E. G. Friedman, “Design Guidelines for RDL-Based Power Networks,” (in submission).

7. K. Xu and E. G. Friedman, “Parasitic Impedance of Power Delivery Networks within Voltage Stacked Systems,” (in submission).

### Conference papers

1. K. Xu, M. Popovich, G. Sizikov and E. G. Friedman, “Distributed Port Assignment for Extraction of Power Delivery Networks,” *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 1 - 5, October 2020.

2. K. Xu and E. G. Friedman, “Challenges in High Current On-Chip Voltage Stacked System,” *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 1 - 5, October 2020.

3. R. Bairamkulov, K. Xu, M. Popovich, J. S. Ochoa, V. Srinivas and E. G. Friedman, “Versatile Framework for Power Delivery Exploration,” *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 1 - 5, May 2018.

4. K. Xu, B. Vaisband, G. Sizikov, X. Li and E. G. Friedman, “Distributed Sinusoidal Resonant Converter with High Step-Down Ratio,” *Proceedings of the IEEE International Conference on Electrical Performance of Electronic Packaging and Systems*, pp. 1 - 3, October 2017.

5. R. Patel, K. Xu, E. G. Friedman and P. Raghavan, “Exploratory Power Noise Models of Standard Cell 14, 10, and 7 nm FinFET ICs,” *Proceedings of the ACM Great Lakes Symposium on VLSI*, pp. 233 - 238, May 2016.

# Acknowledgments

It has been an amazing journey for me, where a number of people have played significant roles in the completion of this dissertation. I thank everyone who has helped and supported me through my Ph.D. experience.

First and foremost, I would like to express my sincere gratitude to Professor Eby G. Friedman, my advisor, mentor, and guide through this challenging journey. I thank your technical supervision, and patient and individualized guidance, without which I would have struggled a lot more conducting research and completing my Ph.D. Through countless short but intelligent talks you gave, you taught me passion, stoicism, critical thinking, and how to approach problems, which not only has helped my research but will also benefit me for the rest of my life. I have learned so much from you that I'm lacking words to properly express my appreciation.

I first came to the University of Rochester as a masters student, not knowing what my plans were afterwards. But I'm the luckiest; you generously offered me the opportunity of this journey with guidance, which turns out has made me who I am,

what I value, and how I see this world. For that, I will forever appreciate what you have provided.

I would like to thank the members of my committee, Professor Engin Ipek, Professor Selcuk Kose, and Professor Yuhao Zhu, for your valuable feedback and suggestions throughout my Ph.D. research. I really appreciate your time and effort on my dissertation. I would also like to thank Professor Jianhui Zhong for serving as the chairperson in my defense committee.

I would like to express my gratitude to my external committee member, Dr. Mikhail Popovich, for providing the precious intern opportunity and supporting me during my Ph.D. work. Thank you for the fruitful conversations, and for guiding me through a more than wonderful intern experience. I can never emphasize enough how much my internship experience helped me in the transition to my next journey.

I thank the Department of Electrical and Computer Engineer at the University of Rochester for the countless help and support I received from the administrative and technical staff. With special thanks to the Graduate Administrator, Michele Foster, for providing precious suggestions to help me get through my first semester in Rochester.

Thank you to my dear members of the High Performance VLSI/IC Design and Analysis Laboratory: Inna, Ravi, Alex, Boris, Avi, Gleb, Rassul, Abdo, Tahereh, Nurzhan, and Ana, for the inspiration, guidance, support, comfort, and kind heart

I received from all of you. The enriching and enjoyable time we spent together will always be cherished. In addition, I thank RuthAnn Williams for the joy and laughter she constantly brings to our lab. Your interesting stories as well as refreshing perspectives always ease our daily routine of research.

I would like to thank my friends for always standing by my side throughout this journey. Whether it is to regularly check on me, weekend gateways together, backing me up during a tough moment, or a heartwarming phone call from the other side of the Pacific, you have supported me more than you think. It is a fortune to always have all of you in my life. An incomplete list: Bo Shi, BWB, CC, Fan Zi, Feng, Gen Duo, Jia Yi, Ju Xiong, and Piao Ge. Special thanks to my girlfriend VK for being my No. 1 fan girl and one of my biggest supports throughout this journey. You've taught me so much about myself and made me a better man.

Last but not least, I would like to thank my parents for your unconditional love, which makes the foundation for everything great that has ever happened to me. You will always be the sweet sweet harbor where I can find peace in a storm, and courage to continue my voyage. For that, I will forever be grateful.

# Abstract

Although CMOS scaling has slowed, the demand for greater performance and heterogeneous integration has yet to end. Greater performance generally leads to higher current demand in high performance computing (HPC) systems. Three-dimensional (3-D) integrated circuits are a natural platform for heterogeneous integration. A 3-D HPC system however suffers from challenging design issues in the power delivery systems due to high current demand and vertical integration.

The dissertation starts by addressing two primary challenges, power noise and electromigration, within high current on-chip power systems. An exploratory model of an on-chip power grid and several on-chip metalization schemes are proposed to mitigate power noise. It is observed that the effectiveness of different metalization schemes on suppressing power noise varies significantly among different advanced technology nodes. To further address the issue of electromigration, voltage stacking is exploited. Parasitic impedance-aware load balancing circuits are proposed to manage load variations across different layers.

Moreover, two critical parameters at the package and board levels, electromagnetic interference (EMI) and “last inch power loss,” in 2.5-D power systems are discussed. A novel resonant converter with a distributed topology is proposed to mitigate EMI. Two VR-on-package topologies, VR-top and -bottom, are described. The impedance characteristics, EMI, power noise, and power loss of these two VR-on-package topologies are compared.

To fully exploit the potential of 3-D HPC systems, current paths within 3-D integrated power systems are explored. A 3-D redistribution layer (RDL), affecting both the vertical and 2-D current paths, is introduced. The effects of through silicon via (TSV) manufacturing processes and stacking topologies on RDLs are presented. A novel grid-based RDL topology is also proposed to support high current 3-D power systems while exhibiting low power noise. The advantages of a grid-based RDL for a nonuniform TSV distribution are also discussed.

3-D HPC systems are an excellent candidate to achieve high performance as well as heterogeneity. Vertical current path-aware design methodologies are critical to support reliable, power efficient, and high current 3-D power systems. This dissertation provides insight and solutions regarding the challenges of high current 3-D power systems.

# Contributors and Funding Sources

This work was supervised by a dissertation committee consisting of Professor Eby G. Friedman (advisor), Professor Engin Ipek, and Professor Selcuk Kose of the Department of Electrical and Computer Engineering, Professor Yuhao Zhu of the Department of Computer Science, and Doctor Mikhail Popovich of Google Inc. All of the work described in this dissertation was completed independently by the student.

This research is supported in part by the National Science Foundation under Grant No. CCF-1716091, Singapore Ministry of Education under Grant No. MOE2019-T2-2-075, and by grants from Cisco Systems, Qualcomm, and Google.

# List of Tables

|     |                                                                                                       |     |

|-----|-------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Power density of HPC systems . . . . .                                                                | 71  |

| 5.1 | EMI characteristics of distributed LLC resonant converter with different number of branches . . . . . | 132 |

| 5.2 | Comparison of single branch LLC resonant converter and distributed LLC resonant converter . . . . .   | 133 |

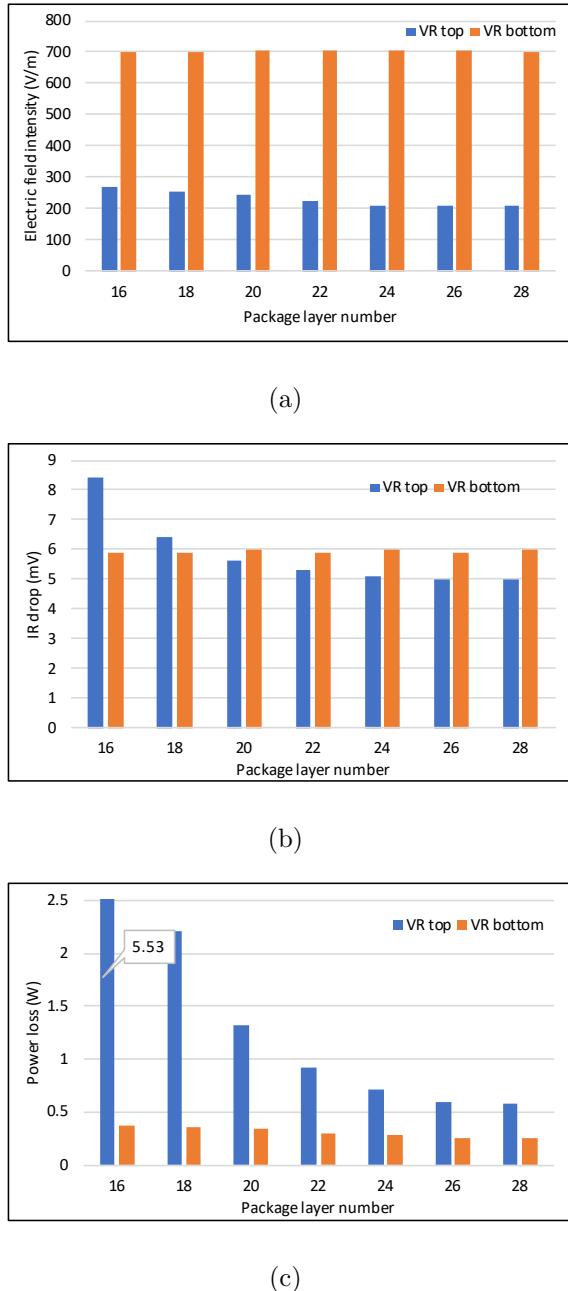

| 6.1 | Design specifications of packages supporting VR top and bottom placement topologies . . . . .         | 143 |

| 6.2 | IR drop and power loss of package in VR top and bottom placement topologies. . . . .                  | 149 |

| 6.3 | $L \ di/dt$ comparison between the VR top and bottom topologies. . . . .                              | 152 |

| 7.1 | Interconnect loss of different components in a silicon photonic system [202] . . . . .                | 160 |

| 7.2 | Comparison of 8 x 8 GWOR router. . . . .                                                              | 175 |

|     |                                                                                                                                           |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.1 | Comparison of different TSV fabrication methods. . . . .                                                                                  | 193 |

| 8.2 | Comparison of a face-to-back and back-to-face 3-D stacking topologies. . . . .                                                            | 193 |

| 8.3 | 2-D power grid specifications [33]. . . . .                                                                                               | 201 |

| 8.4 | P/G TSV specifications [227]. . . . .                                                                                                     | 202 |

| 8.5 | P/G RDL specifications [227]. . . . .                                                                                                     | 204 |

| 9.1 | Specifications of the load imbalance analysis process. . . . .                                                                            | 218 |

| 9.2 | Specifications of the on-chip power network [33]. . . . .                                                                                 | 233 |

| 9.3 | Specification of a resonant converter-based DPP system with a stack-to-bus topology. . . . .                                              | 241 |

| 9.4 | Simulation results of a stack-to-bus DPP system, which utilizes the tile-based power delivery system with ten layer power planes. . . . . | 249 |

# List of Figures

|     |                                                                                                                                                                             |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Power plants generate electricity which is delivered to customers over transmission and distribution power lines. . . . .                                                   | 4  |

| 1.2 | Evolution of computer systems from the first analog computer (Antikythera mechanism) to large scale data centers [4, 8, 12]. . . . .                                        | 5  |

| 1.3 | Power delivery network within a computer system. a) Cross sectional view, and b) top view of hierarchical power delivery network from VR to on-chip load [20, 21] . . . . . | 8  |

| 1.4 | A multi-layer interdigitated mesh structured on-chip power grid. The power and ground lines are, respectively, in orange and blue colors. . . . .                           | 11 |

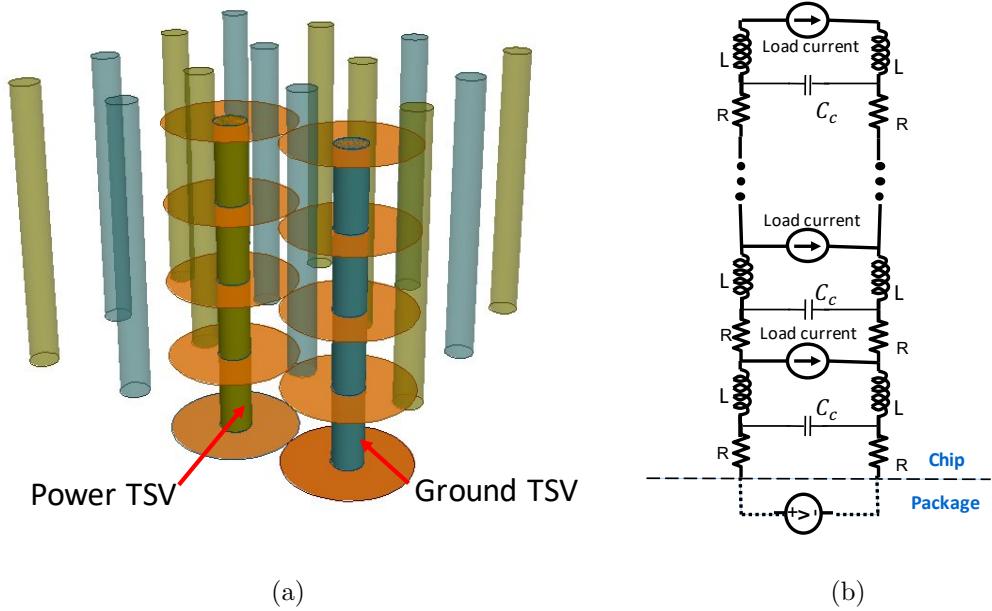

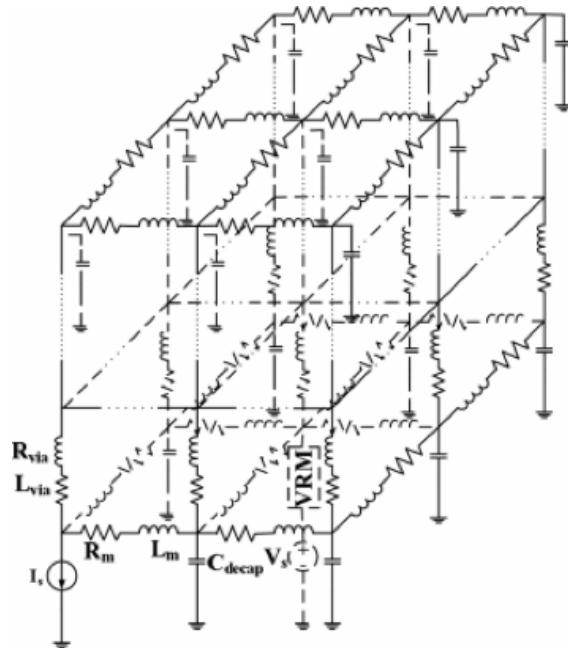

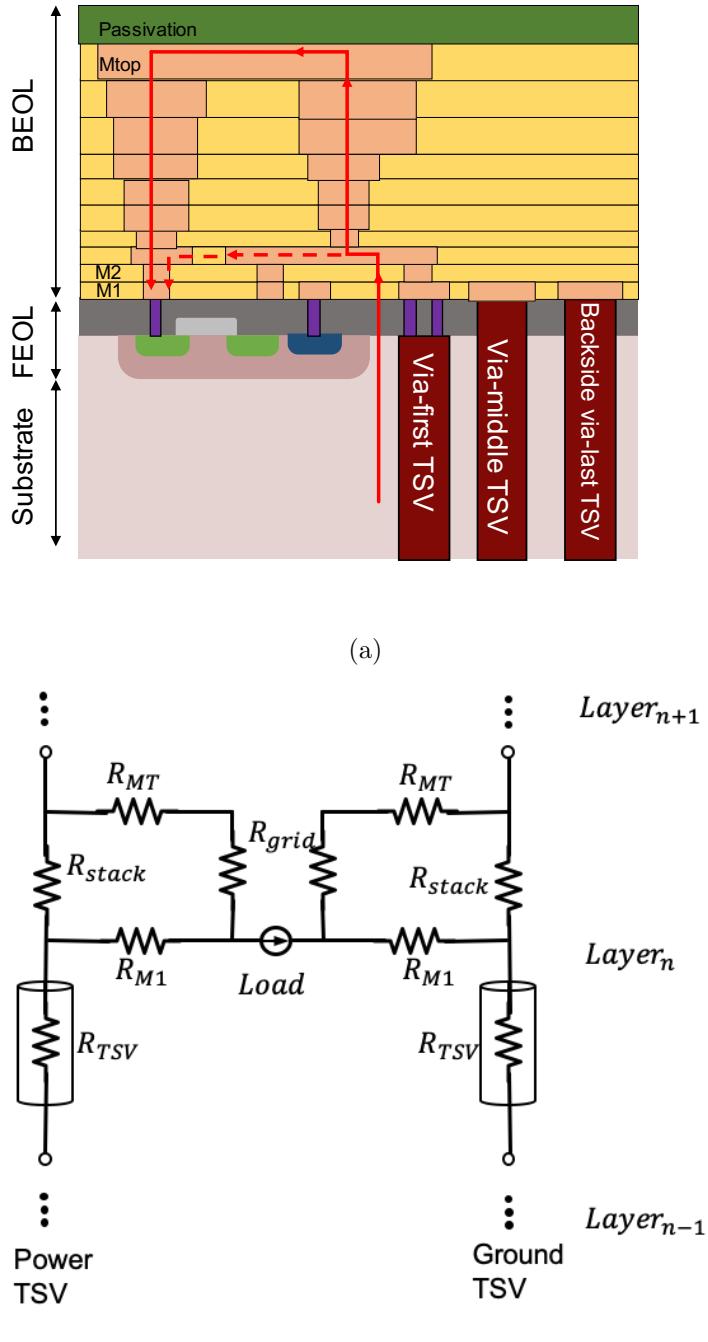

| 1.5 | Overview of 3-D power delivery network. a) Panoramic view of power/ground TSVs and 2-D power distribution cell within a 3-D IC, and b) related circuit model [25]. . . . .  | 12 |

|      |                                                                                                                                                                                                                                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

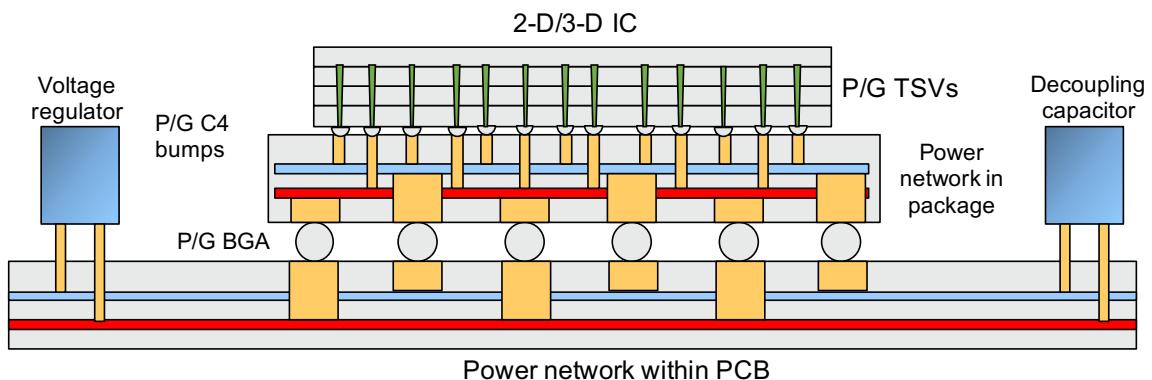

| 2.1  | Hierarchy of a power delivery network from the PCB to on-chip within a high performance computing system. . . . .                                                                                                                                 | 21 |

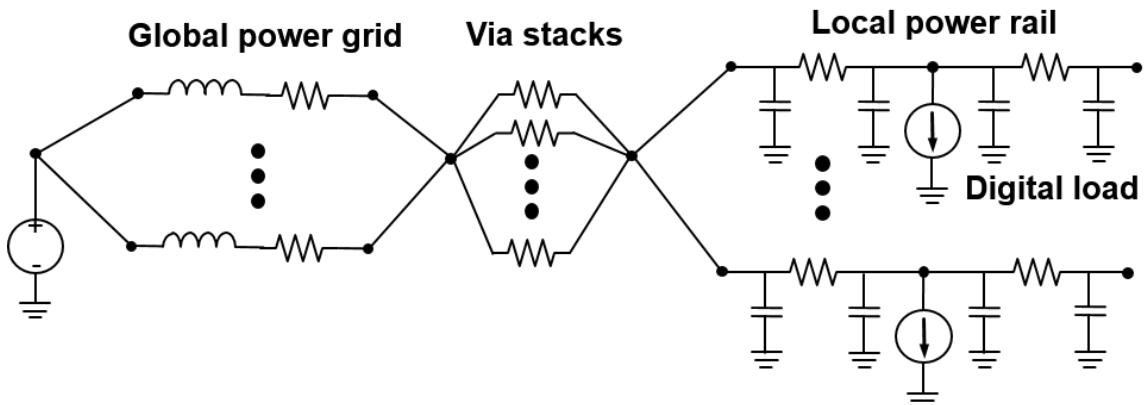

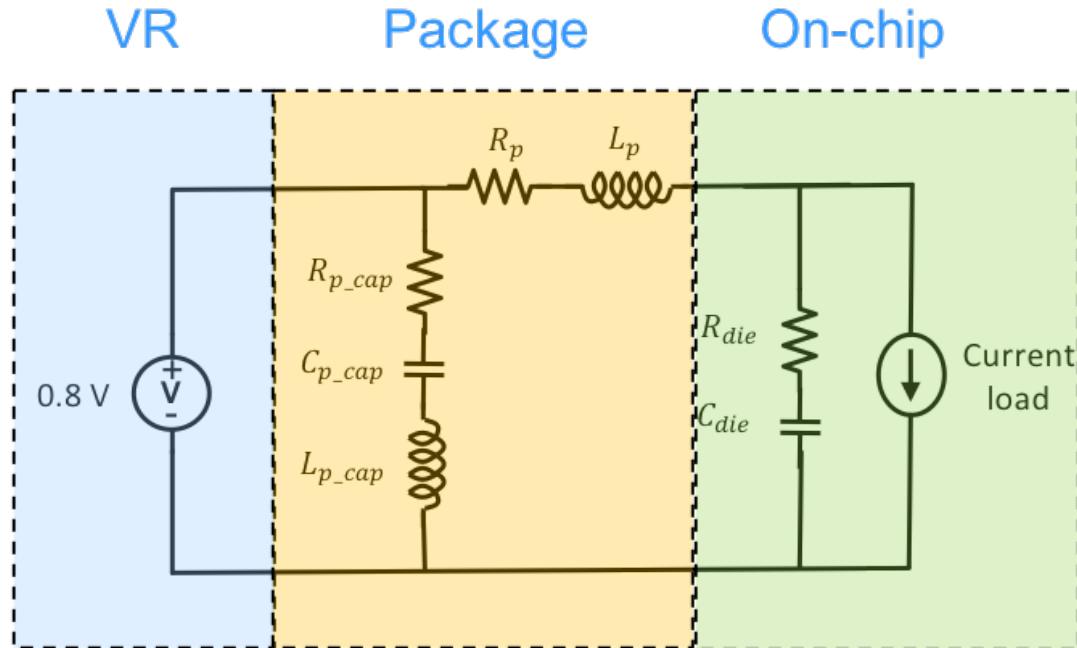

| 2.2  | Circuit model of a power delivery network from the PCB to on-chip. .                                                                                                                                                                              | 25 |

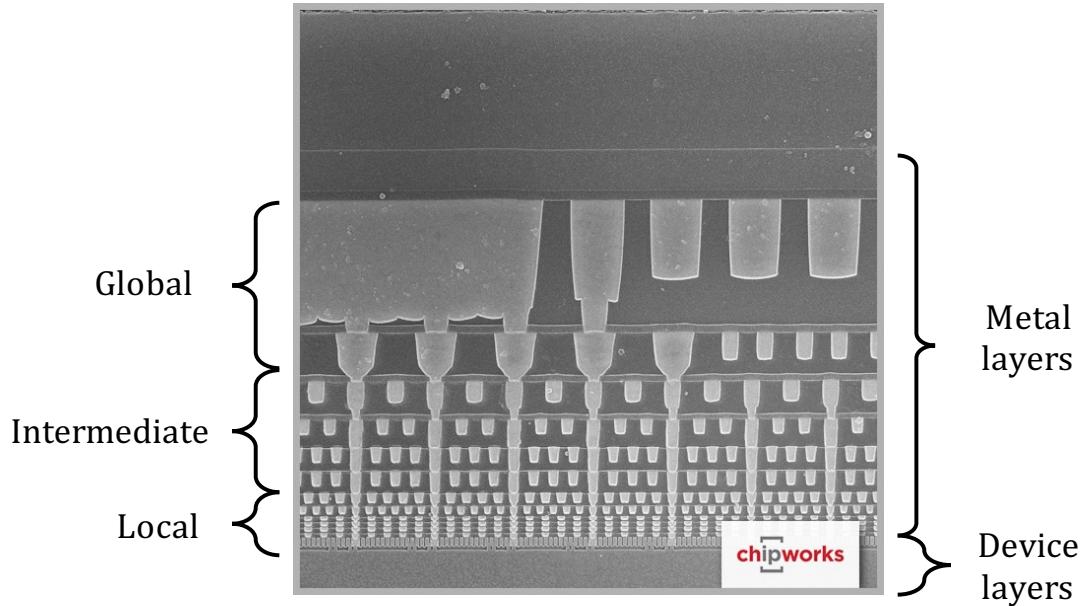

| 2.3  | 13 layer metalization stack in Intel 14 nm process [41]. . . . .                                                                                                                                                                                  | 28 |

| 2.4  | Global power grid with interdigitated power and ground metal line [43].                                                                                                                                                                           | 30 |

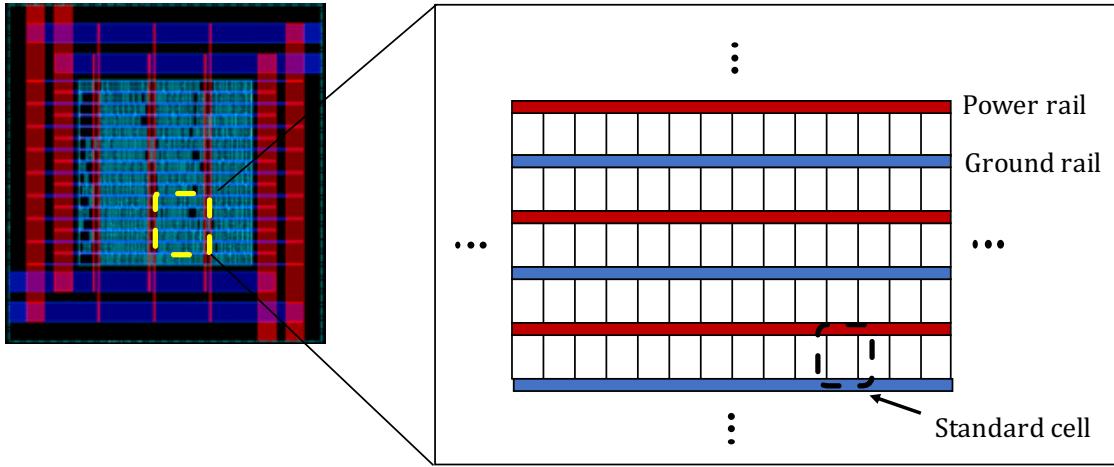

| 2.5  | Standard cell-based local power and ground rails [33]. . . . .                                                                                                                                                                                    | 31 |

| 2.6  | Structure of an on-chip multilayer power delivery network, including the hierarchy of the global power grid, local power rails, and via stacks:<br>a) planar view, and b) cross-sectional view. . . . .                                           | 33 |

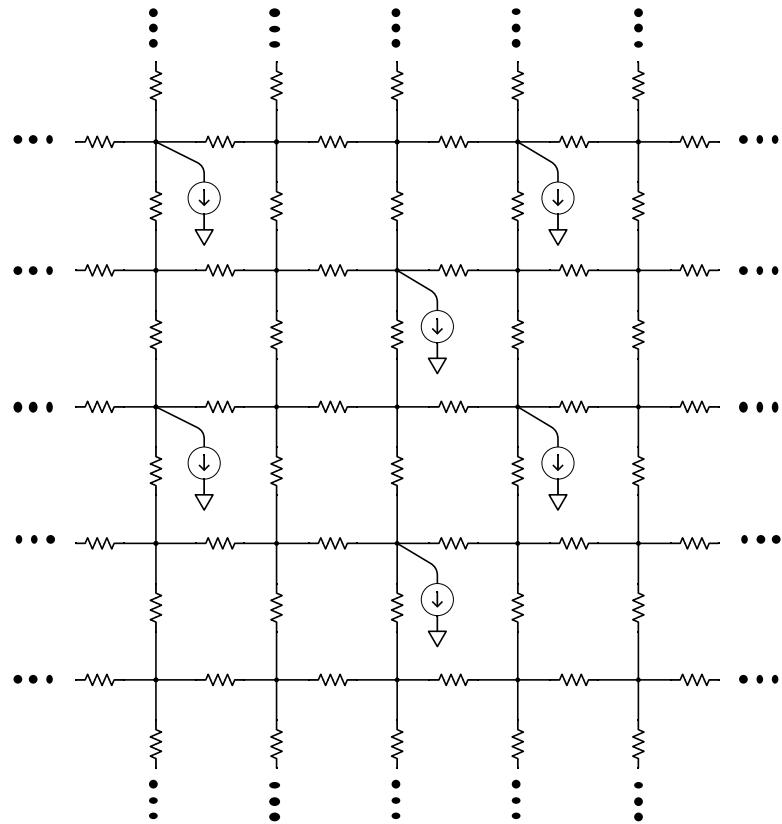

| 2.7  | Two-dimensional distributed model of a two-layer mesh structured power grid. . . . .                                                                                                                                                              | 36 |

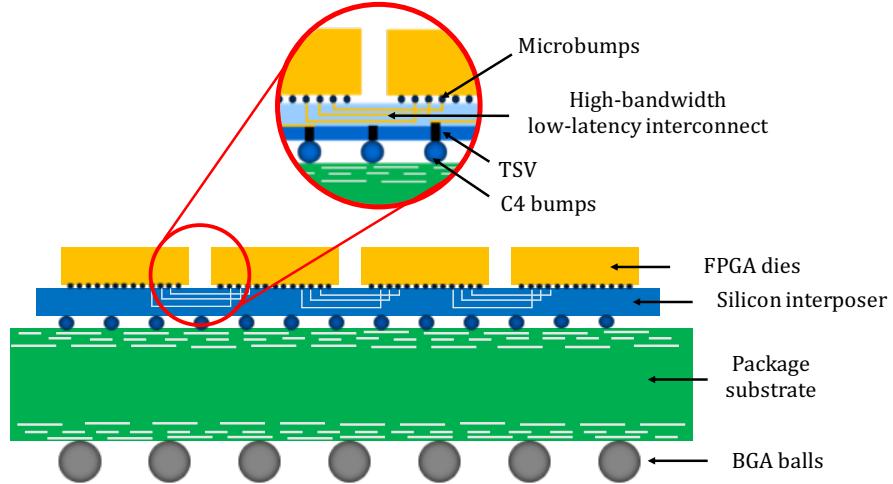

| 2.8  | Cross-sectional view of Xilinx 2.5-D FPGA [80]. . . . .                                                                                                                                                                                           | 42 |

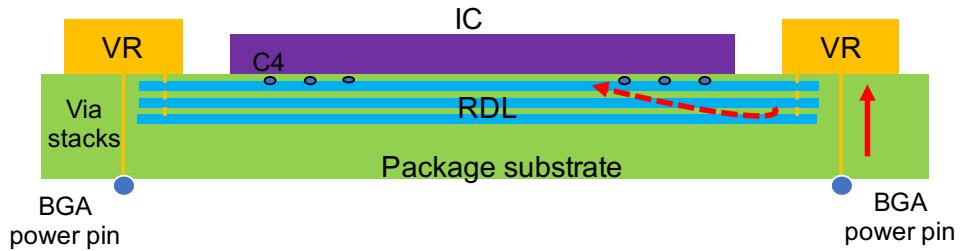

| 2.9  | Sectional view of VR-on-package with two PoL converters placed next to an IC. The solid and dashed arrows depict the current path, respectively, between the ball grid array (BGA) power pins and the VRs and between the VRs and the IC. . . . . | 43 |

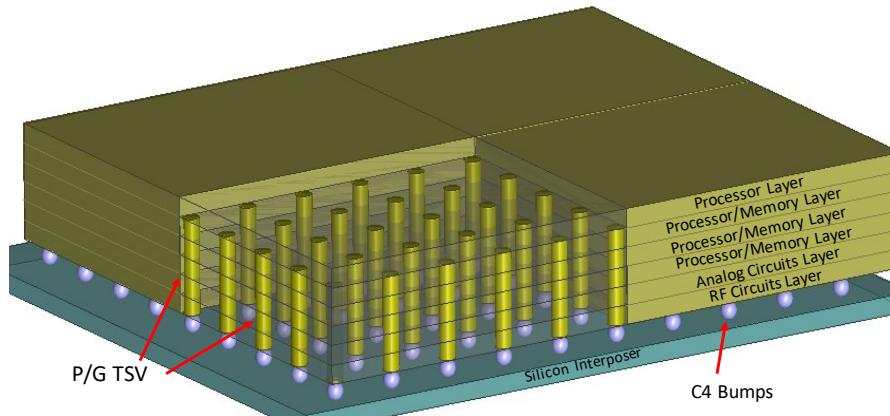

| 2.10 | TSV-based 3-D IC. . . . .                                                                                                                                                                                                                         | 45 |

| 2.11 | Distributed model of an N-layer power delivery network in a 3-D IC [83].                                                                                                                                                                          | 46 |

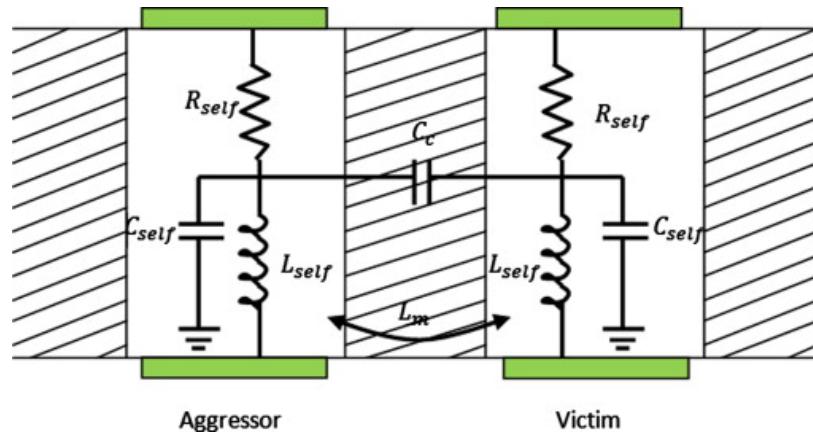

| 2.12 | Electrical parameters characterizing a cylinder shaped TSV [90]. . . .                                                                                                                                                                            | 47 |

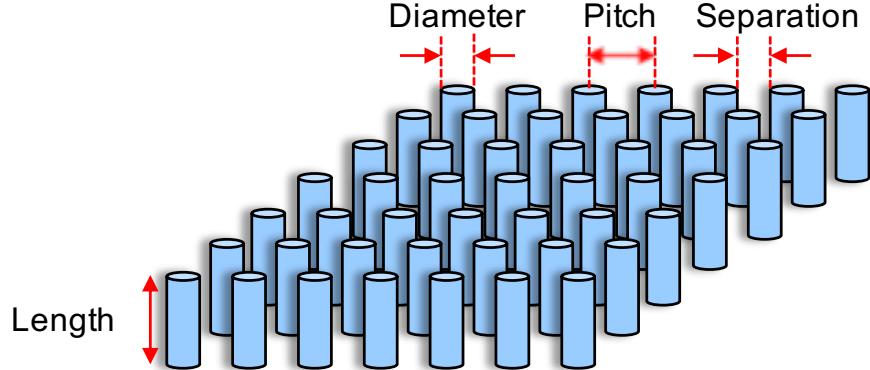

| 2.13 | Geometric parameters in array of P/G TSVs. . . . .                                                                                                                                                                                                | 50 |

|                                                                                                                                                                                  |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

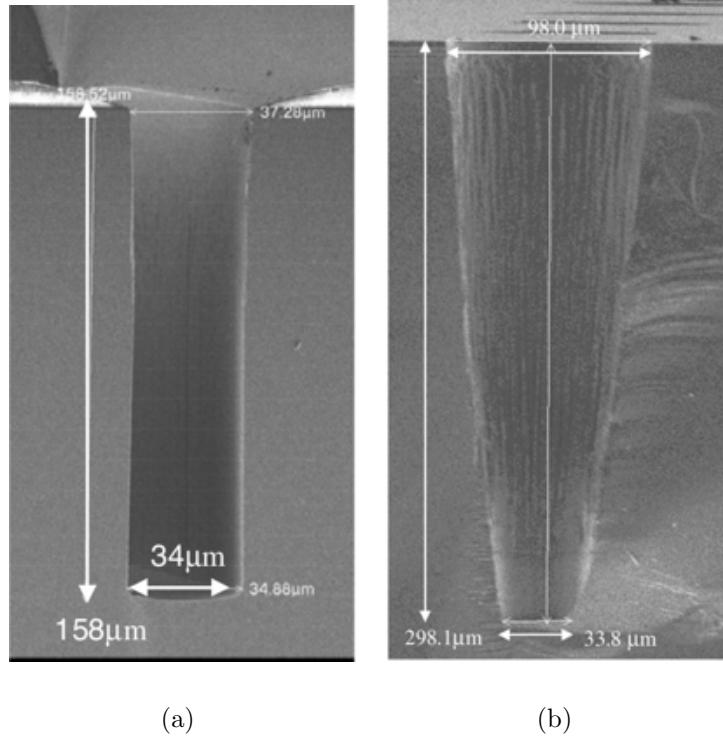

| 2.14 High resolution scanning electron microscope (SEM) images of the etching process of a TSV: a) straight etched TSV hole, and b) tapered etched TSV hole [98]. . . . .        | 52 |

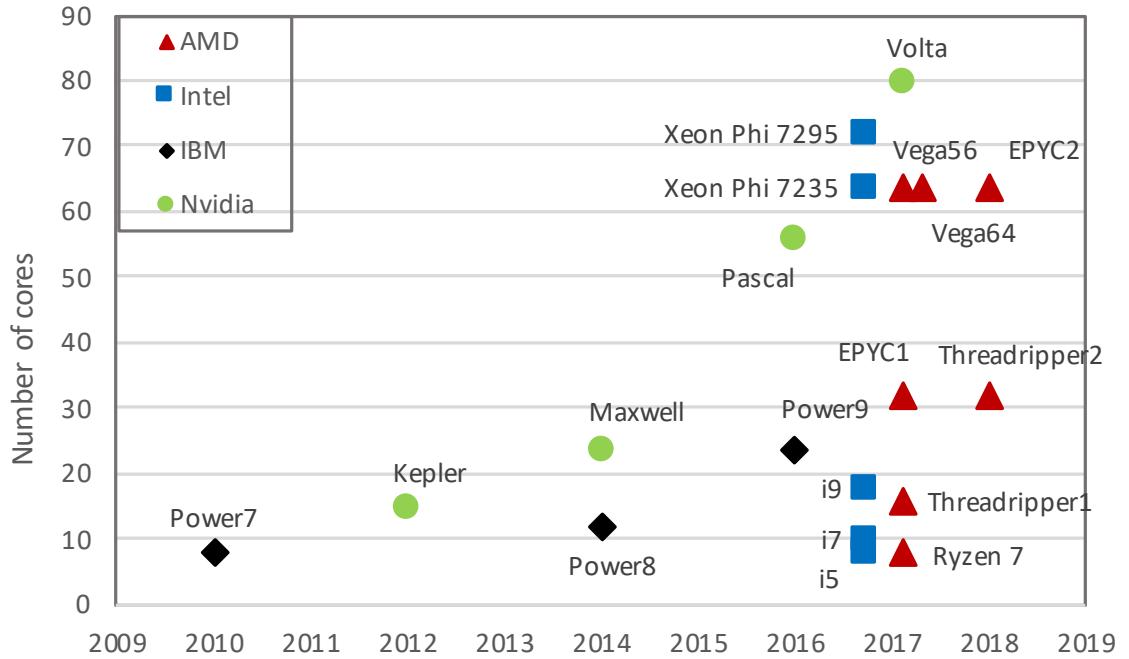

| 3.1 Number of cores in high performance ICs by AMD, Intel, Nvidia, and IBM, including high end desktop processors, server processors, and high end GPUs [21,82,101–115]. . . . . | 57 |

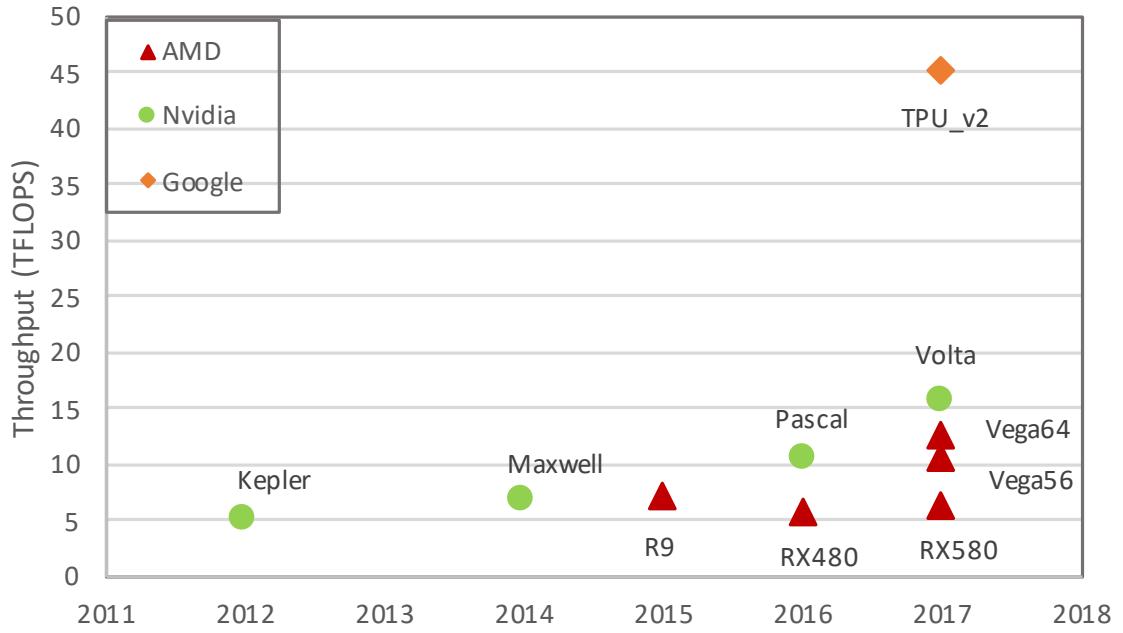

| 3.2 Throughput (in TFLOPS) of modern high end GPUs developed by AMD and Nvidia, and tensor processing units (TPUs) developed by Google [21,82,101–115]. . . . .                  | 58 |

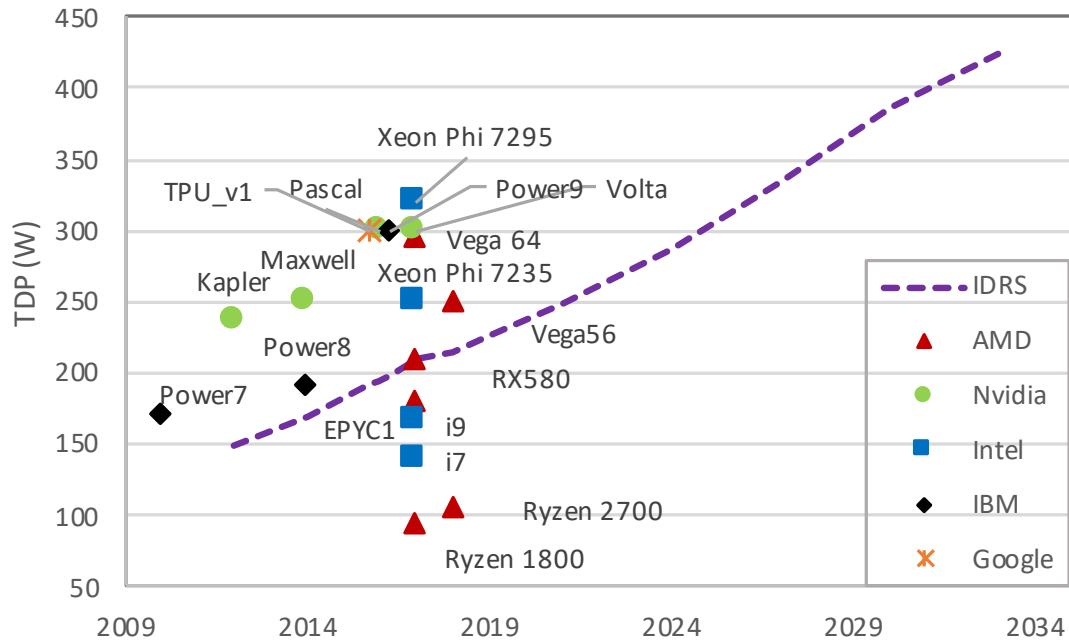

| 3.3 Power consumption of modern high performance processors developed by AMD, Nvidia, Intel, IBM, and Google [21,82,101–115]. . . . .                                            | 59 |

| 3.4 Resistive path (dashed line) between the VR and on-chip load across the board and package . . . . .                                                                          | 62 |

| 3.5 VR-on-package where the VR is moved from the PCB to the package. . . . .                                                                                                     | 64 |

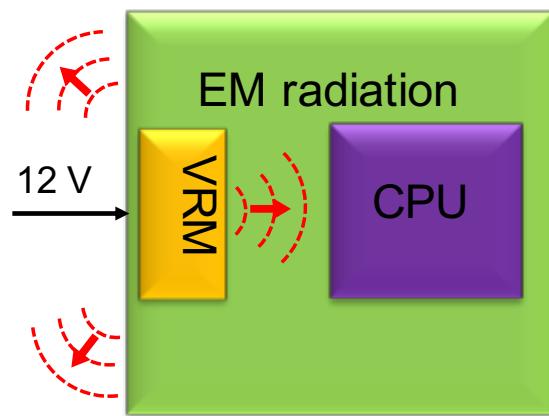

| 3.6 Radiated EMI pollutes the surrounding electromagnetic environment. . . . .                                                                                                   | 65 |

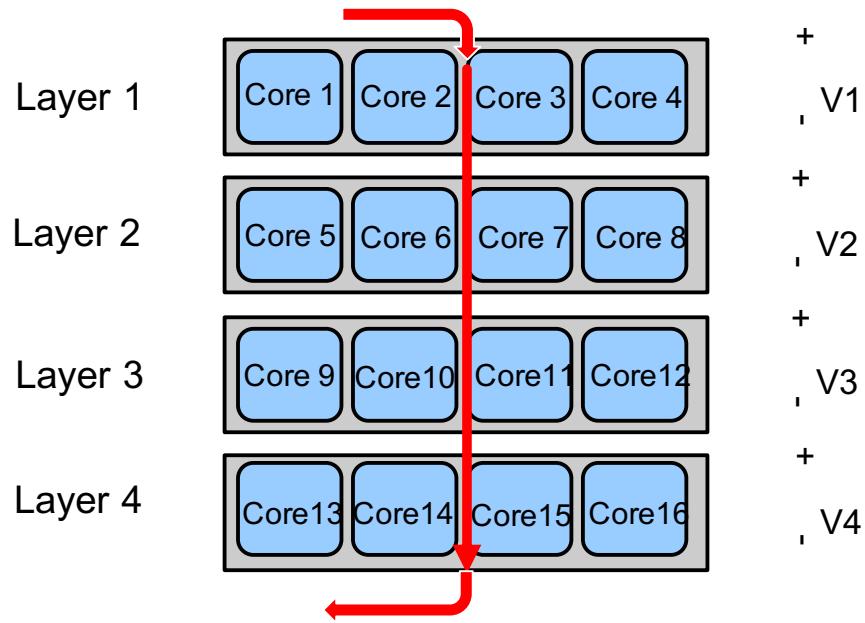

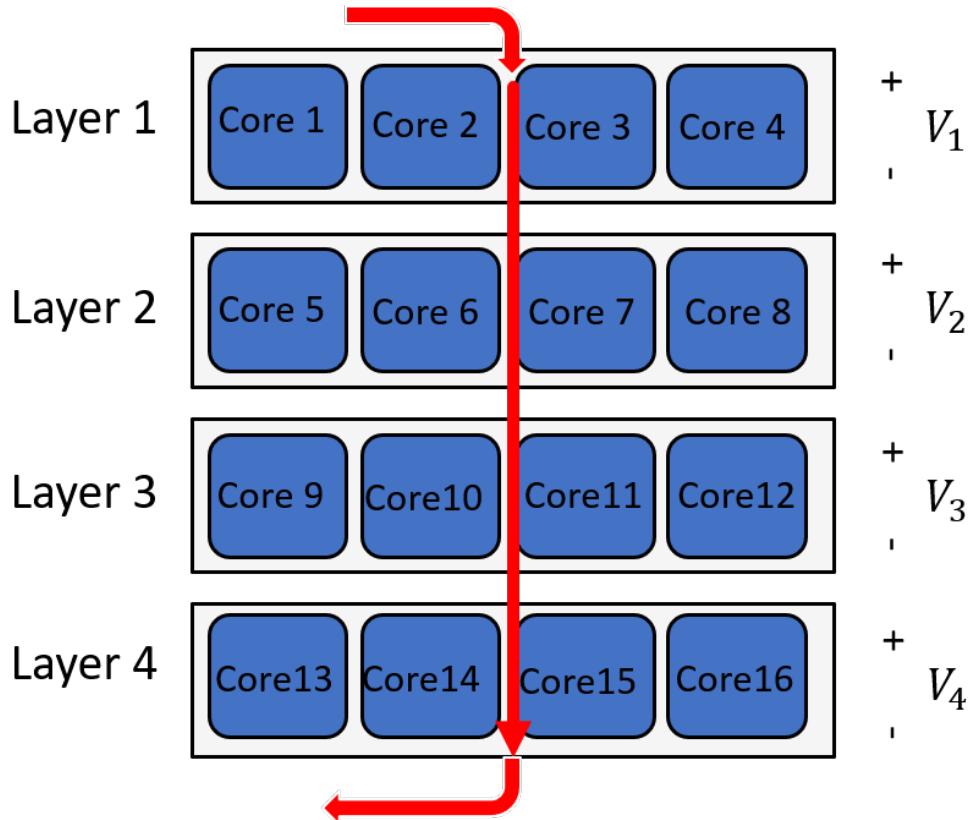

| 3.7 16 core, four layer voltage stacking system. . . . .                                                                                                                         | 68 |

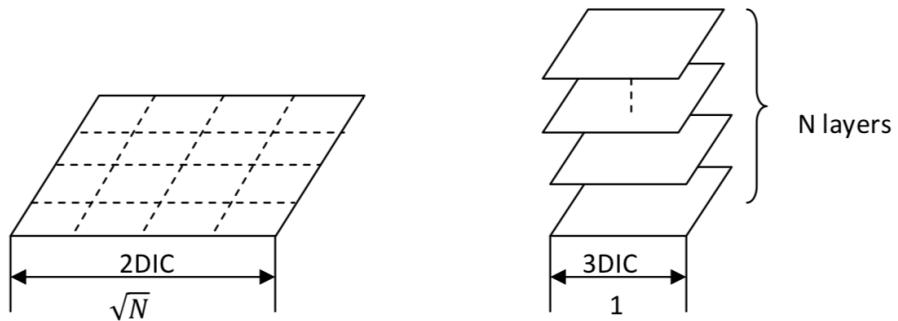

| 3.8 Area comparison of 2-D IC with 3-D IC [90]. . . . .                                                                                                                          | 73 |

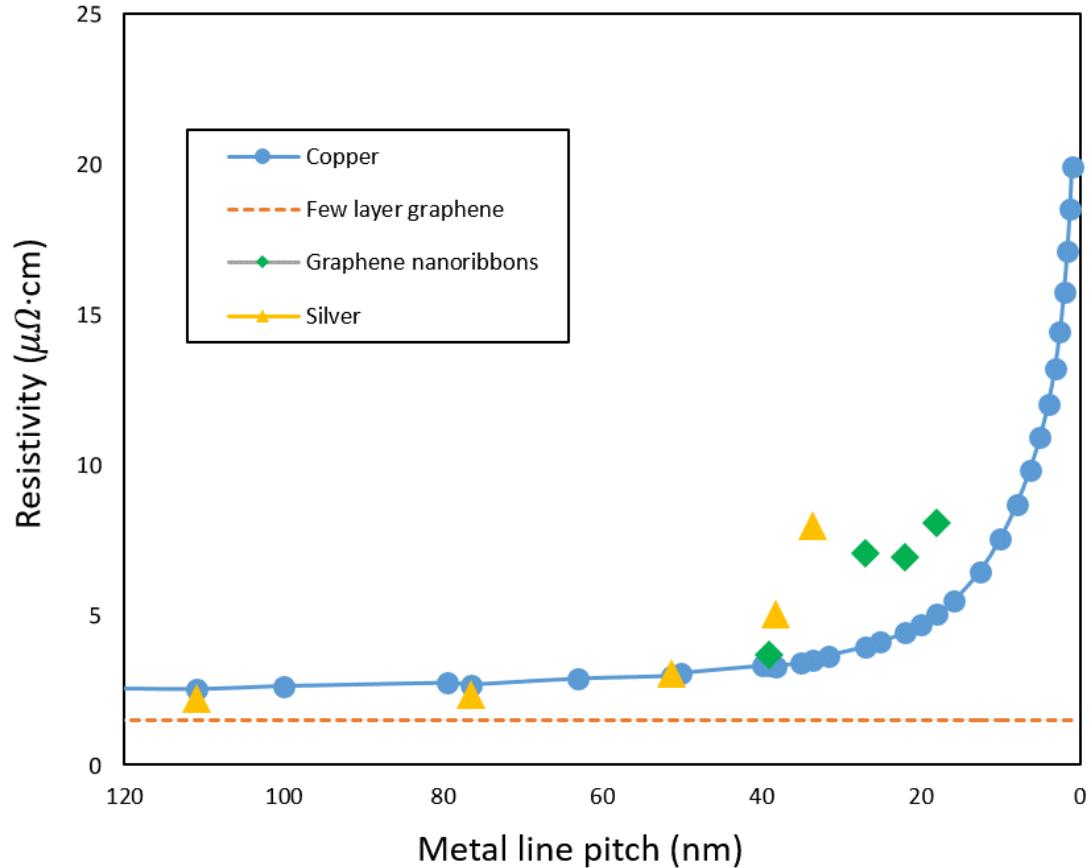

| 4.1 Interconnect resistivity of different materials versus line width. . . . .                                                                                                   | 77 |

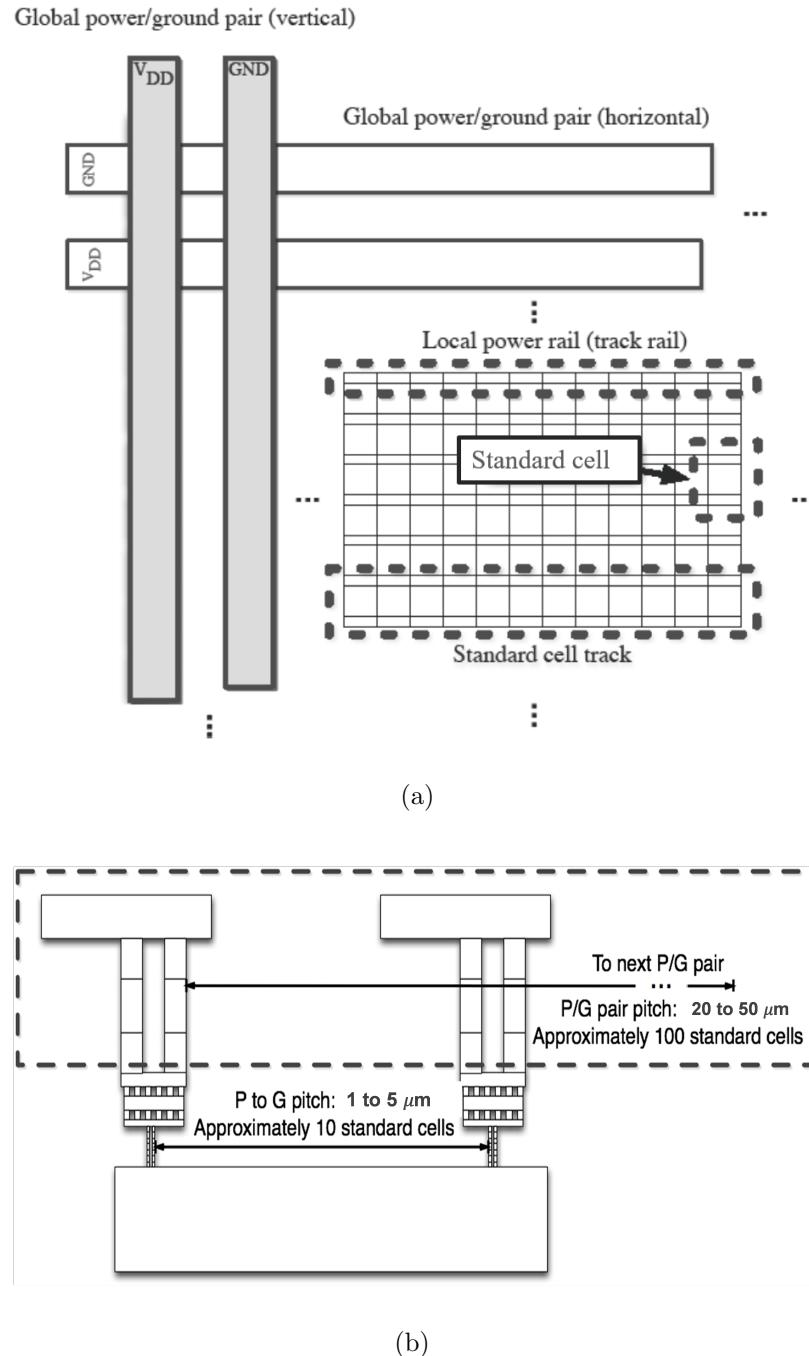

| 4.2 Topology of a standard cell based power network: a) planar view, b) profile view. . . . .                                                                                    | 80 |

|      |                                                                                                                                                                                                     |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.3  | Model of power network                                                                                                                                                                              | 84  |

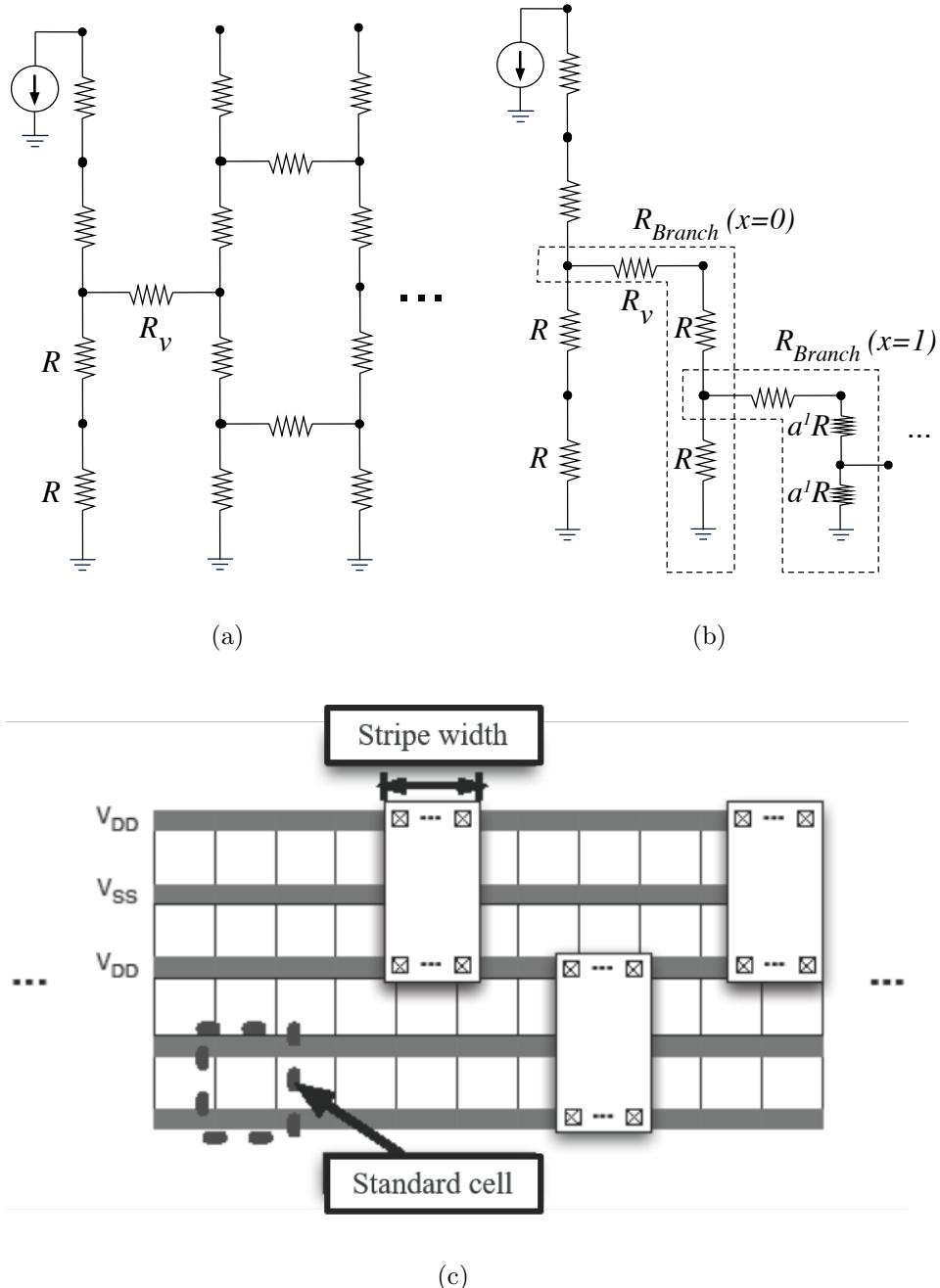

| 4.4  | Circuit models and physical structure of striping between the local power rails. a) comprehensive circuit model, b) $R_{branch}$ approximated circuit model, and c) physical structure of a stripe. | 88  |

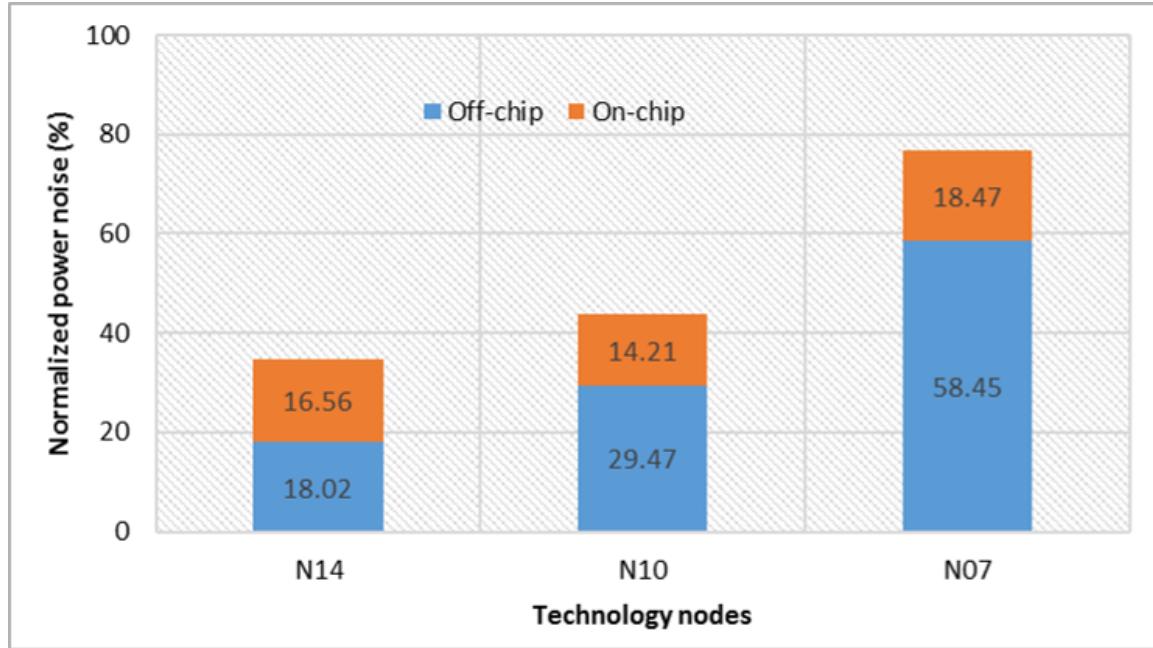

| 4.5  | Comparison between on-chip and off-chip power noise in 14, 10, and 10 nm technology nodes.                                                                                                          | 91  |

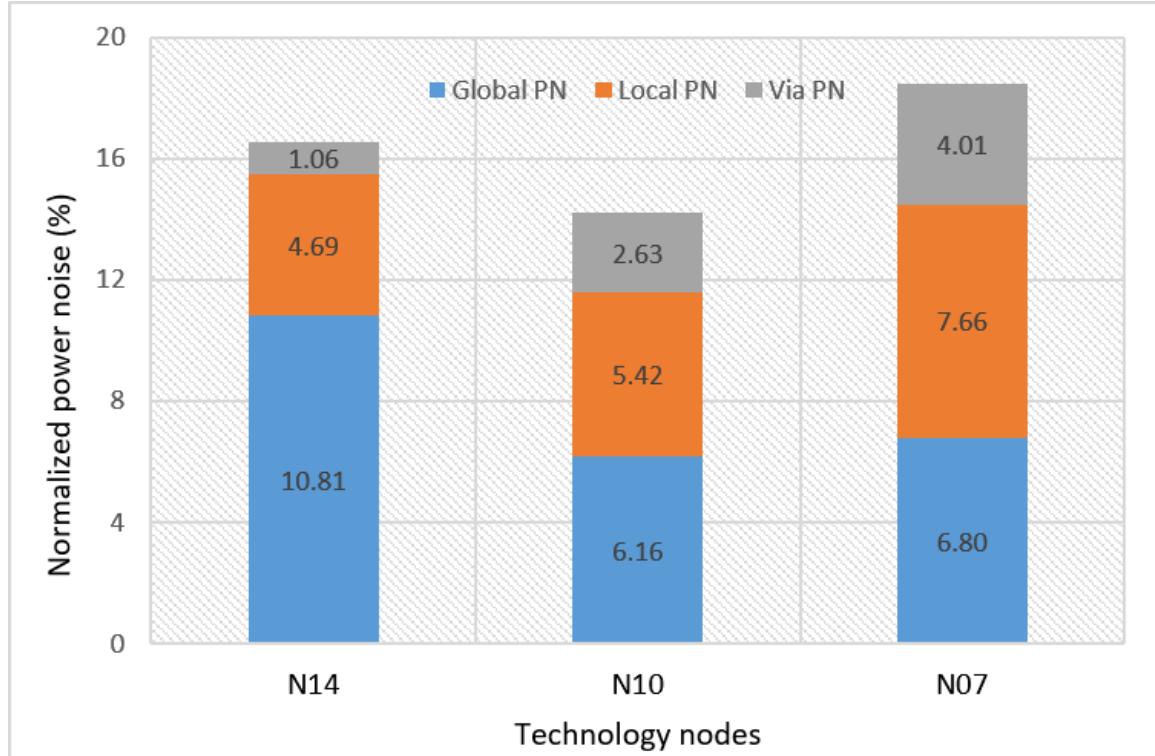

| 4.6  | Components of on-chip power noise in 14, 10, and 10 nm technology nodes.                                                                                                                            | 92  |

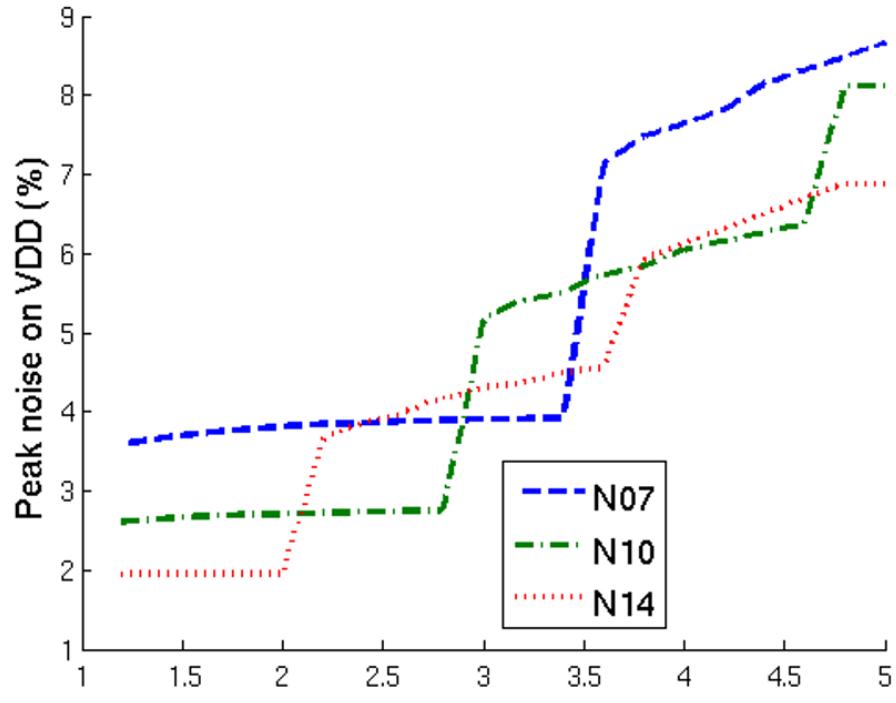

| 4.7  | Local peak power noise in 14 nm, 10 nm, and 7 nm technologies with increasing clock frequency.                                                                                                      | 93  |

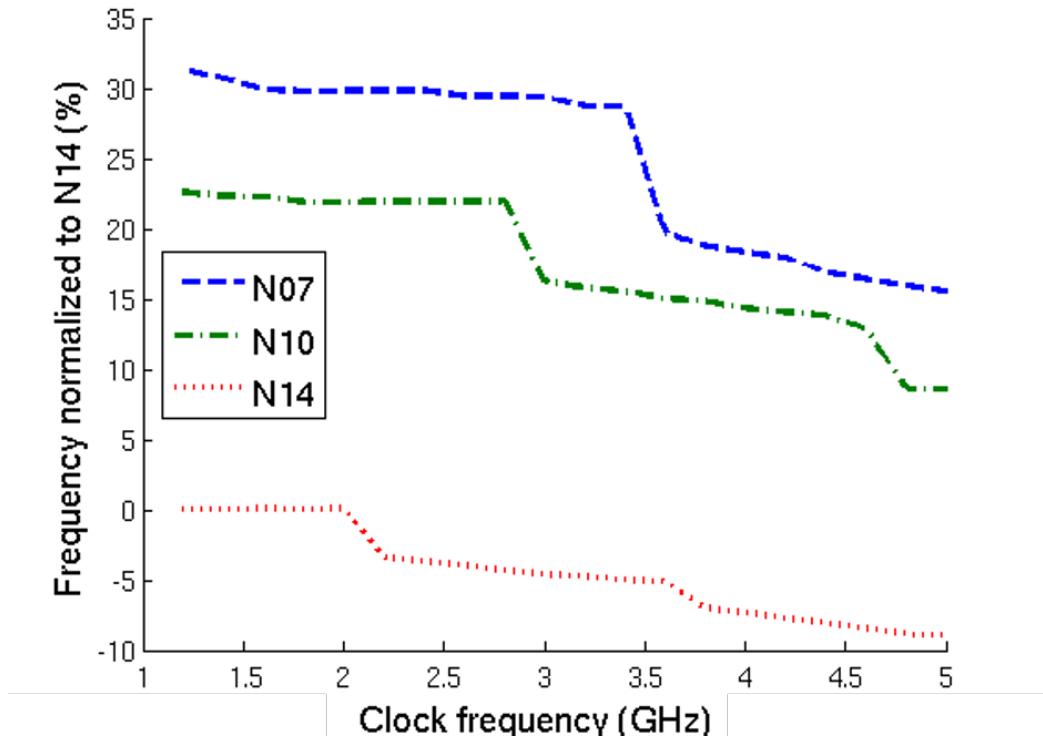

| 4.8  | Per cent decrease in performance of average power noise of a five stage ring oscillator in 14 nm, 10 nm, and 7 nm technologies normalized to an N14 ring oscillator.                                | 95  |

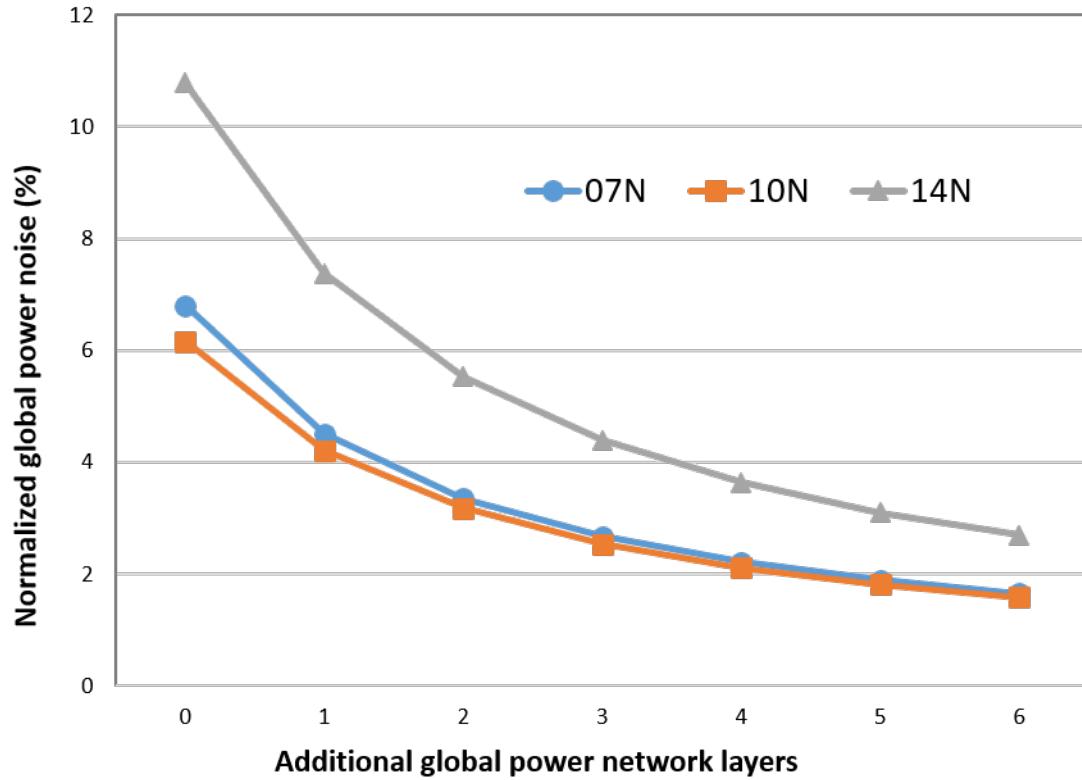

| 4.9  | Degradation in global power noise versus additional global power metal layers                                                                                                                       | 97  |

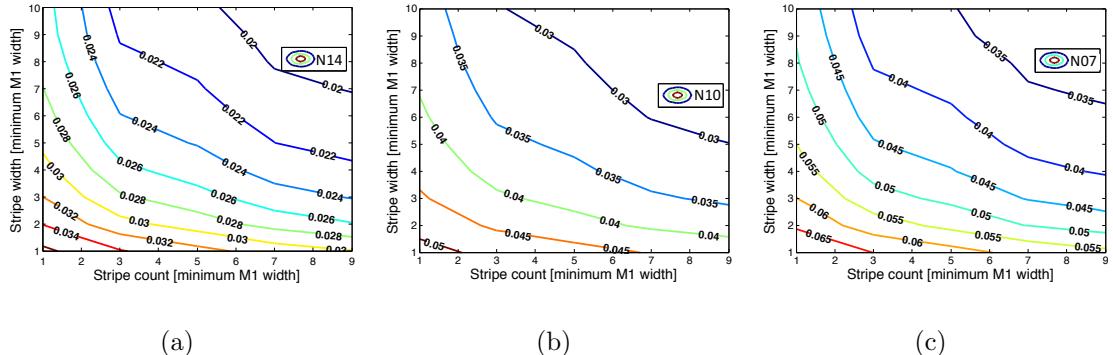

| 4.10 | Effect of track stripe count and stripe width on normalized power noise, a) 14 nm, b) 10 nm, and c) 7 nm technologies. A 3.6 GHz frequency is assumed.                                              | 98  |

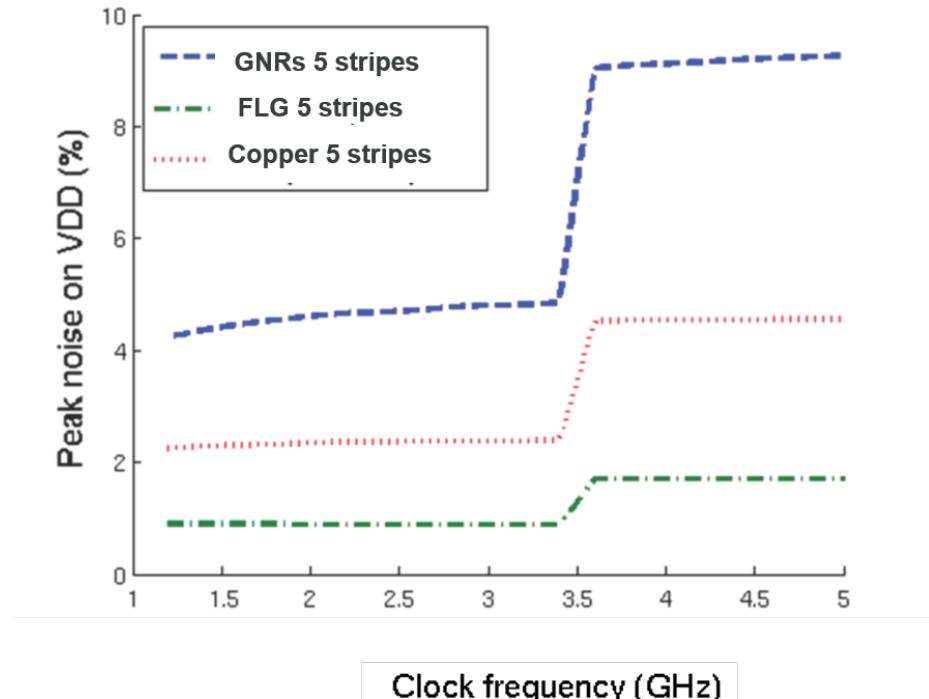

| 4.11 | Peak power noise in GNRs, FLG, and copper power grids with increasing clock frequencies in 7 nm technology.                                                                                         | 100 |

|                                                                                                                                                    |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

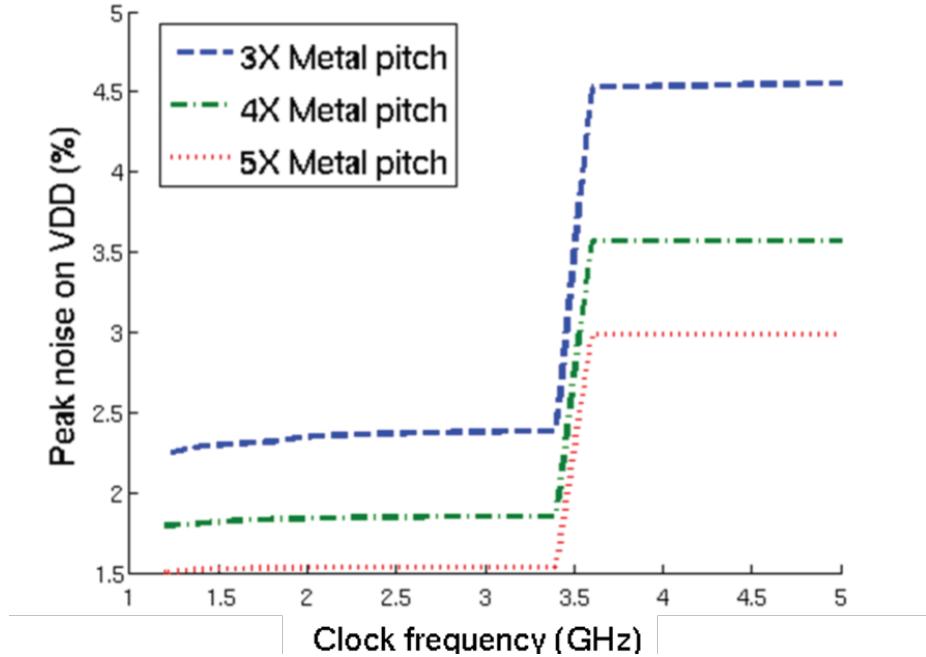

| 4.12 Peak noise in 3X, 4X, and 5X minimum metal pitch interconnect scaling scenarios with increasing clock frequencies in 7 nm technology. . . . . | 102 |

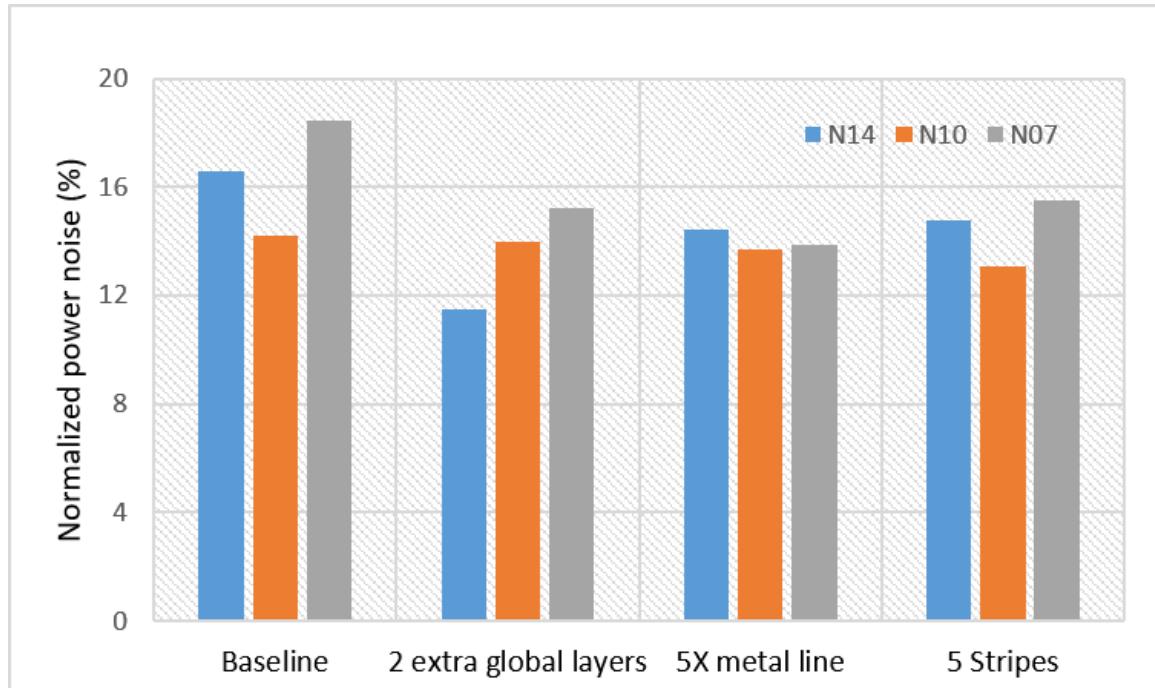

| 4.13 Total power noise in 14, 10, and 7 nm technology nodes for four different scenarios. . . . .                                                  | 104 |

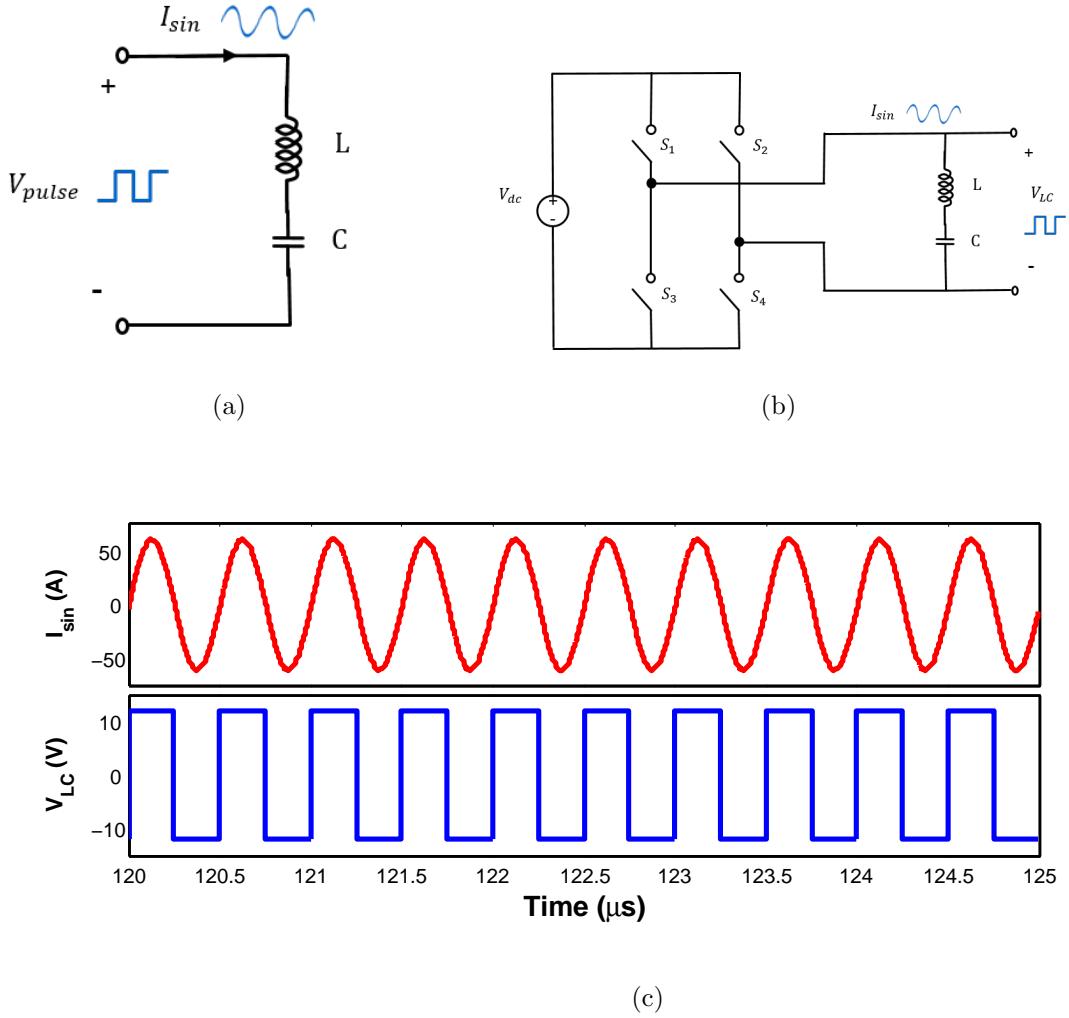

| 5.1 Quasi-sinusoidal current generation circuit within a resonant converter.                                                                       |     |

| (a) Sinusoidal current generation mechanism, (b) $LC$ tank circuit, and                                                                            |     |

| (c) voltage across $LC$ tank and quasi-sinusoidal current. . . . .                                                                                 | 110 |

| 5.2 Full bridge isolated LLC resonant converter . . . . .                                                                                          | 112 |

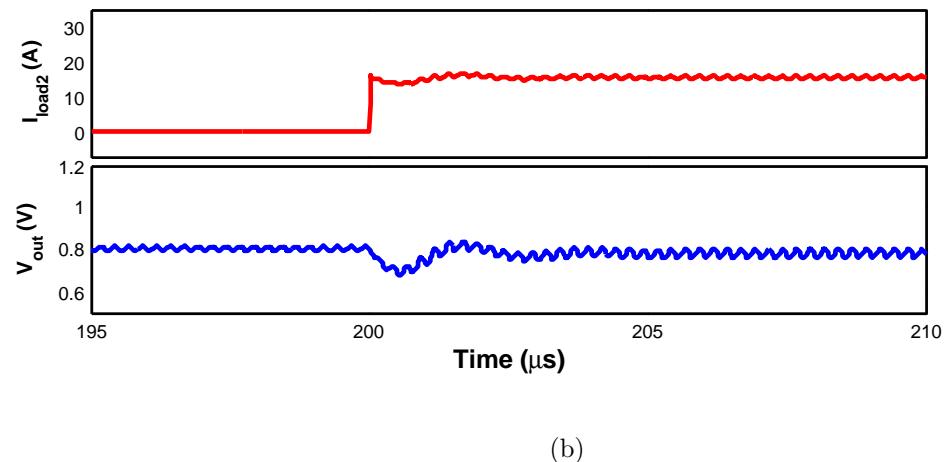

| 5.3 Response of the LLC resonant converter to a change in the load. (a) Static load, and (b) dynamic load. . . . .                                 | 114 |

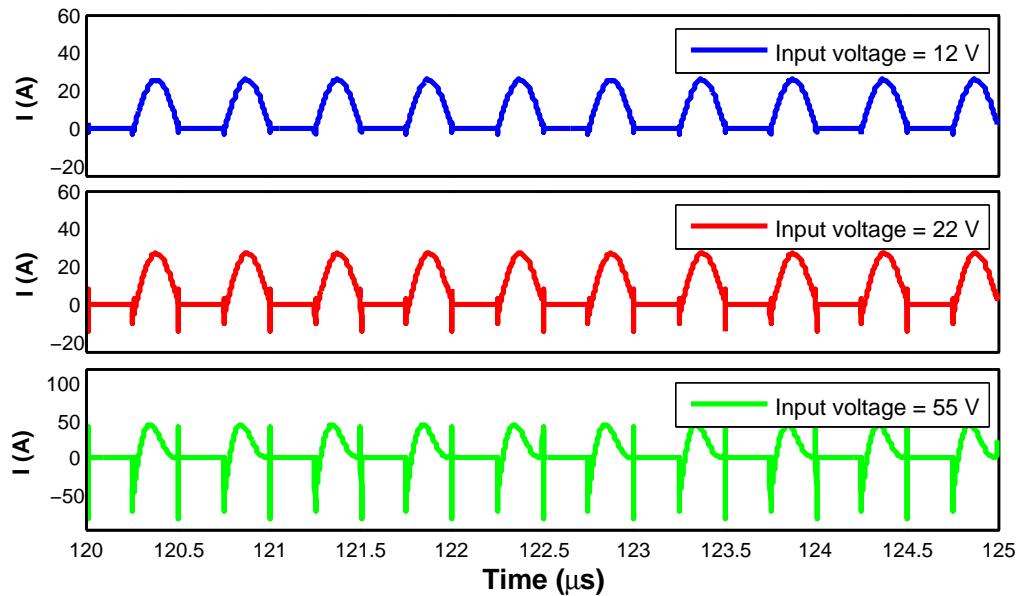

| 5.4 Performance degradation of a high turns ratio converter. . . . .                                                                               | 117 |

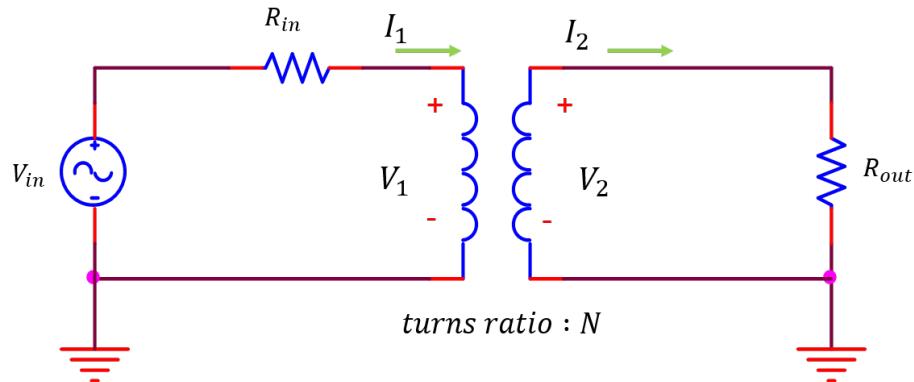

| 5.5 Working principle of basic transformer . . . . .                                                                                               | 118 |

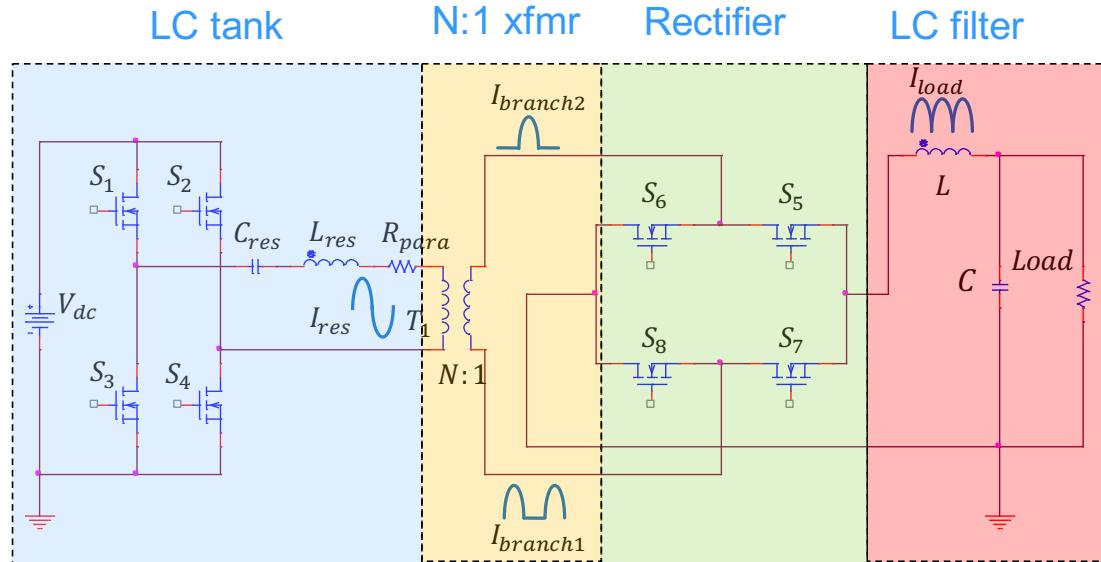

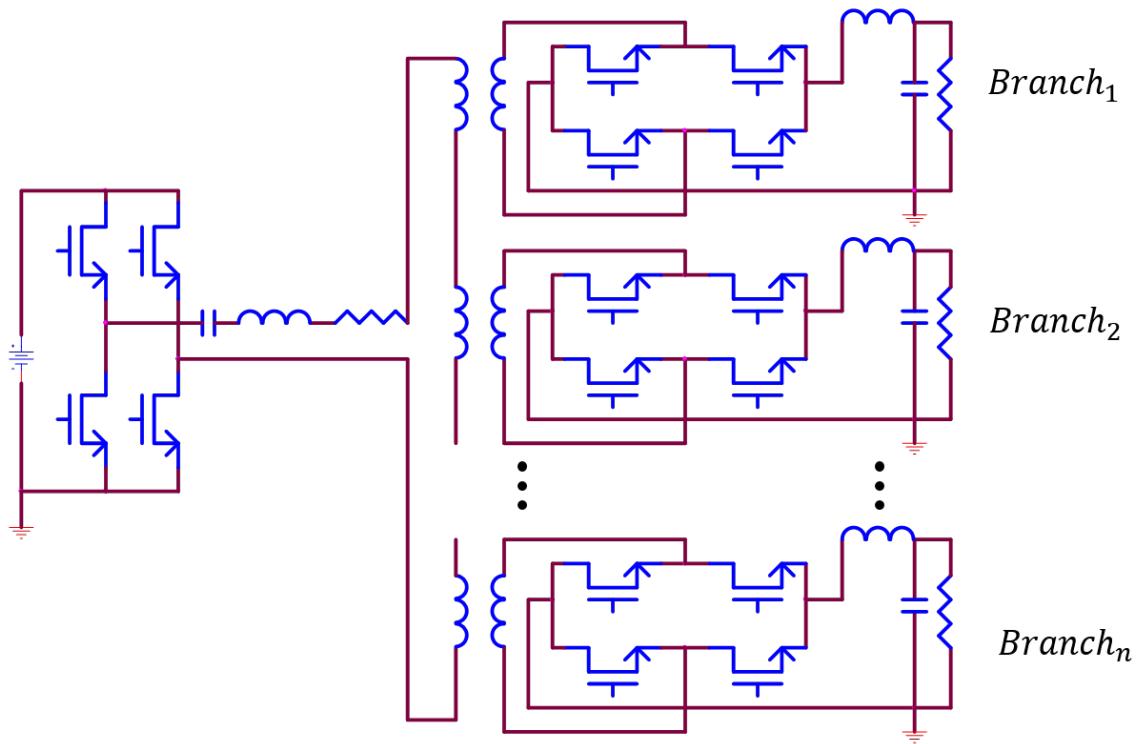

| 5.6 LLC resonant converter with distributed topology . . . . .                                                                                     | 120 |

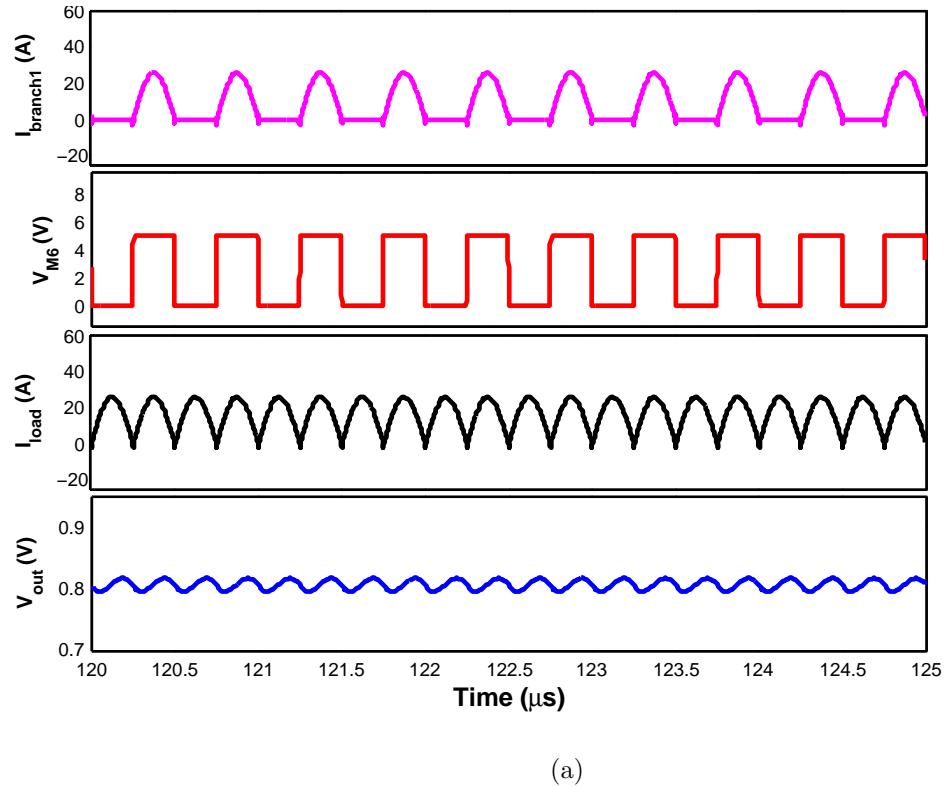

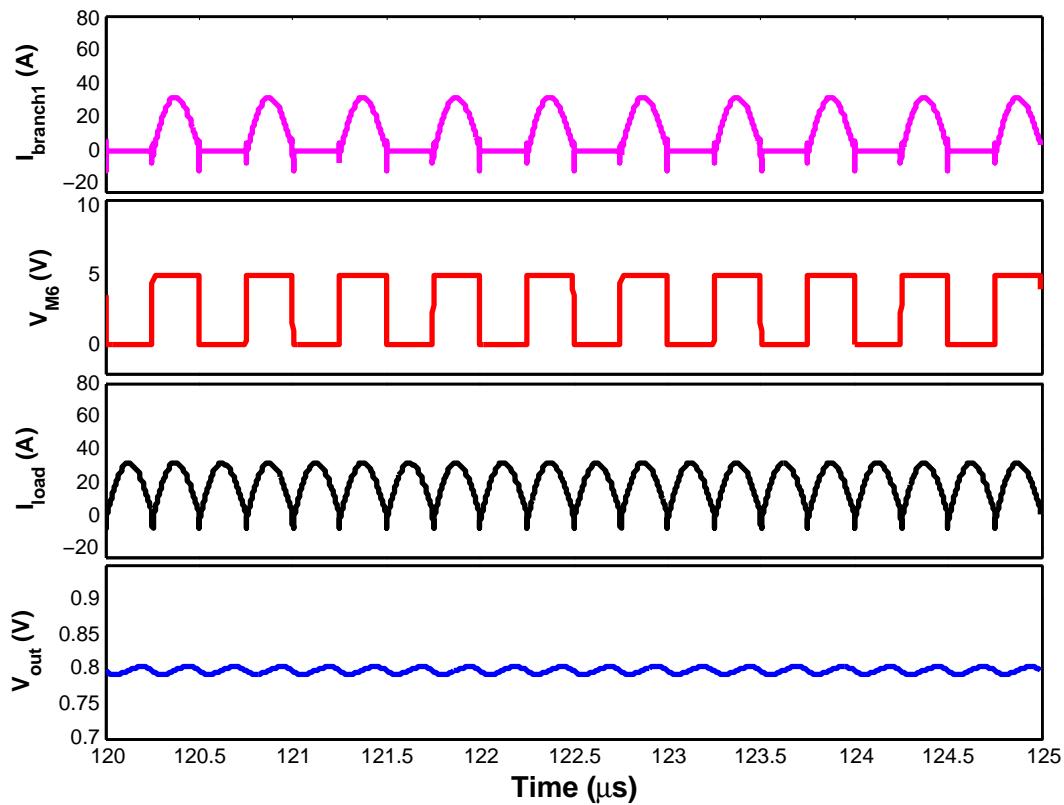

| 5.7 Waveforms characterizing performance of distributed LLC resonant converter . . . . .                                                           | 121 |

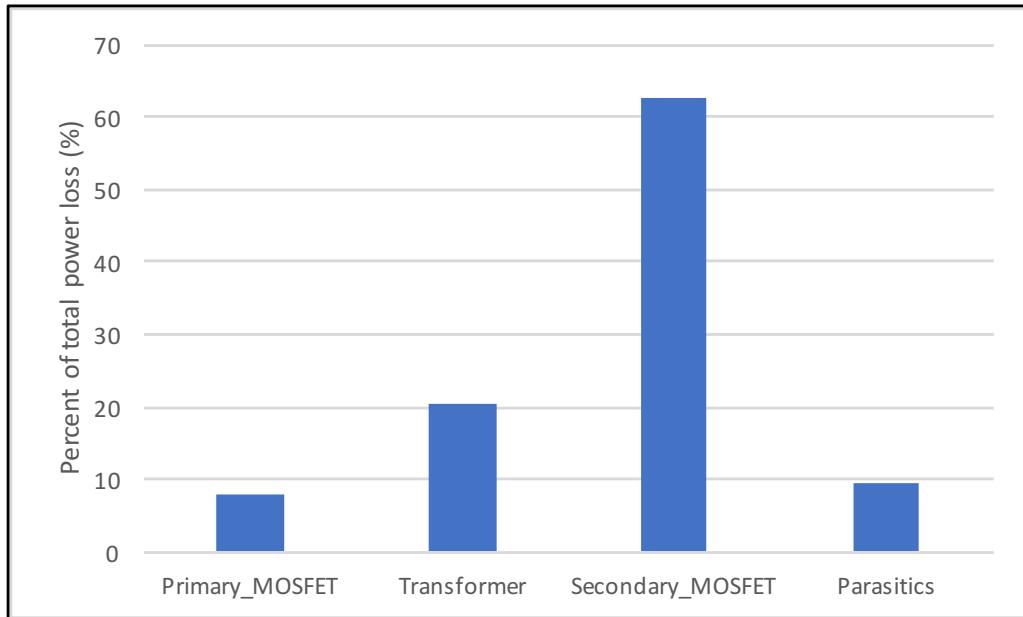

| 5.8 Power loss components for an eight branch distributed LLC resonant converter. . . . .                                                          | 123 |

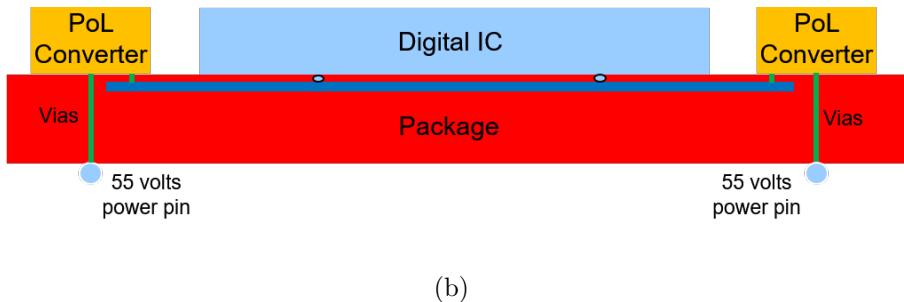

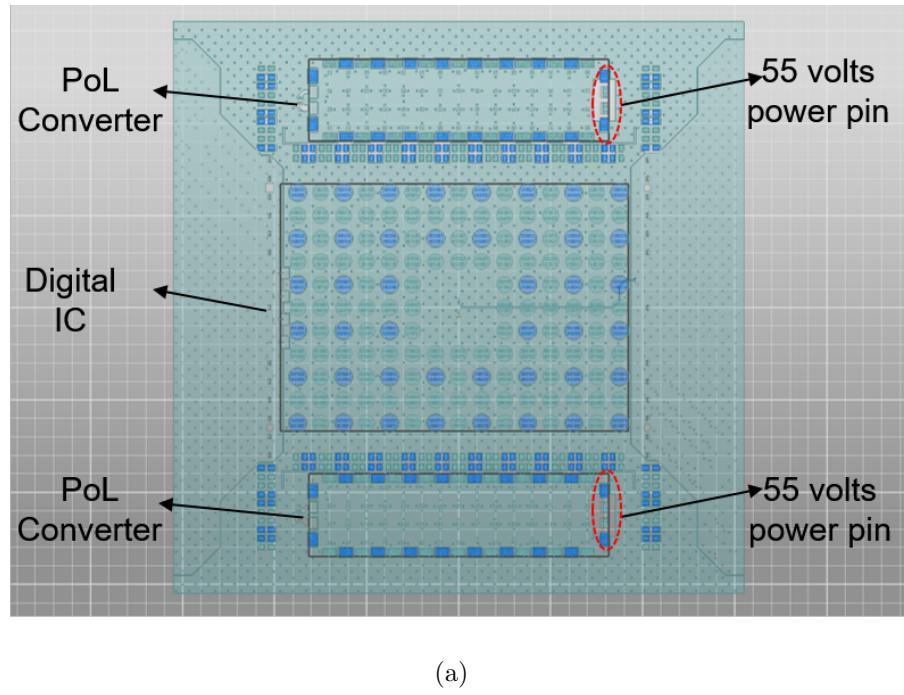

| 5.9 Package with a digital IC and two PoL converter. (a) Top view, and                                                                             |     |

| (b) side view. . . . .                                                                                                                             | 127 |

|                                                                                                                                                                                                                                                                                                        |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

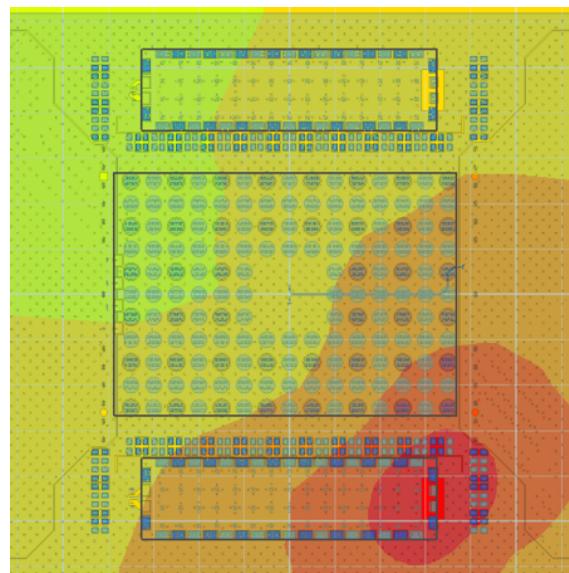

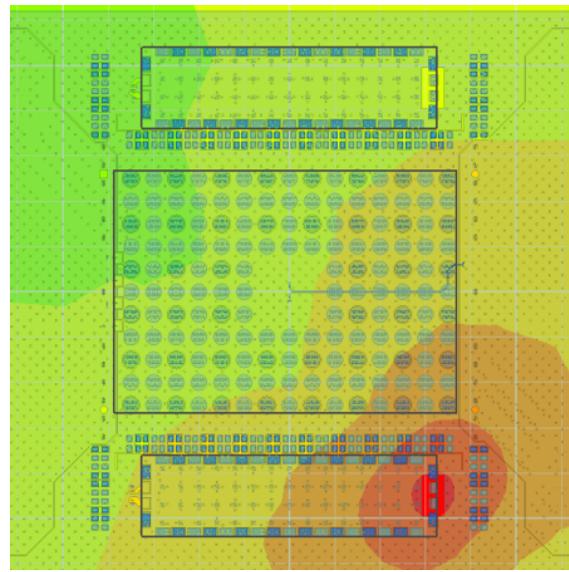

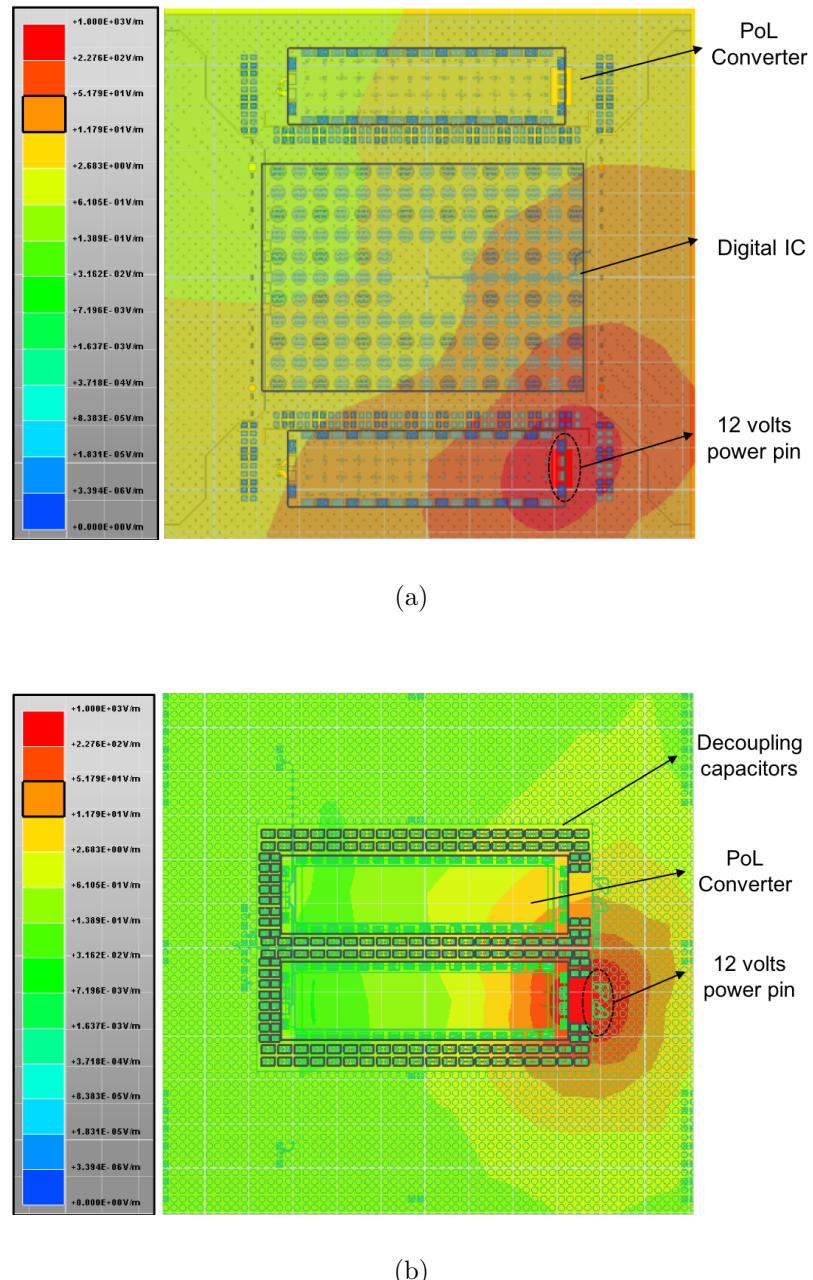

| 5.10 Intensity of electric field across package. (a) Single branch LLC resonant converter, and (b) distributed LLC resonant converter. . . . .                                                                                                                                                         | 130 |

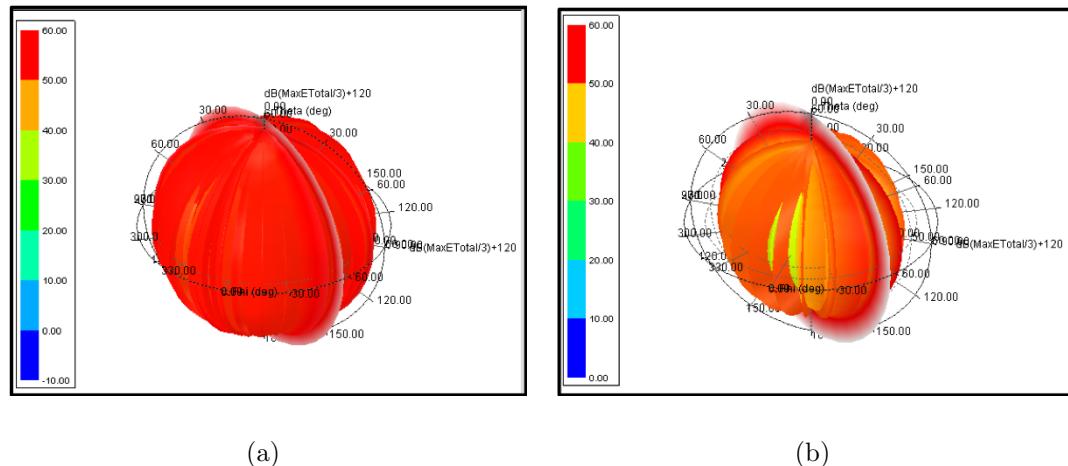

| 5.11 Comparison of 3 meter far field EMI, (a) standard resonant converter, and (b) distributed resonant converter. . . . .                                                                                                                                                                             | 131 |

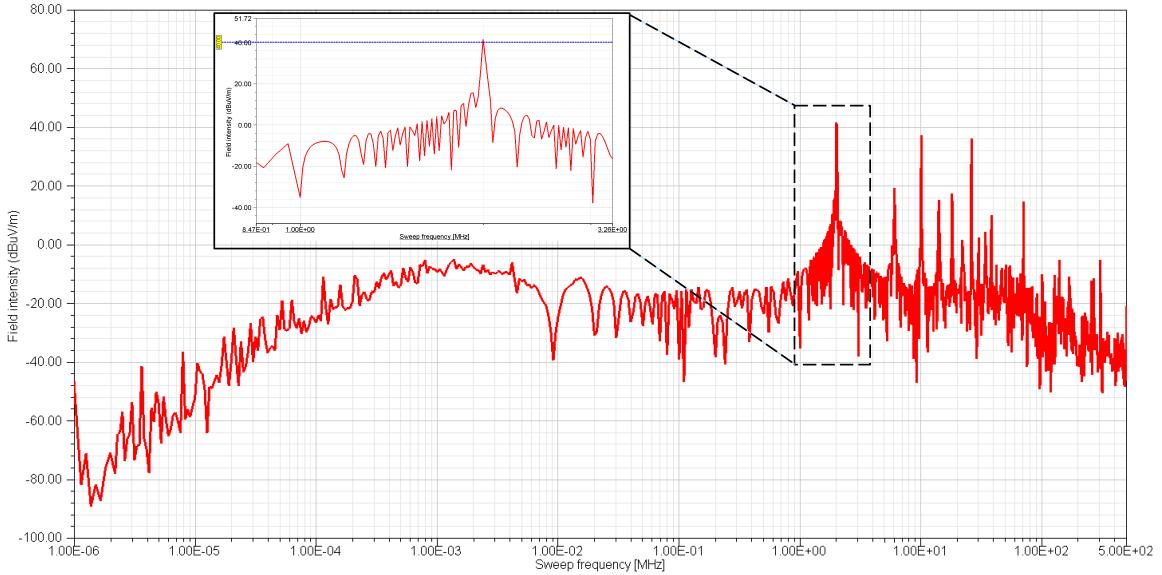

| 5.12 Comparison between far field radiation of distributed LLC resonant converter at 3 meters and the CISPR 22 standard. . . . .                                                                                                                                                                       | 132 |

|                                                                                                                                                                                                                                                                                                        |     |

| 6.1 Board mounted VR. Note the resistive path (dashed line) between the VR and on-chip load . . . . .                                                                                                                                                                                                  | 136 |

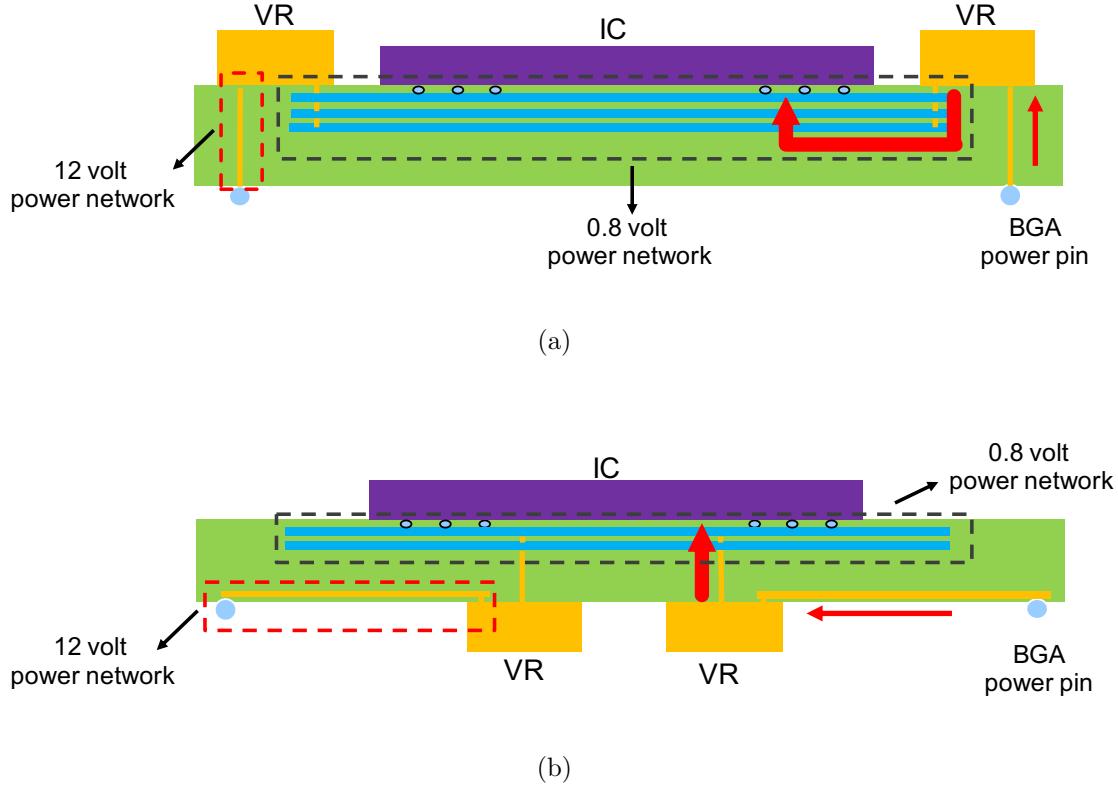

| 6.2 Sectional view of VR-on-package with two PoL converters placed next to the IC. The solid and dashed arrows depict the current path, respectively, between the ball grid array (BGA) power pins and the VRs, and between the VRs and the IC. The VRs are placed on (a) top, and (b) bottom. . . . . | 139 |

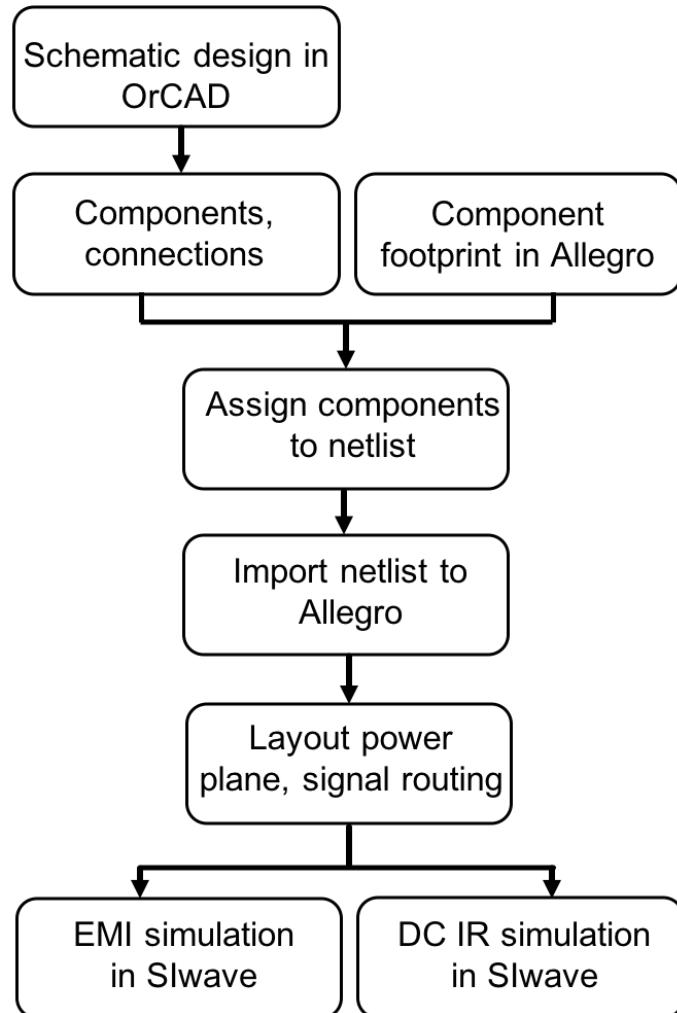

| 6.3 VR-on-package design and evaluation flow . . . . .                                                                                                                                                                                                                                                 | 142 |

| 6.4 Intensity of electric field across package. (a) VR top placement topology, and (b) VR bottom placement topology. . . . .                                                                                                                                                                           | 146 |

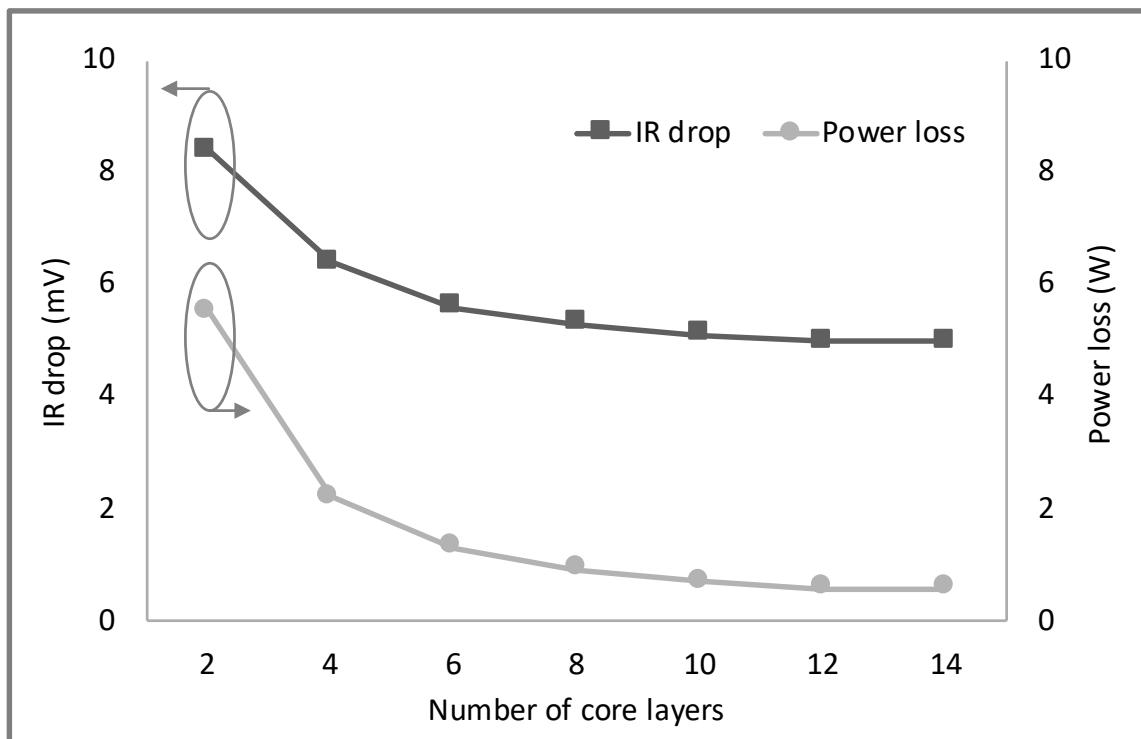

| 6.5 Variation of IR drop and power loss with different number of core layers in the VR top topology . . . . .                                                                                                                                                                                          | 147 |

| 6.6 Power delivery model for evaluating $Ldi/dt$ noise of VR top and bottom topologies . . . . .                                                                                                                                                                                                       | 151 |

|                                                                                                                                                                                              |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.7 Comparison between VR top and bottom placement with number of package layers ranging from 16 to 28 layers. (a) EMI, (b) worst case IR drop, and (c) power loss [193]. . . . .            | 154 |

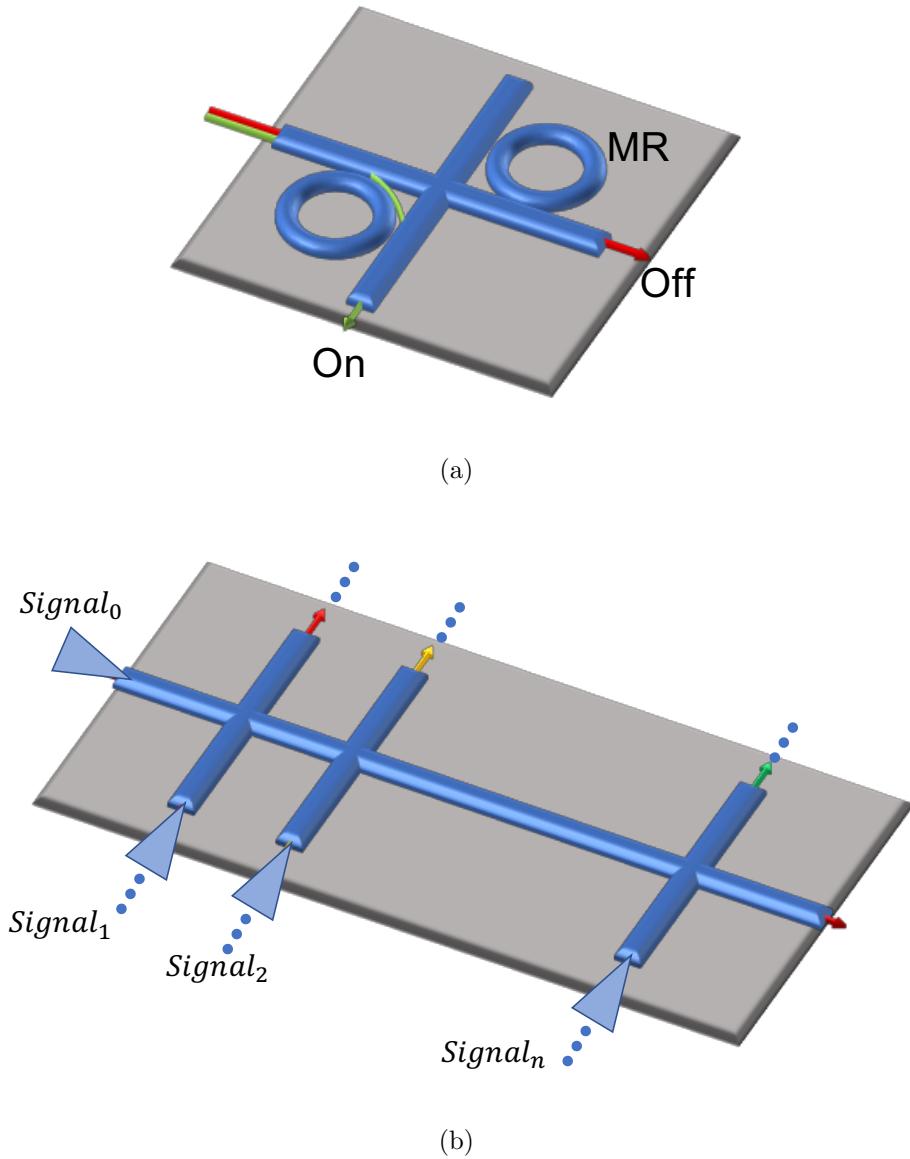

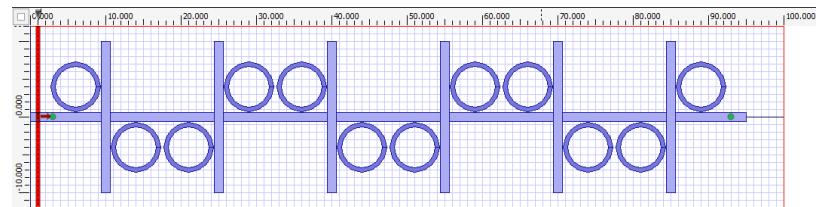

| 7.1 Waveguide crossing, (a) a 2 x 2 $\lambda$ -router, which consists of waveguides and micro-ring resonators, and (b) signal routing within a complex photonic system. . . . .              | 159 |

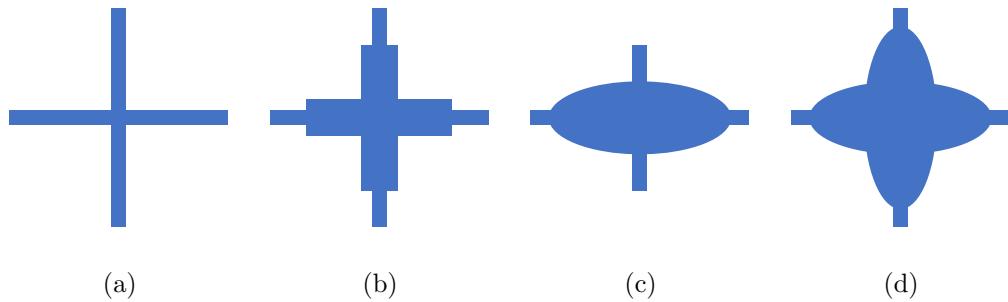

| 7.2 Direct waveguide crossing types. (a) Single mode crossing, (b) multi-mode interference-based crossing, (c) elliptical crossing, and (d) four fold symmetric elliptical crossing. . . . . | 161 |

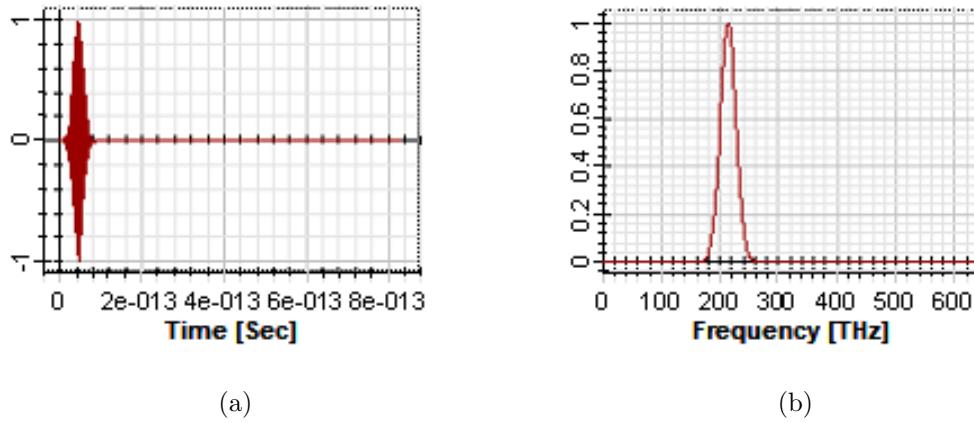

| 7.3 Input light source. (a) Time domain, and (b) frequency domain. . . .                                                                                                                     | 165 |

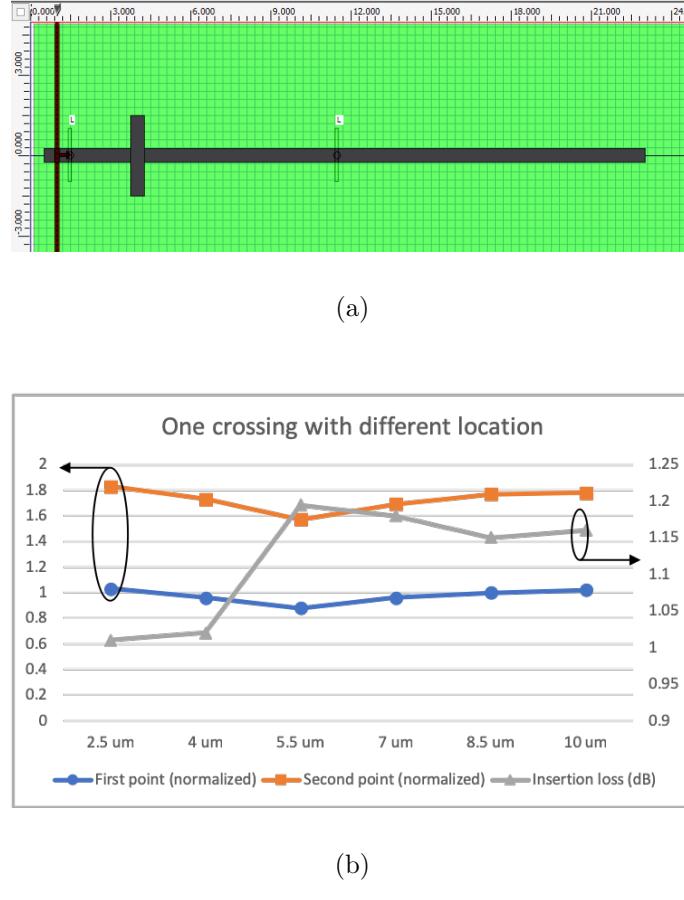

| 7.4 Effect of the placement of a single waveguide crossing on the signal loss. (a) Experimental setup, and (b) FDTD simulations. . . . .                                                     | 166 |

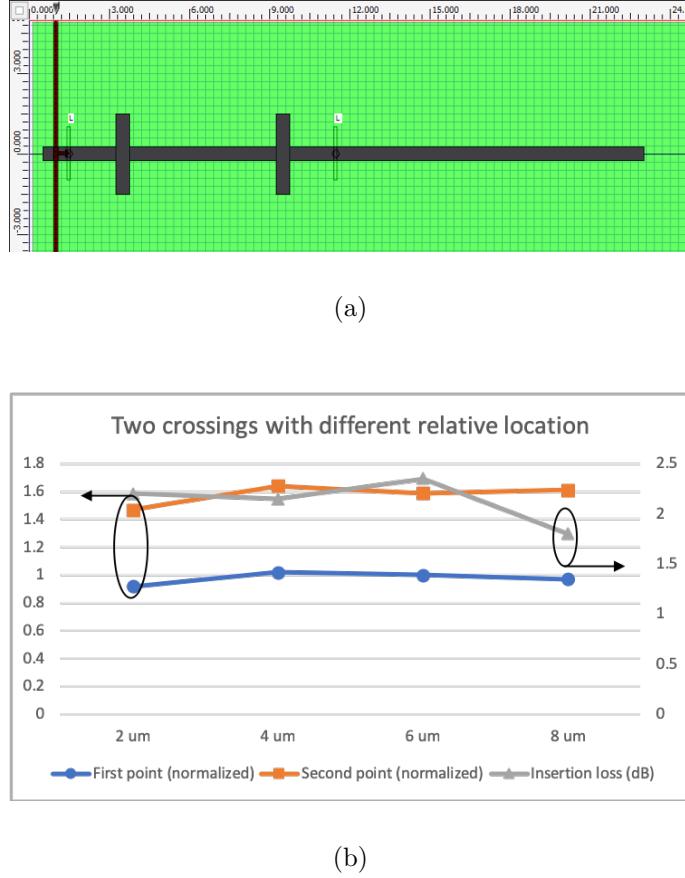

| 7.5 Effect of the placement of two waveguide crossings on signal loss. (a) Experimental setup, and (b) FDTD simulations. . . . .                                                             | 167 |

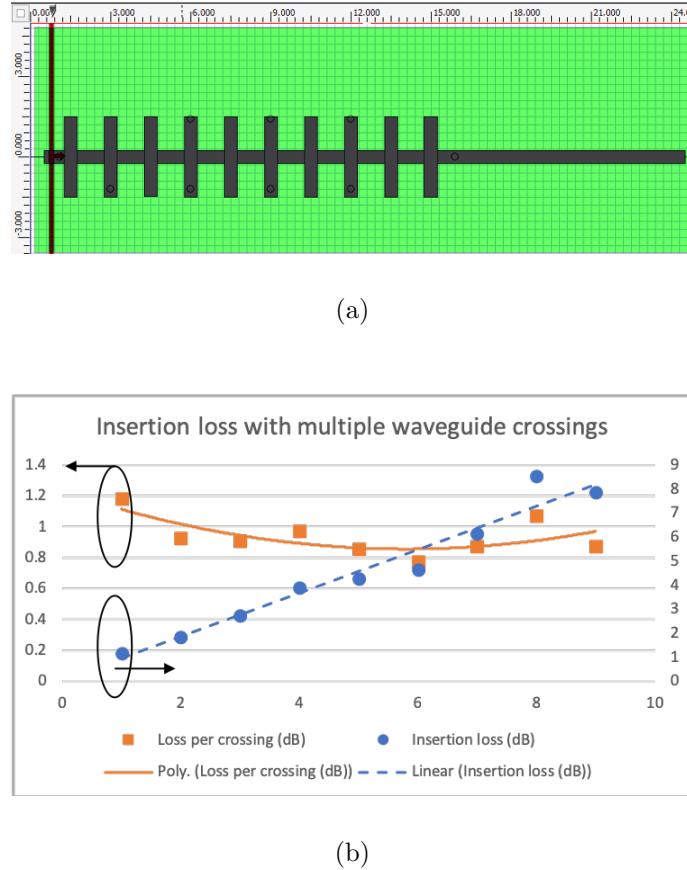

| 7.6 Effect of the placement of multiple waveguide crossings on signal loss. (a) Experimental setup, and (b) FDTD simulations. . . . .                                                        | 168 |

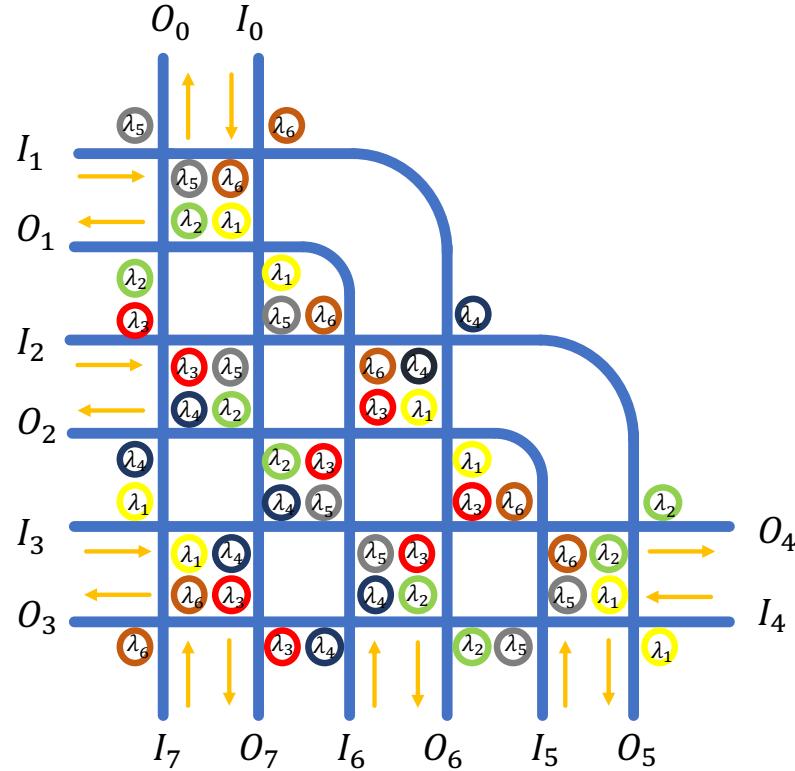

| 7.7 8x8 GWOR router. (a) Demonstration of router topology with waveguide and micro-ring resonators, and (b) FDTD simulation setup for worse case scenario. . . . .                           | 174 |

|     |                                                                                                                                                                                                                                                                                              |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

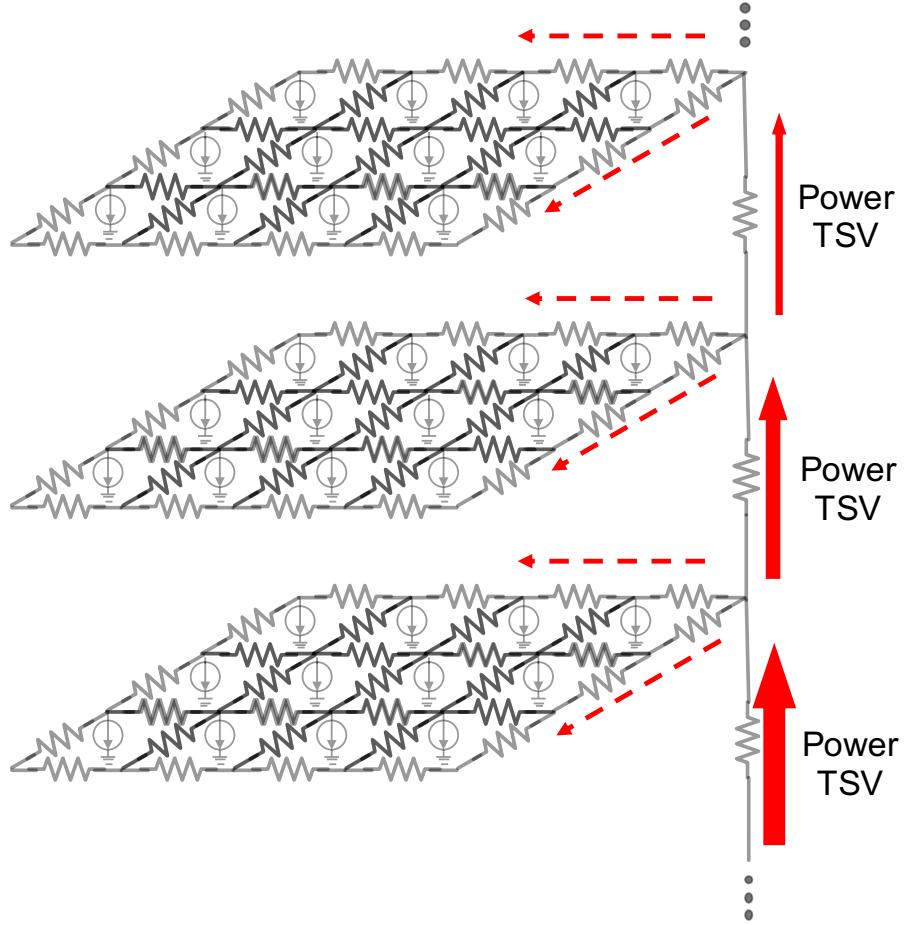

| 8.1 | Current path within a 3-D power distribution network consisting of vertical current paths through the P/G TSVs and horizontal current paths within each 2-D IC. . . . .                                                                                                                      | 178 |

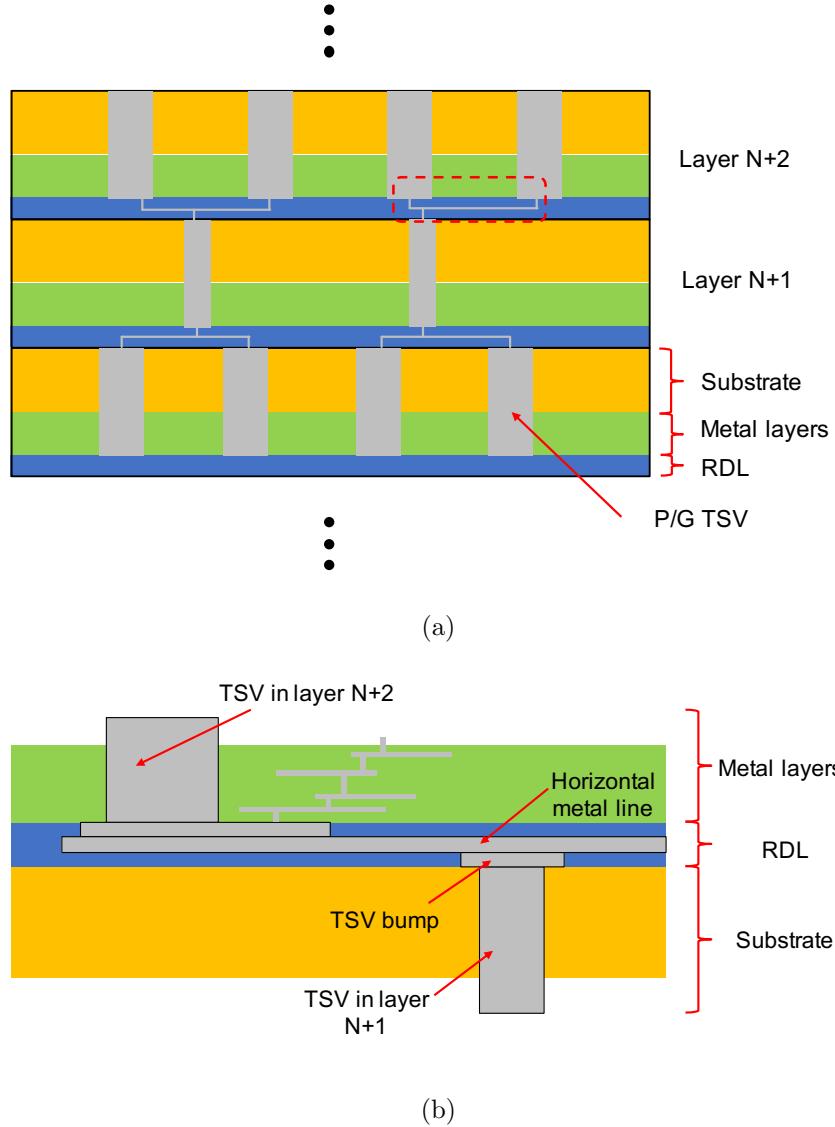

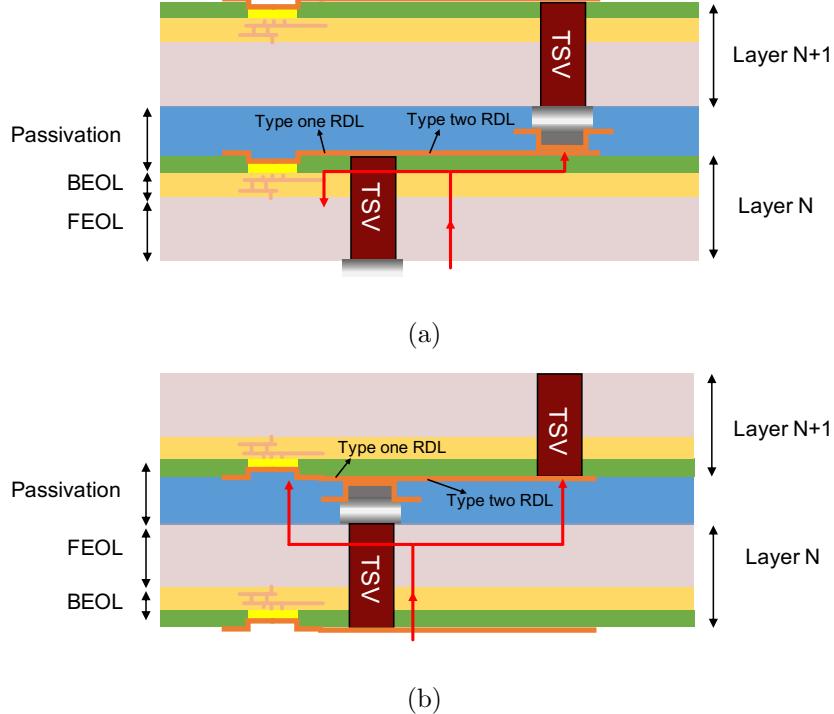

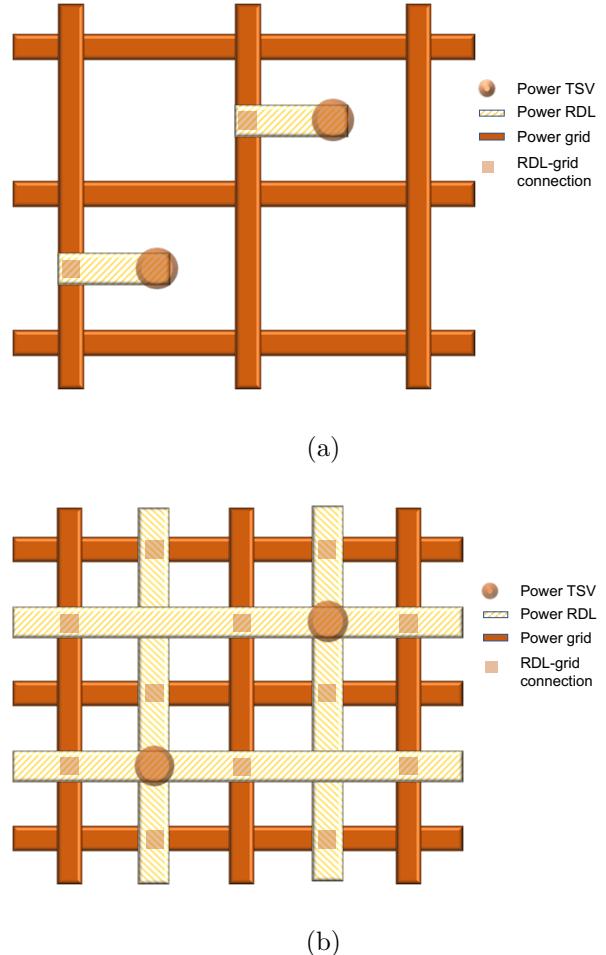

| 8.2 | RDL as an interface between a P/G TSV and an adjacent P/G TSV, and between a P/G TSV and a 2-D power grid. (a) The location of the RDL within a 3-D IC between two adjacent layers; and (b) a zoom-in of the RDL, where the RDL supports both horizontal and vertical current paths. . . . . | 180 |

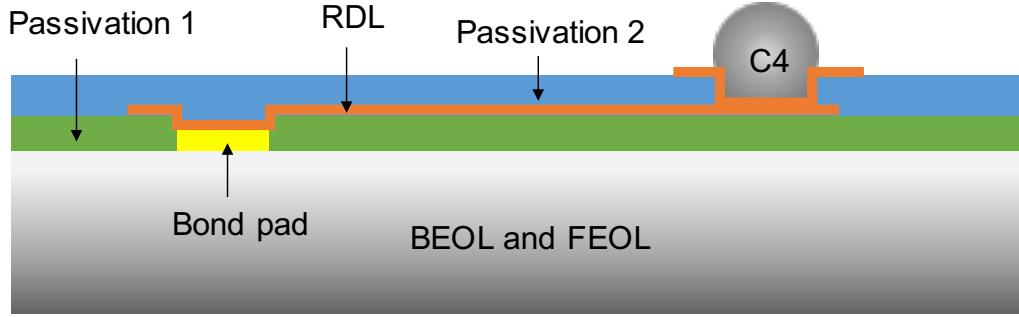

| 8.3 | RDL as an interface between the IC and package. . . . .                                                                                                                                                                                                                                      | 182 |

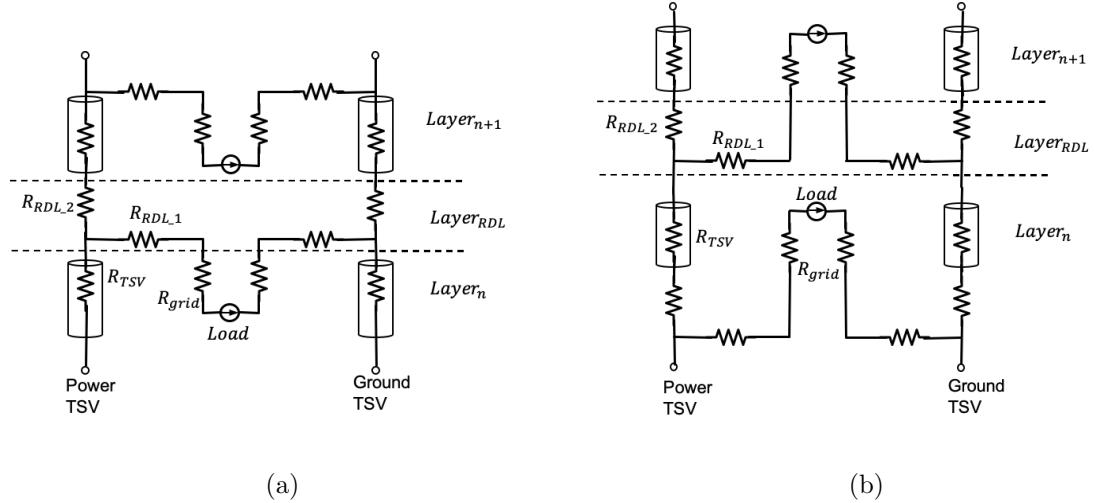

| 8.4 | Type A TSV and current path between the TSV and load. (a) Cross sectional view, and (b) lumped circuit model. . . . .                                                                                                                                                                        | 186 |

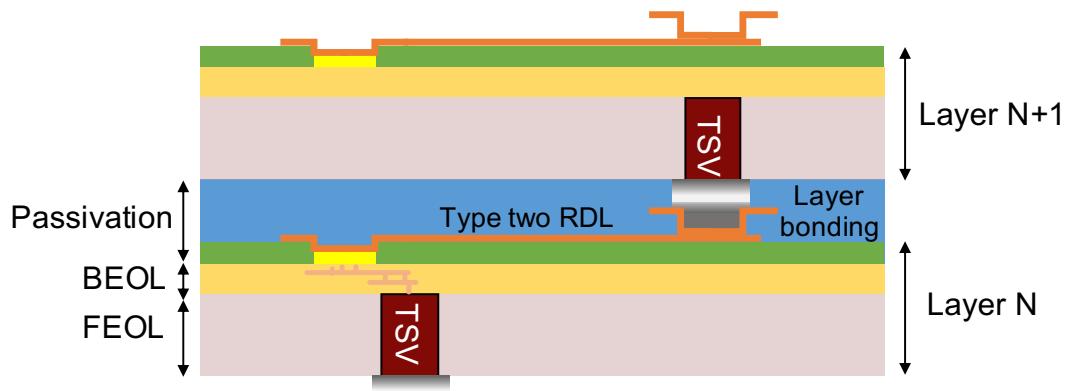

| 8.5 | Cross sectional view of type two RDL for type A TSVs. The type two RDL connects the bond pad of the power grid in layer N to the P/G TSVs in layer N+1. . . . .                                                                                                                              | 189 |

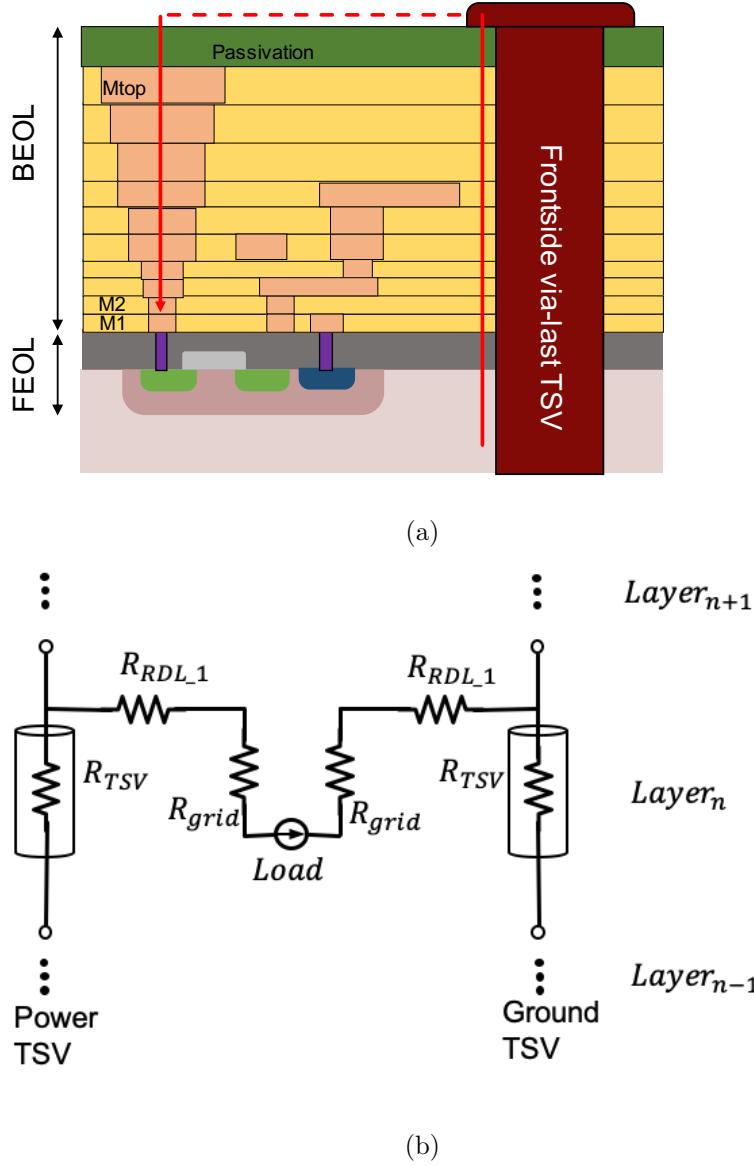

| 8.6 | Type B TSV and current path between TSV and load. (a) Cross sectional view, and (b) lumped circuit model. . . . .                                                                                                                                                                            | 191 |

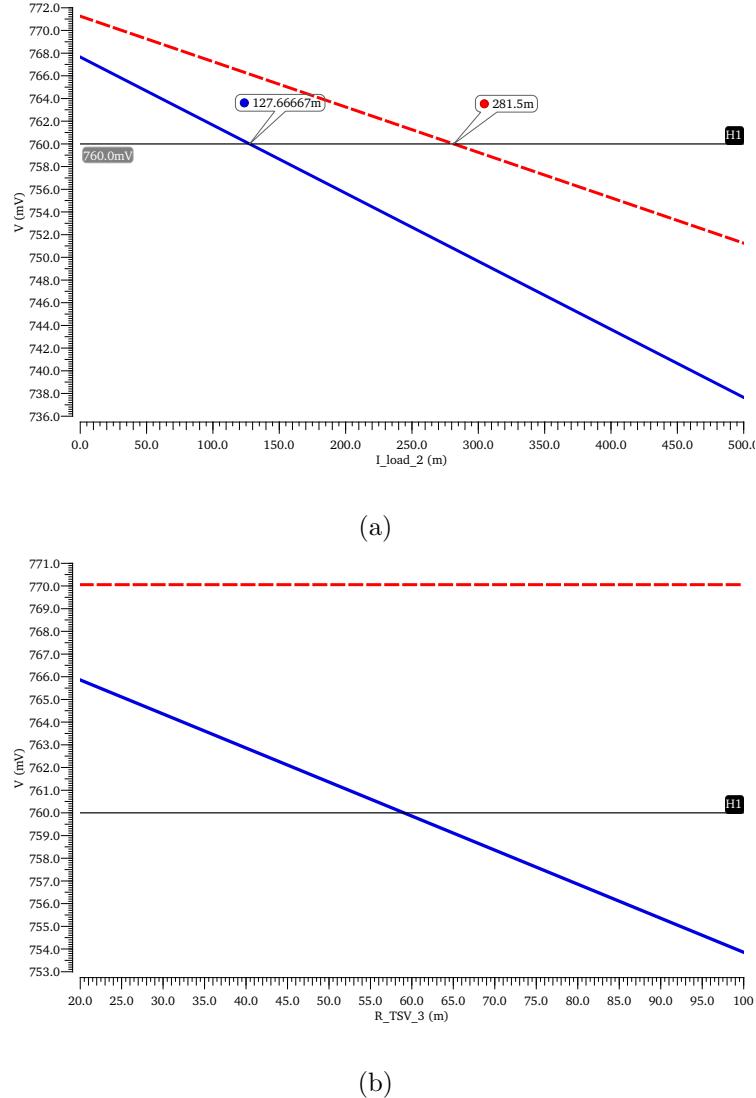

| 8.7 | Cross sectional view of current path and P/G RDL for type B TSVs, (a) back-to-face stacking topology, and (b) face-to-back stacking topology. .                                                                                                                                              | 195 |

| 8.8 | Circuit model of current path and P/G RDL for type B TSVs, (a) back-to-face stacking topology, and (b) face-to-back stacking topology. .                                                                                                                                                     | 195 |

|                                                                                                                                                                                                                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

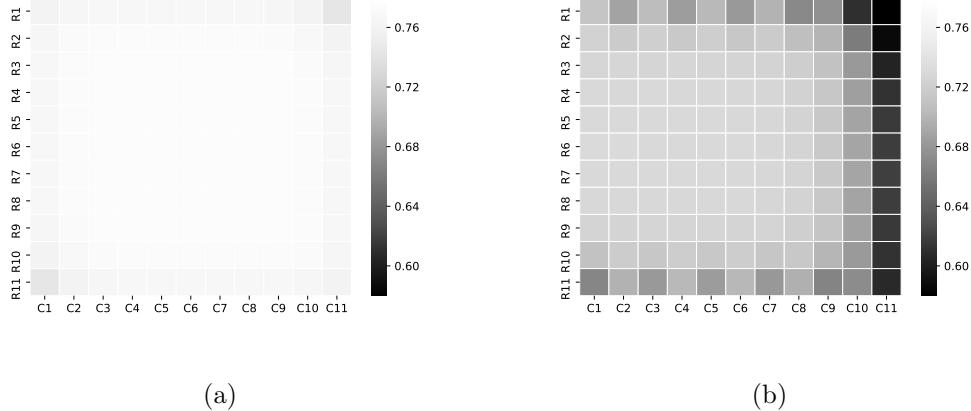

| 8.9 Comparison of voltage drop at the current source of layer three within a seven layer 3-D power network with a back-to-face and face-to-back topology. (a) Load increases in the adjacent layer, and (b) P/G TSV resistance increases within layer three. . . . .                                                    | 197 |

| 8.10 Power grid with a two layer mesh structure. . . . .                                                                                                                                                                                                                                                                | 201 |

| 8.11 Model of the P/G RDL connecting the P/G TSVs to the 2-D power grid. (a) Direct P2P RDL, and (b) grid-based RDL. . . . .                                                                                                                                                                                            | 203 |

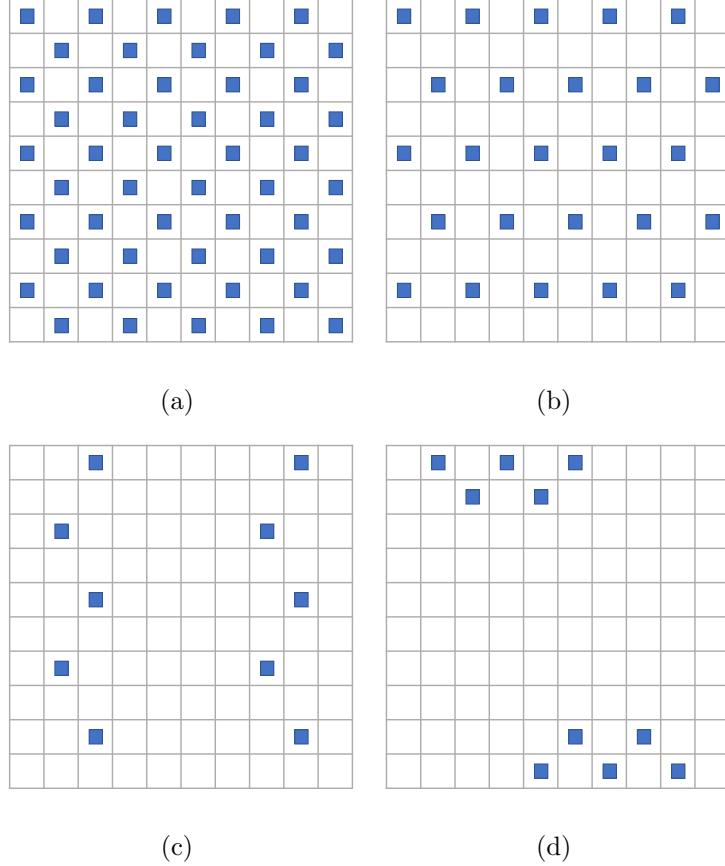

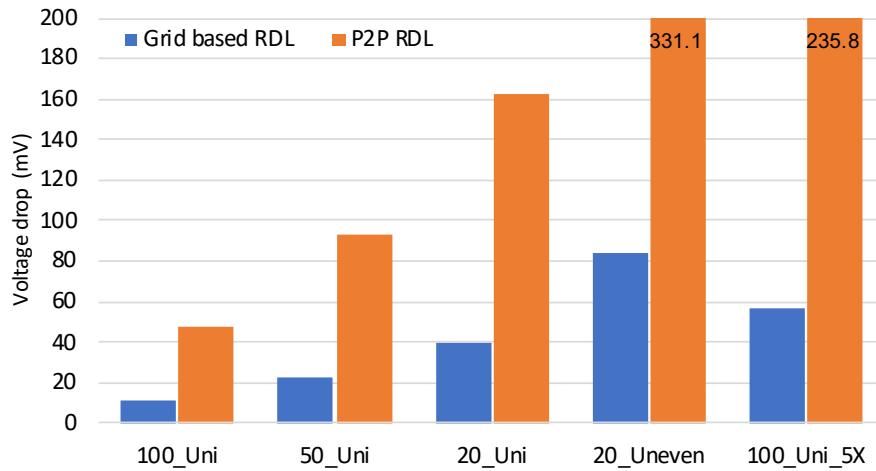

| 8.12 Distribution topologies of P/G TSV for comparison of voltage drop between P2P RDL and grid-based RDL. (a) 100 TSVs with uniform distribution, (b) 50 TSVs with uniform distribution, (c) 20 TSVs with uniform distribution, and (d) 20 TSVs with uneven distribution. . . .                                        | 206 |

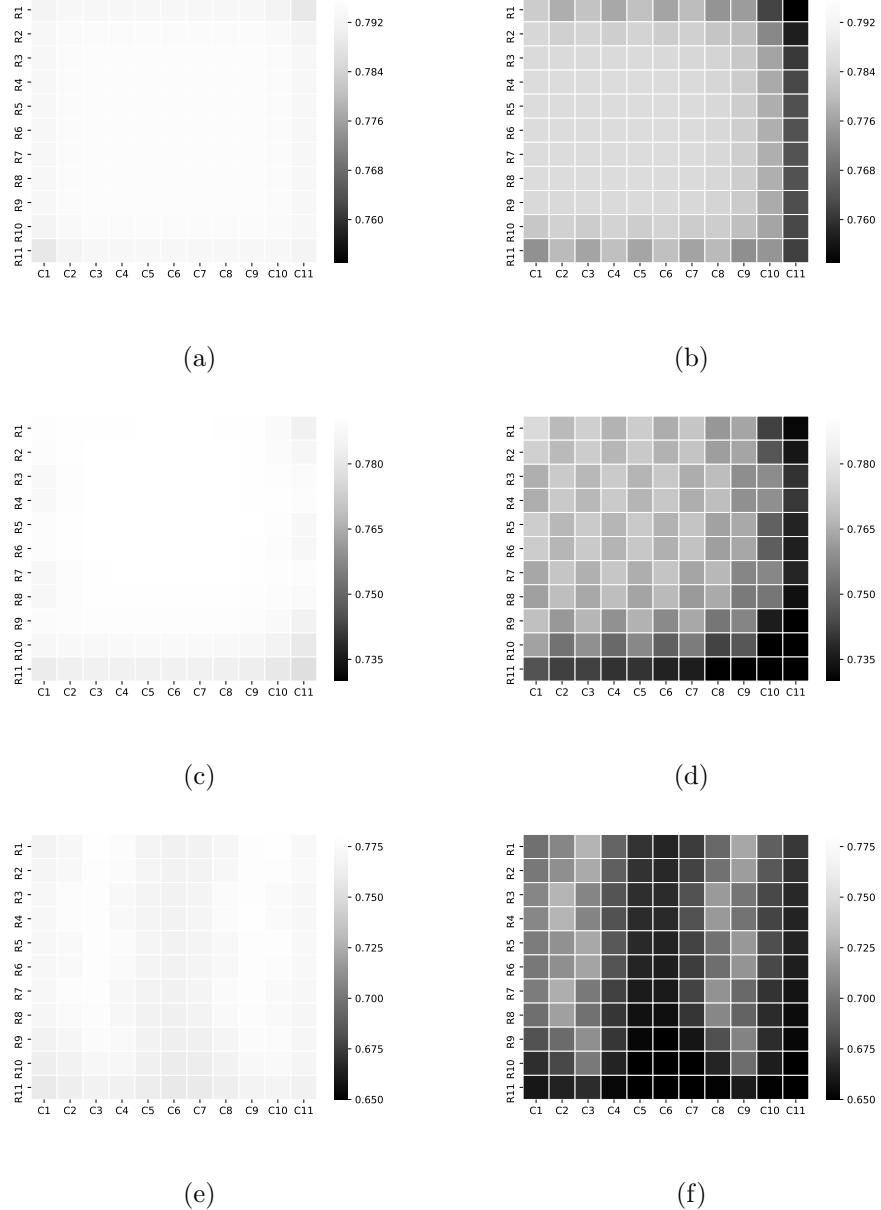

| 8.13 Variation in voltage drop in 3-D power networks with fewer P/G TSVs for grid-based and P2P P/G RDL. (a) 100 TSVs with grid-based P/G RDL, (b) 100 TSVs with P2P RDL, (c) 50 TSVs with grid-based RDL, (d) 50 TSVs with P2P P/G RDL, (e) 20 TSVs with grid-based P/G RDL, and (f) 20 TSVs with P2P P/G RDL. . . . . | 208 |

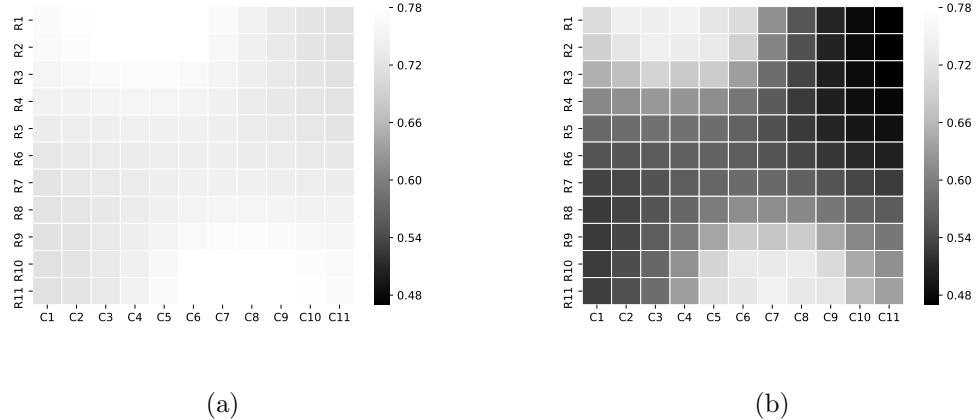

| 8.14 Comparison of voltage drop between the grid-based and P2P RDL with uneven P/G TSV distribution. (a) 20 unevenly distributed P/G TSVs with grid-based RDL, and (b) 20 unevenly distributed P/G TSVs with P2P RDL. . . . .                                                                                           | 209 |

|                                                                                                                                                                                                                                                           |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.15 Comparison of the voltage drop between the grid-based and P2P RDL with increasing load current. (a) Grid-based RDL, and (b) P2P RDL.                                                                                                                 | 210 |

| 8.16 Comparison of the highest voltage drop in the grid-based RDL and P2P RDL for five different scenarios. . . . .                                                                                                                                       | 210 |

| 9.1 16 core, four layer voltage stacked system. . . . .                                                                                                                                                                                                   | 217 |

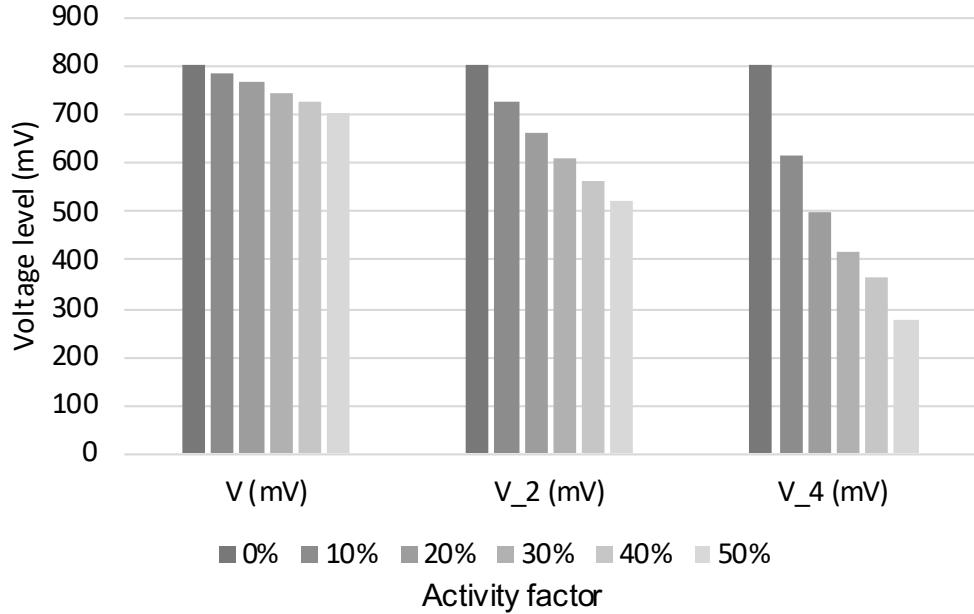

| 9.2 Variation in the voltage levels for different activity factors for a non-stacked system, two layer voltage stacked system, and four layer voltage stacked system. . . . .                                                                             | 219 |

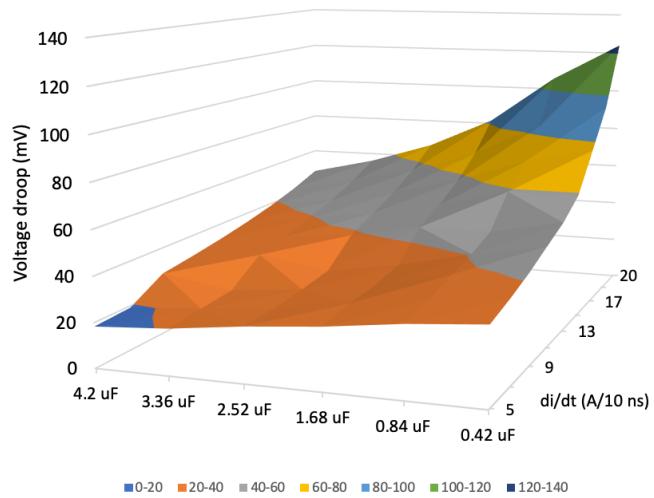

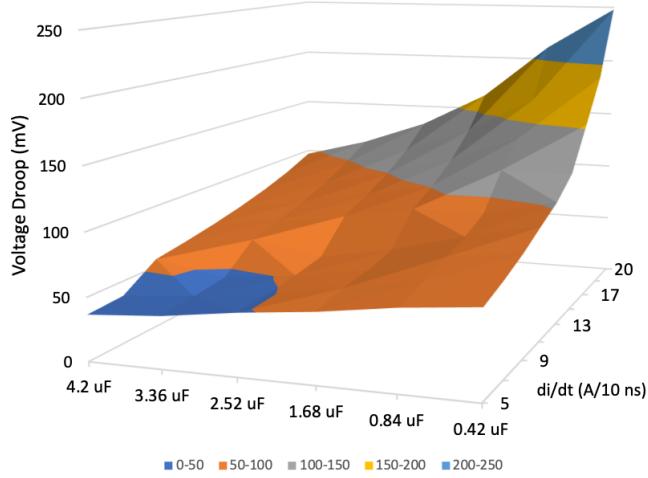

| 9.3 Voltage droop as a function of decoupling capacitance and transient current during a load imbalance, (a) 10 ns, and (b) 5 ns. The decoupling capacitance ranges from 0.42 to 4.2 $\mu$ F and the transient current ranges from 0.5 to 2 A/ns. . . . . | 222 |

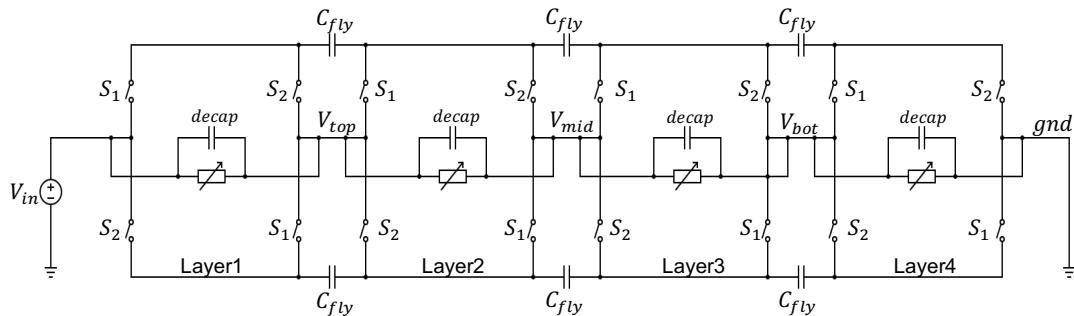

| 9.4 Symmetric ladder topology switched capacitor converter utilized in a four layer voltage stacked system. . . . .                                                                                                                                       | 225 |

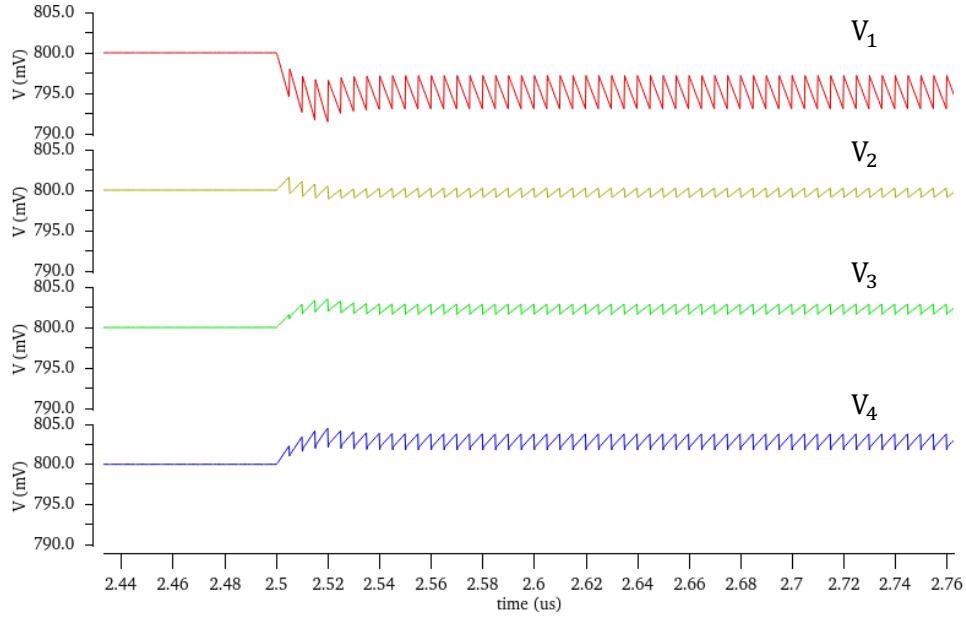

| 9.5 Voltage droop after a 10% load imbalance within a four layer voltage stacked system with a switched capacitor ladder converter. . . . .                                                                                                               | 227 |

|      |                                                                                                                                                                                                                                                                                                                                |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

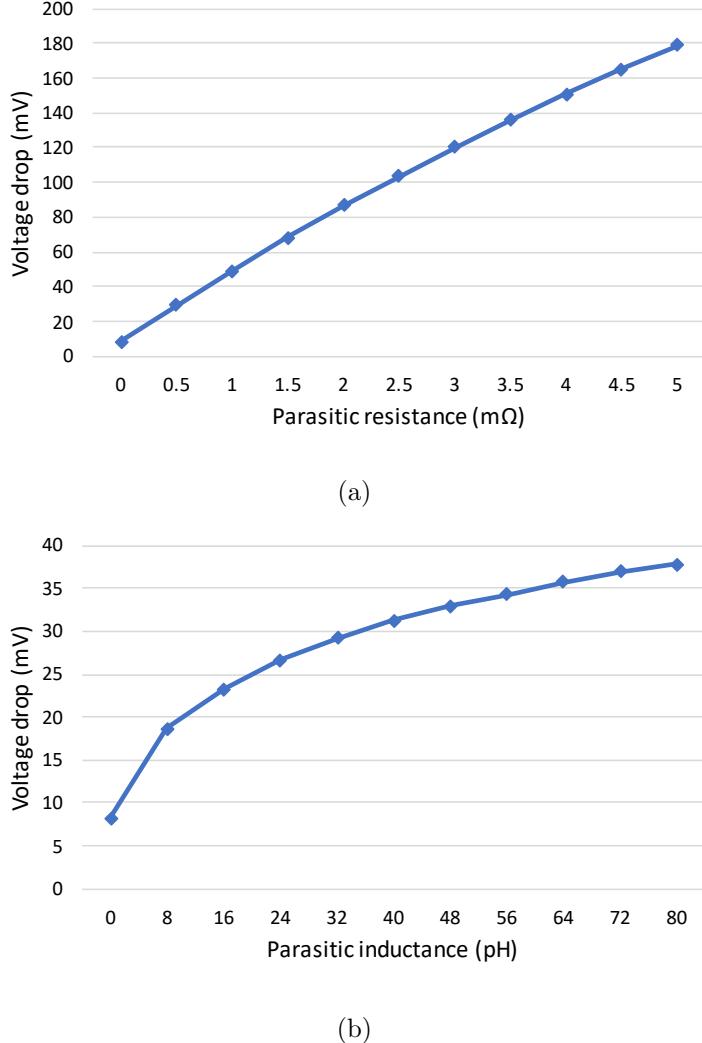

| 9.6  | Voltage drop considering the effects of the parasitic impedances within a power delivery network. (a) Parasitic resistance increases from 0 to 5 mΩ while the parasitic inductance is assumed negligible; and (b) parasitic inductance increases from 0 to 80 pH while the parasitic resistance is assumed negligible. . . . . | 229 |

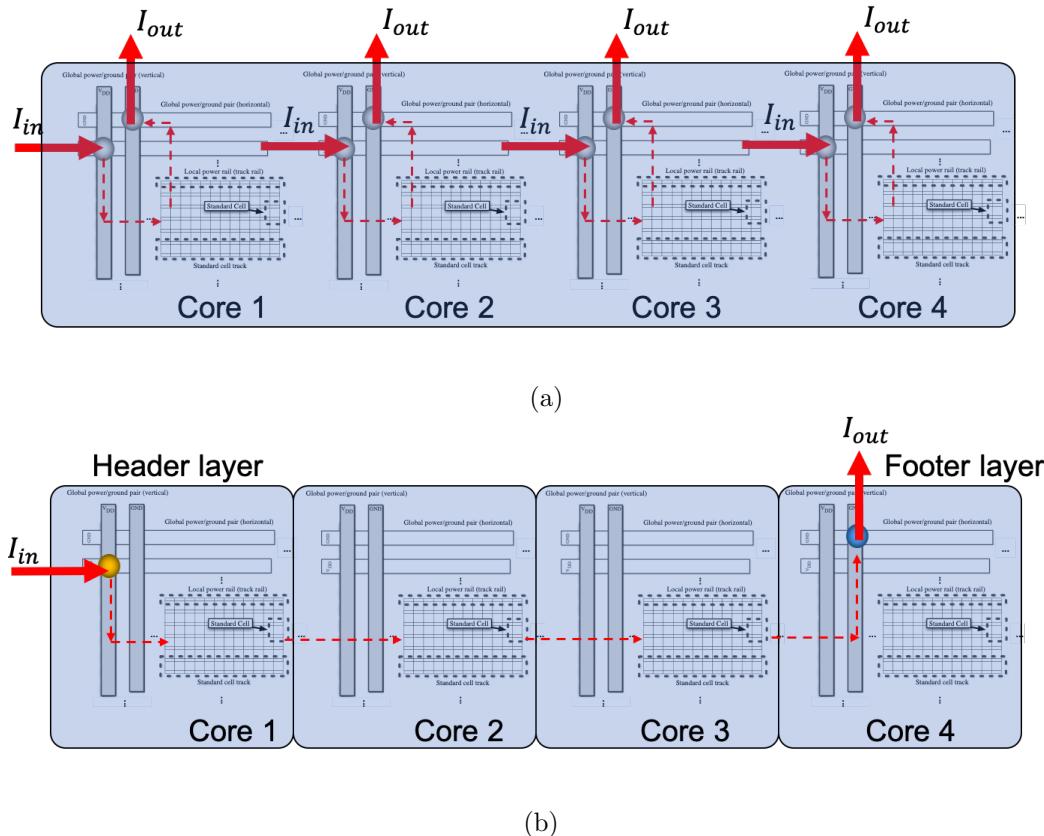

| 9.7  | On-chip current path among different cores. a) Regular non-stacked four core system, and b) four layer voltage stacked system. . . . .                                                                                                                                                                                         | 231 |

| 9.8  | Current density model, a) power distribution cell-based regular non-stacked power grid, and b) voltage stacked power grid with cross-core current path. . . . .                                                                                                                                                                | 234 |

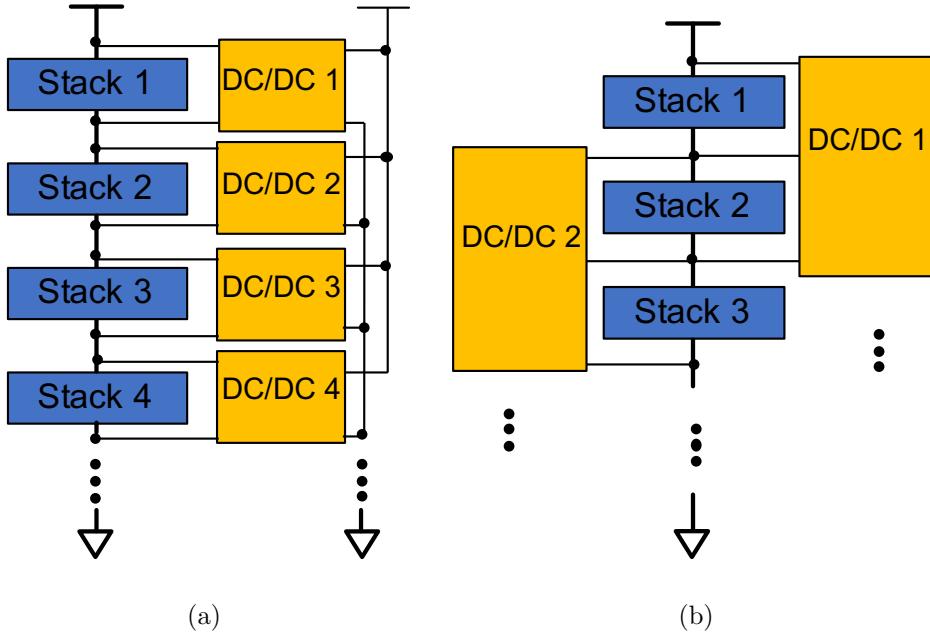

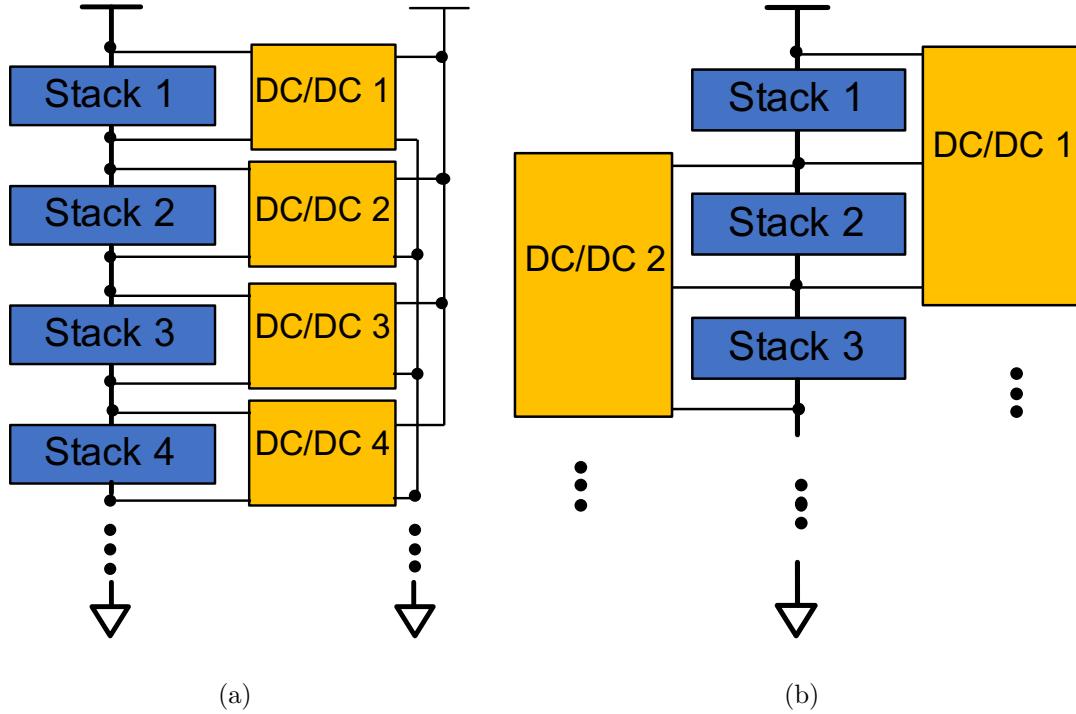

| 9.9  | Two VR topologies utilizing DPP in a voltage stacked system. (a) Stack-to-bus topology, where n DC/DC converters are required for an n layer voltage stacked system, and (b) stack-to-stack topology, where n-1 DC/DC converters are required for an n layer voltage stacked system.                                           | 236 |

| 9.10 | The current path and parasitic impedances of the power delivery system within (a) stack-to-bus topology, and (b) stack-to-stack topology. . . . .                                                                                                                                                                              | 239 |

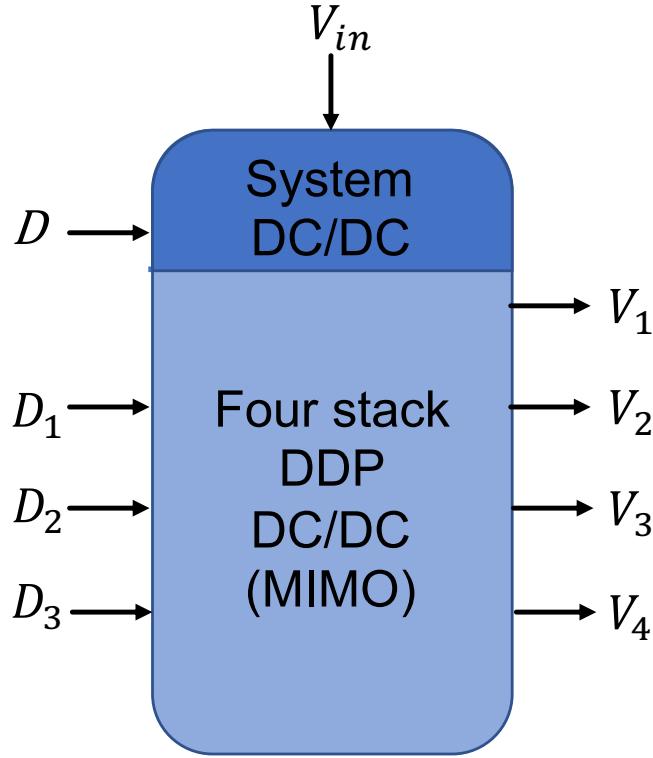

| 9.11 | Resonant converter-based DPP system with stack-to-bus topology in a four layer voltage stacked system. . . . .                                                                                                                                                                                                                 | 241 |

# Chapter 1

## Introduction

The first ever electrical phenomenon recorded by a human being (around 600 BCE) is by Thales of Miletus, who noted that rubbing fur on various substances, such as amber, would produce an attraction between the two materials [1]. Thales believed that this phenomenon was due to the magnetic force generated by the amber which contained a soul inside [2]. In 1600, William Gilbert, for the first time, scientifically explained this phenomenon, which is now called static electricity. He distinguished this phenomenon from magnetism, and gave a new word *electricus* for this phenomenon [3]. The study and exploration of electrical phenomena, and the development and engineering of novel electrical systems and devices have not stopped. Huge power plants, power substations, and electric power grids were developed across the entire country during the electrification era. During the digital era, nanometer scale transistors have been developed and utilized for integrated circuits (ICs) within computer systems.

The Antikythera mechanism (developed in 60 BCE) is generally considered as the oldest computer in human history, which was designed to calculate astronomical positions [4]. Between the late 19th and early 20th centuries, analog computers started to bloom, allowing a user to model or simulate a complex system with a known physical system [5]. These early analog computers were mechanical in nature. The classic example of an early analog computer is the differential analyzer, invented by Vannevar Bush in the 1930's, which used mechanical shafts and gears [6]. Not until 1942 was the first fully electronic analog computer developed by Helmut Hölzer [7], thanks to the development of electronics. The first electronic digital computer, the ENIAC, was developed in 1945 by the US government and can currently be viewed at the University of Pennsylvania [8]. Thanks to the development of integrated circuit technology, computers evolved into the microprocessor era. The successful integration of semiconductor technology into microprocessors started the modern computer era.

The history of the second to the fourth industrial revolution is described in Section 1.1. The effect of computer systems on the third and fourth industrial revolutions is also discussed. Power dissipation plays an important role in the development of computer systems. An overview of power delivery systems within a computer is presented in Section 1.2. An outline of the dissertation is provided in Section 1.3.

## 1.1 Industrial revolutions and computer systems

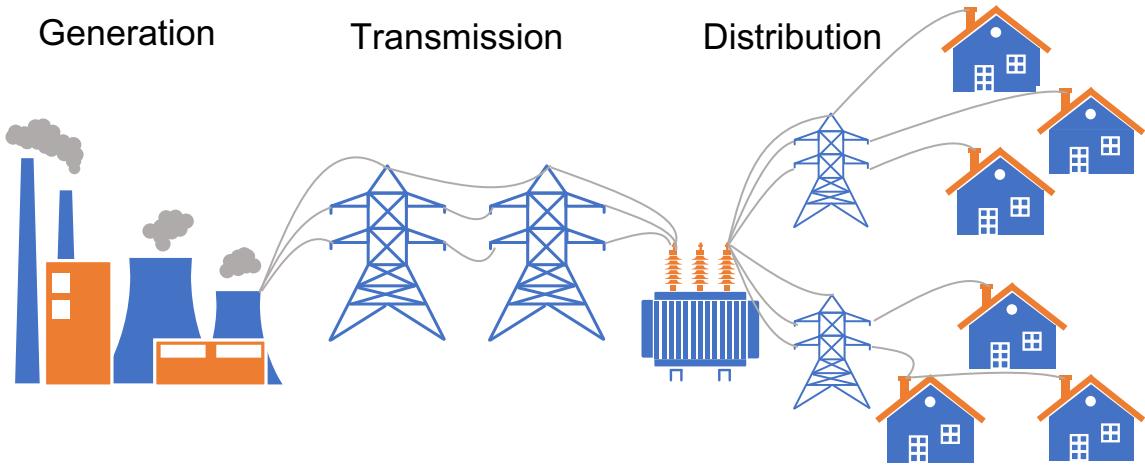

The second industrial revolution, also referred to as the technological revolution, began in the 1870's. This industrial transition provided an excellent opportunity for the development of electrical systems [9]. With the invention of the telephone, incandescent lamp, electric motor, the successful development of AC power stations, and many other important electrical systems, human beings entered the electrification era [10]. The electrical power grid, a combined transmission and distribution network, played an important role in this new electrification era, delivering stable, high quality electrical energy from the power plants to millions of households and factories, as illustrated in Figure 1.1. The development of the electrical power grid enabled the evolution from local generation, steam powered factories to centralized generation, electricity powered factories. This process enabled industry to produce greater output at lower cost, leading to the success of this industrial revolution.

In 1930, the term “electronics” was introduced as a discipline of electrical engineering. Electronics deals with electrical circuits composed of active electrical components such as vacuum tubes, diodes, and so on. Not long after the first electronic digital computer, the first transistor was developed in 1947 by John Bardeen, Walter Brattain, and William Shockley at Bell Labs [11]. The three men probably did not know that they started a new era, the third industrial revolution, also referred to as the digital revolution. Information today is generated, transferred, processed, and stored

Figure 1.1: Power plants generate electricity which is delivered to customers over transmission and distribution power lines.

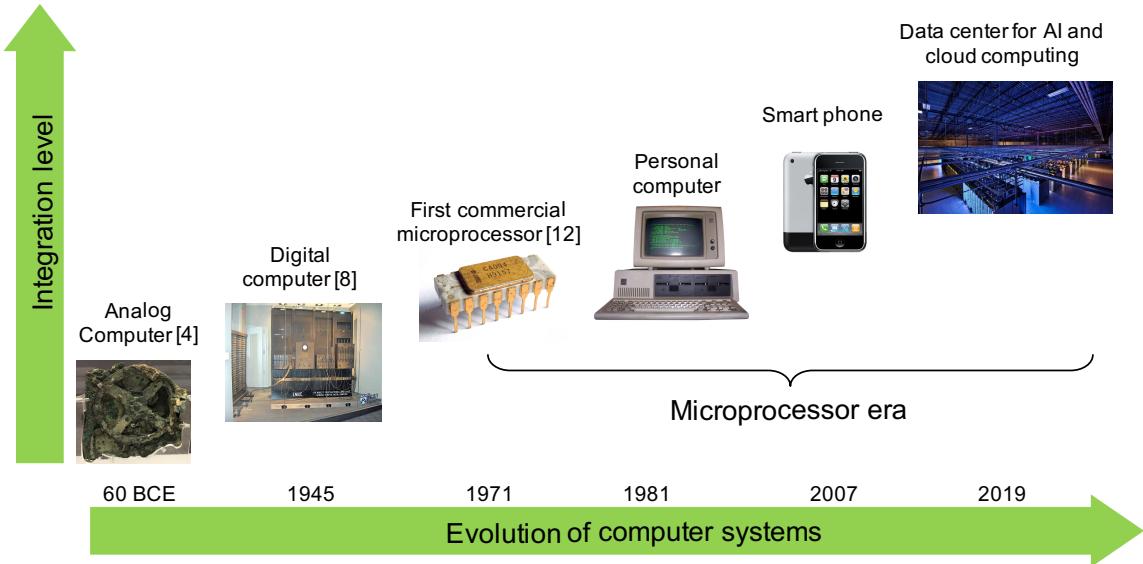

in a digital form. Eleven years after the successful development of the first transistor, the IC was invented and the semiconductor industry was born. The computer industry started to grow rapidly thanks to the development of the semiconductor industry, as illustrated in Figure 1.2.

Computers exhibit increasing performance, smaller footprint, and lower cost than the predecessor versions due to the development of integrated circuit semiconductor technology. It was not until the 1970's that the personal computer was introduced and the digital revolution began to change the life of common people. Early in the development of the microprocessor, speed was the primary design objective. In the 2000's, with the assistance of the Internet, smart phones started to break the communications barrier among people and between people and information, revolutionizing the daily life of everyone anytime and anywhere. Systems-on-chip (SoC), as the processor

Figure 1.2: Evolution of computer systems from the first analog computer (Antikythera mechanism) to large scale data centers [4, 8, 12].

inside mobile smart phones and other smart portable devices, exhibit quite strict requirements for power, making power the design criterion of fundamental importance [13]. Note that power, as a primary design objective, did not attract significant attention during the early development of microprocessor technology. It was not until the 2000's that power became a challenging issue, becoming the primary bottleneck to performance and area [14]. Multicore microprocessors and power minimization techniques have recently been developed to manage this power challenge [15].

Today, the fourth industrial revolution is upon us. Although the definition of the fourth industrial revolution has not yet been widely agreed upon, it is marked by the development of emerging technologies across a number of fields such as artificial intelligence (AI), the Internet of things (IoT), autonomous vehicles, robotics, 5G

wireless technologies, the brain computer interface (BCI), and so on. The IC industry will continue to play an important role in this fourth industrial revolution, facing both novel and similar challenges in the advancement of technology, such as the ever challenging issue of low power.

For example, it is projected that the number of IoT devices will exceed 20 billion by 2020 [16]. IoT devices typically exhibit the following characteristics: (1) small physical area, (2) communications capability, (3) sensing/actuation modality, and (4) low energy consumption [17]. IoT places extreme limitations on area, reliability, cost, and, importantly, power consumption.

As important technologies of the fourth industrial revolution, AI and machine learning applications are starting to push the limits of computational power in high performance processors. Existing low power techniques have not prevented the growth in power consumption in high performance processors [18]. Data centers for cloud computing are being rapidly developed across the world, consuming significant energy. The power consumption of global data centers was roughly 416 terawatt hours in 2016, more than the electricity consumed by the United Kingdom [16].

The increase in power consumption leads to higher current demand for ICs, challenging the reliability of the power delivery network and the power efficiency of the computer system. Innovative technologies, design methodologies, and integrated platforms across the device, circuit, architectural, and system levels are greatly desired

to tackle this high current challenge either by reducing the current demand of the ICs or by developing ICs that can support high currents. Moreover, 3-D ICs that exploit the vertical dimension provide a platform for heterogeneous integration and greater performance regardless of the CMOS technology node [19]. The dense nature of vertical stacking however makes 3-D ICs highly sensitive to high power, preventing 3-D technology from being used in many high current and high performance applications. The full advantages of 3-D integration can only be exploited if high current 3-D systems are enabled.

The power delivery network within a computer is a complex hierarchical system. Each component within the power delivery network affects the reliability and efficiency of the entire system. An overview of power delivery systems within a computer is therefore presented in the following section.

## **1.2 Power delivery network within a computer system**

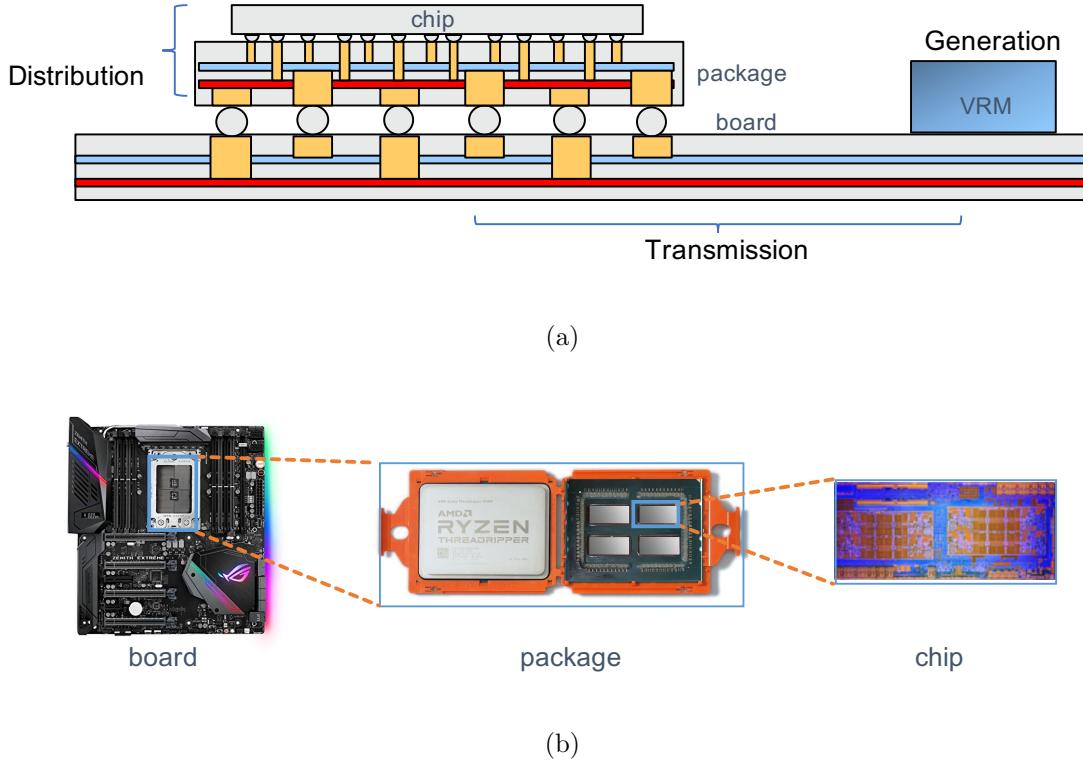

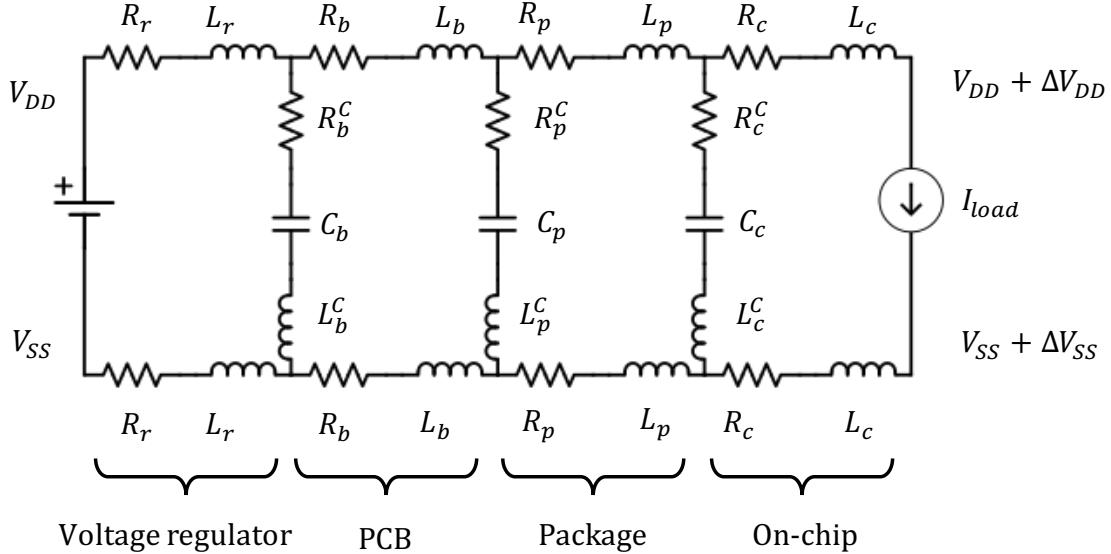

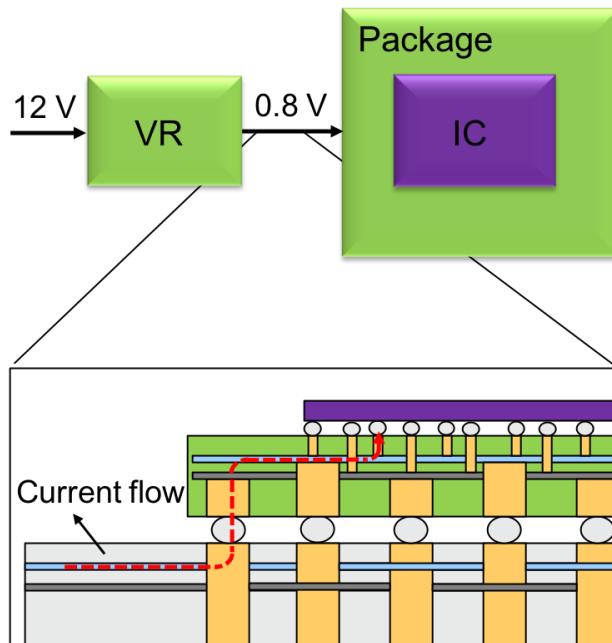

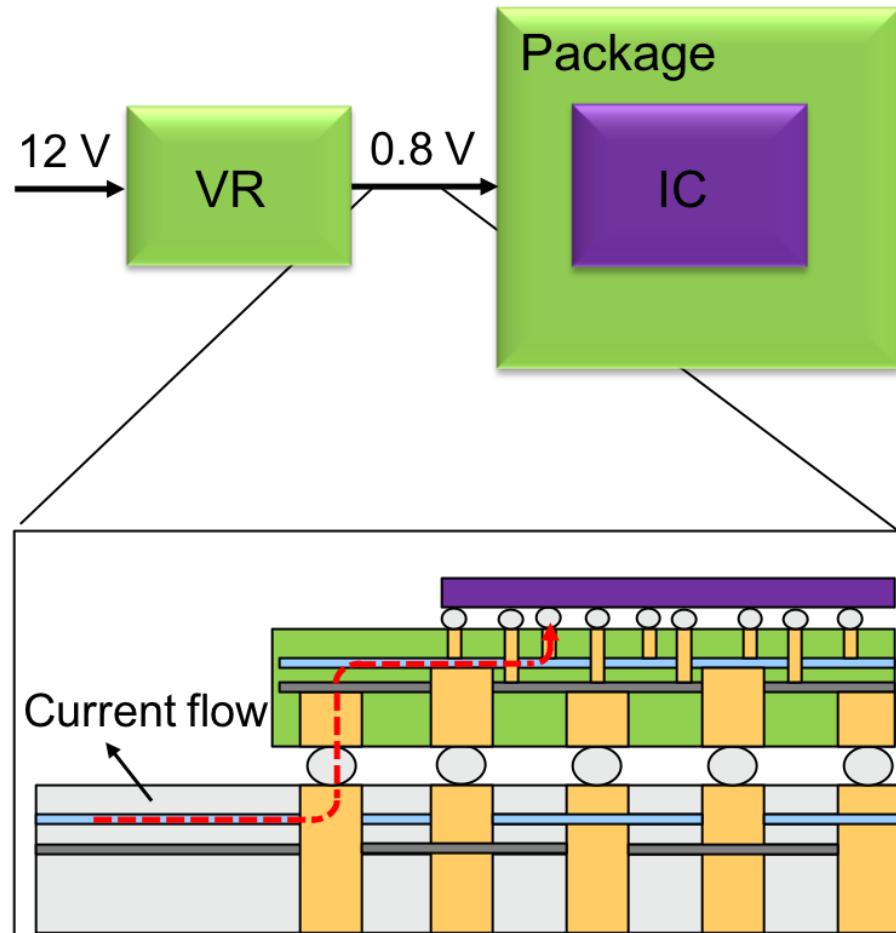

Similar to the electric power grid that generates, transfers, and distributes electricity to many millions of end users, a power delivery network is required within a computer system, as illustrated in Figure 1.3. This power delivery network spans from the voltage regulator module (VRM) to the on-chip load, including the physical

Figure 1.3: Power delivery network within a computer system. a) Cross sectional view, and b) top view of hierarchical power delivery network from VR to on-chip load [20,21]

structures and passive/active devices within the board, package, and IC. A VRM generates power for the system, providing sufficient current at a stable voltage to the load. The power planes within the board transfer power from the VRM to the microprocessor with low loss. The physical structure and devices between the board and on-chip load distribute the power, effectively transferring current from the off-chip power pins to the on-chip load with low energy consumption and small voltage drops.

As a basic component within the power delivery network, a VRM converts a high

DC voltage (for instance, 12 volts) to an on-chip voltage (for instance, 0.8 volts), supporting the proper operation of the microprocessor. The VRM also regulates the output voltage under load variations within the microprocessor. Variations in transient current demand and reduced noise margins have made the VRM design process quite challenging. Important characteristics of a VRM include the form factor, power efficiency, power density, step-down ratio, regulation capability, electromagnetic compatibility, as well as many other attributes.

Three classic topologies of a VRM have been developed, including switching mode power supplies (SMPS), switched capacitor converters, and linear regulators. SMPS requires a large inductor and capacitor to store and transfer power from the input to the load where the time that the passive circuit elements are connected to the input and output are carefully managed. SMPS exhibits high power efficiency and load regulation, making this topology effective for microprocessors. SMPS however requires significant area due to the large inductor, making on-chip integration quite challenging. A switched capacitor converter uses capacitors to store and transfer power. Due to trench capacitor technology, integration of large capacitors within a small area has become more feasible, making a switch capacitor converter a useful candidate for on-chip integration. The load regulation capability is however degraded in switched capacitor converters. Alternatively, a linear regulator uses a variable resistor to divide the input voltage, generating and regulating a steady output voltage.

The small area and excellent load regulation characteristics make linear regulators a good candidate for on-chip integration, although the efficiency is limited to the ratio of the output voltage to the input voltage.

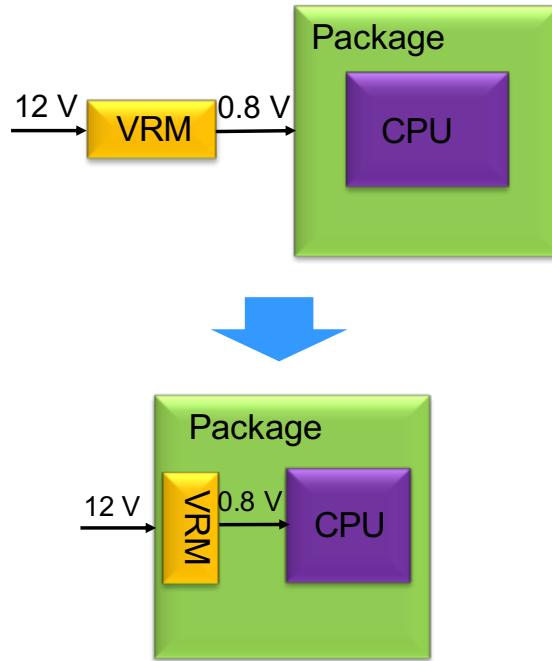

Due to heterogeneous systems integration and reductions in power noise margin, multiple voltage domains and fine grained, fast power management are required. A centralized on-board VRM, far from the on-chip load, is therefore no longer sufficient. Historically, the VRM was located on the printed circuit board due to the large footprint, leading to a large parasitic impedance and significant power loss between the VRM and the on-chip load [13]. On-package and on-chip voltage regulation has therefore been developed to provide higher power efficiency and to enable fast load regulation required for dynamic voltage scaling (DVS) systems. On-chip buck converters are utilized by Intel as a fully integrated voltage regulator (FIVR) in the Haswell processor with advanced packaging technology in which the bulky inductors are also integrated [22]. Distributed linear low dropout regulators (LDO), a type of linear regulator, have been integrated within the IBM POWER8 processor, where core level dynamic voltage frequency scaling (DVFS) is achieved [23].

An efficient power delivery network that provides high quality power to the on-chip load has become a primary concern of the IC design process, in which the on-chip power grid plays a critical role. The on-chip power grid refers to the metal layers that transfer current from the controlled collapse chip connection (C4) to the on-chip

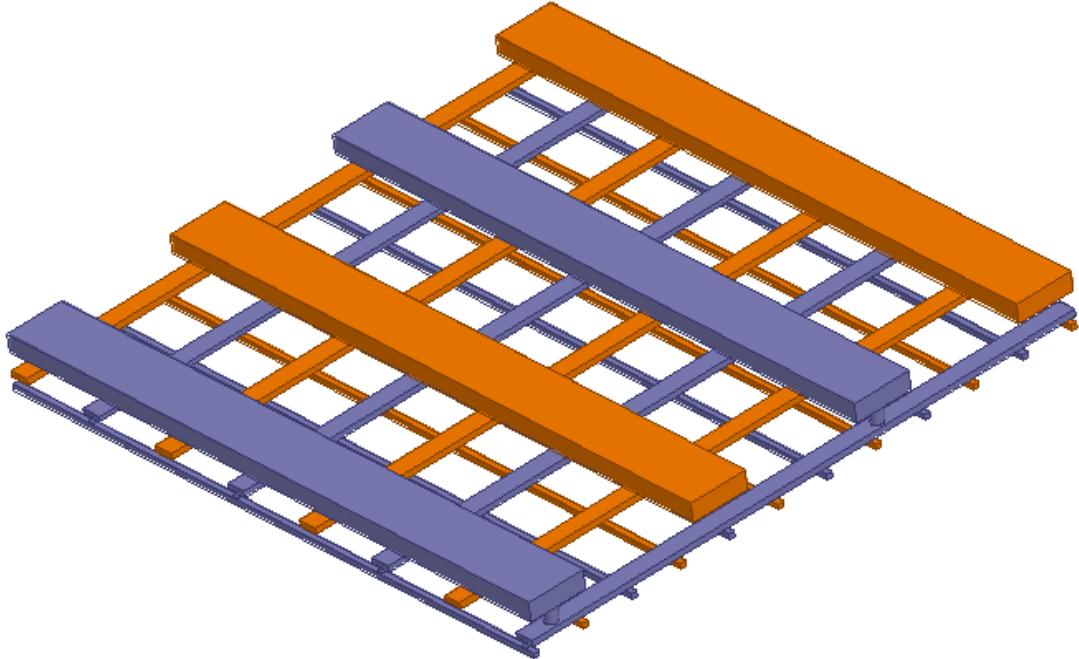

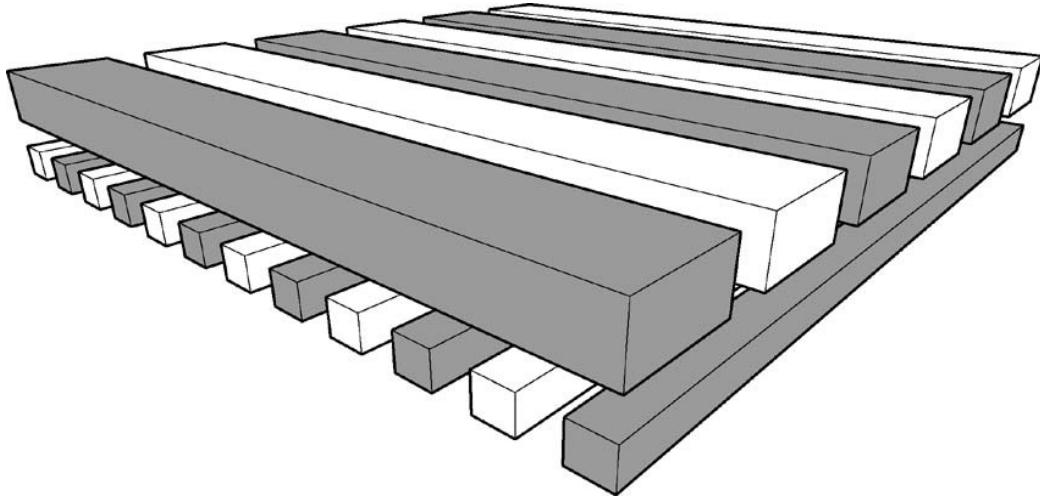

Figure 1.4: A multi-layer interdigitated mesh structured on-chip power grid. The power and ground lines are, respectively, in orange and blue colors.

transistors. The on-chip power grid is the final physical structure that passes current before reaching the load. As illustrated in Figure 1.4, a multi-layer, interdigitated mesh structure is generally utilized in the power grid within high performance ICs to provide significant robustness and lower impedance. With increasing clock frequencies and on-chip transient currents, the inductive power noise within the power grid has become non-negligible [24]. The power grid is typically located within the top metal layers and connected to the local, lower power rails through via stacks. On-chip interconnect scaling has led to thinner and narrower local power rails and via stacks.

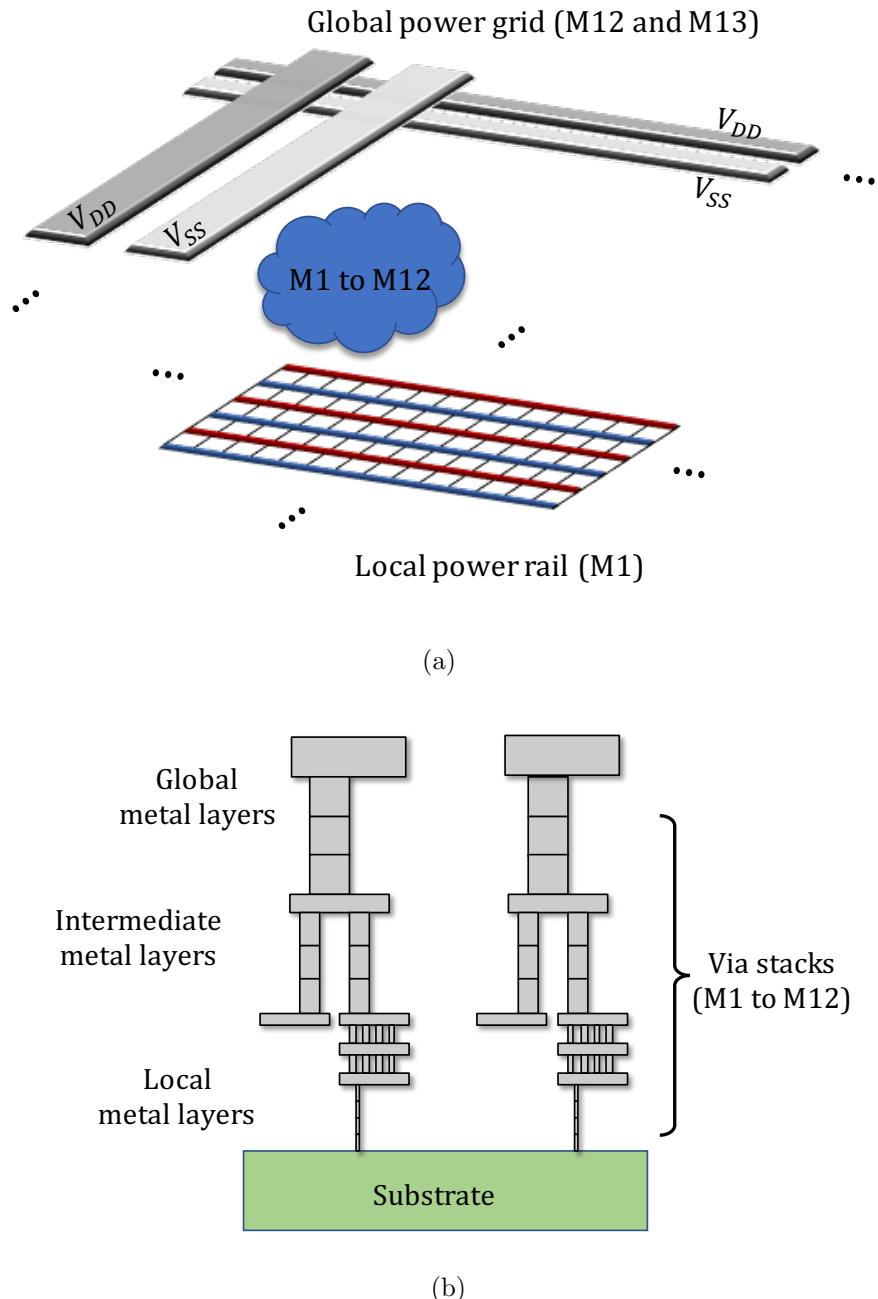

Figure 1.5: Overview of 3-D power delivery network. a) Panoramic view of power/ground TSVs and 2-D power distribution cell within a 3-D IC, and b) related circuit model [25].

The resistivity of the metal line has increased significantly with interconnect scaling. As a result, the local power network is highly resistive, leading to significant resistive power noise. Inductive and resistive power noise together challenges the development of reliable power delivery networks and the proper functionality of the ICs. A breakdown of the power noise based on the hierarchical structure of the on-chip power network is therefore desirable. Suppression schemes targeting different power noise components are also needed [13]. Increases in the performance of microprocessors have slowed and become more costly due to the greater difficulty in scaling CMOS technology.

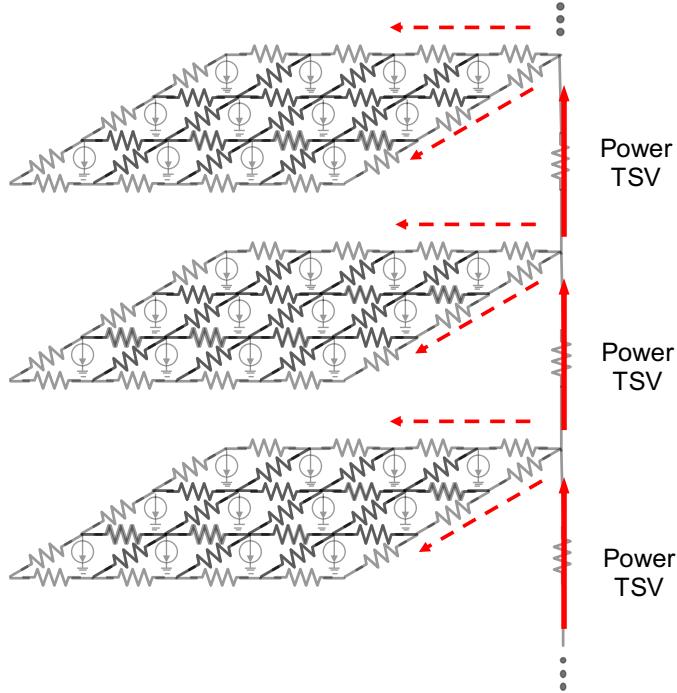

As a platform to enhance performance, multiple ICs are stacked together in the third dimension. Three-dimensional ICs have attracted significant attention within both academia and industry [26–28]. As illustrated in Figure 1.5, the on-chip power delivery network of a 3-D IC is highly sophisticated due to the introduction of power and ground (P/G) through silicon vias (TSVs), the key structure which delivers power vertically to the individual layers. Despite the successful development of 3-D products such as 3-D DRAM memory, high bandwidth memory, and field programmable gate arrays (FPGAs), 3-D ICs suffer from power integrity issues and low power efficiency within the 3-D power delivery network. To enable high power applications of 3-D ICs, improved understanding of the distribution of current within the power delivery network across multiple layers is required. Innovative technologies and design methodologies across circuit and architectural levels that support high current within 3-D power delivery networks is highly desirable to fully exploit the advantages provided by 3-D integration.

### 1.3 Outline

The importance and challenges of developing a reliable power delivery network, supporting high current demand, are presented in this dissertation. In Chapter 2, a breakdown of the physical structure of an on-chip power delivery network within a 2-D IC is presented. The hierarchical power delivery network is divided into a global

power grid, power via stacks, and local power rails. Lumped and distributed models of the power delivery network are described in this chapter. Accurate and efficient simulation engines, supporting large scale power networks, are reviewed. The power delivery network within a 2.5-D and 3-D system is also presented in this chapter. As a key component of a 3-D power delivery network, P/G TSVs require accurate models supporting different circumstances. Closed-form expressions, accurately capturing the impedance of the P/G TSVs in a large array, are presented.

At the system level, processors composed of a large number of cores and providing high throughput are highly desirable for high performance computing (HPC) systems. At the transistor level, dynamic and leakage power consumption do not decrease with standard CMOS scaling. As a result, power consumption continues to increase, leading to significant on-chip current. The challenges of developing a power delivery network, supporting high currents, are therefore discussed in Chapter 3. One challenge, the last inch power loss, is the undesirable power loss from the board to the IC before reaching the on-chip load, which can be significant due to the high current demands of HPC systems. Another classic issue is electromigration, an old problem within the IC community, which challenges the reliability of the power delivery network within HPC systems. Novel materials, mitigating electromigration, are reviewed in this chapter. An architectural technique, voltage stacking, is also introduced, reducing on-chip current demand by adding layers sharing the same current

within a voltage stacked system.

To explore the effects of high current on the power network of advanced technology nodes, several power noise suppression methods utilizing different on-chip metalization schemes are proposed in Chapter 4. An exploratory modeling methodology is presented to estimate power noise in advanced technology nodes. The models are evaluated for the 14, 10, and 7 nm FinFET technology nodes. Power noise is composed of three parts, noise related to the global power grids, via stacks, and local power rails, based on the hierarchical nature of the power distribution network. The components of the on-chip power noise for the 14, 10, and 7 nm technology nodes are compared. Different on-chip metalization schemes are proposed to suppress power noise, including additional global power metal layers, metal stripes, graphene interconnect, and deeply scaling the local power rails. The efficiency of these suppression techniques on different power noise components and technology nodes is also discussed.

One method to mitigate the last inch power loss is to shorten the "last inch" distance by bringing the point-of-load (PoL) converter close to the processor. A voltage regulator (VR)-on-package topology using system-in-package (SiP) technology can effectively reduce the last inch power loss by moving the PoL converter from the board to the package. To further decrease the last inch power loss, a high step-down ratio within the PoL converter is utilized. In this way, high voltage transmission is achieved between the PoL converter and processor, leading to less current passing

through the power delivery network. Electromagnetic interference (EMI) however has become more challenging due to the close proximity of the components within an SiP environment and the higher voltage levels within the package. A distributed resonant converter that supports a high step-down ratio and low EMI is described in Chapter 5. The converter exhibits a stable load voltage with less than 4% ripple and a fast transient response of less than 1  $\mu$ s. More than 3X lower EMI in the distributed resonant converter is demonstrated as compared with a single branch resonant converter using the same step-down ratio.

As previously mentioned, a VR-on-package is a promising topology which supports high voltage transmission within a printed circuit board and package, leading to lower distribution loss. A study of VR top and bottom placement topologies within a system-in-package environment in terms of EMI and power integrity is presented in Chapter 6. This comparative analysis targets a specific server package application, and evaluation of the power integrity focuses on the power delivery network between the VR and IC. The VR top placement topology exhibits more than 3X less EMI, and 15.3% lower worse case IR drop as compared with the VR bottom placement topology. The tradeoffs are however a larger power loss within the package and higher cost of the package due to the greater number of package layers required by the VR top placement topology. The VR top placement topology exhibits 52.6% higher power loss than the VR bottom placement topology.

Insights and design guidelines to mitigate high current challenges within HPC systems are presented in this dissertation. Due to the high bandwidth and power efficiency characteristics, silicon photonics, as a candidate for HPC systems, has attracted significant attention from both industry and academia. In a silicon photonic system, hundreds of photonic components are connected by waveguides, inevitably forming waveguide crossings within a limited area. Insertion loss due to the placement of these multiple waveguide crossings are discussed in Chapter 7. Existing metrics for determining the total signal loss are shown to be inaccurate since these metrics ignore the location of the waveguide crossings. Three experiments with different waveguide crossing locations are evaluated using 3-D finite difference time domain analysis. It is observed that the location of a waveguide crossing, the relative location of two crossings, and the total number of crossings within a system affect the loss per crossing. Bloch wave and multimode interference are subsequently introduced to explain this phenomenon.

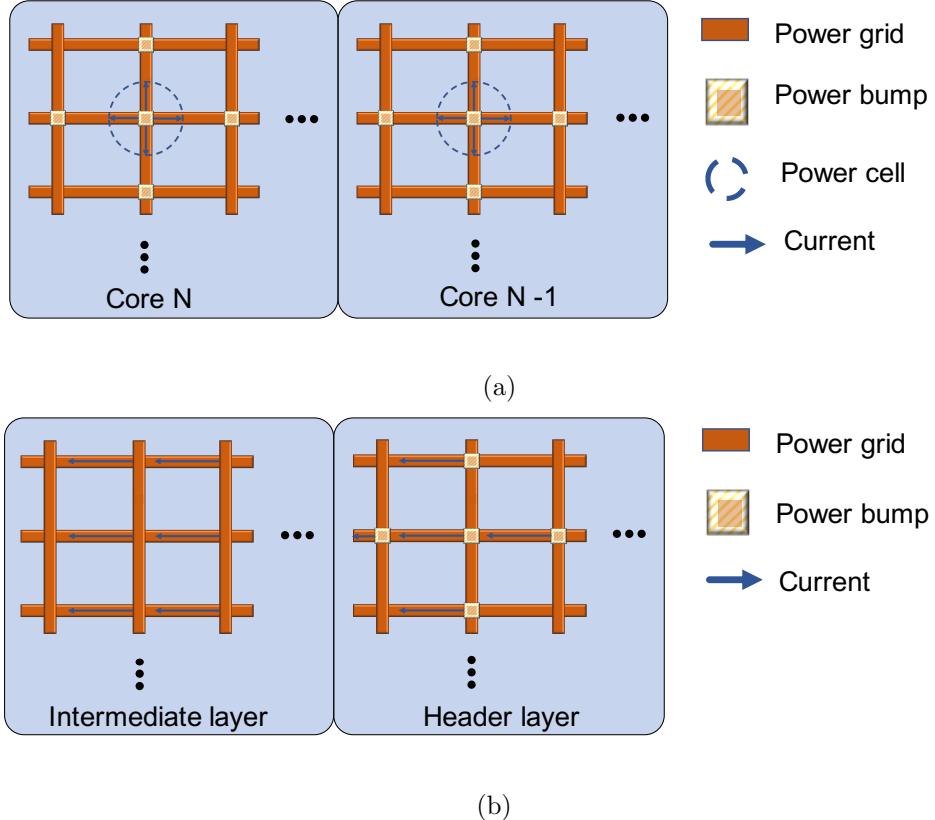

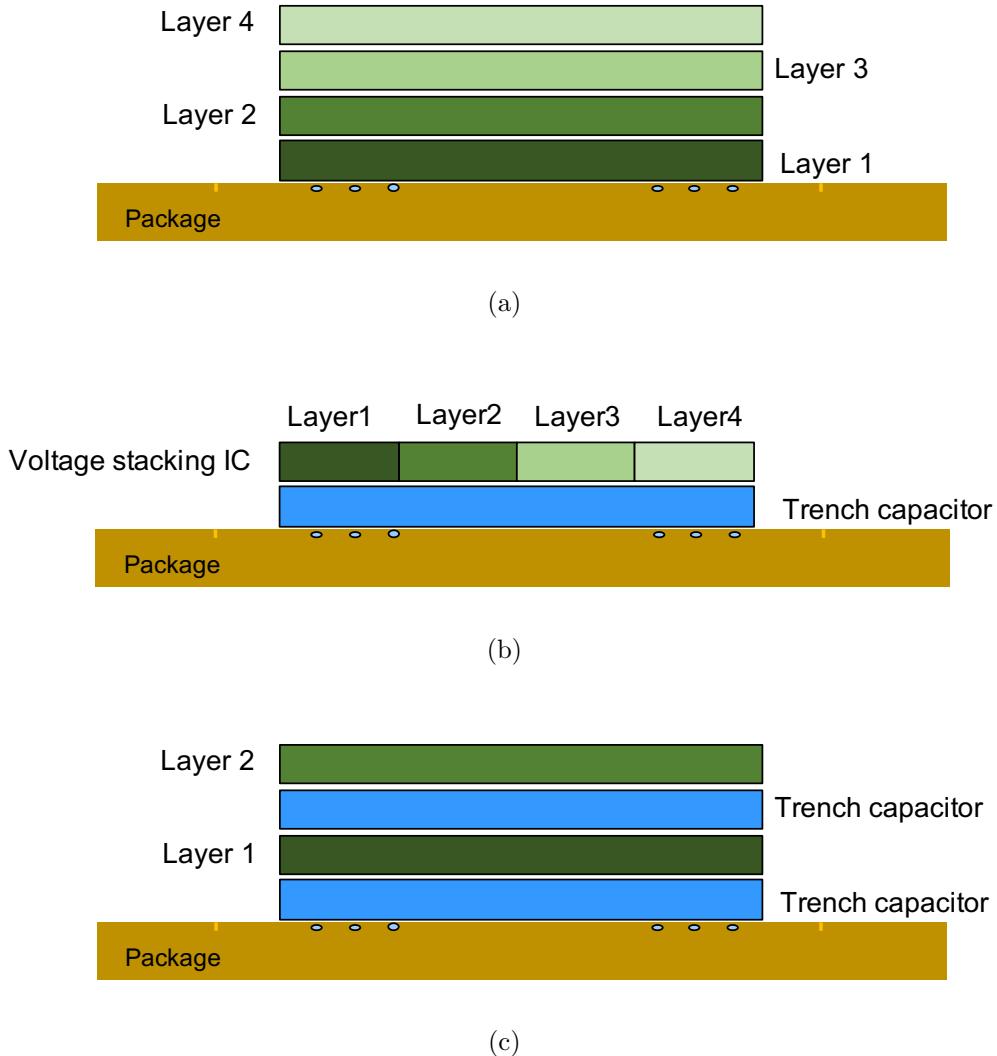

3-D ICs exploit the vertical dimension, providing a promising method to extend scaling. The previously mentioned high current issues are however more challenging in 3-D ICs than in 2-D ICs, preventing the application of a 3-D platform to HPC systems. As a key factor affecting current distribution in 3-D ICs, the redistribution layer (RDL) has to date received little attention from the research community. Oversimplified assumptions regarding RDLs are made such as a perfect TSV-to-TSV

match between adjacent layers, or simple metal stripe connections between the TSVs and 2-D power grid. A comprehensive evaluation of RDLs with different TSV fabrication methods and 3-D stacking topologies is provided in Chapter 8. A circuit model of an RDL is described to provide insight into the effects of two types of RDLs on intra-layer and inter-layer power distribution networks. A novel grid-based RDL topology is also proposed to suppress voltage drops in 3-D power networks, supporting fewer TSVs and high current demand. It is also observed that a grid-based RDL topology is an excellent candidate for managing certain issues such as nonuniform TSV distribution and TSV mismatch.

Multiple methods have been introduced to alleviate high current issues without reducing the demand for current. Voltage stacking has become a topic of growing interest as a technique to reduce on-chip current. The challenge of load imbalances within voltage stacked systems is however significant. Existing work to manage load imbalances focus on two directions: (1) utilizing circuit, architectural, or scheduling methods to reduce the likelihood or magnitude of a load imbalance, and (2) given specific load imbalance profiles, utilize a power converter to mitigate voltage variations due to load imbalances. The power delivery network for voltage stacked systems, despite being critical, has to date received minimal attention. The challenges of a voltage stacked power network to support multiple voltage domains, high current demand, and exotic load balancing circuits are explored in Chapter 9. It is observed

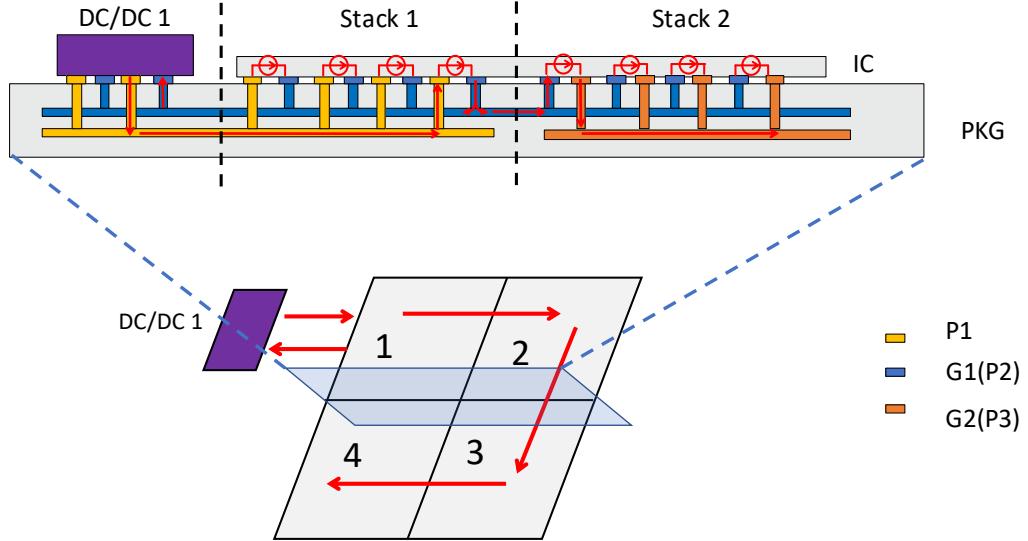

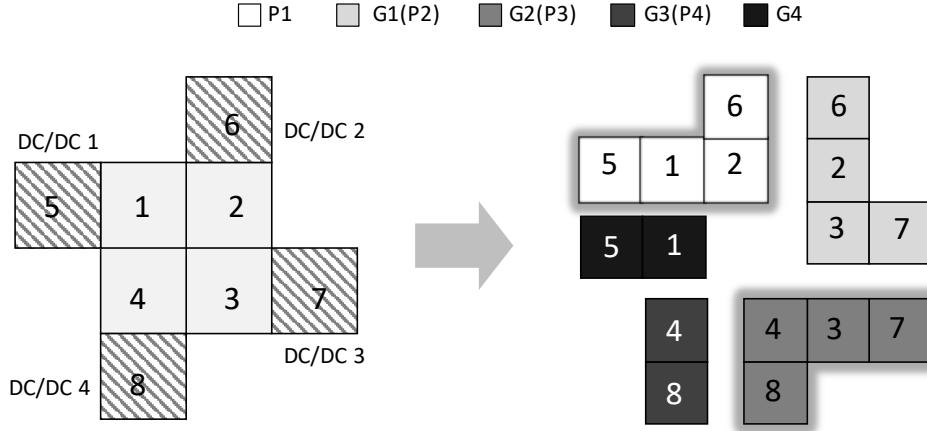

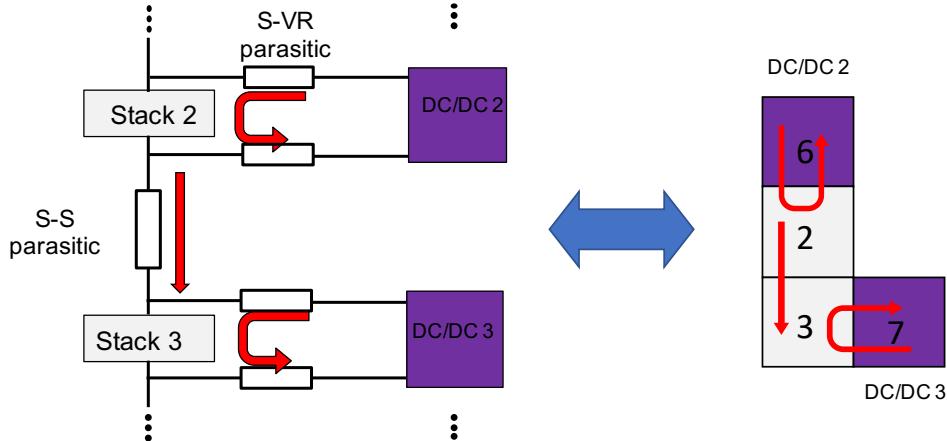

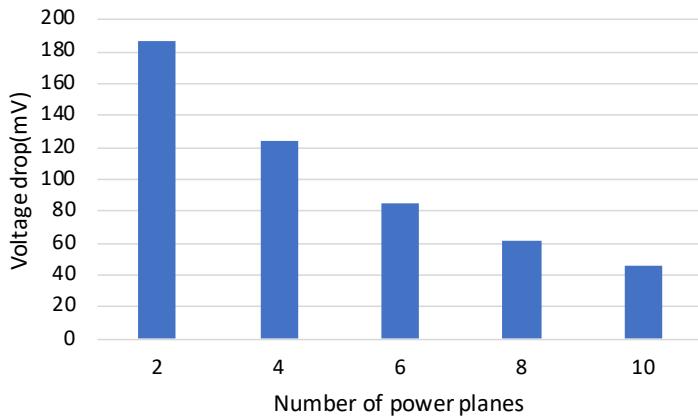

that the parasitic impedance of the power network in voltage stacked systems significantly affects the power integrity as compared with conventional 2-D power networks. Characterization of the parasitic impedance within the power network is therefore discussed for both stack-to-bus and stack-to-stack topologies. A case study of a power network for voltage stacked systems is also described in this chapter.