#### Delay Uncertainty in High Performance Clock Distribution Networks

by

Dimitrios Velenis

Submitted in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Supervised by Professor Eby G. Friedman

Department of Electrical and Computer Engineering School of Engineering and Applied Sciences The College

> University of Rochester Rochester, New York

> > 2003

UMI Number: 3102306

#### UMI Microform 3102306

Copyright 2003 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

### Dedication

To my family, my parents Stamatios and Penelopi, my brother Patroklos, and my wife Andreia Marina who brings all the happiness in my life.

### Curriculum vitae

The author was born in Kavala, Macedonia, Greece on July 22, 1974. He attended the Technical University of Crete, in Chania Greece, from 1993 to 1998 and graduated in July of 1998 with a Bachelor of Science degree in Electronics and Computer Engineering. He came to the University of Rochester in August of 1998, and began graduate studies at the Department of Electrical and Computer Engineering. He received his Masters of Science degree in May 2000. He performed research with Intel Corporation, Santa Clara, CA in 1999 and with IBM Corporation at Austin Research Lab, Austin, TX in 2001. From 1998 to 2003, he pursued research in very large scale integrated circuits under the direction of Professor Eby G. Friedman, in the areas of timing optimization and noise effects in high performance synchronous integrated circuits with emphasis in the design of multi-gigahertz clock distribution networks.

### Acknowledgements

I would like to express my most sincere feelings of gratitude to my academic advisor, Professor Eby G. Friedman, for his enthusiastic encouragement and enlightment during all my years as a doctoral student. His inexhaustible dedication and enthusiasm have become the source of my inspiration, while his brilliant research ideas earned my deepest respect. In addition, he has been a great mentor for me, having a human interest for many aspects of my life. I wish I will be able to give to the people around me just a fraction of the motivation and support that Professor Friedman has offered me. I would like to wish to Professor Friedman to offer this opportunity to many more students in the future.

I am also deeply indebted to Professor Marios C. Papaefthymiou for his sound contribution in my research effort. His determination, clear focus, and capability to formulate complicated problems were great assets during the development of the work presented in this dissertation. My collaboration with him was a very productive, and at the same time, enjoyable experience.

I would also like to thank Professors David Albonesi, John C. Lambropoulos, and Martin Margala for serving in my committee and for their influence and suggestions regarding my work. I am also grateful to the entire faculty, staff, and students of the Department of Electrical and Computer Engineering for putting their hearts into filling everyday life with excitement and joy. Special thanks to Profes-

sor Alexander Albicki, Amy Freitas, Maureen Muar, Debra Neiner, Jim Prescott, Yana Shinkman, John Simonson, Melissa Singkhamsack, and John Strong.

In particular, I would like to recognize the contribution of the people that we shared together the whole experience. I would like to thank all the members of the High Performance VLSI/IC Design and Analysis Laboratory for the unforgettable moments we had together. It was an honor for me to work in the same team with Volkan Kursun, Andrey Mezhiba, Boris Andreev, Magdy El-Moursy, Dr. Ivan Kourtev, Dr. Tianwen (Kevin) Tang, Dr. Yehea Ismail, Dr. Radu Secareanu, Dr. Victor Adler, Weize Xu, Junmou Zhang, Mikhail Popovich, Guoqing Chen, Jonathan Rosenfeld, and Vasilis Pavlidis. Special thanks to Mrs. RuthAnn Williams for the true love and the great joy she offered to us in every single day.

I would also like to thank all my friends for all the great time we had together that became wonderful memories. It was a great pleasure to meet with Dimitrios Katsis, Christos Koulouvatianos, Grigoris Maglis, Thanos Papathanasiou, Stephanos Nitodas, Panagiotis Kambylafkas, and Manos Fitrakis.

Finally, I would like to thank my family for their unconditional love, support, and understanding. They have always been on my side, teaching me to challenge life and believe in myself. To my loving wife Andreia Marina—I am really blessed to share my life with you. Thank you for your ocean of love and support. You are my inspiration and my source of happiness, I wouldn't have made it without you.

This work was supported in part by the Semiconductor Research Corporation under Contract No. 99-TJ-687, and No. 2003-TJ-1068, the DARPA/ITO under AFRL Contract F29601-00-K-0182, grants from the New York State Office of Science, Technology & Academic Research to the Center for Advanced Technology - Electronic Imaging Systems and to the Microelectronics Design Center, and

by grants from Xerox Corporation, IBM Corporation, Intel Corporation, Lucent Technologies Corporation, Eastman Kodak Company and Photon Vision Systems, Inc.

#### **Abstract**

The effect of noise on circuit operation and reliability has become an important issue in the design of high performance integrated circuits. The main effect of noise is the degradation of signal integrity causing uncertainty in the signal delay. The uncertainty of the propagation delay of a signal can cause a catastrophic violation of the timing constraints within a system.

One way to improve the tolerance of a system to delay uncertainty is by relaxing the timing constraints of the critical paths. A methodology that implements this concept by applying non-zero clock skew scheduling is described. Furthermore, a variation of this methodology is presented that reduces the power dissipated in the fast data paths of a system.

One of the most critical signals in a synchronous digital circuit is the clock signal. It is important to reduce the uncertainty of the clock signal delay, particularly of the clock signals driving the registers belonging to the most critical data paths. A methodology that controls the topology of the clock tree so as to improve the tolerance of the clock signal to delay uncertainty is described. The primary target of that methodology is to reduce the non-common portion of the clock tree among the clock paths that drive the registers of the most critical data paths. An algorithm that implements this methodology and extracts the clock tree topology is presented. The application of the algorithm to a set of bench-

mark circuits demonstrates a significant reduction in the delay uncertainty of the clock signal in the most critical data paths.

Furthermore the effect of layout design elements on the delay uncertainty of the clock signal is considered. The delay uncertainty introduced by device parameter variations and interconnect crosstalk is investigated. It is demonstrated that increasing the size of the clock buffers reduces the effects that introduce delay uncertainty, albeit with increasing the power dissipation on the clock tree. The dependence of delay uncertainty upon physical characteristics is leveraged in the development of a methodology for clock tree physical layout design. The developed methodology utilizes buffer insertion and layout enhancement techniques to reduce the delay uncertainty of the clock signal to the registers of the most critical data paths. The primary tradeoff in the application of the proposed techniques is between the power dissipation and total area of a clock distribution network.

# Contents

| D            | edica | tion   |                    |            |           |          |        |        |                | ii     |

|--------------|-------|--------|--------------------|------------|-----------|----------|--------|--------|----------------|--------|

| C            | urric | ulum ' | Vitae              |            |           |          |        |        |                | iii    |

| $\mathbf{A}$ | ckno  | wledge | $\mathbf{e}$ ments |            |           |          |        |        |                | iv     |

| A            | bstra | ıct    |                    |            |           |          |        |        |                | vii    |

| Li           | st of | `Table | S                  |            |           |          |        |        |                | xii    |

| Li           | st of | `Figur | es                 |            |           |          |        |        |                | xiv    |

| 1            | Inti  | roduct | ion                |            |           |          |        |        |                | 1      |

| 2            | Del   | ay Un  | certainty          | y in Hig   | gh Spee   | d CM(    | OS Cia | rcuits |                | 8      |

|              | 2.1   | Variat | tions of C         | MOS de     | vice para | ameters  |        |        |                | <br>10 |

|              |       | 2.1.1  | Effective          | e channe   | el length | variatio | on     |        | . •<br>• • • • | <br>10 |

|              |       | 2.1.2  | Variatio           | ons in ca  | rrier mol | oility   |        |        |                | <br>13 |

|              |       | 2.1.3  | Variatio           | ons in the | e gate ox | ide thic | ckness |        |                | <br>15 |

|              |       | 2.1.4  | Thresho            | old volta  | ge variat | ion .    |        |        |                | <br>16 |

|              | 2.2   | Variat | tions in ir        | iterconn   | ect parar | neters   |        |        |                | <br>22 |

|   | 2.3  | Interconnect noise                                 | · · · · · · · · · · · · · · · | 25  |

|---|------|----------------------------------------------------|-------------------------------|-----|

|   |      | 2.3.1 Capacitive interconnect coupling             |                               | 25  |

|   |      | 2.3.2 Inductance effects                           |                               | 27  |

|   | 2.4  | Variations in system parameters                    |                               | 30  |

|   |      | 2.4.1 Power supply fluctuations - $IR$ drops       |                               | 30  |

|   |      | 2.4.2 Electromagnetic Interference (EMI) effects   |                               | 32  |

|   |      | 2.4.3 Temperature variations                       |                               | 34  |

|   | 2.5  | Conclusions                                        |                               | 34  |

| 3 | Per  | rformance Enhancements Through Clock Skev          | w Scheduling                  | 36  |

|   | 3.1  | Improving the Timing Constraints and Speed         |                               | 37  |

|   |      | 3.1.1 Background on clock skew scheduling          |                               | 37  |

|   |      | 3.1.2 Optimal clock skew schedule algorithm imp    | olementation                  | 42  |

|   |      | 3.1.3 Experimental results from application of opt | timum clock skew              |     |

|   |      | scheduling                                         |                               | 45  |

|   | 3.2  | Reducing Power in Non-Critical Data Paths          |                               | 49  |

|   |      | 3.2.1 The general technique and related delay co   | nstraints                     | 50  |

|   |      | 3.2.2 Application to critical data paths           |                               | 53  |

|   |      | 3.2.3 Results on a demonstration circuit           |                               | 55  |

|   | 3.3  | Conclusions                                        | • • • • • • • •               | 5.7 |

| 4 | Clo  | ock Tree Topological Enhancements to Reduc         | ce Delay Uncer-               |     |

|   | tair | ${f nty}$                                          |                               | 59  |

|   | 4.1  | Concept of the Algorithm                           |                               | 60  |

|   | 4.2  | Description of the Algorithm                       |                               | 64  |

|   | 4.3  | Incorporating non-zero clock skew scheduling       |                               | 66  |

|              |       |                                                                  | xi  |

|--------------|-------|------------------------------------------------------------------|-----|

|              | 4.4   | Experimental results                                             | 69  |

|              | 4.5   | Conclusions                                                      | 72  |

| 5            | Buf   | fer Sizing for Reduced Delay Uncertainty                         | 73  |

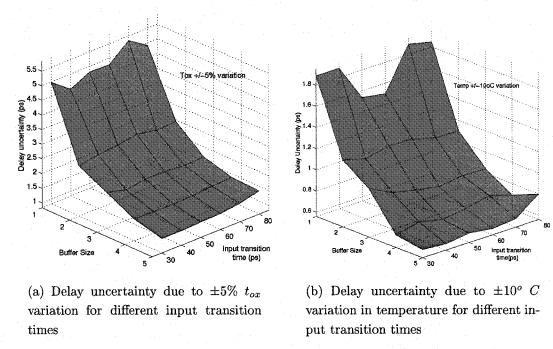

|              | 5.1   | Delay uncertainty due to device parameter variations             | 75  |

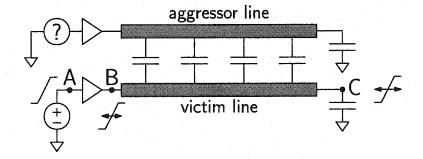

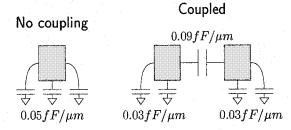

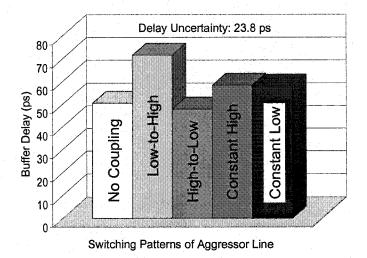

|              | 5.2   | Delay uncertainty due to interconnect crosstalk                  | 82  |

|              | 5.3   | Power dissipation tradeoffs                                      | 89  |

|              | 5.4   | Conclusions                                                      | 92  |

| 6            | Clo   | ck Tree Buffer Insertion and Layout Enhancements                 | 93  |

|              | 6.1   | Buffer insertion and sizing                                      | 94  |

|              | 6.2   | Dedicated minimal clock tree driving the critical path registers | 100 |

|              | 6.3   | Conclusions                                                      | 104 |

| 7            | Con   | aclusions                                                        | 105 |

| 8            | Fut   | ure Research                                                     | 110 |

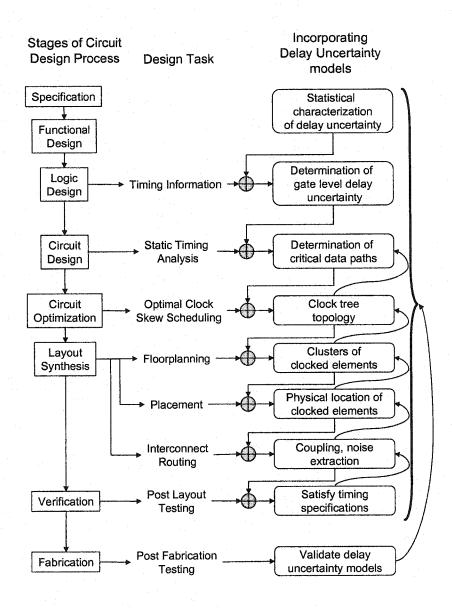

|              | 8.1   | Incorporating delay uncertainty into the design flow             | 111 |

|              | 8.2   | Design techniques for reducing delay uncertainty                 | 114 |

|              |       | 8.2.1 Tapered buffer insertion for delay balancing               | 114 |

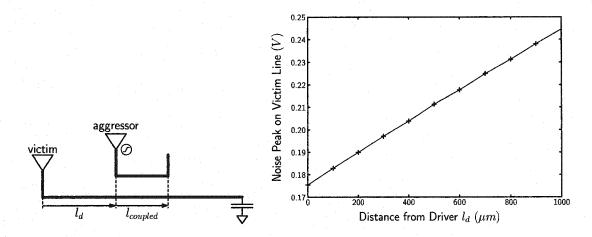

|              |       | 8.2.2 Shielding of clock lines                                   | 116 |

|              | 8.3   | New design trends and challenges                                 | 118 |

| Re           | efere | nces                                                             | 119 |

| A            | Clo   | ck Tree Layouts                                                  | 127 |

| В            | Des   | ign Example                                                      | 135 |

| $\mathbf{C}$ | Puh   | dications                                                        | 138 |

## List of Tables

| 2.1 | Parameter values for electron and hole carriers at 300° K             | 14  |

|-----|-----------------------------------------------------------------------|-----|

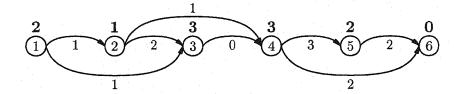

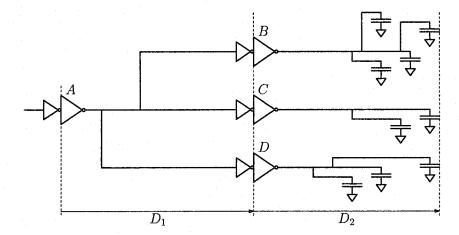

| 3.1 | Comparison between the original and the increased delay of data       |     |

|     | paths B, C, and D within the FUB illustrated in Fig. 3.6              | 56  |

| 3.2 | Normalized power dissipation within the circuit block containing      |     |

|     | the latches                                                           | 56  |

| 4.1 | Reduction in delay uncertainty of the most critical data paths. BF    |     |

|     | describes the branching factor of the original binary tree            | 71  |

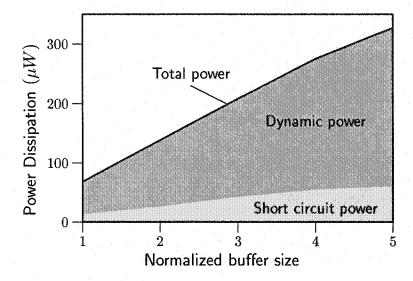

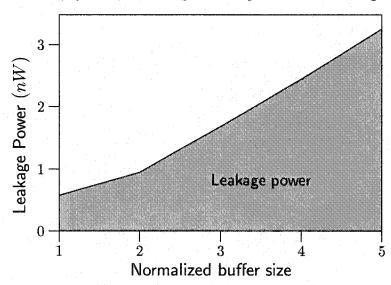

| 5.1 | Transistor size and power dissipation components for different buffer |     |

|     | sizes                                                                 | 89  |

| 6.1 | Increase in power dissipation with increasing buffer size             | 100 |

| 6.2 | Tradeoff between the reduction in power dissipation and the in-       |     |

|     | crease in clock tree area                                             | 103 |

| 6.3 | Comparison between the reduction in power dissipation and the         |     |

|     | reduction in the aggregate buffer size                                | 104 |

| B.1 | Application | of different | design  | techniques to | manage de | elay uncer- |     |

|-----|-------------|--------------|---------|---------------|-----------|-------------|-----|

|     | tainty      |              | • • • • |               |           |             | 136 |

# List of Figures

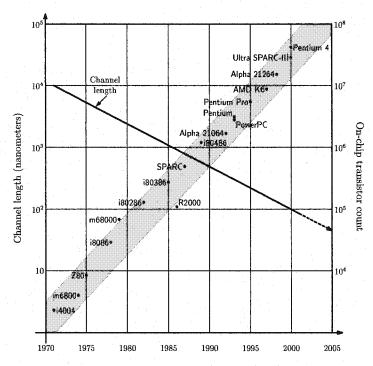

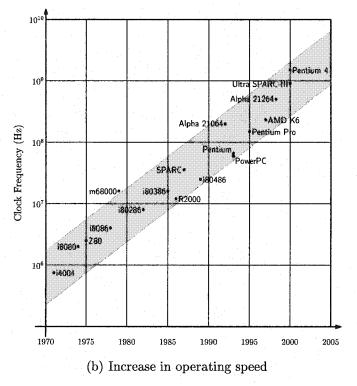

| 1.1  | Evolution of the microprocessor since the 1970's                           | 3  |

|------|----------------------------------------------------------------------------|----|

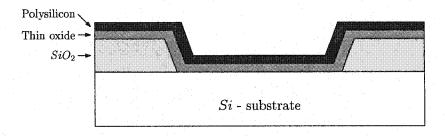

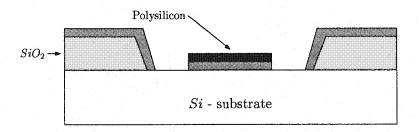

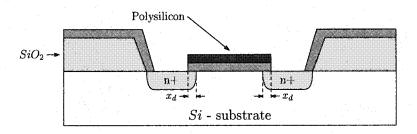

| 2.1  | Basic steps of the transistor source and drain creation process            | 11 |

| 2.2  | $V_{SB}$ variations due to floating sources along the N-channel tree       |    |

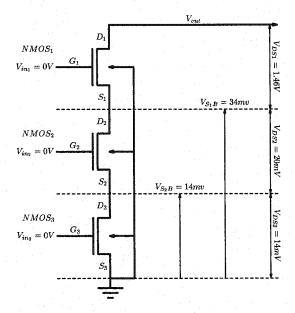

|      | portion of a three input NAND gate                                         | 19 |

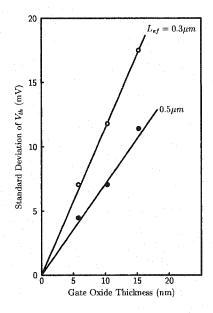

| 2.3  | Standard deviation of $V_{th}$ as a function of $t_{ox}$                   | 20 |

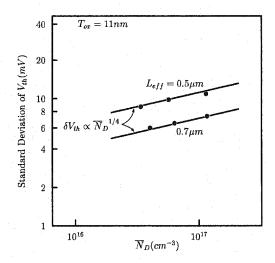

| 2.4  | Standard deviation of $V_{th}$ as a function of doping concentration .     | 21 |

| 2.5  | Geometric parameters of the interconnect lines                             | 22 |

| 2.6  | Copper line thickness losses due to dishing and erosion effects            | 24 |

| 2.7  | Variation in ILD thickness due to different pattern density of inter-      |    |

|      | connect lines                                                              | 24 |

| 2.8  | Capacitive coupling among different interconnect layers                    | 26 |

| 2.9  | Capacitively coupled net                                                   | 27 |

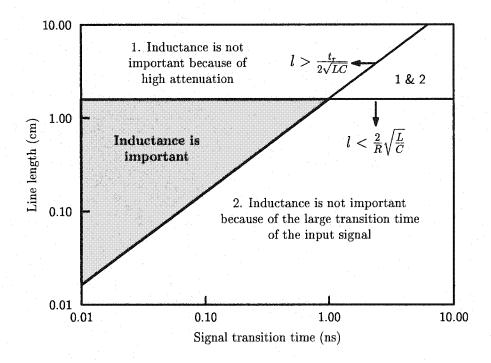

| 2.10 | Transition time $(t_r)$ versus the length of the interconnect line $(l)$ . |    |

|      | The shaded area denotes the region where inductance is important           | 29 |

| 2.11 | Voltage drop due to the resistance within the power distribution           |    |

|      | network                                                                    | 31 |

| 2.12 | EMI-induced delay versus EMI phase differences for a logic transition      | 33 |

| 3.1  | A local data path                                                      | 38         |

|------|------------------------------------------------------------------------|------------|

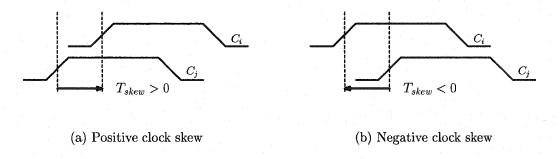

| 3.2  | Examples of positive and negative clock skew                           | 39         |

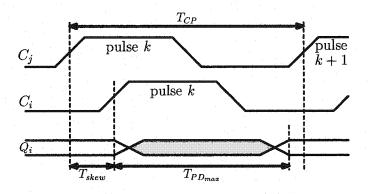

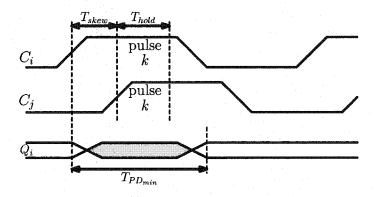

| 3.3  | Preventing timing hazards in synchronous digital systems               | 41         |

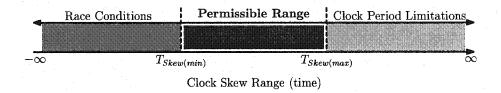

| 3.4  | Clock skew permissible range.                                          | 42         |

| 3.5  | The minimum clock period extraction algorithm                          | 43         |

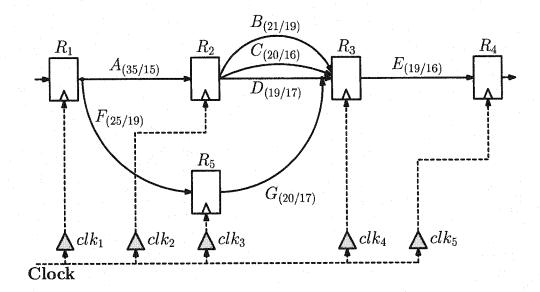

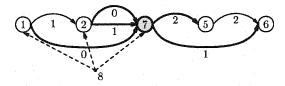

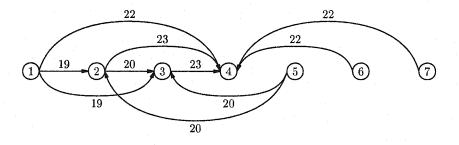

| 3.6  | Circuit graph of Itanium $^{TM}$ FUB with normalized data path delays. | 46         |

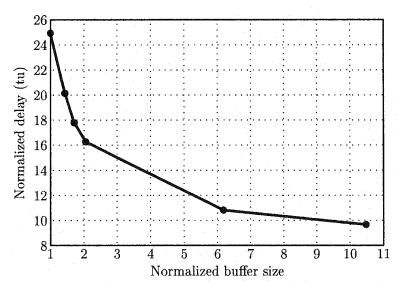

| 3.7  | Variation of clock signal delay to different clock buffer sizes        | 48         |

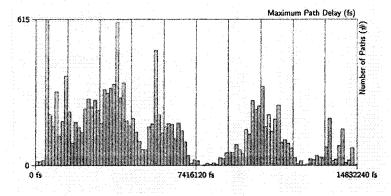

| 3.8  | Path delay distribution with zero clock skew scheduling                | 50         |

| 3.9  | Increasing the delay of the fast data paths by downsizing the local    |            |

|      | latches that drive these paths                                         | 51         |

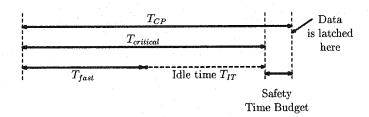

| 3.10 | The added delay of the fast data path should not violate the long      |            |

|      | path timing constraint                                                 | 52         |

| 3.11 | Application of local clock skew to equalize the available idle time    |            |

|      | between the long and short delay data paths. (a) Initial timing of     |            |

|      | the data paths. (b) Timing of the data paths after the application     |            |

|      | of local clock skew                                                    | <b>5</b> 4 |

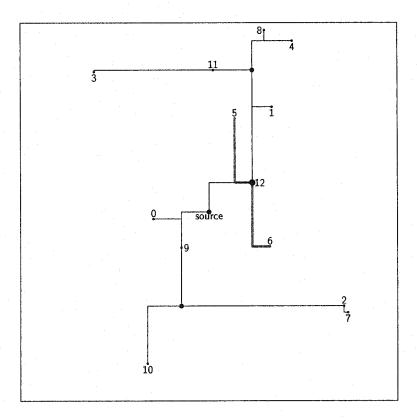

| 4.1  | Introduction of different clock signal delays to the non-common        |            |

|      | portions of the clock tree.                                            | 61         |

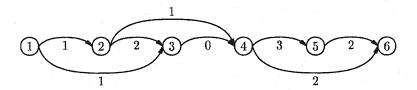

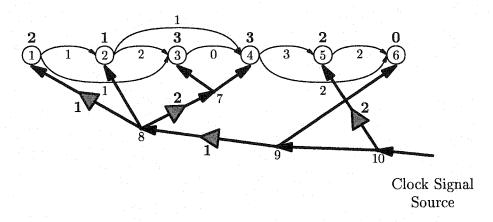

| 4.2  | Uncertainty graph representation of a circuit.                         | 62         |

| 4.3  | Clock tree topology for the circuit shown in Fig. 4.2                  | 63         |

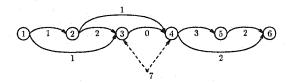

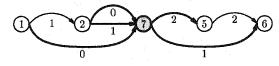

| 4.4  | Iterations of the algorithm to reduce the input graph to a single      |            |

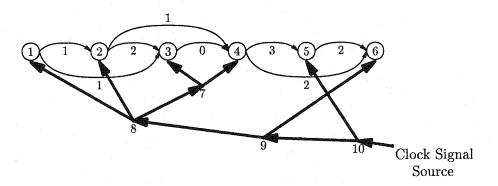

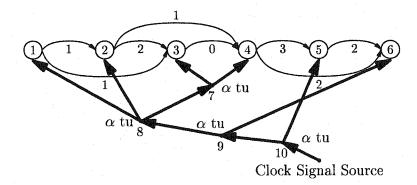

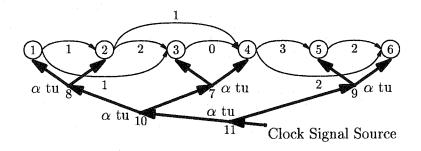

|      | node                                                                   | 65         |

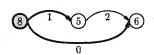

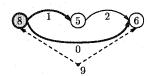

| 4.5  | Incorporating non-zero clock skew scheduling within the CTT al-        |            |

|      | gorithm                                                                | 68         |

| 4.6  | Comparison between the algorithmically extracted CTT and a bi-            |    |

|------|---------------------------------------------------------------------------|----|

|      | nary tree                                                                 | 70 |

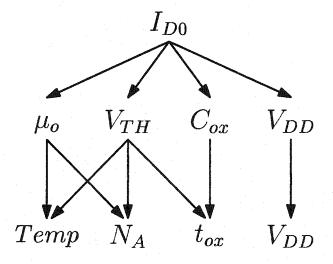

| 5.1  | Dependence of device parameters on process, environmental, and            |    |

|      | system parameters                                                         | 78 |

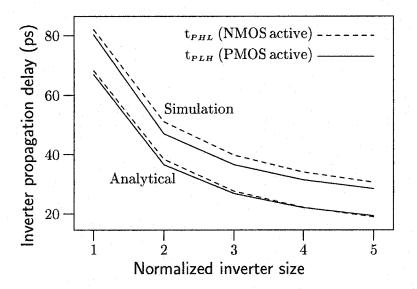

| 5.2  | Reduction in delay with increasing inverter size                          | 79 |

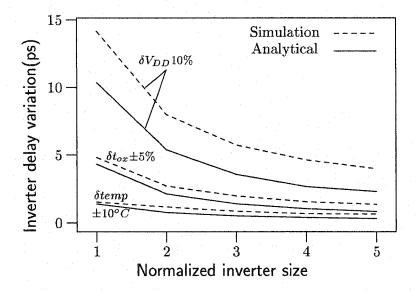

| 5.3  | Uncertainty in inverter delay due to process, environmental, and          |    |

|      | system parameter variations                                               | 80 |

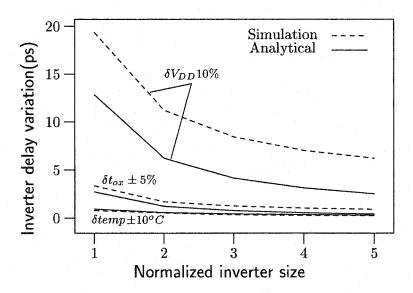

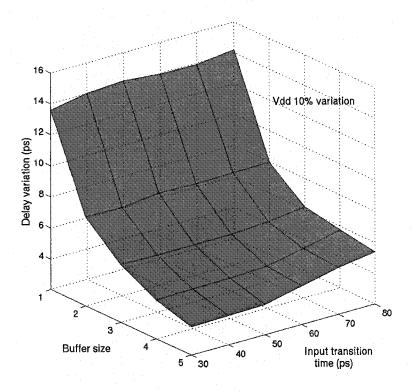

| 5.4  | Delay uncertainty due to 10% $V_{dd}$ variation for different input tran- |    |

|      | sition times                                                              | 81 |

| 5.5  | Effect of input signal transition time $t_T$ on delay uncertainty         | 82 |

| 5.6  | Capacitive coupling between two interconnect lines                        | 84 |

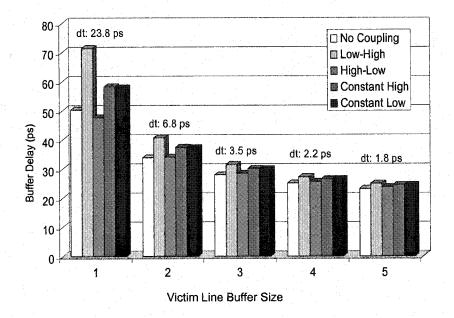

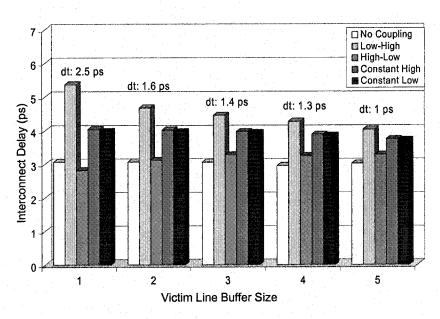

| 5.7  | Simulation of capacitively coupled interconnect                           | 85 |

| 5.8  | Uncertainty of the signal delay of the buffer driving the victim          |    |

|      | line due to different switching activities of the aggressor line. Low     |    |

|      | coupling between the interconnect lines is considered                     | 86 |

| 5.9  | Reduction in delay uncertainty along the victim line with increasing      |    |

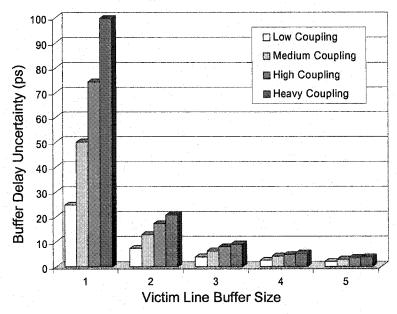

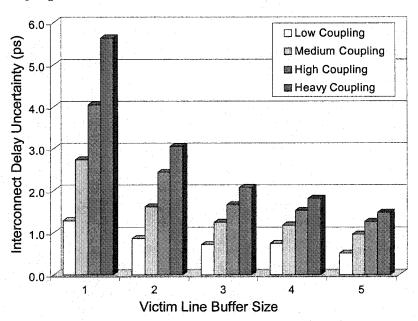

|      | buffer size                                                               | 87 |

| 5.10 | Delay uncertainty increases proportionally with capacitive coupling       |    |

|      | among the lines                                                           | 88 |

| 5.11 | Increase in power dissipation with buffer size                            | 90 |

| 5.12 | Power-Delay uncertainty Product $(PD_UP)$ for device parameter            |    |

|      | variations, interconnect coupling, and the sum of both effects            | 92 |

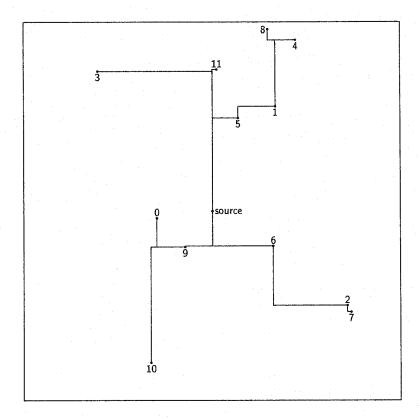

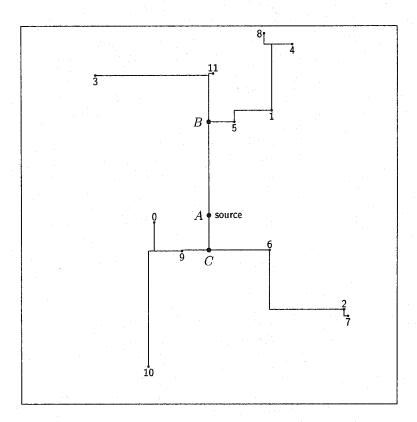

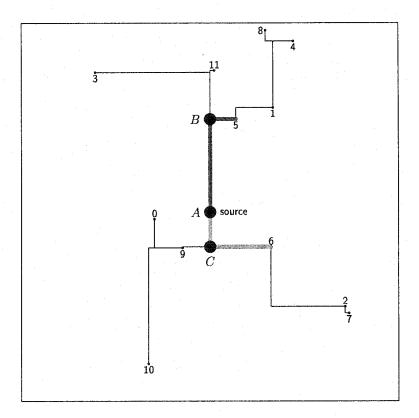

| 6.1  | An example of a minimal rectilinear Steiner clock tree                    | 96 |

| 6.2  | Buffer insertion in the clock tree shown in Fig. 6.1                      | 97 |

|      |                                                                         | xvii |

|------|-------------------------------------------------------------------------|------|

| 6.3  | Increasing buffer size to reduce delay uncertainty                      | 99   |

| 6.4  | Dedicated clock tree and buffers to drive the critical registers in the |      |

|      | circuit shown in Fig. 6.1                                               | 102  |

| 8.1  | Incorporating delay uncertainty models into the design flow to es-      |      |

|      | timate delay uncertainty earlier in the circuit design process          | 113  |

| 8.2  | Sizing of tapered buffers per stage to match upstream and down-         |      |

|      | stream delays                                                           | 115  |

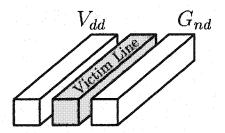

| 8.3  | Shielding a victim line with power supply lines                         | 117  |

| 8.4  | Peak noise increases as coupling occurs farther from the driver         | 117  |

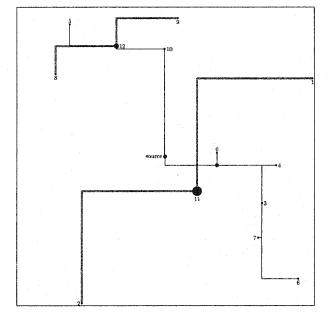

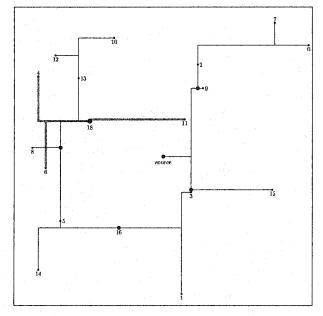

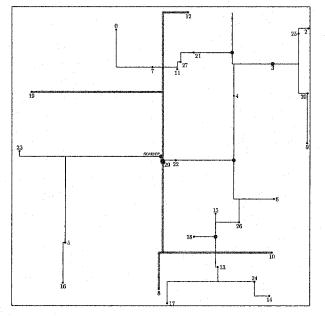

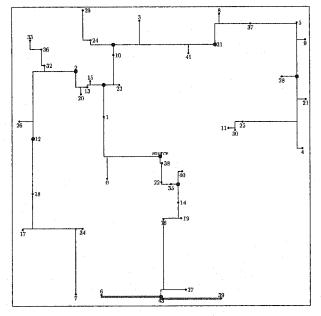

| A.1  | Circuit # 1 - buffer insertion and sizing                               | 128  |

| A.2  | Circuit # 1 - dedicated minimal clock tree                              | 128  |

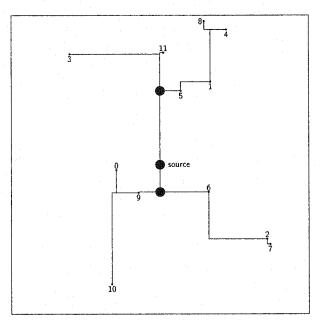

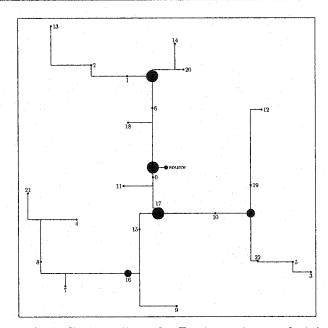

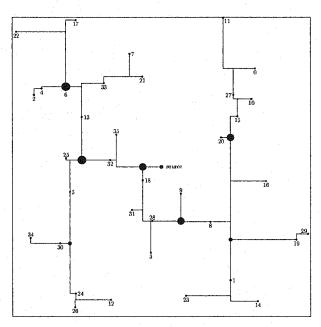

| A.3  | Circuit # 2 - buffer insertion and sizing                               | 129  |

| A.4  | Circuit # 2 - dedicated minimal clock tree                              | 129  |

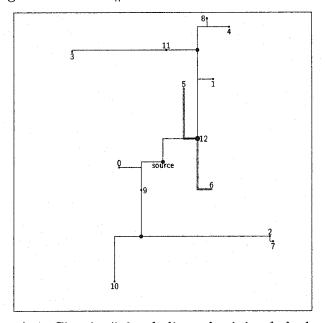

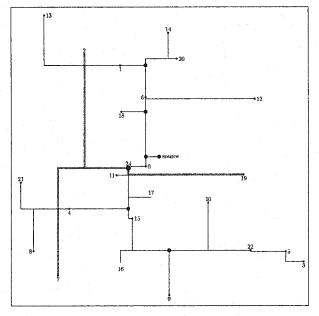

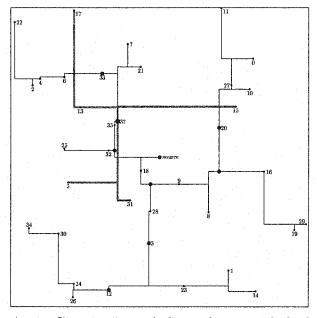

| A.5  | Circuit # 3 - buffer insertion and sizing                               | 130  |

| A.6  | Circuit # 3 - dedicated minimal clock tree                              | 130  |

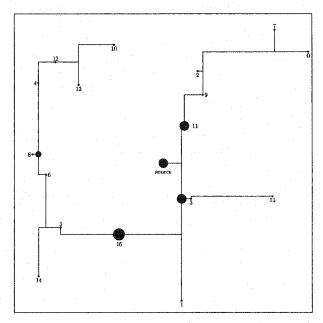

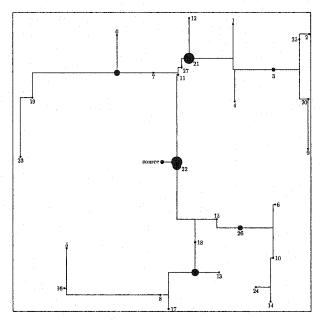

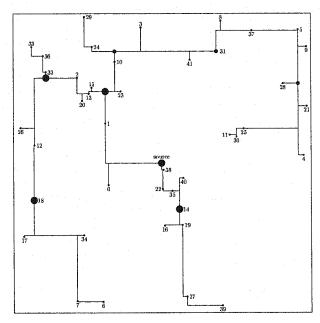

| A.7  | Circuit # 4 - buffer insertion and sizing                               | 131  |

| A.8  | Circuit # 4 - dedicated minimal clock tree                              | 131  |

| A.9  | Circuit # 5 - buffer insertion and sizing                               | 132  |

| A.10 | Circuit # 5 - dedicated minimal clock tree                              | 132  |

| A.11 | Circuit # 6 - buffer insertion and sizing                               | 133  |

| A.12 | Circuit # 6 - dedicated minimal clock tree                              | 133  |

| A.13 | Circuit # 7 - buffer insertion and sizing                               | 134  |

| A.14 | Circuit # 7 - dedicated minimal clock tree                              | 134  |

|     |         |                 |         |      | xviii |

|-----|---------|-----------------|---------|------|-------|

|     |         |                 |         |      |       |

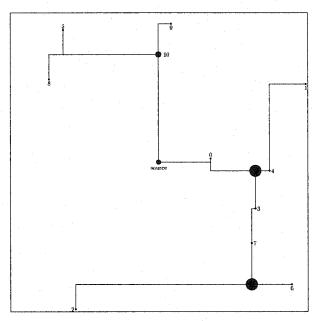

| B.1 | Example | of circuit data | a paths | <br> | 135   |

|     |         |                 |         |      |       |

### Chapter 1

### Introduction

The microprocessor is commonly used in a broad spectrum of human activities varying from the sciences and engineering to arts and entertainment. The capability of the microprocessor to process and transfer large amounts of data and information that were inconceivable in the past has made possible a number of important breakthroughs. Furthermore, everyday life has radically been changed, affecting the way people access news, information, and knowledge, as well as the way people communicate with each other. All of these achievements have changed our lives forever and are based on the microprocessor. Within thirty years, the microprocessor has become the life support system of the modern world [1].

The first commercial integrated microprocessor was the 4004, launched by Intel Corporation in 1971. The 4004 offered approximately the same performance as the ENIAC with 18000 vacuum tubes did in 1946. The low cost (approximately \$200) and tiny size (12  $mm^2$ ) of the 4004 enabled engineers to create new categories of society changing products. At the same time, however, skeptics predicted that the market for a single integrated circuit computer would be tiny. Soon afterwards, these predictions were proved wrong. The computer-on-a-chip has become one of the largest markets in the world and a fundamental factor in the world economy.

Since 1971, the development of the microprocessor has continued, steadily following Gordon Moore's prediction in the 1960's. Moore predicted that the density of integrated circuits (IC) would double every eighteen months. This statement is widely known as *Moore's law* [2]. The increase in circuit density is accompanied by a decrease in the on-chip feature size [3], enabling system designers to enhance the functionality of an IC by adding more components. The trend characterizing the reduction in the on-chip feature size (*i.e.*, the channel length) together with a significant increase in circuit density since 1971 are shown in Fig. 1.1(a). In addition, circuits with smaller device sizes can operate faster, permitting the operating clock frequency to be increased. This increasing trend in operating clock frequencies is shown in Fig. 1.1(b)

During the evolution of the microprocessor, the circuit design process has faced several serious challenges and obstacles. Providing solutions to overcome these challenges has permitted IC design and manufacturing technologies to mature and move forward into new eras where more challenging problems would be faced. In the 1970's, the primary design constraint was die area. Small wafer area and the high density of defects per die area degraded manufacturing yield and made the fabrication of large ICs extremely costly and non-profitable. Solutions were provided by the development of scaling techniques [3] which reduced the minimum feature size and die area. In addition, manufacturing process technologies have improved, dramatically reducing defect densities while improving manufacturing yield.

Scaling the feature size, in addition to relaxing area constraints, has also increased the functionality of the ICs, since more system components could be integrated onto a single die. In addition, circuits with smaller channel lengths are

(a) Reduction of channel length and increase of circuit density

Fig. 1.1: Evolution of the microprocessor since the 1970's

able to operate faster, boosting the operating frequency of the microprocessor, as shown in Fig. 1.1(b). The quest for improved functionality, faster circuit speed, and lower power dissipation has shifted the manufacturing process from PMOS to NMOS and finally to CMOS, introducing the era of VLSI circuits, where the term *VLSI* stands for Very Large Scale Integration.

As the number of transistor devices on an IC and the operating frequency have both been increasing, on-chip power dissipation has become a challenging issue. Several power reduction techniques and strategies have been developed to reduce the on-chip power dissipation. One of the most effective techniques is scaling the power supply voltage [4]. This approach exploits the quadratic dependence of power dissipation on supply voltage. The scaling of the supply voltage, however, reduces the noise margins of a circuit [5], thereby increasing the sensitivity of a system to noise.

The effect of noise on circuit operation and reliability has recently become an extremely important issue in the design of high performance integrated circuits. Presently, the leading integrated circuit manufacturers have the technological capability to mass produce VLSI circuits with a feature size of less than a hundred nanometers [6]. These technologies are identified with the term very deep submicrometer (VDSM), since the minimum feature size is well below the one micrometer mark. At these very small geometries, the deleterious effects caused by noise are aggravated. The challenges faced today in the design of VDSM circuits are greater than ever.

The main effect of noise is the degradation of signal integrity and an increased uncertainty in the signal delay. The research presented in this dissertation is specifically concerned with the effects of delay uncertainty in high performance CMOS integrated circuits. The results of this research focus on improving the tolerance of a system to delay uncertainty.

The variation of process and environmental parameters is the primary source of noise that introduces uncertainty in the delay of the signals propagating within a circuit. At the transistor device level, the variation of geometric and electrical parameters such as the effective channel length and threshold voltage are some of the important effects that introduce delay uncertainty. In addition, a significant effect on the signal delay is caused by the coupling of signals [7] due to capacitive [8] and inductive [9] coupling among the wires. The variations of the geometric parameters of the interconnects due to limitations of the manufacturing process [10–12] also cause uncertainty in the delay of a signal propagating through an interconnect line. At the system level, variations in the power supply voltage [13], temperature variations [14], and electromagnetic effects [15] can affect the signal delay. These effects that introduce delay uncertainty are summarized in Chapter 2.

The uncertainty of the propagation delay of a signal can cause a catastrophic violation of the timing constraints within a system. With increasing clock frequencies, these constraints have become tighter and the sensitivity of a system to delay uncertainty has increased. One way to improve the tolerance of a system to delay uncertainty is by relaxing the timing constraints of the critical paths. In Chapter 3, a methodology that implements this concept through the application of non-zero clock skew scheduling is described. A variation of this methodology is applied to reduce the power dissipated in the fast data paths of a system. This problem is discussed and the application of the proposed solution to an industrial circuit is described in Chapter 3.

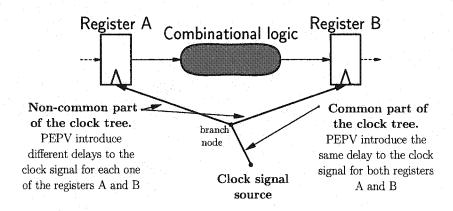

One of the most critical signals in a synchronous digital circuit is the clock signal. It is important to reduce the uncertainty of the clock signal delay, particularly the clock signals driving the registers belonging to the most critical data paths. In Chapter 4, a methodology is described that controls the topology of the clock tree so as to improve the tolerance of the clock signal to delay uncertainty. An algorithm that implements this methodology and extracts the clock tree topology is also presented in Chapter 4. The application of the algorithm to a set of benchmark circuits demonstrates a significant reduction in the delay uncertainty of the clock signal in the most critical data paths.

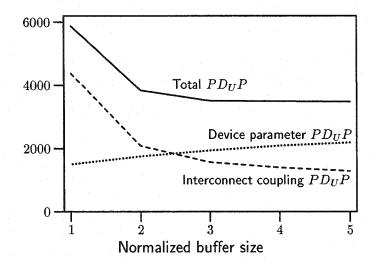

The delay of the clock signal propagating along a clock distribution network can be controlled by inserting clock buffers within the signal path. The variation of the device parameters, however, can change the current flow through that buffer, thereby introducing uncertainty in the buffer delay. The dependence of the uncertainty in the buffer delay upon the size of a buffer is investigated in Chapter 5. It is shown that the uncertainty in the buffer delay can be reduced by increasing the buffer size. Furthermore, it is demonstrated that increasing the buffer size reduces the delay uncertainty caused by crosstalk coupling among interconnect lines. The primary drawback of increasing the clock buffer size is the increase in power dissipation. The tradeoff between reducing the delay uncertainty and increasing the power dissipation is considered by introducing the Power-Delay-uncertainty-Product  $(PD_UP)$ .

The delay uncertainty of a clock signal is strongly dependent upon the geometric characteristics and the spatial location of the clock lines and registers. Therefore, in order to estimate and reduce delay uncertainty, physical layout information should be incorporated into the clock distribution network design pro-

cess. Two different strategies are described in Chapter 6 for synthesizing the clock tree layout. Both strategies reduce the delay uncertainty of the clock signals arriving at the registers of the most critical data paths. Clock buffer insertion and sizing is utilized in one approach, exploiting the reduction in delay uncertainty with increasing buffer size. In the second approach, the clock signal is distributed to the registers of the critical paths by a dedicated portion of the clock tree, which increases the common path among the clock signals. A tradeoff between power dissipation and wire length is demonstrated by the application of these two strategies to the synthesis of a clock layout for a set of benchmark circuits.

Conclusions of this dissertation are offered in Chapter 7. Finally, ideas for future research that will enhance and incorporate the presented methodologies into a unified system level design methodology to control the effects that introduce delay uncertainty are presented in Chapter 8.

### Chapter 2

# Delay Uncertainty in High Speed CMOS Circuits

The primary characteristic of the microelectronics revolution, as discussed in Chapter 1, is the rapid decrease in device size, producing phenomenal increases in circuit density, functionality, and operational clock frequencies [6, 16]. Scaling of the device geometries supports the system-on-a-chip integration of multiple subsystems [17, 18], greatly increasing the number of on-chip clocked elements. These effects have resulted in hundreds of thousands of elementary operations being executed in sequences specified by application-specific algorithms and controlled by a clock signal, operating within time periods much less than a nanosecond [19]. These constraints demonstrate the tight timing control of the arrival times of the clock signal at the many registers distributed throughout an integrated circuit. Deviations of the clock signal from the target delay can cause incorrect data to be latched within a register, resulting in a system malfunctioning.

The variation of the signal propagation delay is described by the term *delay uncertainty*. The effects that introduce uncertainty in the signal delay can generally be referred to as *noise*. Examples of effects that produce noise are the variations of process, environmental, and system parameters and interconnect signal coupling.

One common characteristic of these phenomena is that these effects are highly unpredictable. It is therefore extremely difficult to estimate and adequately model these effects. In addition, most of those parameters whose variation introduces delay uncertainty cannot be controlled within the circuit design process. For example, the difference in the arrival time of the clock signal between two paths due to different wire lengths in a clock distribution network can be estimated based on the impedance characteristics of a line. That difference in delay can also be compensated by certain design techniques, such as decreasing the length of the longer path, or inserting buffers of an appropriate size [20]. However, there is variation in the signal delay of these paths due to the non-uniformity of the interconnect lines caused by imperfections during the etching and metal deposition processes. Additional variations in delay are caused by the interaction between the clock signal and data signals on neighboring lines. These variations in delay are extremely difficult to predict and to compensate, creating delay uncertainty.

An approach to manage these delay uncertainties is to develop design methodologies that tolerate the parameter variations rather than compensate for these variations. A statistical analysis can be used to model those parameter variations, providing quantitative estimates of the delay uncertainty. These models are used to develop design methodologies that account for the effects that introduce delay uncertainty and produce systems capable of tolerating delay variations. The issue of delay uncertainty, however, remains a crucial one since the race for smaller devices and faster operational frequencies aggravates the effects that cause delay variations. Designing a system tolerant to delay uncertainty is a highly challenging task that involves precise balancing between design tradeoffs and operational specifications.

The effects that introduce delay uncertainty in different circuit elements are discussed in this chapter. Design methodologies and techniques that tolerate delay uncertainty are presented in the following chapters. The effects that cause uncertainty in the delay of a signal propagating through a CMOS device are presented in section 2.1. Geometric parameter variations of interconnect lines and the effect of these variations on delay are discussed in section 2.2. The effect of signal transition noise on interconnects is described in section 2.3. In section 2.4, the effects of system level parameter variations are discussed. Finally, some conclusions are presented in section 2.5.

#### 2.1 Variations of CMOS device parameters

As device sizes are decreased, the effect of device parameter variations is aggravated. Assuming that the magnitude of the variation of an MOS device parameter remains constant, the per cent variation of this parameter increases inversely proportional with the scaling of the device. In this section, the variation of several device parameters and the effects on the signal propagation delay through a CMOS circuit are discussed. The variation of the effective channel length is discussed in subsection 2.1.1. Variations in carrier mobility are presented in subsection 2.1.2. Gate oxide thickness variation is described in subsection 2.1.3, while variations in threshold voltage are presented in subsection 2.1.4.

#### 2.1.1 Effective channel length variation

The basic steps of the semiconductor manufacturing process that creates the source and drain of an NMOS transistor are shown in Fig. 2.1 (the process that

(a) Deposition of thin oxide and polysilicon layers

(b) Etching the poly and oxide layer to expose the source and drain regions

(c) Doping of the source and drain regions

Fig. 2.1: Basic steps of the transistor source and drain creation process

creates a PMOS device is similar with only minor modifications). Initially, the silicon substrate is covered with a thick layer of  $SiO_2$ . Afterwards, the  $SiO_2$  layer is etched in the area where a transistor will be created. This area is covered with a layer of thin oxide, followed by a layer of polysilicon, as shown in Fig 2.1(a). After

deposition, the polysilicon layer is patterned and etched to form the interconnects and the MOS transistor gate. The thin oxide layer not covered by polysilicon is also etched away, exposing the bare silicon substrate on which the source and drain regions are formed [see Fig. 2.1(b)]. The length of the polysilicon and the thin oxide layers that remain on the silicon substrate define the *gate* and the *channel length* of the transistor. The exposed silicon surface is then doped with a high concentration of donors, either through diffusion or ion implantation. As shown in Fig 2.1(c), the donors penetrate the exposed areas of the silicon substrate, creating two n-type regions. Note that the polysilicon gate, which is patterned before doping, actually defines the location of the channel region as well as the locations of the source and drain regions. Since this process allows the direct positioning of the two regions relative to the gate, this process is also called a *self-aligned* process [21].

Ideally, the edge of the source and drain regions should be aligned with the edge of the gate oxide layer. Practically, however, both the source and drain regions tend to extend below the oxide by an amount  $x_d$ , the lateral diffusion, as shown in Fig. 2.1(c). The effective channel  $L_{eff}$  of a transistor therefore becomes shorter than the drawn gate length L by a factor of  $\Delta_L = 2x_d$ . As shown in [22], the lateral diffusion factor for a 0.25  $\mu$ m CMOS technology is approximately  $\Delta_L = 0.08 \ \mu$ m. As a rule of thumb, the lateral diffusion factor is about 30% of the drawn transistor gate [6].

There are several effects that can cause variations in the effective channel length of a transistor. These variations can be either global (*i.e.*, variations of the effective channel length among transistors at different areas within a die), or local (*i.e.*, variation of the effective channel length within a single transistor).

One of the effects that can cause variations of the effective channel length is a change in the lateral diffusion of the source and drain areas below the transistor gate. The lateral diffusion  $x_d$  is proportional to the donor doping density at the source and drain areas. Therefore, a non-uniform doping density is possible which will create non-uniform lateral diffusion areas and variations in the effective channel length. Usually, a non-uniform doping density has a global profile across a die, therefore, variations in the effective channel length due to non-uniform doping densities occur between transistors at distant areas on an IC. Other effects such as misalignment or misplacement of the photoresist masks and resolution limitations of the photolithography process also contribute to global variations in the effective channel length.

Alternatively, etching imperfections of the gate oxide and polysilicon layers that define the transistor gate may create local variations in the effective channel length within a single transistor. These imperfections may occur randomly along a transistor. However, the wider a transistor gate, the higher the probability that these imperfections will occur. Therefore, this effect is greater in the case of wide transistors.

#### 2.1.2 Variations in carrier mobility

When an electric field is applied across a semiconductor, the charge carriers within the semiconductor lattice are accelerated. This carrier motion is described as *drift*. As the carriers move within the crystal, the carriers collide with ionized impurity atoms and thermally agitated lattice atoms. These collisions are described with the term *carrier scattering*. The *mobility* of the carriers charac-

terizes the "ease of carrier motion" within the semiconductor lattice, as described by Pierret in [23]. The higher the carrier mobility, the greater the current flow through a semiconductor. Carrier mobility is, therefore, an important parameter that greatly affects the performance of an MOS device.

Carrier scattering can be characterized by two separate effects. The first effect is the collision of carriers with thermally agitated lattice atoms, described as *lattice* scattering. The second effect is the collision of carriers with ionized impurity atoms, called *ionized impurity scattering*. Both effects decrease carrier mobility. For impurity atom concentrations below  $10^{15}/cm^3$ , the effect of ionized impurity scattering on mobility can be neglected. However, if the impurity concentration is well above  $10^{15}/cm^3$ , the ionized impurity scattering cannot be neglected and the mobility of carriers are dependent on the doping concentration. The dependency on doping is described by

$$\mu = \mu_{min} \frac{\mu_o}{1 + (N/N_{ref})^{\alpha}},$$

(2.1)

where  $\mu$  is the carrier mobility ( $\mu_n$  for electrons and  $\mu_p$  for holes) and N is the doping concentration ( $N_D$  for donors and  $N_A$  for acceptors). The parameters  $\mu_{min}$ ,  $\mu_o$ ,  $N_{ref}$ , and  $\alpha$  are empirical parameters. Typical values of these empirical parameters for electron and hole carriers (at 300° K) are listed in Table 2.1 [23].

Table 2.1: Parameter values for electron and hole carriers at 300° K

| Parameter               | Electrons          | Holes               |

|-------------------------|--------------------|---------------------|

| $\mu_{min} (cm^2/Vsec)$ | 92                 | 54.3                |

| $\mu_o \ (cm^2/Vsec)$   | 1268               | 406.9               |

| $N_{ref} (cm^{-3})$     | $1.3\cdot 10^{17}$ | $2.35\cdot 10^{17}$ |

| α                       | 0.91               | 0.88                |

In addition to doping concentration, carrier mobility also strongly depends upon temperature. The temperature controls the agitation of the atoms within the semiconductor lattice. An increase in temperature increases the thermal agitation of these atoms and the probability of the carriers colliding with the atoms. The mobility, therefore, decreases with increasing temperature. For impurity doping concentrations below  $10^{14}/cm^3$ , temperature variations are the primary cause of mobility variations. For doping concentrations greater than  $10^{14}/cm^3$ , the carrier mobility decreases with increasing temperature, but this effect is less severe due to the dominant effect of ionized impurity scattering.

#### 2.1.3 Variations in the gate oxide thickness

Another device parameter that is susceptible to imperfections of the manufacturing process is the gate oxide thickness  $(t_{ox})$ . The oxide layer at the gate of a transistor is extremely thin, with a nominal value well below 100 angstroms (45 Å for a 0.25  $\mu$ m CMOS process [22]). The slightest imperfections of the deposition process can create significant variations in  $t_{ox}$ . The gate oxide thickness determines the input capacitance of a transistor gate, as well as the characteristics of the channel inversion and carrier concentration within the channel. Therefore, variations in  $t_{ox}$  can introduce uncertainty both in the input signal that drives the gate of a transistor and in the output signal of a transistor that depends upon the current flow in the channel. These effects are discussed in greater detail below.

The delay of a signal driving a transistor depends upon the total input capacitive load seen at the transistor gate. A portion of this load is the gate parasitic capacitance  $C_g$ ,

$$C_g = C_{ox} \frac{W}{L} = \frac{\varepsilon_{ox}}{t_{ox}} \frac{W}{L}.$$

(2.2)

In (2.2),  $C_{ox}$  is the gate oxide capacitance per unit area and equals  $\frac{\varepsilon_{ox}}{t_{ox}}$ , where  $\varepsilon_{ox}$  is the dielectric constant of silicon dioxide. W and L represent the gate width and drawn length  $(L = L_{eff} + 2x_d)$ , respectively. As shown in (2.2),  $t_{ox}$  determines the input capacitance of a transistor gate and therefore the delay of the input signal driving the transistor.

The delay of the output signal depends upon the amount of current flowing through the gate of the transistor. A first order approximation of this current is given by the Shockley model [24] for each region of operation of a transistor.

$$I_{D} = \begin{cases} 0 & : (V_{GS} \leq V_{th}) \\ \mu \frac{\varepsilon_{ox}}{t_{ox}} \frac{W}{L} \left\{ (V_{GS} - V_{th}) V_{DS} - \frac{1}{2} V_{DS}^{2} \right\} & : (V_{GS} \geq V_{th}) \& (V_{DS} \leq V_{DSAT}) \\ \frac{1}{2} \mu \frac{\varepsilon_{ox}}{t_{ox}} \frac{W}{L} (V_{GS} - V_{th})^{2} & : (V_{GS} \geq V_{th}) \& (V_{DS} \geq V_{DSAT}). \end{cases}$$

(2.3)

As shown in (2.3), the current flow through an on transistor is inversely proportional to the gate oxide thickness. Therefore, variations in  $t_{ox}$  may cause changes in the current flow and introduce delay uncertainty at the output of a transistor.

#### 2.1.4 Threshold voltage variation

Equation (2.3) also demonstrates the effect of another device parameter on the current flow, that is the threshold voltage  $(V_{th})$ . Threshold voltage is one of the most important parameters that characterize the operation and behavior of a CMOS circuit. As shown in (2.3),  $V_{th}$  determines the current flow through a transistor and, consequently, the signal delay. In addition,  $V_{th}$  determines the noise margins of a digital gate [5] that define the tolerance of a system to signal noise. The discussion that follows about  $V_{th}$  dependencies and variations is in terms of an N-channel device but the results are applicable, with minor modifications, to P-channel devices as well.

There are four physical components of the threshold voltage [21] that should be considered for almost all practical purposes. These are:

- i. The work function difference  $\Phi_{GC}$  between the gate and the channel of a transistor.  $\Phi_{GC}$  represents the built-in potential drop in a MOS system.

- ii. The change of the surface potential (i.e., the voltage that is applied to achieve surface inversion)  $-2\phi_F$ , where  $\phi_F$  is the Fermi potential for silicon,

$$\phi_F = \frac{kT}{q} \ln \frac{n_i}{N_D}.\tag{2.4}$$

In (2.4), k denotes the Boltzmann constant, q is the electron charge, T is the temperature,  $N_D$  represents the substrate doping density, and  $n_i$  is the intrinsic carrier concentration.

iii. The potential (i.e., the voltage drop across the gate oxide) that offsets the depletion region charge  $\frac{Q_B}{C_{ox}}$ , where  $C_{ox}$  is described in (2.2) and  $Q_B$  is the depletion region charge density,

$$Q_B = -\sqrt{2qN_D\varepsilon_{Si}|-2\phi_F + V_{SB}|},\tag{2.5}$$

where  $\varepsilon_{Si}$  is the dielectric constant of silicon, and  $V_{SB}$  is the source-to-substrate voltage.

iv. The voltage component to offset the fixed positive charge density  $Q_{ox}$  at the interface between the gate oxide and the silicon substrate. This voltage component is  $-\frac{Q_{ox}}{C_{ox}}$ .

Therefore, the threshold voltage  $V_{th}$  can be analytically expressed by the summation of these four components:

$$V_{th} = \Phi_{GC} - 2\phi_F - \frac{Q_B}{C_{ox}} - \frac{Q_{ox}}{C_{ox}}.$$

(2.6)

In this one-dimensional model, the variation in the threshold voltage  $\delta V_{th}$  arises from four independent sources. These sources are: the substrate bias  $V_{SB}$  (e.g., body effect), the gate oxide thickness  $t_{ox}$ , the substrate doping density  $N_D$ , and the effective channel length  $L_{eff}$ . The effect of each of these factors on the variation of the threshold voltage is discussed below.

The dependence of the threshold voltage on the substrate bias  $V_{SB}$  is described by (2.5) and (2.6). Qualitatively, the width of the depletion region formed under the channel increases when a negative back-bias voltage  $(V_{SB})$  is applied at the substrate with respect to the source. The increased depletion region requires additional charge in order to maintain a constant channel conductivity [21]. Therefore, the voltage  $V_{GS}$  applied at the gate is increased which corresponds to an increase in the threshold voltage  $V_{th}$ . Alternatively, if the substrate potential with respect to the source increases, the depletion region below the channel is decreased and the threshold voltage decreases.

Variations of the  $V_{SB}$  voltage are very common in those cases where the source of the transistor is floating. An example of a floating source is the NMOS stack structure of a 3-input NAND gate, shown in Fig. 2.2 [25].

The effect of the gate oxide thickness on threshold voltage is described by the two components of  $V_{th}$ :  $-\frac{Q_B}{C_{ox}}$  and  $-\frac{Q_{ox}}{C_{ox}}$ . The variation of gate oxide thickness therefore affects the charge at the depletion region in the channel as well as the charge density at the oxide-substrate interface. The importance of variations in

Fig. 2.2:  $V_{SB}$  variations due to floating sources along the N-channel tree portion of a three input NAND gate

the gate oxide thickness increases as the on-chip feature size is reduced into the deep submicrometer range. As shown in [26], the effect of  $t_{ox}$  variations on  $V_{th}$  is four times more significant in a 0.1  $\mu$ m device as compared with a 1.0  $\mu$ m sized transistor.

Experimental measurements of the standard deviations of  $V_{th}$  as a function of the gate oxide thickness are shown in Fig. 2.3. The closed and open circles show the experimental data for  $L_{eff}$ =0.5  $\mu$ m and 0.3  $\mu$ m CMOS technology respectively [27].

In addition to the effect of the gate oxide thickness, the effect of the effective channel length on the standard deviation of  $V_{th}$  is shown in Fig. 2.3. The data illustrated in Fig. 2.3 is another indication that as the on-chip feature size is decreased, variations in the device parameters becomes increasingly important. The nominal value of  $V_{th}$ , however, is found to monotonically decrease with decreasing

Fig. 2.3: Standard deviation of  $V_{th}$  as a function of  $t_{ox}$

channel length. Qualitatively, a reduction in threshold voltage can be explained as follows [23]. In order to form an inversion layer, or channel, beneath the gate, the subgate region must first be depleted. In a short-channel device, the pn junctions formed between the source/drain regions and the silicon substrate assist in depleting the region under the gate. Thus, less charge is required at the gate to reach the state of channel inversion, therefore  $V_{th}$  decreases. As the  $L_{eff}$  becomes smaller, the source and drain pn junctions assist in depleting a greater percentage of charge under the gate, further reducing  $V_{th}$ .

Another process parameter that affects the threshold voltage is the substrate doping density  $N_D$ . As shown in (2.4) and (2.5), the substrate doping density contributes both to the surface potential  $(\phi_F)$  and the charge density of the depletion region  $(Q_B)$ . The substrate doping density is the controlling parameter of the threshold voltage in low power applications such as dual-threshold voltage systems that reduce standby dissipation caused by subthreshold leakage currents

[28]. Experimental results determined from varying the threshold voltage with respect to the substrate doping density are presented in [27]. The standard deviation of threshold voltage  $\sigma V_{th}$  as a function of the average channel doping density is shown in Fig. 2.4 for two different channel lengths. As shown in Fig. 2.4, the change in  $\sigma V_{th}$  with respect to the doping density is relatively small. This behavior explains the use of doping density to control the threshold voltage [27].

Fig. 2.4: Standard deviation of  $V_{th}$  as a function of doping concentration

## 2.2 Variations in interconnect parameters

As the on-chip feature size is reduced concurrently with increasing chip dimensions, the on-chip interconnect delay has become more significant than the gate delay. By decreasing the on-chip feature size, the geometric parameters of the interconnect lines have also been decreased. Reducing the interconnect wire width and the distance between the lines increases the per unit length wire resistance and interline capacitance. In addition, increasing die dimensions have resulted in interconnect lines running over longer distances across an IC. The interconnect component of the on-chip signal delay has, therefore, become increasingly significant.

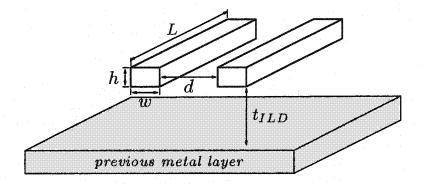

The basic geometric parameters of the interconnect lines are shown in Fig. 2.5. The symbols w, h, d, L, and  $t_{ILD}$  are the line width, the metal thickness, the distance between two lines of the same metal level, the length of the line, and the thickness of the interlevel dielectric oxide, respectively. The variation of these parameters due to manufacturing process imperfections produces variations in the parasitic resistance and capacitance of a line. These impedances determine the

Fig. 2.5: Geometric parameters of the interconnect lines

signal propagation delay within a line. Variations in the geometric parameters, therefore, create delay uncertainty. The dominant role of interconnect on the total on-chip delay demonstrates the importance of delay uncertainty. The effects that create variation in each one of the interconnect geometric parameters are discussed below [25].

Line width and interline spacing. Line width variation arises primarily due to photolithography and etching imperfections. At smaller dimensions (i.e., lower metal levels), line width variations occur due to proximity and lithographic effects. Etching effects which depend on the line width and local layout can also create non-uniformities of the deposited metal. The variation of the line width has a direct impact on the resistance of a line as well as on the capacitance between overlapping lines on different metal layers. In addition, line width variations also result in differences in interline spacing between lines of the same metal layer. These spacing variations can affect the line-to-line capacitance, thereby affecting the crosstalk and signal integrity.

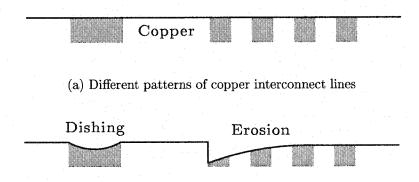

Metal thickness. The deposition of metal wires and barriers is well controlled in an aluminum metal interconnect process. Small variations in metal thickness can occur on different dies across a wafer or among different wafers. However, in damascene (e.g., copper) processes, the metal thickness of the patterned lines can vary significantly due to dishing and erosion effects, as shown in Fig. 2.6. The losses of line thickness depend upon the particular line patterns and are within the range of 10% to 20% [12].

Dielectric thickness. The thickness of deposited and polished dielectric oxide layers over metal layers can also vary significantly. The variation of the dielectric oxide thickness across a wafer is within the range of 5%. However, greater varia-

(b) Dishing and erosion effects after the polishing process

Fig. 2.6: Copper line thickness losses due to dishing and erosion effects

tions can occur due to pattern dependencies of the dielectric deposition process. For example, in high-density plasma (HDP) processes the dielectric thickness depends strongly upon the size and/or width of a deposited feature. Furthermore, in chemical mechanical polishing (CMP) processes the dielectric oxide thickness can vary significantly depending upon the effective density of the underlying interconnect lines, as shown in Fig. 2.7.

(b) Dielectric oxide thickness variation

Fig. 2.7: Variation in ILD thickness due to different pattern density of interconnect lines

Contact and via size. Variations in the etching process and the dielectric thickness can affect the size of a contact or via. The etching depth can vary significantly depending upon the location of the contact or via, resulting in variations in the lateral opening size. These variations can significantly change the resistance of a contact or via.

## 2.3 Interconnect noise

The trend in next generation integrated circuit technology is towards smaller on-chip feature sizes and higher operating speeds. The density of the on-chip interconnect lines has increased together with the switching rate of the signals propagating through these lines, resulting in increased on-chip interconnect noise. Interconnect noise is primarily introduced by electromagnetic effects such as capacitive and inductive crosstalk between/among interconnects. The contribution of these effects to signal delay uncertainty along interconnect lines is discussed in this section.

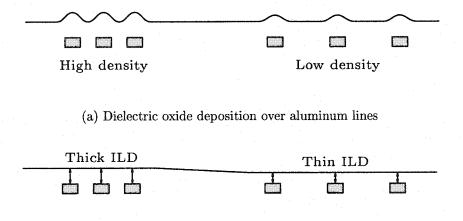

## 2.3.1 Capacitive interconnect coupling

With the transition to deep submicrometer technologies, shrinking geometries have led to a reduction in the self-capacitance of interconnect lines, while coupling capacitances between the lines have increased as the lines are placed physically closer. In current processes, the coupling capacitance can be as high as the capacitance-to-ground [8]. Furthermore, trends indicate that the role of coupling capacitances will become more dominant as the feature size continues

to shrink [29]. The capacitive components between three parallel lines on two different metal levels are shown in Fig. 2.8.

Fig. 2.8: Capacitive coupling among different interconnect layers

One of the important effects of coupling capacitances is unwanted voltage spikes in neighboring nets. A net (or wire) on which a switching event is generated is termed an *aggressor*, while a net (wire) on which that switching event produces a noise spike is referred to as a *victim*. This effect of coupling unwanted signals is known as *crosstalk*. Crosstalk can affect the behavior of circuits in one of two ways:

- Introducing unwanted noise on a quiescent line.

- Altering the delay of a switching transition.

In both of these cases, the switching of a line in a capacitively coupled net alters the effective capacitance of all of the other coupled lines.

Consider, for example, the simple capacitively coupled net shown in Fig. 2.9. The effective load capacitance driven by each of the CMOS inverters depends upon

Fig. 2.9: Capacitively coupled net

the lines switching (i) in phase, (ii) out of phase, and (iii) one being active and the other remaining quiescent [7]. The uncertainty of the effective load capacitance due to the signal activity introduces uncertainty on the signal propagation delay within a coupled net. Further delay uncertainty is introduced by the coupling capacitance between two adjacent nets. This capacitance is proportional to the length along which the nets run close to each other [30]. Modeling and estimating the delay uncertainty due to crosstalk effects in large nets has therefore become a complicated and challenging process.

#### 2.3.2 Inductance effects

Another effect that increases the deviation of the signal propagation delay from traditional interconnect models is inductance. While on-chip inductance has been relatively ignored in the past, with faster on-chip signal transition times and longer wire lengths, on-chip inductance has become increasingly important. Wide wires are frequently encountered in clock distribution networks and in upper metal

layers. These wires are low resistance lines that can exhibit significant inductance effects. More accurate RLC models are therefore required for these global interconnect lines [9]. Furthermore, as performance requirements are accelerating the introduction of new materials (copper) for low resistive interconnect, inductance effects have become important for an increasing portion of on-chip lines.

Three different factors determine the inductance effects on an *RLC* line [9, 31]. These are (i) the signal impedance characteristics across the line, (ii) the transition time of the signal at the near end, and (iii) the time of flight of the signal propagating along the line. Based on these factors, the effect of inductance on the signal propagation delay increases as

- The attenuation of the signal along the line decreases (wider wires have less resistivity per unit length).

- The transition of the signal is faster (smaller driver resistance).

- The signal time of flight increases (longer wires).

The factors described above have been combined into a two-sided inequality [31] that determines the range of interconnect length for which inductance effects are important. This range is

$$\frac{t_r}{2\sqrt{LC}} \le l \le \frac{2}{R}\sqrt{\frac{L}{C}},\tag{2.7}$$

where R, L, and C are the resistance, inductance, and capacitance of the line, respectively, l is the length of the line, and  $t_r$  is the transition time of the signal. This inequality is graphically illustrated in Fig. 2.10 [31].

Inequality (2.7) demonstrates that for long wire lengths, the RC time constant is sufficient due to high signal attenuation along the line. At intermediate

Fig. 2.10: Transition time  $(t_r)$  versus the length of the interconnect line (l). The shaded area denotes the region where inductance is important

wire lengths the ratio of the signal transition time over the signal time of flight determines the inductive behavior of a line. Lines with intermediate length are typical on many on-chip busses where the signal delay is affected by the mutual inductance among the lines. It is therefore important to accurately characterize the inductive behavior of these lines. For short wire lengths, inductance becomes important only for very fast signal transition times.

## 2.4 Variations in system parameters

In addition to the noise introduced by crosstalk and inductance effects, there are many other sources of delay uncertainty and noise originating at the system level or the surrounding environment of an IC. Such sources of uncertainty are power supply fluctuations (*IR* drops), electromagnetic interference (EMI), and system temperature. In this section, the effects of these noise sources on high performance digital circuits are discussed.

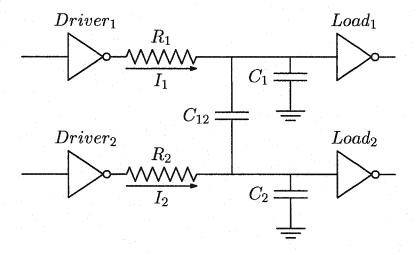

## 2.4.1 Power supply fluctuations - IR drops

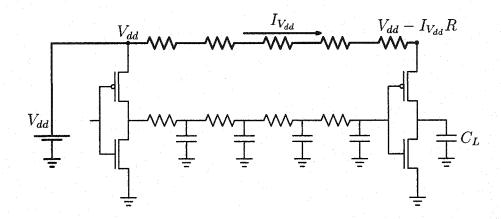

One issue that has become an important source of delay uncertainty is the fluctuation of the power supply  $V_{DD}$  due to the resistance of the power distribution system, also known as IR drops. IR drops increase with larger currents flowing through the power grid. With narrow metal lines common in deep submicrometer (DSM) circuits, interconnect resistance has become a major factor in power distribution systems. Although wider lines are often used in power busses to reduce resistance, high operating frequencies require large buffers which draw large currents. When these currents flow from the power supply to the drivers, any resistance encountered in the power busses can cause the voltage to drop. This effect is shown in Fig. 2.11 [13]. The far end inverter shown in Fig 2.11 experiences a lower supply voltage than the initial inverter due to the IR drop along the supply line.

Since the power distribution network is composed of long interconnect lines running across a die, IR drops have a global effect within a die. The on-chip global structure that is primarily affected by IR drops is the clock distribution

Fig. 2.11: Voltage drop due to the resistance within the power distribution network

network. Since *IR* drops effectively reduce the supply voltage, the clock buffers connected to the power grid provide less current, increasing the propagation delay of the clock signal.

Furthermore, voltage variations due to IR drops change transiently at each buffer as the clock signal changes. The current delivered to the buffers varies depending upon the instantaneous level of the IR drops. This transient fluctuation of the supply voltage causes variations in the clock delay, clock skew, and signal slew rates. As shown in [13], an IR drop can be translated directly into delay uncertainty. For example, a 10% voltage drop of the power supply can cause at most a 10% increase in delay. More accurately, a 10% IR drop increases the delay by 5% to 10%. The experimental results described in [13] demonstrate that an N% IR drop causes a delay change between N/2% to N%. This relation serves as a useful rule of thumb for quantifying the impact of IR drops on delay uncertainty.

In order to mitigate potential IR drops, wide metal lines are used in the topmost metal layers to reduce the interconnect resistance. In addition, the routing of these lines is often changed to reduce the transient IR drops. Other methods include the use of decoupling capacitors and ball-grid arrays. Key drawbacks of these advanced design techniques are the increased cost and complexity of the verification process for both the power and clock distribution networks.

## 2.4.2 Electromagnetic Interference (EMI) effects

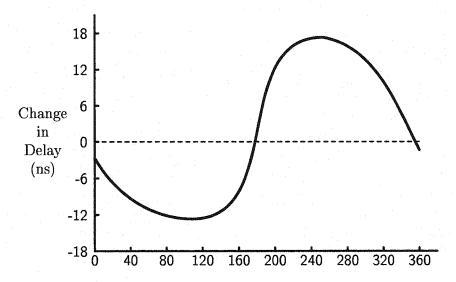

With increasing operating frequencies and circuit densities, electromagnetic interference is becoming a crucial issue in the design of modern electronic systems. In particular, EMI has two distinct effects on digital devices [15]. The first effect is false switching or *static failure*, which occurs when the amplitude of the interference is sufficient to cause a change in the state of a static signal. The second effect is that of EMI-induced delays. It is shown in [15] that significant variations in the propagation delay of a device occur at much lower amplitudes of EMI than those that cause false switching. These variations lead to a violation of the critical timing constraints such as the minimum set-up and hold time of a flip flop. The violation of these constraints may cause *dynamic failures* which, unlike static failures, are dependent on the phase of the EMI with respect to the transition of a logic state [32].

When EMI is injected into a digital circuit, variations in the signal propagation delay are produced. This behavior is a result of EMI changing the time at which a logic transition crosses the switching threshold. The amount of EMI-induced delay can be positive or negative depending upon the phase of the EMI relative to the logic transition, as shown in Fig. 2.12 [15]. Note in Fig. 2.12 that at 0° and 180° of phase the effect of EMI is zero; therefore, no change in the propagation delay occurs. Also, for an EMI phase between 0° and 180°, the induced delay is

negative, resulting in a decrease of the signal propagation delay. However, for an EMI phase between 180° and 360°, the induced delay is positive and the signal propagation delay increases.

Fig. 2.12: EMI-induced delay versus EMI phase differences for a logic transition

Increased system immunity to EMI-induced delay uncertainty is achieved by increasing the *delay margins* within a system. The delay margins are defined in [15] as "the maximum allowable change in the timing of a signal transition for which a circuit will continue to operate reliably." The delay margins for a synchronous circuit depend upon the set-up (positive delay margin) and hold time (negative delay margin) constraints. As shown in [15], a larger delay margin leads to a greater immunity to EMI effects and for a given clock frequency, the immunity is maximized when both the positive and negative delay margins are equal.

### 2.4.3 Temperature variations

Temperature (T) variation is another factor that affects the performance of a circuit. Temperature variations have two primary components, the change in temperature due to the heat generated by the power dissipated on-chip and any changes in the ambient temperature. With increasing circuit densities and greater on-chip power dissipation, the temperature variations due to the heat generated on-chip has become significant. As the die size becomes larger, differences in the temperature occur across an IC. The effects of temperature on performance are therefore non-uniform across a die.

There are three primary circuit parameters that vary with temperature and introduce delay uncertainty [33]. These are the resistivity of the interconnect  $\rho(T)$ , the threshold voltage  $V_{th}(T)$ , and the carrier mobility  $\mu(T)$ . Temperature variations across an IC result in different buffer speeds and wire resistances, directly affecting the signal propagation delay. A simulation of the clock skew due to temperature variation is presented in [14]. The clock skew is based on an H-tree assuming a circular temperature gradient from the center of the IC to the edges. For a temperature variation of  $\Delta T = 30$  K, an average increase in clock skew of 20% is demonstrated for a 0.25  $\mu$ m CMOS technology.

## 2.5 Conclusions

The effects that introduce uncertainty in the signal propagation delay are presented in this chapter. The main sources of delay uncertainty within a CMOS device are variations in the effective channel length, gate oxide thickness, and threshold voltage. The uncertainty of the interconnect delay is caused by varia-

tions in the geometric parameters of a line due to imperfections in the manufacturing process. Noise from signal transitions produce crosstalk among interconnect lines which contributes to the delay uncertainty of the signals propagating along an interconnect line. Finally, variations in system level parameters introduce delay uncertainty to signals at different locations within a die. The effects of variations in the power supply voltage due to the resistance of the interconnect, electromagnetic interference, and temperature variations are specifically discussed.

## Chapter 3

# Performance Enhancements Through Clock Skew Scheduling

The effects that introduce delay uncertainty in various circuit elements are described in Chapter 2. As the device size is scaled and clock frequencies push deeper into the multi-gigahertz frequency levels, timing constraints have become much tighter and delay uncertainty has become increasingly significant. Deviations of the clock and data signals from the target delay can cause incorrect data to be latched within a register resulting in the system malfunctioning. The sensitivity of the circuit elements to these effects has therefore become an issue of fundamental importance to the problem of designing high speed digital integrated circuits.

Increasing the chip size and density adds to the on-chip power dissipation. High power dissipation penalizes the overall system since more advanced packaging and heat removal technology are necessary. Additionally, wider on-chip and off-chip power busses, larger on-chip decoupling capacitors, and more complicated power supplies are required. These factors increase the system size and cost. Furthermore, with the revolution of portable electronic devices, power dissipation

has become a system performance metric, since the operation of these devices is limited by the battery life.

Design techniques and strategies that relax the tight timing constraints and reduce the on-chip power dissipation have been demonstrated on an industrial circuit and are presented in this chapter. To improve the timing margins of the data paths and the circuit speed, non-zero clock skew scheduling has been applied to specific circuit blocks of a high performance microprocessor. The application of this methodology is presented in section 3.1. In order to reduce the power dissipation, a technique that increases the delay of the non-critical data paths to exploit power savings has also been applied to this circuit and is discussed in section 3.2. Finally, some conclussions are reviewed in Section 6.3.

## 3.1 Improving the Timing Constraints and Speed

In this section, the effectiveness of the application of non-zero clock skew scheduling to improve performance and minimize the likelihood of race conditions is demonstrated. Background information about clock skew scheduling is presented in subsection 3.1.1. An algorithm to implement a non-zero clock skew schedule is discussed in subsection 3.1.2. Finally, the demonstration of the application of this technique on certain blocks of an industrial high performance microprocessor is presented in subsection 3.1.3.

## 3.1.1 Background on clock skew scheduling

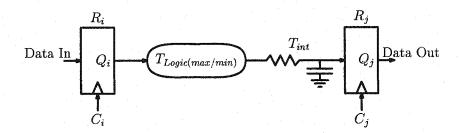

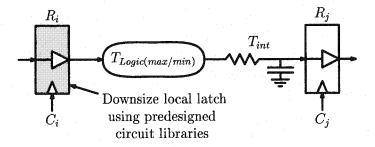

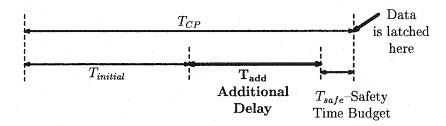

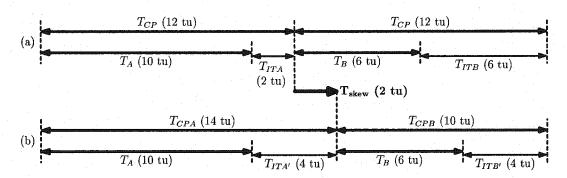

A synchronous digital circuit is composed of a network of functional logic elements and globally clocked registers. Two registers,  $R_i$  and  $R_j$ , in a synchronous

Fig. 3.1: A local data path.

digital circuit are considered sequentially-adjacent if there exists at least one sequence of logic elements and/or interconnect connecting the output of the initial register  $R_i$  to the input of the final register  $R_j$ . A pair of sequentially-adjacent registers together with a logic block and/or interconnect make up a local data path. A data path consisting of one or more local data paths is called a global data path. A local data path composed of two registers,  $R_i$  and  $R_j$ , driven by the clock signals,  $C_i$  and  $C_j$ , respectively, is shown in Fig. 3.1.