### Switching Noise and Timing Characteristics in Nanoscale Integrated Circuits

by

Emre Salman

Submitted in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Supervised by Professor Eby G. Friedman

Department of Electrical and Computer Engineering Arts, Sciences and Engineering School of Engineering and Applied Sciences

> University of Rochester Rochester, New York

> > 2009

## Dedication

This work is dedicated to my parents, Nevin Salman and Ayhan Teoman Salman.

### Curriculum Vitae

Emre Salman was born in Ankara, Turkey in 1981. He received the B.S. degree in microelectronics engineering from Sabancı University, Istanbul, Turkey in 2004, and the M.S. degree in electrical and computer engineering from the University of Rochester, Rochester, NY in 2006, where he is completing the Ph.D. degree in electrical engineering.

He was a co-op student at ST Microelectronics, Istanbul, Turkey between October 2003 and May 2004, where he worked on the design and verification of a clock and data recovery circuit for a multichannel fiber-optic transceiver. During summer 2005, he was a research and development intern at Synopsys, Mountain View, CA, where he worked on pessimism reduction in static timing analysis (STA) and cell library characterization. During summers 2006 and 2007, he was with Freescale Semiconductor, Tempe, AZ, where he worked on noise reduction techniques at the circuit and physical levels in large scale mixed-signal circuits, computationally efficient substrate noise analysis, and signal isolation methodologies with application to

monolithic transceivers in CMOS and BiCMOS technologies.

His primary research expertise is in the field of noise and timing characteristics in mixed-signal and high performance synchronous digital circuits. Specifically, he is interested in the physical codesign of clock and power distribution networks, the interdependence between noise and timing, noise estimation in large scale circuits, and signal isolation methodologies to enhance signal and power integrity.

### **Publications**

#### Journal Papers

- 1. E. Salman, E. G. Friedman, R. M. Secareanu, and O. L. Hartin, "Worst Case Power/Ground Noise Estimation Using an Equivalent Transition Time for Resonance," *IEEE Transactions on Circuits and Systems I: Regular Papers* (in press).

- 2. E. Salman, R. Jakushokas, E. G. Friedman, R. M. Secareanu, and O. L. Hartin, "Methodology for Efficient Substrate Noise Analysis in Large Scale Mixed-Signal Circuits," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* (in press).

- 3. E. Salman, E. G. Friedman, R. M. Secareanu, and O. L. Hartin, "Identification of Dominant Noise Source and Parameter Sensitivity for Substrate Coupling," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* (in press).

- 4. E. Salman, A. Dasdan, F. Taraporevala, K. Küçükçakar, and E. G. Friedman, "Exploiting Setup-Hold Time Interdependence in Static Timing Analysis," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 26, No. 6, pp. 1114–1125, June 2007.

#### **Conference Papers**

- E. Salman, R. Jakushokas, E. G. Friedman, R. M. Secareanu, and O. L. Hartin, "Contact Merging Algorithm for Efficient Substrate Noise Analysis in Large Scale Circuits," *Proceedings of the ACM/IEEE Great Lakes Symposium on VLSI*, May 2009 (in press).

- 6. S. Köse, E. Salman, and E. G. Friedman, "Shielding Methodologies in the Presence of Power/Ground Noise," *Proceedings of the IEEE International Symposium on Circuits and Systems*, May 2009 (in press).

- 7. S. Köse, E. Salman, Z. Ignjatovic, and E. G. Friedman, "Pseudo-Random Clocking to Enhance Signal Integrity," *Proceedings of the IEEE International SOC Conference*, pp. 47–50, September 2008.

- 8. E. Salman and E. G. Friedman, "Methodology for Placing Localized Guard Rings to Reduce Substrate Noise in Mixed-Signal Circuits," *Proceedings of the IEEE Conference on PhD Research on Microelectronics and Electronics*, pp. 85–88, June 2008.

- E. Salman, R. Jakushokas, E. G. Friedman, R. M. Secareanu, and O. L. Hartin, "Input Port Reduction for Efficient Substrate Extraction in Large Scale ICs," Proceedings of the IEEE International Symposium on Circuits and Systems, pp. 376–379, May 2008.

- E. Salman, E. G. Friedman, R. M. Secareanu, and O. L. Hartin, "Equivalent Rise Time for Resonance in Power/Ground Noise Estimation," *Proceedings of* the IEEE International Symposium on Circuits and Systems, pp. 2422–2425, May 2008.

- 11. E. Salman, E. G. Friedman, R. M. Secareanu, and O. L. Hartin, "Dominant Substrate Noise Coupling Mechanism for Multiple Switching Gates," *Proceedings of the IEEE International Symposium on Quality Electronic Design*, pp. 261–266, March 2008.

- 12. E. Salman, E. G. Friedman, R. M. Secareanu, and O. L. Hartin, "Substrate Noise Reduction Based on Noise Aware Cell Design," *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 3227–3230, May 2007.

- E. Salman, E. G. Friedman, and R. M. Secareanu "Substrate and Ground Noise Interactions in Mixed-Signal Circuits," *Proceedings of the IEEE International* SOC Conference, pp. 293–296, September 2006.

- 14. E. Salman, A. Dasdan, F. Taraporevala, K. Küçükçakar, and E. G. Friedman, "Pessimism Reduction in Static Timing Analysis Using Interdependent Setup and Hold Times," *Proceedings of the IEEE International Symposium on Quality Electronic Design*, pp. 159–164, March 2006.

- 15. E. Salman, H. Akın, Ö. Gürsoy, A. Ergintav, I. Tekin, A. Bozkurt, and Y. Gürbüz "Design of a 3.2 mW PLL Based Clock and Data Recovery Circuit in 90 nm CMOS Technology," Proceedings of the Mediterranean Microwave Symposium, September 2005.

#### Patent Disclosures

- 16. R. M. Secareanu, O. L. Hartin, and E. Salman, "Apparatus and Method for Reducing Noise in Mixed-Signal Circuits and Digital Circuits," United States patent pending.

- 17. A. Dasdan, E. Salman, F. Taraporevala, and K. Küçükçakar, "Characterizing Sequential Cells Using Interdependent Setup and Hold Times, and Utilizing the Sequential Cell Characterization in Static Timing Analysis" United States Patent, No. 7,506,293.

## Acknowledgments

The years I spent at the University of Rochester have been full of unforgettable memories. Thanks to many people who deserve my highest gratitude.

First of all, I am deeply grateful to my academic advisor, Professor Eby G. Friedman. I wish I could find a word to better describe his role in this process since he has been much more than just an academic advisor. His mentorship in my research, motivation, dedication, consideration, and generosity were the primary reasons that made me greatly enjoy my last years as a student. He not only gave me the opportunity to complete my doctoral degree, but also provided valuable insight and vision for my professional career. I always feel how lucky I am in having Professor Eby G. Friedman as my advisor. Thank you Professor.

I would like to thank Professors Michael Huang, Paul Ampadu, and Jim Zavislan for serving on my proposal and defense committees. The valuable comments they provided have greatly improved my dissertation. I would also like to express my appreciation to the University of Rochester, and specifically, the Department of

Electrical and Computer Engineering for providing such a friendly and encouraging environment with all the required tools to support high quality academic research.

I am grateful to Dr. Radu M. Secareanu of Freescale Semiconductor for the collaboration, friendship, and technical discussions we enjoyed during my summer internships and over the phone during my academic years. He contributed significantly to my academic research by providing valuable feedback. I would also like to thank Dr. Olin L. Hartin for providing me with the opportunity of two summer internships at Freescale Semiconductor. I would also like to express my gratitude to Marie Burnham and Dr. Len Borucki for their advice on my studies, listening to my presentations, and very sincere friendship during my two warm summers in Arizona.

I thank Dr. Ali Dasdan for his mentorship, collaboration, and suggestions during my internship at Synopsys. I am also grateful to Feroze Taraporevala and Dr. Kayhan Küçükçakar for giving me the opportunity to work at Synopsys, where I had a very fruitful start to my doctoral studies.

I also acknowledge the previous and current members of the High Performance VLSI/IC Design and Analysis Laboratory: Dr. Guoqing Chen, Dr. Mikhail Popovich, Dr. Vasilis Pavlidis, Jonathan Rosenfeld, Renatas Jakushokas, Ioannis Savidis, and Selçuk Köse for their companionship and support. I also thank RuthAnn Williams for her friendship, motivating discussions, and constant help on the administrative side.

I am grateful to all of my friends in Turkey and those in the United States for making it easier to be so far away from home. I thank my relatives for their understanding and support. Last, but not least, I express my deepest appreciation to my parents Nevin Salman and Ayhan Teoman Salman to whom I owe not only my success but every step of my life.

This research was supported in part by the Semiconductor Research Corporation under Contract No. 2004-TJ-1207, the National Science Foundation under Contract No. CCF-0541206, grants from the New York State Office of Science, Technology & Academic Research to the Center for Advanced Technology in Electronic Imaging Systems, and by grants from Intel Corporation, Eastman Kodak Corporation, and Freescale Semiconductor Corporation.

### Abstract

Continuous progress in the design and manufacturing of integrated circuits (ICs) has enabled the integration of more than two billion transistors on the same die with clock frequencies well above several gigahertz. These improvements have triggered the era of system-on-chip (SoC) and system-in-package (SiP), drastically changing the classical understanding of noise in complex ICs. Traditionally, device noise has been the primary concern for analog ICs while digital ICs have typically been considered to be relatively immune to noise. This situation has changed significantly due to denser integration and faster signal transition times. Specifically, *switching noise* has become a primary design criterion for both mixed-signal and high performance synchronous digital ICs.

Voltage fluctuations on the power/ground nodes of a circuit, *i.e.*, power/ground noise, is a type of switching noise affecting both mixed-signal and digital ICs. A methodology is proposed to accurately estimate the worst case power/ground noise in an inductive power/ground distribution network with a decoupling capacitor. In

mixed-signal ICs, power/ground noise affects the highly sensitive analog/RF blocks through the monolithic substrate, degrading critical performance parameters such as gain, bandwidth, dynamic range, total harmonic distortion, and phase noise. Several approaches are presented to efficiently model and alleviate substrate noise coupling in mixed-signal ICs. The proposed analysis process determines the noise characteristics of a circuit, thereby identifying appropriate noise isolation techniques. A methodology is also proposed to reduce noise by incorporating noise-aware standard cells. The proposed methodologies and algorithms are validated with industrial circuits, exhibiting significant improvement in computational efficiency while maintaining sufficient accuracy in the noise voltage. A significant reduction in substrate coupling noise is also demonstrated.

In synchronous digital ICs, switching noise affects the timing characteristics of a circuit by generating additional delay uncertainty, possibly degrading system performance or causing a circuit to fail. Interdependent setup and hold times are characterized and exploited to compensate for delay uncertainty, producing a more robust circuit tolerant to switching noise. The proposed algorithms are demonstrated on industrial circuits, verifying the efficiency of exploiting interdependence in reducing delay uncertainty. The research presented in this dissertation provides methodologies and algorithms for designing both mixed-signal and synchronous digital ICs with superior noise performance and enhanced signal integrity.

## Contents

| D              | edica | tion              |                                                             | i    |

|----------------|-------|-------------------|-------------------------------------------------------------|------|

| $\mathbf{C}_1$ | urric | ulum `            | Vitae                                                       | iii  |

| $\mathbf{A}$   | ckno  | wledgr            | ments                                                       | vi   |

| $\mathbf{A}$   | bstra | ıct               |                                                             | Х    |

| Li             | st of | Table             | s                                                           | xvii |

| Li             | st of | Figur             | es                                                          | XX   |

| 1              | Intr  | roducti           | ion                                                         | 1    |

|                | 1.1   | Noise             | in Electrical Circuits                                      | 6    |

|                |       | 1.1.1             | Active and Passive Device Noise                             | 7    |

|                |       | 1.1.2             | Switching Noise                                             | 10   |

|                | 1.2   | Disser            | tation Outline                                              | 11   |

| 2              | Swi   | $\mathbf{tching}$ | Noise in Synchronous Digital Integrated Circuits            | 16   |

|                | 2.1   | Power             | Ground Noise                                                | 20   |

|                |       | 2.1.1             | Power and Ground Distribution Networks                      | 20   |

|                |       | 2.1.2             | Impedance Characteristics of a Power Distribution Network . | 24   |

|                |       | 2.1.3             | Decoupling Capacitance                                      | 27   |

|                | 2.2   | Interc            | onnect Coupling Noise: Crosstalk                            | 32   |

|                |       | 2.2.1             | Ideal vs. Realistic Interconnect Scaling                    | 32   |

|   |     | 2.2.2   | Capacitive Coupling                                         | 35  |

|---|-----|---------|-------------------------------------------------------------|-----|

|   |     | 2.2.3   | Inductive Coupling                                          | 41  |

|   | 2.3 | Effects | s of Switching Noise in Digital ICs                         | 44  |

|   |     | 2.3.1   | Functional Failure                                          | 45  |

|   |     | 2.3.2   | Glitch Power Consumption                                    | 50  |

|   |     | 2.3.3   | Increased Delay Uncertainty                                 | 52  |

|   | 2.4 | Techn   | iques to Reduce Switching Noise in Digital ICs              | 58  |

|   |     | 2.4.1   | Power/Ground Noise Reduction                                | 58  |

|   |     | 2.4.2   | Reduction of Interconnect Coupling Noise                    | 65  |

|   | 2.5 | Chapt   | er Summary                                                  | 76  |

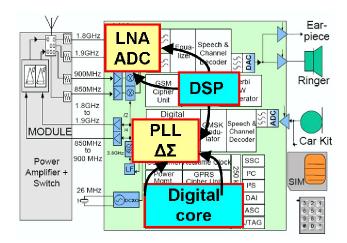

| 3 | Swi | tching  | Noise in Mixed-Signal/Analog Integrated Circuits            | 82  |

|   | 3.1 | _       | ning Noise Coupling Mechanisms in Mixed-Signal/Analog ICs . | 84  |

|   |     | 3.1.1   | Interconnect Coupling                                       | 86  |

|   |     | 3.1.2   | Substrate Coupling                                          | 87  |

|   | 3.2 | Substi  | rate Noise Coupling in Mixed-Signal ICs                     | 88  |

|   |     | 3.2.1   | Substrate Noise Injection Mechanisms                        | 89  |

|   |     | 3.2.2   | Substrate Extraction Techniques                             | 93  |

|   |     | 3.2.3   | Compact Substrate Models                                    | 99  |

|   |     | 3.2.4   | High Level Substrate Noise Analysis                         | 103 |

|   | 3.3 | Effects | s of Substrate Noise in Mixed-Signal ICs                    | 108 |

|   |     | 3.3.1   | Effect of Substrate Noise on a Low Noise Amplifier          | 110 |

|   |     | 3.3.2   | Effect of Substrate Noise on a Phase Locked Loop            | 111 |

|   |     | 3.3.3   | Effect of Substrate Noise on a Sigma-Delta Data Converter   | 114 |

|   | 3.4 | Techn   | iques to Reduce Substrate Noise                             |     |

|   |     | in Mix  | ked-Signal/Analog ICs                                       | 116 |

|   |     | 3.4.1   | Physical Separation                                         | 117 |

|   |     | 3.4.2   | Guard Rings                                                 | 119 |

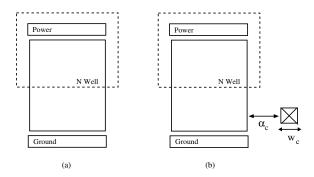

|   |     | 3.4.3   | Deep N-Well Isolation                                       | 123 |

|   |     | 3.4.4   | Silicon-on-Insulator (SOI) Technology                       | 125 |

|   |     | 3.4.5   | Differential Signaling                                      | 127 |

|   | 3.5                                                       | Chapt    | er Summary                                                        | 128  |  |  |

|---|-----------------------------------------------------------|----------|-------------------------------------------------------------------|------|--|--|

| 4 | Equ                                                       | ıivalent | t Transition Time for Resonant Frequency                          | 134  |  |  |

|   | 4.1                                                       | Power    | Ground Noise Model                                                | 137  |  |  |

|   | 4.2                                                       | Non-m    | nonotonic Noise Behavior                                          | 144  |  |  |

|   |                                                           | 4.2.1    | Worst Case Transition Time                                        | 144  |  |  |

|   |                                                           | 4.2.2    | Noise Sensitivity as a Function of Transition Time                | 150  |  |  |

|   | 4.3                                                       | Conclu   | isions                                                            | 152  |  |  |

| 5 | Sub                                                       | strate   | and Ground Noise Interactions in Mixed-Signal Circuits            | 3154 |  |  |

|   | 5.1                                                       | Backgr   | round                                                             | 156  |  |  |

|   | 5.2                                                       | Circui   | t Models and Superposition Technique                              | 159  |  |  |

|   | 5.3                                                       | Simula   | ation Results                                                     | 161  |  |  |

|   |                                                           | 5.3.1    | PWL Current Estimation                                            | 161  |  |  |

|   |                                                           | 5.3.2    | Effect of the Substrate on Ground Noise                           | 163  |  |  |

|   | 5.4                                                       | Summ     | ary                                                               | 164  |  |  |

| 6 | Dominant Substrate Noise Coupling with Multiple Switching |          |                                                                   |      |  |  |

|   | Gat                                                       | es       |                                                                   | 167  |  |  |

|   | 6.1                                                       | Previo   | us Work                                                           | 169  |  |  |

|   | 6.2                                                       | Substr   | ate Coupling Model to Estimate Noise                              | 170  |  |  |

|   |                                                           | 6.2.1    | Substrate Coupling for a Single Switching Gate                    | 171  |  |  |

|   |                                                           | 6.2.2    | Substrate Coupling Model for Multiple Switching Gates             | 173  |  |  |

|   |                                                           | 6.2.3    | Extraction of Parameters and Model Validation $\ \ldots \ \ldots$ | 175  |  |  |

|   | 6.3                                                       | Domin    | ant Substrate Noise Coupling Mechansism                           | 177  |  |  |

|   |                                                           | 6.3.1    | Effect of Circuit Size on the Dominant Noise Coupling Mechanism   | n178 |  |  |

|   |                                                           | 6.3.2    | Effect of Rise Time, Inductance, and Capacitance on Dominant      |      |  |  |

|   |                                                           |          | Noise Coupling Mechanism                                          | 180  |  |  |

|   | 6.4                                                       | Param    | eter Sensitivity                                                  | 184  |  |  |

|   | 6.5                                                       | Design   | Implications                                                      | 186  |  |  |

|   |                                                           | 6.5.1    | Increasing Substrate Contact Density                              | 186  |  |  |

|   |      | 6.5.2                  | Increasing Decoupling Capacitance vs. Reducing Parasitic In- |     |

|---|------|------------------------|--------------------------------------------------------------|-----|

|   |      |                        | ductance                                                     | 189 |

|   | 6.6  | Summ                   | nary                                                         | 189 |

| 7 | Effi | cient S                | Substrate Noise Analysis in Large Scale Mixed-Signal         |     |

|   | Circ | $\operatorname{cuits}$ |                                                              | 191 |

|   | 7.1  | Voltag                 | ge Domains Within the Substrate                              | 193 |

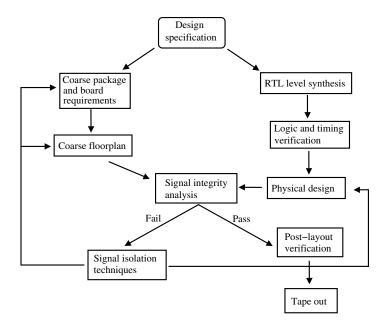

|   | 7.2  | Substi                 | rate Noise Analysis Methodology                              | 195 |

|   |      | 7.2.1                  | Theoretical Analysis                                         | 199 |

|   |      | 7.2.2                  | Contact Merging Algorithm                                    | 203 |

|   |      | 7.2.3                  | Bounds on Error                                              | 211 |

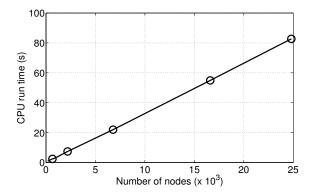

|   |      | 7.2.4                  | Complexity Analysis                                          | 213 |

|   | 7.3  | Simula                 | ation Results                                                | 214 |

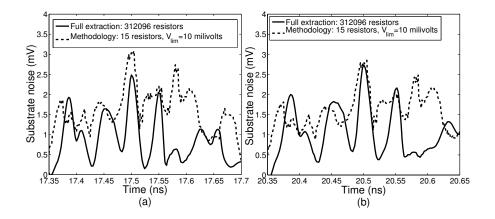

|   |      | 7.3.1                  | Circuit 1                                                    | 215 |

|   |      | 7.3.2                  | Circuit 2                                                    | 221 |

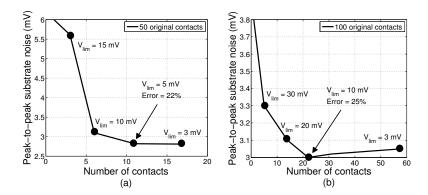

|   |      | 7.3.3                  | Proper Selection of $V_{lim}$                                | 228 |

|   | 7.4  | Limita                 | ations                                                       | 230 |

|   | 7.5  | Summ                   | nary                                                         | 231 |

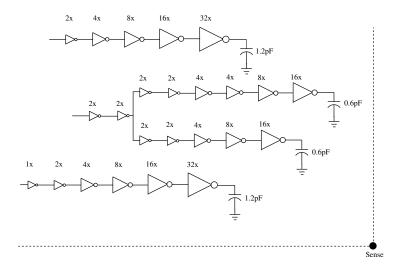

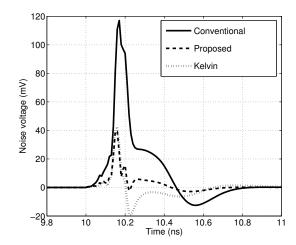

| 8 | Sub  | strate                 | Noise Reduction Based on Noise Aware Cell Design             | 233 |

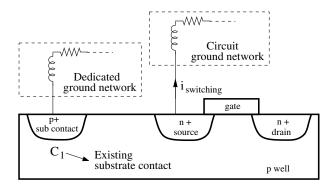

|   | 8.1  | Substi                 | rate Biasing Schemes                                         | 234 |

|   | 8.2  | Propo                  | sed Methodology                                              | 236 |

|   |      | 8.2.1                  | Standard Cell with a Dedicated Substrate Contact             | 236 |

|   |      | 8.2.2                  | Analysis of Noise Reduction Mechanism                        | 238 |

|   | 8.3  | Simula                 | ation Results                                                | 242 |

|   | 8.4  |                        | ssion                                                        | 245 |

|   | 8.5  | Summ                   | nary                                                         | 246 |

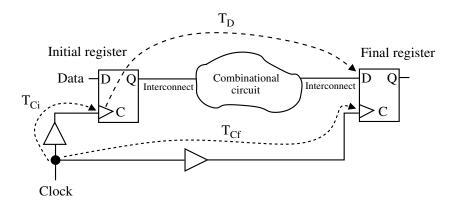

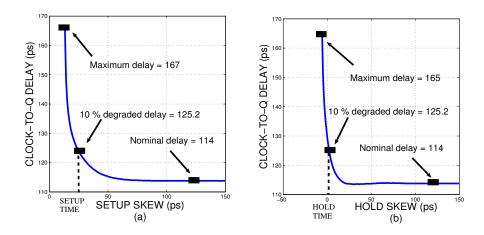

| 9 | Exp  | oloiting               | g Setup-Hold Time Interdependence in Timing Analysis         | 247 |

|   | 9.1  | Backg                  | round                                                        | 250 |

|   |      | 9.1.1                  | Timing Characteristics of Synchronous Circuits               | 250 |

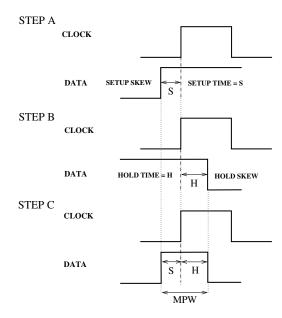

|   |      | 9.1.2                  | Setup / Hold Times and Skews                                 | 252 |

|    | 9.2                                                      | Proble                                                                                 | m Formulation                                                                       | 253                                                  |

|----|----------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|

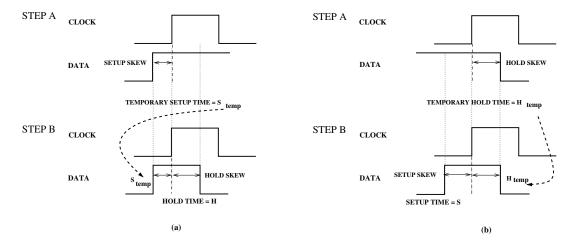

|    |                                                          | 9.2.1                                                                                  | Existing Characterization Approaches                                                | 254                                                  |

|    |                                                          | 9.2.2                                                                                  | Interdependence Between Setup and Hold Times                                        | 255                                                  |

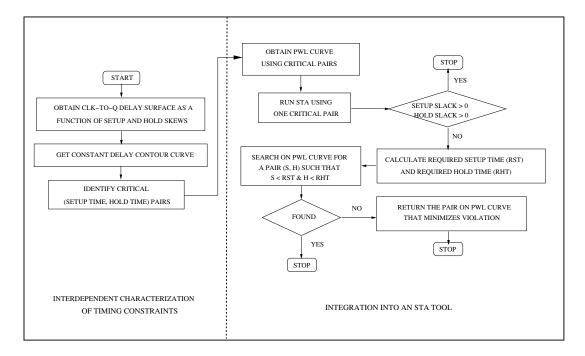

|    | 9.3                                                      | Propos                                                                                 | sed Methodology                                                                     | 259                                                  |

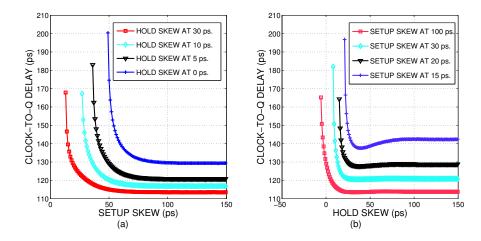

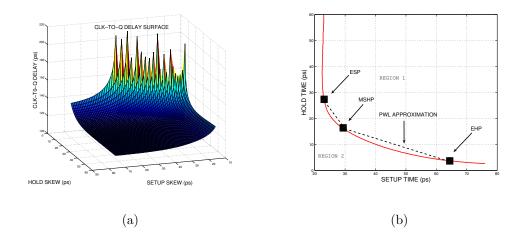

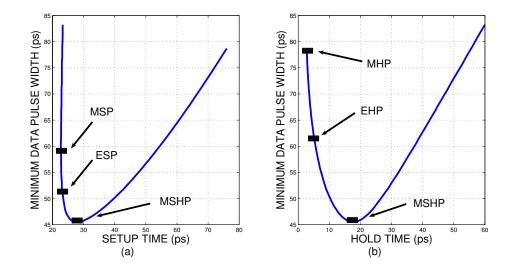

|    |                                                          | 9.3.1                                                                                  | CLK-to-Q Delay Surface                                                              | 261                                                  |

|    |                                                          | 9.3.2                                                                                  | Constant Delay Contour                                                              | 262                                                  |

|    |                                                          | 9.3.3                                                                                  | Critical Pairs on Contour                                                           | 263                                                  |

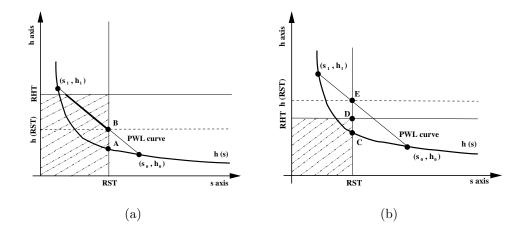

|    |                                                          | 9.3.4                                                                                  | Piecewise Linear (PWL) Approximation of Contour                                     | 265                                                  |

|    |                                                          | 9.3.5                                                                                  | Integration of Interdependent Characterization into STA $$                          | 268                                                  |

|    |                                                          | 9.3.6                                                                                  | Limitations                                                                         | 273                                                  |

|    | 9.4                                                      | STA R                                                                                  | Results                                                                             | 274                                                  |

|    | 9.5                                                      | Summ                                                                                   | ary                                                                                 | 279                                                  |

| 10 | D . 1                                                    |                                                                                        |                                                                                     |                                                      |

| 10 | 0 Reducing Delay Uncertainty Using Interdependent Timing |                                                                                        |                                                                                     |                                                      |

|    |                                                          | straint                                                                                |                                                                                     | 280                                                  |

|    |                                                          |                                                                                        | m Formulation                                                                       | 282                                                  |

|    | 10.2                                                     | -Metho                                                                                 | dology to Roduco Dolay Uncortainty and Components for Vari                          |                                                      |

|    |                                                          |                                                                                        | dology to Reduce Delay Uncertainty and Compensate for Vari-                         | 205                                                  |

|    |                                                          | ations                                                                                 |                                                                                     | 285                                                  |

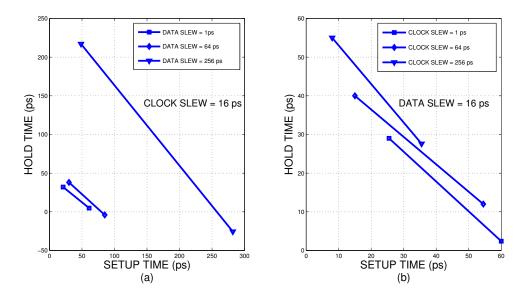

|    |                                                          | ations<br>10.2.1                                                                       | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285                                                  |

|    |                                                          | ations<br>10.2.1<br>10.2.2                                                             | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285<br>288                                           |

|    |                                                          | ations<br>10.2.1<br>10.2.2                                                             | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285                                                  |

|    |                                                          | ations<br>10.2.1<br>10.2.2<br>10.2.3                                                   | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285<br>288                                           |

|    |                                                          | ations<br>10.2.1<br>10.2.2<br>10.2.3<br>10.2.4                                         | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285<br>288<br>291                                    |

|    | 10.3                                                     | ations<br>10.2.1<br>10.2.2<br>10.2.3<br>10.2.4<br>10.2.5                               | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285<br>288<br>291<br>293                             |

|    | 10.3                                                     | ations<br>10.2.1<br>10.2.2<br>10.2.3<br>10.2.4<br>10.2.5<br>Case S                     | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285<br>288<br>291<br>293<br>297<br>299               |

|    | 10.3                                                     | ations<br>10.2.1<br>10.2.2<br>10.2.3<br>10.2.4<br>10.2.5<br>Case S<br>10.3.1           | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285<br>288<br>291<br>293<br>297<br>299               |

|    | 10.3                                                     | ations<br>10.2.1<br>10.2.2<br>10.2.3<br>10.2.4<br>10.2.5<br>Case S<br>10.3.1<br>10.3.2 | Obtaining Linear $T_S$ vs. $T_H$ Relationship                                       | 285<br>288<br>291<br>293<br>297<br>299<br>300<br>303 |

|    |                                                          | ations 10.2.1 10.2.2 10.2.3 10.2.4 10.2.5 Case S 10.3.1 10.3.2 10.3.3                  | Obtaining Linear $T_S$ vs. $T_H$ Relationship Procedure to Reduce Delay Uncertainty | 285<br>288<br>291<br>293<br>297<br>299<br>300        |

| 12 Future Work                                        |     |  |  |

|-------------------------------------------------------|-----|--|--|

| 12.1 Unified Noise Analysis Methodology:              |     |  |  |

| Chip-Package-Board                                    | 317 |  |  |

| 12.2 Timing Aware Power Grid Design                   | 319 |  |  |

| 12.3 Effect of Substrate Isolation on Power Integrity | 321 |  |  |

| 12.4 Summary                                          | 322 |  |  |

| Bibliography                                          |     |  |  |

| Appendices                                            |     |  |  |

| A An Upper Bound on the Error                         | 346 |  |  |

## List of Tables

| 2.1 | Scaling characteristics of local and global interconnects for four dif-       |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | ferent scaling scenarios: ideal, quasi-ideal, constant resistance, and        |     |

|     | constant thickness. $S$ is the scaling factor for the local interconnects     |     |

|     | and $S_c$ is the scaling factor for the die size                              | 34  |

| 2.2 | The dependence of coupling capacitance on the signal switching char-          |     |

|     | acteristics                                                                   | 38  |

| 4.1 | Comparison of the peak-to-peak ground noise analytically obtained at          |     |

|     | $t_{r,wc} = 2\sqrt{L_gC_d}$ with the peak-to-peak noise obtained by SPICE for |     |

|     | different parasitic ground network impedances                                 | 148 |

| 4.2 | Effect of the decoupling capacitance on reducing the peak-to-peak             |     |

|     | ground noise. $L_g = 1 \ nH$                                                  | 151 |

| 4.3 | Effect of the parasitic inductance on reducing the peak-to-peak ground        |     |

|     | noise. $C_d = 10 \ pF$                                                        | 151 |

| 5.1 | Absolute (abs) and relative (rel) contribution of the source and bulk         |     |

|     | currents to the ground noise voltage for three gates: inverter (INV),         |     |

|     | NAND, and NOR. The negative and positive peak noise is listed for             |     |

|     | both the high-to-low and low-to-high output transitions                       | 165 |

| 6.1 | Extracted parameters characterizing an inverter                               | 176 |

| 6.2 | Effect of the decoupling capacitance, parasitic inductance, and sub-          |     |

|     | strate contact density on reducing the peak-to-peak substrate noise at        |     |

|     | various operating points                                                      | 187 |

| 7.1  | Error comparison due to merging contacts obtained by SPICE and                          |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | (7.4) for different noise voltages                                                      | 203 |

| 7.2  | Original and updated $R(node)$ values of $C_{41}$ to $C_{48}$ for different values      |     |

|      | of $V_{lim}$                                                                            | 217 |

| 7.3  | Reduction in the number of extracted substrate resistors, Peak-to-peak                  |     |

|      | (P-P) and RMS substrate noise at the sense node, and the correspond-                    |     |

|      | ing error in the substrate noise for different values of $V_{lim}$ in Circuit           |     |

|      | 1                                                                                       | 220 |

| 7.4  | Original and updated $R(node)$ and $L(node)$ values of $C_{43}$ to $C_{49}$ for         |     |

|      | various values of $V_{lim}$                                                             | 222 |

| 7.5  | Reduction in the number of extracted substrate resistors, substrate                     |     |

|      | noise at the sense node, and the corresponding error in the substrate                   |     |

|      | noise for different values of $V_{lim}$ in Circuit 2                                    | 225 |

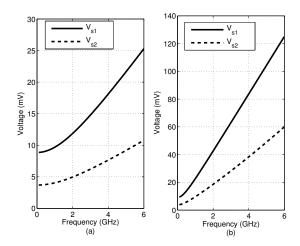

| 8.1  | Comparison of peak-to-peak substrate noise voltage for the conven-                      |     |

|      | tional, Kelvin, and proposed techniques. On-chip interconnect par-                      |     |

|      | asitic impedances: $R=3$ $\Omega$ and $L=160$ pH. Flip-chip parasitic                   |     |

|      | impedances: $R = 0.1 \Omega$ and $L = 60 \text{ pH}$ . Bond-wire parasitic impedances:  |     |

|      | $R=0.2~\Omega$ and $L=1~\mathrm{nH.}$                                                   | 245 |

| 9.1  | Absolute (abs) and Relative (rel) improvements of two circuits with                     |     |

|      | respect to library 3. WNS is the worst negative slack. $\Delta$ WNS is the              |     |

|      | increase in WNS, and $\Delta N$ is the decrease in the number of violations.            | 276 |

| 10.1 | Variation of the critical points due to a 10% decrease in the power                     |     |

|      | supply voltage.                                                                         | 292 |

| 10.2 | Variation of critical points due to a 10% increase in the power supply                  |     |

|      | voltage.                                                                                | 292 |

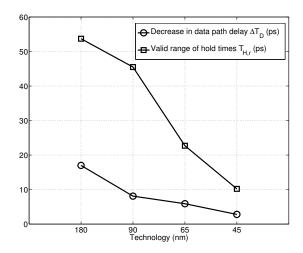

| 10.3 | Power supply voltage, clock-to-Q delay, and critical points $T_{S,min}$ , $T_{H,max}$ , |     |

|      | $T_{S,max}$ , $T_{H,min}$ , $T_{S,r}$ , and $T_{H,r}$ for each technology               | 302 |

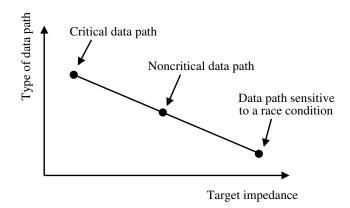

| 10.4 | Increase in the delay of the critical data path (shown in Fig. 10.12)                   |     |

|      | caused by a 10% drop in the power supply voltage                                        | 304 |

| 10.5 | Decrease in the delay of the data path shown in Fig. 10.13 due to a    |     |

|------|------------------------------------------------------------------------|-----|

|      | 10% increase in the power supply voltage                               | 305 |

| 10.6 | Compensation of delay uncertainty caused by power noise for a critical |     |

|      | data path                                                              | 308 |

| 10.7 | Compensation of delay uncertainty caused by power noise for a short    |     |

|      | path                                                                   | 308 |

# List of Figures

| 1.1 | Photographs of the first transistor: (a) point-contact transistor by      |    |

|-----|---------------------------------------------------------------------------|----|

|     | Bardeen and Brattain, (b) bipolar junction transistor by Shockley         | 3  |

| 1.2 | Photographs of the first integrated circuits: (a) built by Texas Instru-  |    |

|     | ments in 1958 using discrete wires as interconnections, (b) built by      |    |

|     | Fairchild Semiconductor using a planar process technology                 | 3  |

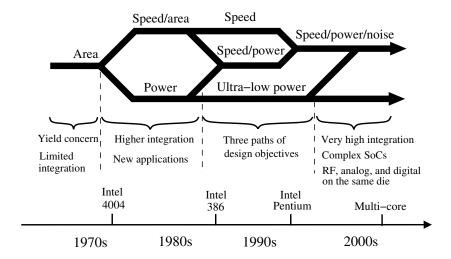

| 1.3 | Evolution of design objectives for integrated circuits                    | 4  |

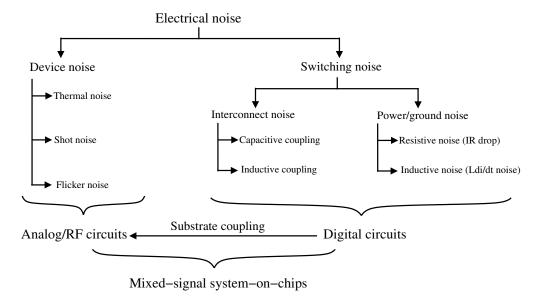

| 1.4 | Classification of noise in electrical circuits. Device noise is a primary |    |

|     | concern for analog/RF circuits. Switching noise originates in digital     |    |

|     | circuits and affects the analog/RF circuits through substrate coupling.   | 6  |

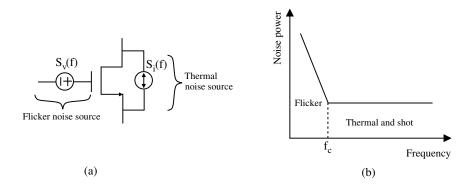

| 1.5 | Thermal and flicker noise in an NMOS transistor: (a) Thermal noise is     |    |

|     | modeled as a current source between the drain and source, and flicker     |    |

|     | noise is modeled as a voltage source at the gate of the transistor, (b)   |    |

|     | variation of noise power as a function of frequency                       | 10 |

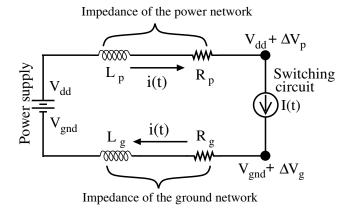

| 2.1 | Power and ground noise due to the switching current flowing through       |    |

|     | the power and ground network impedances                                   | 18 |

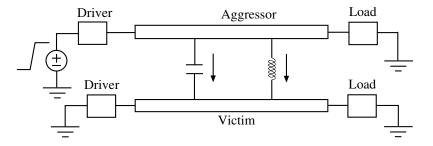

| 2.2 | Interconnect noise due to capacitive and inductive coupling from a        |    |

|     | switching aggressor node to a victim node                                 | 18 |

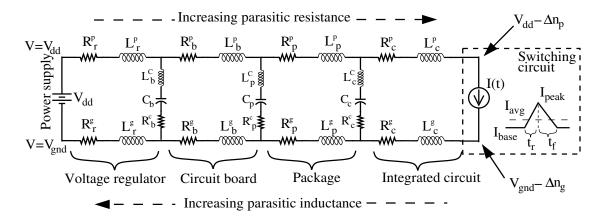

| 2.3 | Simplified circuit level representation of a power distribution system.   | 21 |

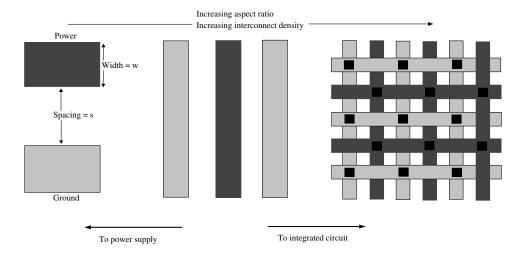

| 2.4 | Change in the physical characteristics of the power/ground intercon-      |    |

|     | nects from the power supply to the integrated circuit                     | 22 |

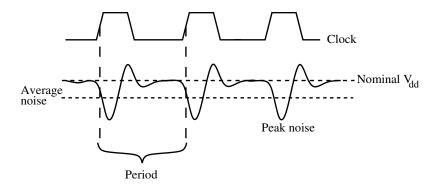

| 2.5 | Clock waveform and the corresponding peak and average power noise         |    |

|     | in the time domain                                                        | 24 |

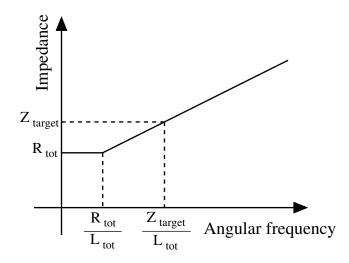

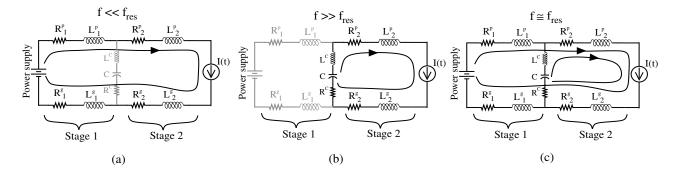

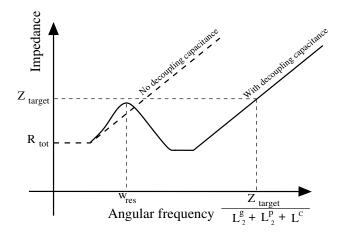

| 2.6  | Impedance characteristics of a power distribution network with no de-             |  |

|------|-----------------------------------------------------------------------------------|--|

|      | coupling capacitance                                                              |  |

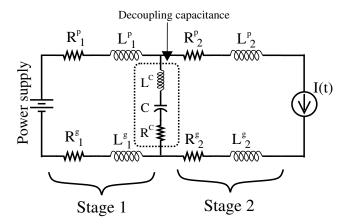

| 2.7  | A circuit model of a power distribution system with a decoupling ca-              |  |

|      | pacitance. Stage 1 represents the impedance between the decoupling                |  |

|      | capacitance and the power supply. Stage 2 represents the impedance                |  |

|      | between the decoupling capacitance and the switching circuit. $\ \ldots \ \ldots$ |  |

| 2.8  | The switching current distribution as a function of frequency in a power          |  |

|      | distribution network with a decoupling capacitance: (a) At frequencies            |  |

|      | $f \ll f_{res}$ , most of the current is provided by the power supply. The        |  |

|      | decoupling capacitance does not affect the power noise. (b) At fre-               |  |

|      | quencies $f >> f_{res}$ , most of the current is provided by the decoupling       |  |

|      | capacitance, bypassing the parasitic impedance of stage 1. The decou-             |  |

|      | pling capacitance reduces the power noise. (c) At frequencies close to            |  |

|      | the resonant frequency, both the power supply and decoupling capac-               |  |

|      | itance provide current, giving rise to resonant behavior. The power               |  |

|      | noise increases due to the high impedance of the power distribution               |  |

|      | network                                                                           |  |

| 2.9  | Impedance characteristics of a power distribution network with a de-              |  |

|      | coupling capacitance                                                              |  |

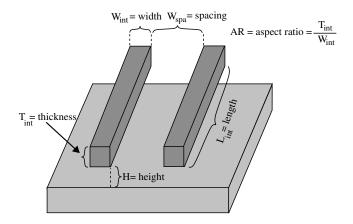

| 2.10 | Physical dimensions of two parallel conductors located on the same                |  |

|      | metalization layer                                                                |  |

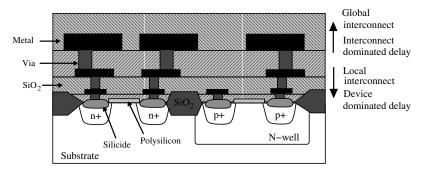

| 2.11 | Local versus global interconnects. Global interconnects are typically             |  |

|      | located on the upper metal layers while the local interconnects are               |  |

|      | closer to the devices                                                             |  |

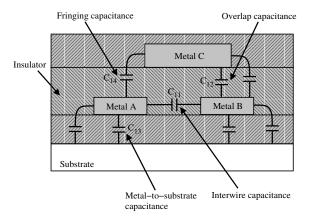

| 2.12 | Capacitive components among three metal wires                                     |  |

| 2.13 | Capacitively coupled interconnects driven by CMOS inverters. The                  |  |

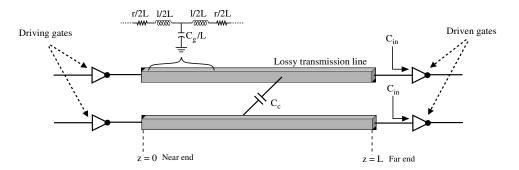

|      | interconnects are represented as lossy transmission lines                         |  |

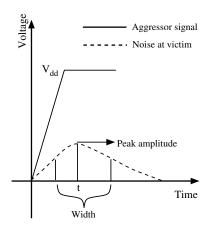

| 2.14 | Coupling noise induced on the victim line due to signal switching on              |  |

|      | the aggressor line                                                                |  |

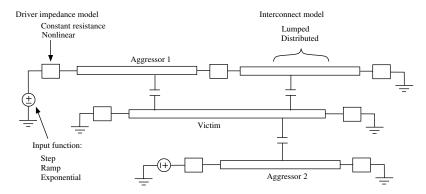

| 2.15 | Primary modeling issues for coupling noise: Type of input excitation,               |    |

|------|-------------------------------------------------------------------------------------|----|

|      | impedance model of the driver, interconnect model, and location and                 |    |

|      | number of aggressors affecting the victim line                                      | 39 |

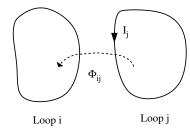

| 2.16 | The loop inductance relates the magnetic flux in loop $i$ induced by the            |    |

|      | current in loop $j$                                                                 | 42 |

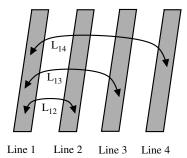

| 2.17 | The long range effect of inductive coupling where the mutual induc-                 |    |

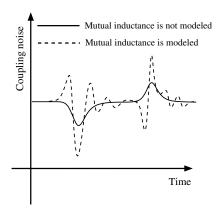

|      | tance among nonadjacent interconnects is not negligible                             | 43 |

| 2.18 | The effect of mutual inductance on coupling noise characteristics                   | 44 |

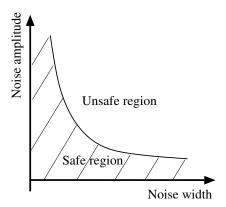

| 2.19 | Typical noise tolerance curve of a gate based on the noise amplitude                |    |

|      | and width                                                                           | 45 |

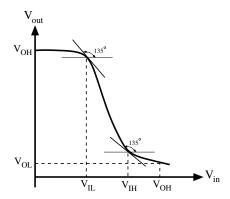

| 2.20 | Typical DC voltage transfer characteristics of an inverter                          | 46 |

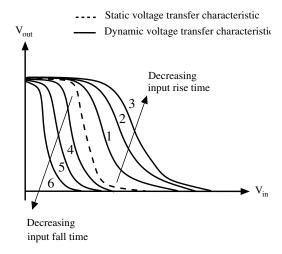

|      | Dynamic voltage transfer characteristics of a CMOS inverter for various             |    |

|      | input transitions                                                                   | 48 |

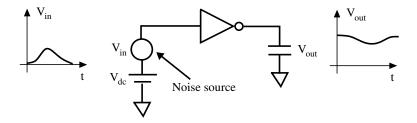

| 2.22 | Time domain DC noise sensitivity of a CMOS inverter                                 | 49 |

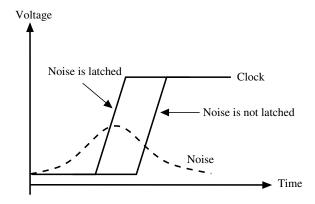

|      | Alignment of the noise pulse with the clock signal to determine whether             |    |

|      | the noise is latched into the memory element                                        | 51 |

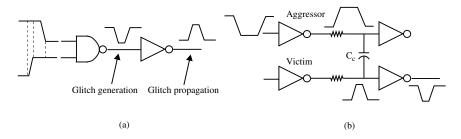

| 2.24 | Generation and propagation of a glitch due to two different reasons:                |    |

|      | (a) Misalignment of the switching times of the input signals. (b) Ca-               |    |

|      | pacitive coupling among interconnects                                               | 51 |

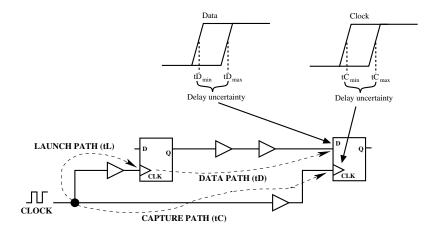

| 2.25 | Variation in the arrival time of the data and clock signals, described              | 01 |

| 0    | as delay uncertainty.                                                               | 53 |

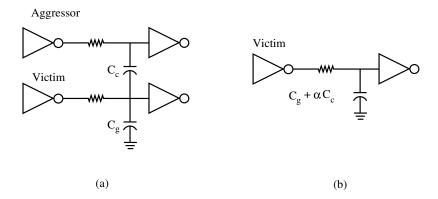

| 2.26 | Transformation of a capacitively coupled interconnect into a decoupled              | 00 |

| 0    | interconnect using the Miller factor: (a) Two capacitively coupled in-              |    |

|      | terconnects, (b) Decoupled interconnect using the Miller factor                     | 54 |

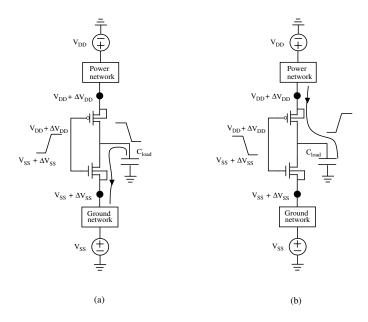

| 2 27 | Power noise $\Delta V_{DD}$ and ground noise $\Delta V_{SS}$ appear at the input of | 01 |

| 2.21 | the gate assuming a single power and ground pin: (a) High-to-low                    |    |

|      | transition of the output. (b) Low-to-high transition of the output                  | 56 |

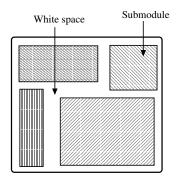

| 2 28 | Illustration of white space utilized for decoupling capacitor placement.            | 59 |

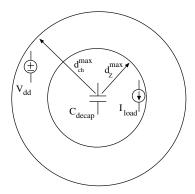

|      | Effective radii of the decoupling capacitor as determined by the target             | υg |

| 4.49 |                                                                                     | 60 |

|      | impedance and charge time                                                           | 60 |

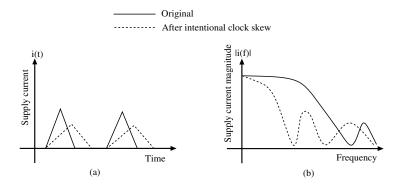

| 2.30 | Supply current before and after intentional clock skew to reduce power   |  |

|------|--------------------------------------------------------------------------|--|

|      | noise: (a) In the time domain. (b) In the frequency domain               |  |

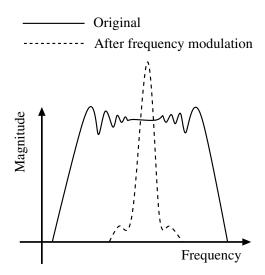

| 2.31 | Reduction in the peak amplitude of a harmonic due to frequency mod-      |  |

|      | ulation of the trapezoidal clock signal                                  |  |

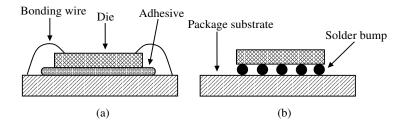

| 2.32 | Two different bonding techniques to connect the die pads and package:    |  |

|      | (a) Wire bonding. (b) Solder bump bonding using flip-chip technique.     |  |

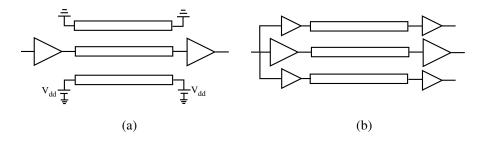

| 2.33 | Shield insertion to reduce coupling among interconnects: (a) Passive     |  |

|      | shielding where the shield lines are connected to power or ground. (b)   |  |

|      | Active shielding where the shield lines are driven with the same input   |  |

|      | signal to reduce the effective coupling capacitance                      |  |

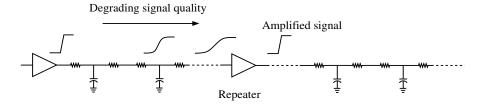

| 2.34 | Repeater insertion to reduce the interconnect delay by restoring the     |  |

|      | signal along a line.                                                     |  |

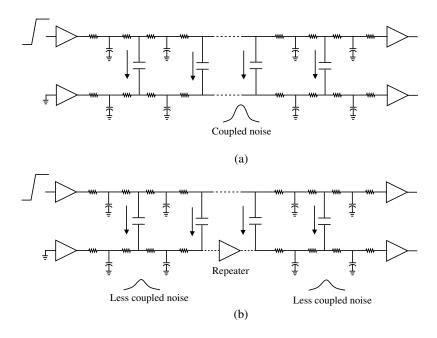

| 2.35 | Repeater insertion to reduce capacitive coupling noise: (a) No re-       |  |

|      | peaters exist. The total coupling capacitance is high. (b) The re-       |  |

|      | peater reduces the coupling capacitance by dividing the interconnect     |  |

|      | into multiple (two in this example) sections                             |  |

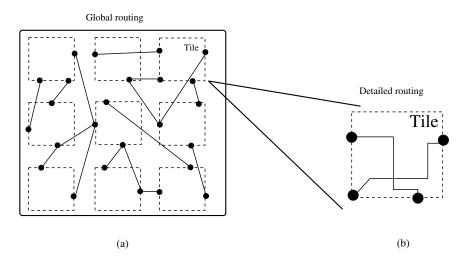

| 2.36 | Routing the interconnects in an integrated circuit: (a) Global routing.  |  |

|      | (b) Detailed routing                                                     |  |

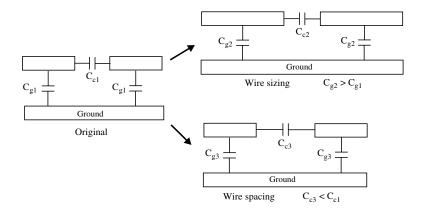

| 2.37 | Wire sizing and spacing to reduce coupling noise, respectively, by in-   |  |

|      | creasing the ground capacitance and decreasing the coupling              |  |

|      | capacitance                                                              |  |

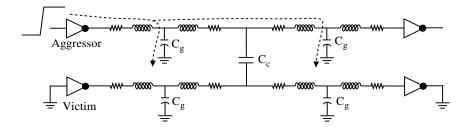

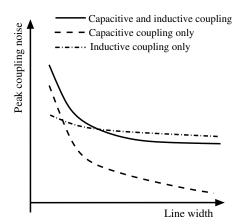

| 2.38 | An increase in the width of the aggressor line increases the ground      |  |

|      | capacitance. A higher ground capacitance behaves as a filter, reducing   |  |

|      | the coupling noise                                                       |  |

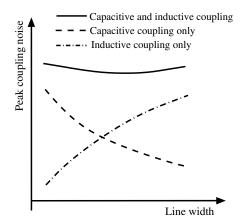

| 2.39 | The effect of line width on coupling noise in the presence of capacitive |  |

|      | and inductive coupling                                                   |  |

| 2.40 | The effect of spacing on coupling noise in the presence of capacitive    |  |

|      | and inductive coupling                                                   |  |

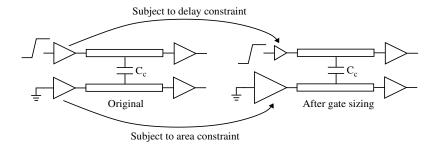

| 2.41 | Gate sizing to reduce coupling noise. The driver of the aggressor and    |  |

|      | victim are, respectively, downsized and upsized to reduce coupling       |  |

|      | noise                                                                    |  |

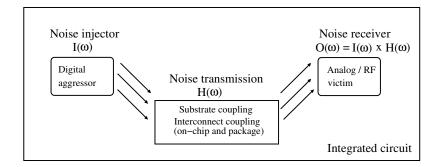

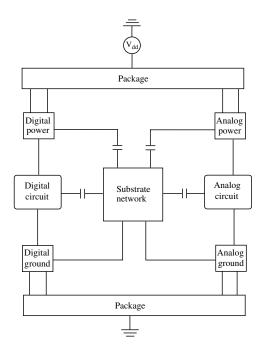

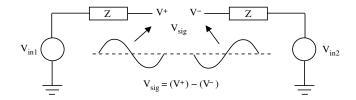

| 3.1  | Noise is generated by the aggressor digital circuit, transmitted through         |     |

|------|----------------------------------------------------------------------------------|-----|

|      | the substrate and interconnect at the circuit and package levels, and            |     |

|      | received by the analog/RF victim circuit                                         | 82  |

| 3.2  | Mixed-signal circuit where the noisy digital circuits coexist with the           |     |

|      | sensitive analog/RF circuits                                                     | 83  |

| 3.3  | Interactions among the digital, analog/RF circuits, and substrate in a           |     |

|      | mixed-signal environment with dedicated power/ground networks                    | 85  |

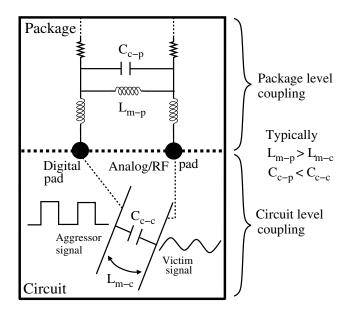

| 3.4  | Capacitive and inductive coupling at the circuit and package levels.             |     |

|      | The mutual inductance typically dominates at the package level while             |     |

|      | the coupling capacitance typically dominates at the circuit level                | 86  |

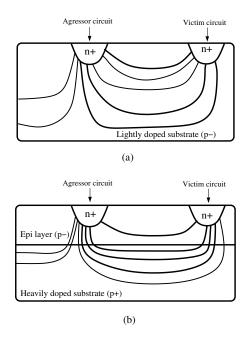

| 3.5  | Current flow within the substrate: (a) high resistivity bulk type sub-           |     |

|      | strate, (b) epi type substrate where a high resistivity epi layer is de-         |     |

|      | posited over a low resistivity substrate                                         | 88  |

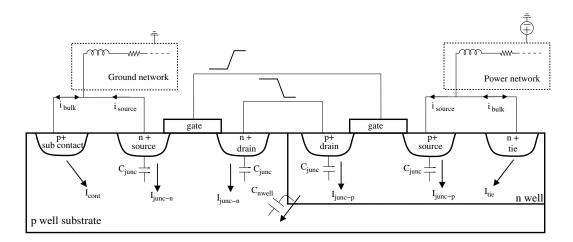

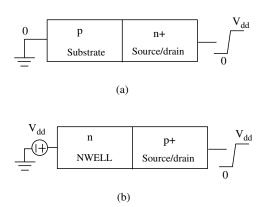

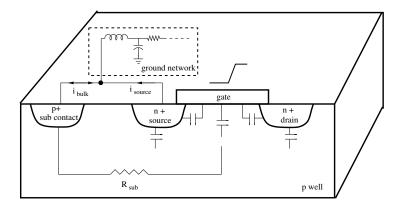

| 3.6  | Noise injection mechanisms into the substrate for a CMOS inverter.               |     |

|      | $I_{junc-n}$ and $I_{junc-p}$ represent the source/drain junction coupling for,  |     |

|      | respectively, the NMOS and PMOS transistors. $I_{cont}$ and $I_{tie}$ represent, |     |

|      | respectively, the current injected into the substrate from the substrate         |     |

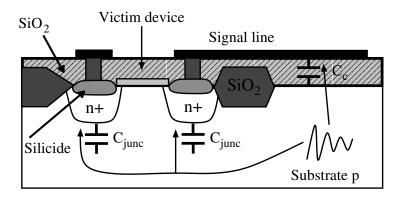

|      | contact on the ground network and N-well tie on the power network.               | 90  |

| 3.7  | Reverse biased pn junctions form a depletion capacitance, thereby in-            |     |

|      | jecting noise into the substrate and N-well: (a) NMOS transistor, (b)            |     |

|      | PMOS transistor                                                                  | 91  |

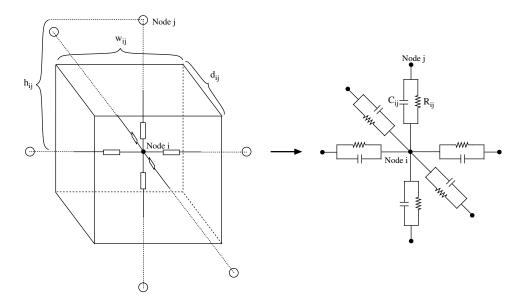

| 3.8  | Representation of the substrate as a collection of rectangular prisms to         |     |

|      | discretize (3.7). $\dots$                                                        | 95  |

| 3.9  | Discretization of each port on the substrate into panels in the boundary         |     |

|      | element method: (a) ports on the substrate and the resistances among             |     |

|      | the ports, (b) discretization of port 1 into four panels                         | 98  |

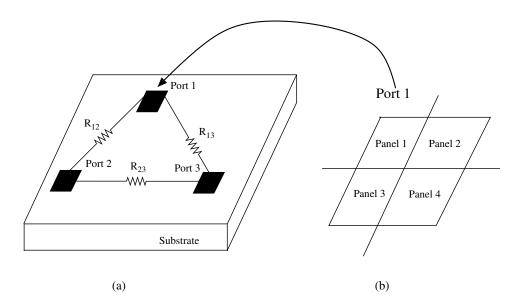

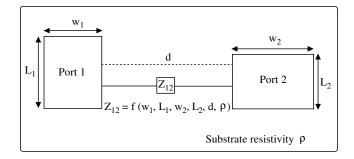

| 3.10 | Substrate impedance between two ports represented in a compact form              |     |

|      | as a function of technology and geometry related parameters                      | 100 |

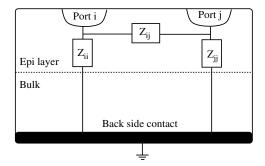

| 3.11 | Epi type substrate with a grounded backside contact. $Z_{ii}$ and $Z_{jj}$ are |     |

|------|--------------------------------------------------------------------------------|-----|

|      | the impedances between, respectively, port $i$ and the backside contact,       |     |

|      | and port $j$ and the back side contact. $Z_{ij}$ is the impedance between      |     |

|      | the ports                                                                      | 100 |

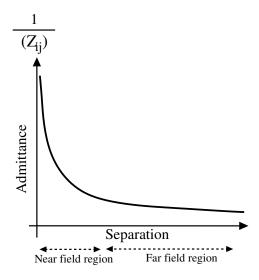

| 3.12 | Nonlinear variation of mutual substrate admittance $1/(Z_{ij})$ with re-       |     |

|      | spect to the separation between the ports                                      | 102 |

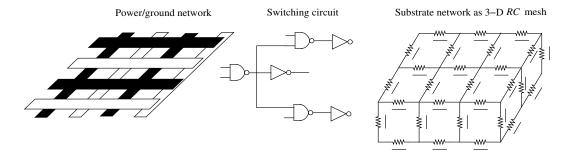

| 3.13 | Complexity requirements of substrate noise analysis in a large scale           |     |

|      | circuit. The power/ground networks, switching circuit, and substrate           |     |

|      | network have to be simultaneously considered                                   | 104 |

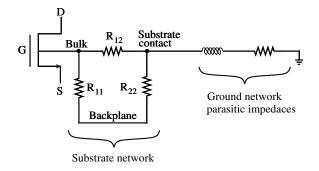

| 3.14 | Schematic level representation of the substrate impedances to analyze          |     |

|      | substrate noise                                                                | 104 |

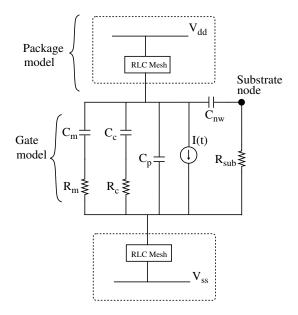

| 3.15 | Reduced model of a digital block to analyze substrate noise including          |     |

|      | the parasitic impedance of the package                                         | 106 |

| 3.16 | High level model to analyze substrate noise where a macromodel is              |     |

|      | generated for each standard cell                                               | 107 |

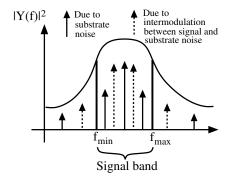

| 3.17 | Substrate noise capacitively coupling to the signal and power/ground           |     |

|      | lines and source/drain nodes of the victim transistor                          | 109 |

| 3.18 | Noise tones located in the frequency band of the signal degrade per-           |     |

|      | formance. Those noise tones located outside the band can be filtered           |     |

|      | using an appropriate filter                                                    | 111 |

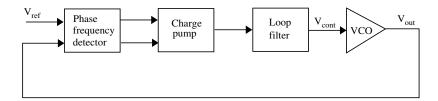

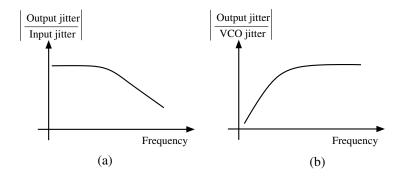

| 3.19 | Architecture of a charge pump PLL consisting of a phase frequency              |     |

|      | detector, charge pump, loop filter, and a voltage controlled oscillator        |     |

|      | (VCO)                                                                          | 112 |

| 3.20 | Jitter transfer function within a PLL: (a) PLL output to PLL input,            |     |

|      | (b) PLL output to VCO input                                                    | 113 |

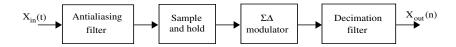

| 3.21 | Analog to digital converter with a $\Sigma\Delta$ modulator to enhance SNR     | 114 |

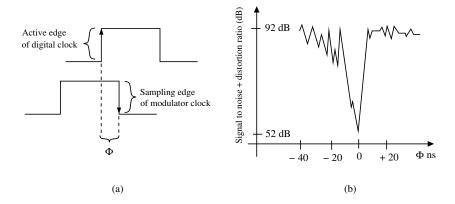

| 3.22 | Sensitivity of the SNDR to the time difference $\Phi$ between the active       |     |

|      | edge of the digital clock and the sampling edge of the modulator clock:        |     |

|      | (a) digital clock and sampling clock of the modulator, (b) variation of        |     |

|      | SNDR with respect to $\Phi$                                                    | 115 |

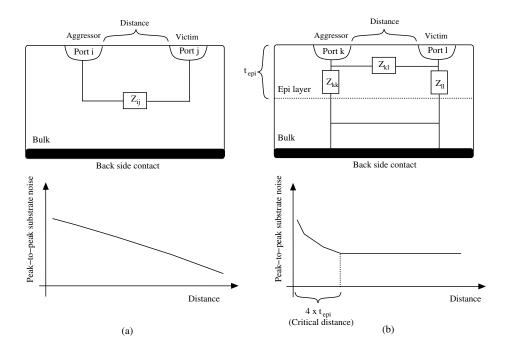

| 3.23 | The effect of physical separation on the substrate noise characteris-                                       |     |

|------|-------------------------------------------------------------------------------------------------------------|-----|

|      | tics: (a) for bulk type high resistivity substrates, (b) for epi type low                                   |     |

|      | resistivity substrates                                                                                      | 118 |

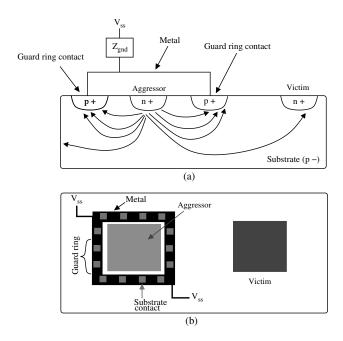

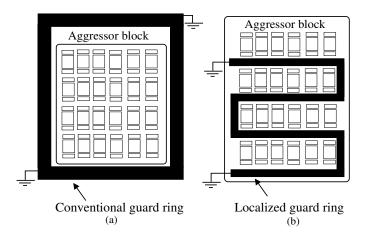

| 3.24 | The use of guard rings around an aggressor circuit to provide a low                                         |     |

|      | impedance path for the injected noise current within the substrate:                                         |     |

|      | (a) Cross-sectional view, (b) Top view                                                                      | 120 |

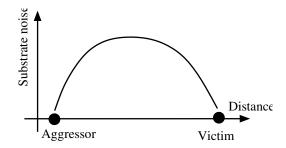

| 3.25 | Variation of the substrate noise as a function of the location of the                                       |     |

|      | guard ring                                                                                                  | 121 |

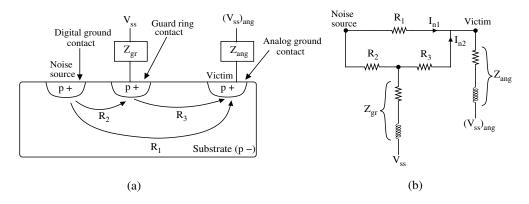

| 3.26 | Noise source, guard ring, and victim: (a) physical representation, (b)                                      |     |

|      | circuit representation                                                                                      | 122 |

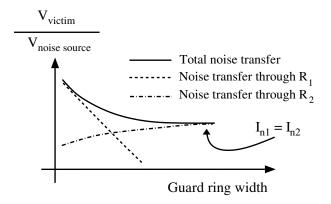

| 3.27 | Variation of noise transfer from aggressor to victim as a function of the                                   |     |

|      | guard ring width. $R_1$ , $R_2$ , $I_{n1}$ , and $I_{n2}$ are shown in Fig. 3.26                            | 123 |

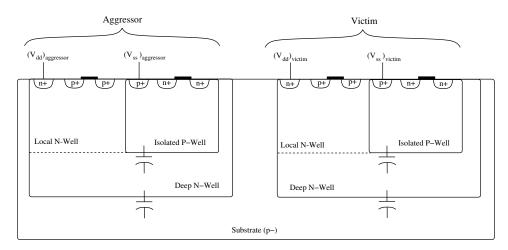

| 3.28 | Use of deep N-well to capacitively isolate NMOS transistors from the                                        |     |

|      | noisy substrate                                                                                             | 123 |

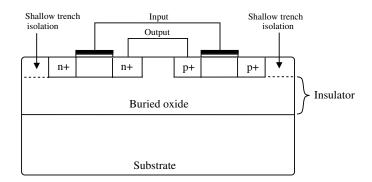

| 3.29 | Cross section of a CMOS inverter built on SOI technology                                                    | 125 |

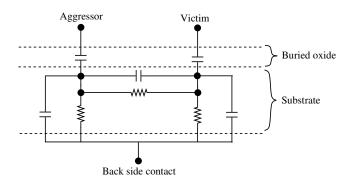

| 3.30 | Equivalent circuit illustrating substrate noise coupling in SOI                                             |     |

|      | $technology. \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                                                         | 126 |

| 3.31 | Differential signaling where the voltage refers to the difference between                                   |     |

|      | two out-of-phase signals rather than with reference to ground                                               | 127 |

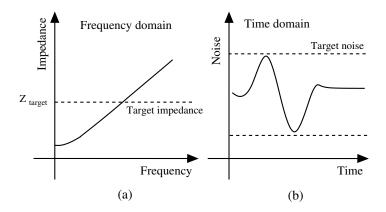

| 4.1  | Target impedance and noise: (a) target impedance is not satisfied in                                        |     |

|      | the frequency domain, (b) although the target noise is satisfied in the                                     |     |

|      | time domain.                                                                                                | 135 |

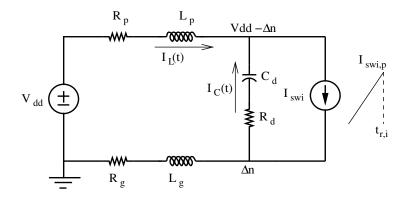

| 4.2  | Equivalent circuit model to estimate power supply noise and ground                                          |     |

|      | bounce. $R_p$ , $L_p$ , and $R_g$ , $L_g$ represent the power and ground impedances,                        |     |

|      | respectively. $C_d$ is the decoupling capacitor and $R_d$ is the effective se-                              |     |

|      | ries resistance of the capacitor. The load circuit is represented by a                                      |     |

|      | current source with a transition time $t_{r,i}$ and peak current $I_{swi,p}$                                | 137 |

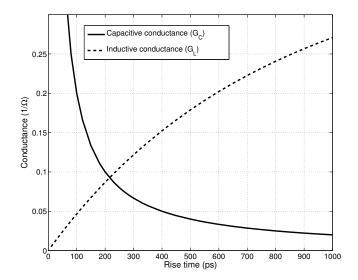

| 4.3  | Capacitive and inductive conductance as a function of rise time where                                       |     |

|      | $I_{swi,p} = 11.5 \text{ mA}, L_g = 1 \text{ nH}, C_d = 10 \text{ pF}, R_g = 2.2 \Omega, R_d = 0.1 \Omega,$ |     |

|      | and $t = t_{r,v}$                                                                                           | 141 |

|      |                                                                                                             |     |

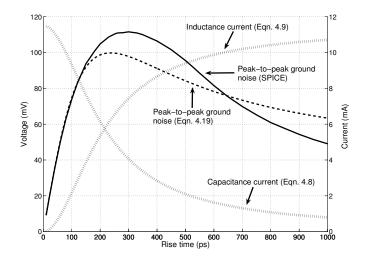

| 4.4 | Comparison of peak-to-peak ground noise as a function of the transition                                                          |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------|-----|

|     | time obtained from SPICE simulations and equation (4.19) for $I_{swi,p} =$                                                       |     |

|     | 11.5 mA. The ground network impedances are $L_g=1$ nH, $C_d=10$ pF,                                                              |     |

|     | $R_g = 2.2 \Omega$ , and $R_d = 0.1 \Omega$ . The dotted lines depict the estimated                                              |     |

|     | capacitive and inductive currents as a function of transition time                                                               | 145 |

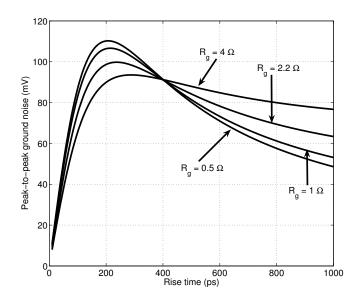

| 4.5 | Peak-to-peak ground noise for different values of $R_g$ when $I_{swi,p} = 11.5$                                                  |     |

|     | mA, $L_g = 1$ nH, $C_d = 10$ pF, and $R_d = 0.1 \Omega \dots \dots \dots$                                                        | 149 |

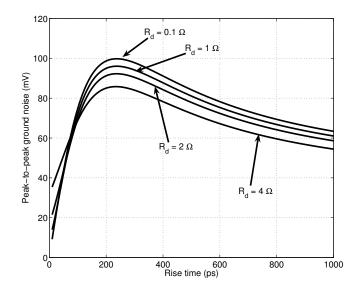

| 4.6 | Peak-to-peak ground noise for different values of $R_d$ when $I_{swi,p} = 11.5$                                                  |     |

|     | mA, $L_g = 1$ nH, $C_d = 10$ pF, and $R_g = 2.2 \Omega \dots \dots \dots$                                                        | 149 |

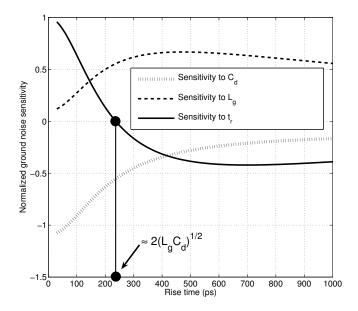

| 4.7 | Normalized sensitivity of the ground noise as a function of transition                                                           |     |

|     | time when $I_{swi,p}=11.5$ mA, $L_g=1$ nH, $C_d=10$ pF, $R_g=2.2$ $\Omega$ , and                                                 |     |

|     | $R_d = 0.1 \ \Omega \dots \dots$ | 151 |

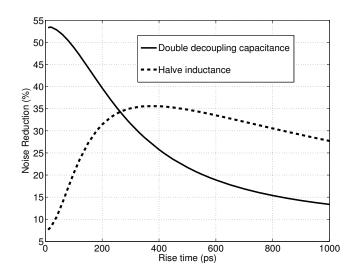

| 4.8 | Comparison of the noise reduction obtained by doubling the decoupling                                                            |     |

|     | capacitance and halving the inductance                                                                                           | 152 |

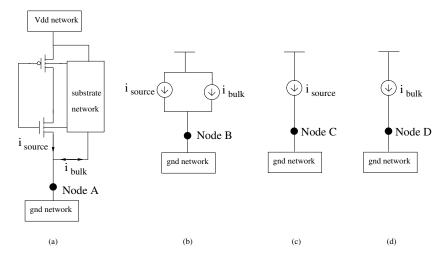

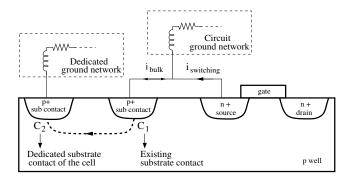

| 5.1 | Interaction of the substrate and on-chip ground distribution network                                                             |     |

|     | within an NMOS transistor. The current flowing through the ground                                                                |     |

|     | network is the summation of the source and bulk currents                                                                         | 156 |

| 5.2 | A bulk-type substrate model of a CMOS structure                                                                                  | 159 |

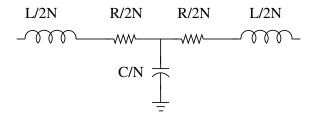

| 5.3 | One stage of a distributed $RLC$ interconnect model for an on-chip                                                               |     |

|     | ground distribution network                                                                                                      | 160 |

| 5.4 | Illustration of the superposition technique to analyze the effect of the                                                         |     |

|     | substrate on the on-chip ground noise. The overall ground noise is                                                               |     |

|     | modeled as a superposition of two noise voltages: source related ground                                                          |     |

|     | noise and bulk related ground noise: (a) The CMOS inverter includ-                                                               |     |

|     | ing the substrate network and the ground distribution network used to                                                            |     |

|     | analyze the total ground noise, (b) summation of the PWL approxi-                                                                |     |

|     | mation of the source current and bulk current which flows through the                                                            |     |

|     | same ground network, (c) PWL approximation of the source current to                                                              |     |

|     | estimate the source related ground noise, and (d) PWL approximation                                                              |     |

|     | of the bulk current to estimate the bulk related ground noise                                                                    | 160 |

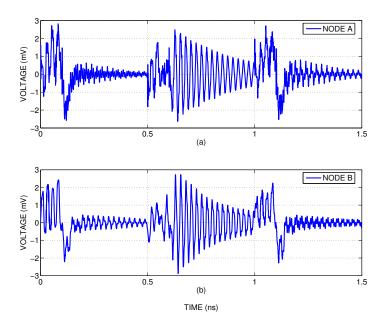

| 5.5 | Comparison of the voltage at Nodes A and B (see Fig. 5.4) illustrating                                                |     |

|-----|-----------------------------------------------------------------------------------------------------------------------|-----|

|     | the accuracy of the current estimations. The maximum error for the                                                    |     |

|     | peak voltage is less than 10% within one period                                                                       | 162 |

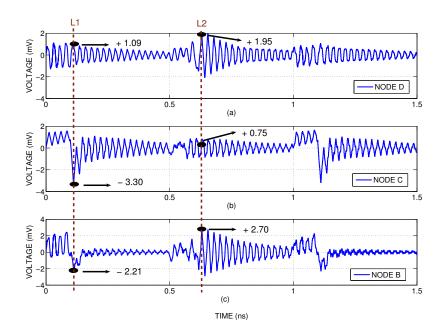

| 5.6 | Comparison of the voltage at Nodes B, C and D (see Fig. 5.4). Nodes B,                                                |     |

|     | C, and D illustrate, respectively, the total ground noise, source related                                             |     |

|     | ground noise, and bulk related ground noise                                                                           | 163 |

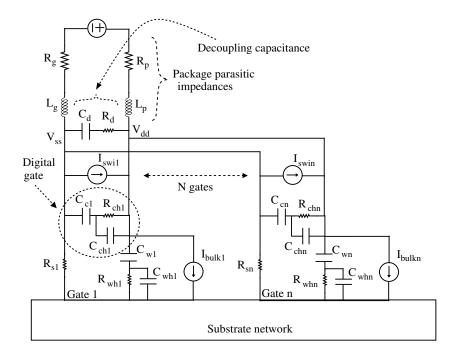

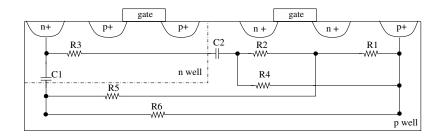

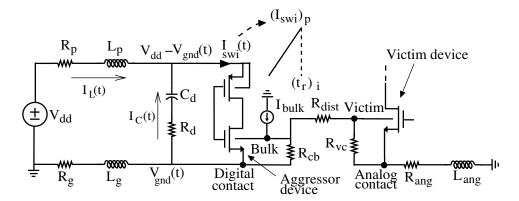

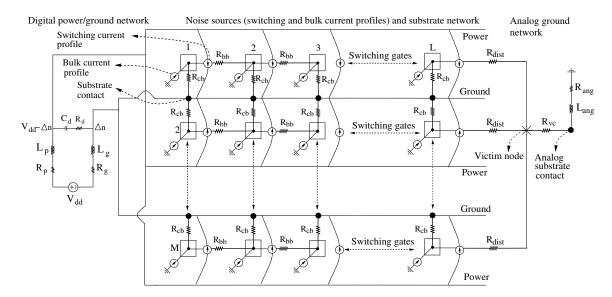

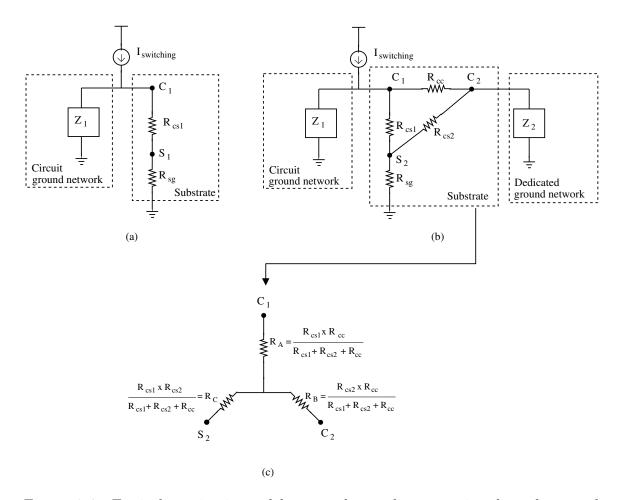

| 6.1 | Equivalent model to estimate two types of substrate coupling mecha-                                                   |     |

|     | nisms for a single switching gate: (1) ground coupling and (2) source                                                 |     |

|     | and drain junction coupling                                                                                           | 172 |

| 6.2 | Equivalent circuit model to estimate substrate noise for multiple switch-                                             |     |

|     | ing gates                                                                                                             | 174 |

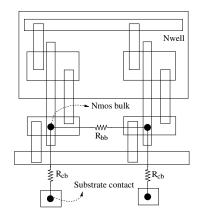

| 6.3 | Layout of two inverters to extract $R_{bb}$ and $R_{cb}$                                                              | 175 |

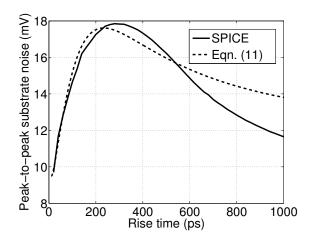

| 6.4 | Comparison of peak-to-peak substrate noise as a function of the rise                                                  |     |

|     | time obtained from SPICE simulations and $(6.4)$                                                                      | 177 |

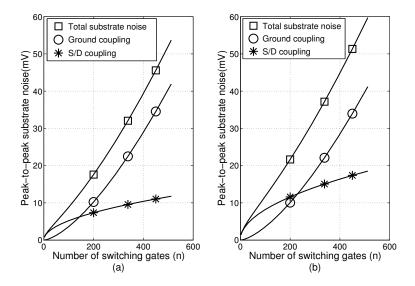

| 6.5 | Number of simultaneously switching gates vs. substrate noise as pre-                                                  |     |

|     | dicted by (6.4) when $(t_r)_i = 250 \text{ ps}$ , $L_g = 1 \text{ nH}$ , $C_d = 10 \text{ pF}$ , $R_g = 2.2$          |     |

|     | $\Omega, R_d = 0.1 \ \Omega, R_{bb} = 16.8 \ k\Omega, R_{cb} = 10.7 \ k\Omega, R_{dist} = 40 \ k\Omega, R_{sc} = 660$ |     |

|     | $\Omega$ , $R_{ang}=2.2~\Omega$ , and $L_{ang}=1$ nH. (a) Each gate has a substrate con-                              |     |

|     | tact, (b) two gates share one substrate contact                                                                       | 179 |

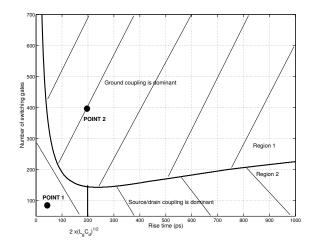

| 6.6 | For each rise time, the number of switching gates for which source/drain                                              |     |

|     | coupling is equal to ground coupling is determined from (6.4). Regions                                                |     |

|     | $1\ \mathrm{and}\ 2$ represent, respectively, the area where ground and source/drain                                  |     |

|     | coupling is dominant. The operating parameters are $L_g=1$ nH,                                                        |     |

|     | $C_d = 10 \text{ pF}, R_g = 2.2 \Omega, R_d = 0.1 \Omega, R_{bb} = 16.8 \text{ k}\Omega, R_{cb} = 10.7$               |     |

|     | k $\Omega$ , $R_{dist}=40$ k $\Omega$ , $R_{sc}=660$ $\Omega$ , $R_{ang}=2.2$ $\Omega$ , and $L_{ang}=1$ nH           | 181 |

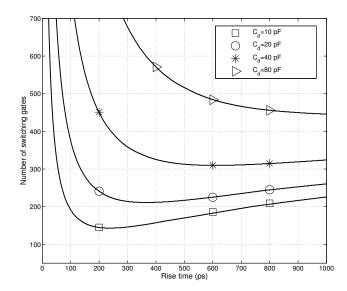

| 6.7 | Effect of decoupling capacitance on the dominant noise coupling mech-                                                 |     |

|     | anism. In this figure, the data shown in Fig. 6.6 are obtained for dif-                                               |     |

|     | ferent decoupling capacitances while the other circuit parameters are                                                 |     |

|     | maintained the same                                                                                                   | 182 |

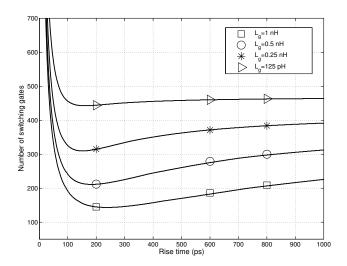

| 6.8  | Effect of parasitic inductance on the dominant noise coupling mech-                                                            |     |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

|      | anism. In this figure, the data shown in Fig. 6.6 are obtained for                                                             |     |

|      | different parasitic inductances while the other circuit parameters are                                                         |     |

|      | maintained the same                                                                                                            | 183 |

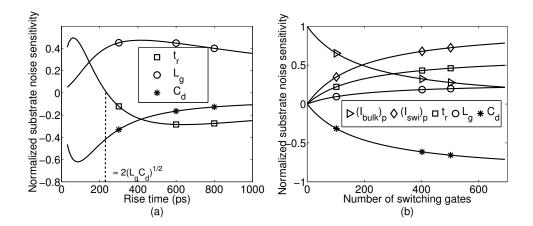

| 6.9  | Substrate noise sensitivity when $L_g = 1$ nH, $C_d = 10$ pF, $R_g = 2.2 \Omega$ ,                                             |     |

|      | $R_d = 0.1 \ \Omega, \ R_{cb} = 10.7 \ k\Omega, \ R_{dist} = 40 \ k\Omega, \ R_{vc} = 660 \ \Omega, \ R_{ang} = 2.2 \ \Omega,$ |     |

|      | and $L_{ang} = 1$ nH, (a) As a function of rise time when $n = 400$ , (b) As                                                   |     |

|      | a function of the number of switching gates when $t_r = 100$ ps                                                                | 185 |

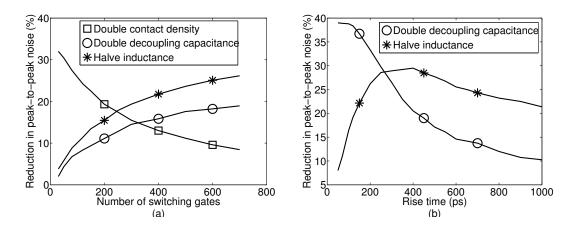

| 6.10 | Comparison of noise reduction techniques when $L_g = 1$ nH, $C_d = 10$                                                         |     |

|      | pF, $R_g=2.2~\Omega,~R_d=0.1~\Omega,~R_{ang}=2.2~\Omega,~{\rm and}~L_{ang}=1~{\rm nH}$ : (a) As                                |     |

|      | a function of the number of switching gates at $t_r = 400$ ps. (b) As a                                                        |     |

|      | function of the rise time when $n = 700$                                                                                       | 188 |

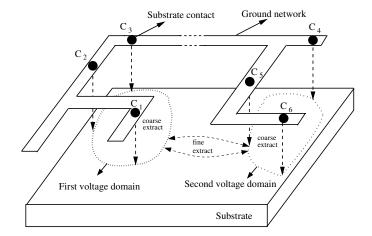

| 7.1  | Identifying the voltage domains within the substrate. Assuming $V_{C1} \approx$                                                |     |

| •••  | $V_{C2} \approx V_{C3}$ and $V_{C4} \approx V_{C5} \approx V_{C6}$ , two voltage domains are created                           |     |

|      | by the first and last three contacts. A coarse extraction is performed                                                         |     |

|      | within each domain to reduce the computational complexity, followed                                                            |     |

|      | by a fine extraction of those domains where the dominant current flow                                                          |     |

|      | occurs                                                                                                                         | 194 |

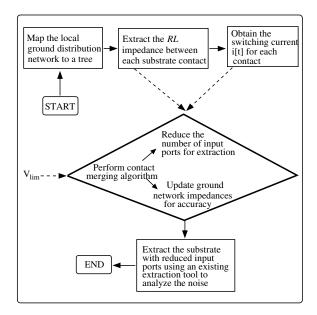

| 7.2  | Flowchart summarizing the proposed methodology to analyze substrate                                                            |     |

|      | noise in a large scale mixed-signal circuit                                                                                    | 195 |

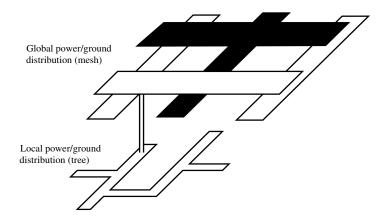

| 7.3  | In a typical power/ground distribution network, upper metal layers                                                             |     |

|      | span the entire die, forming a global mesh. The power/ground net-                                                              |     |

|      | work is distributed to the devices in each macroblock through the local                                                        |     |

|      | distribution network, represented as a tree                                                                                    | 196 |

| 7.4  | The current injected into each substrate contact by the switching cir-                                                         |     |

|      | cuit is characterized over a specific time window. The current in-                                                             |     |

|      | jected by those cells located between two contacts is shifted to the                                                           |     |

|      | previous contact such that $i_{c1}[t] = i_1[t] + i_2[t], i_{c2}[t] = i_3[t] + i_4[t],$                                         |     |

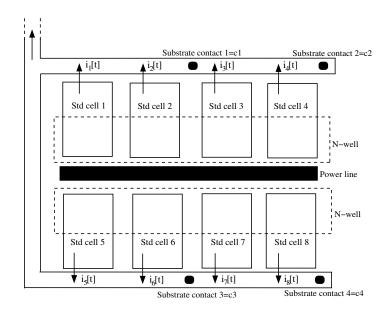

|      | $i_{c3}[t] = i_5[t] + i_6[t]$ , and $i_{c4}[t] = i_7[t] + i_8[t]$                                                              | 197 |

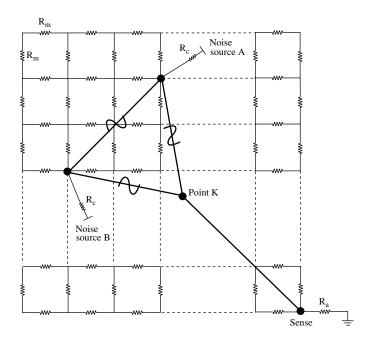

| 7.5  | Two substrate contacts A and B acting as noise sources, where the                   |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | substrate is represented as a 2-D resistive mesh                                    | 200 |

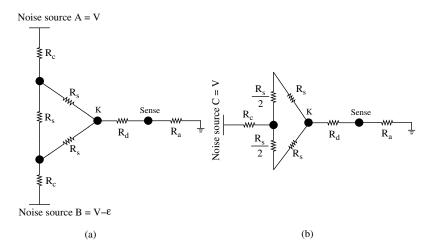

| 7.6  | Equivalent circuit to analyze the impact of two noise sources with                  |     |

|      | similar noise voltages on the substrate: (a) Before merging. (b) After              |     |

|      | merging                                                                             | 200 |

| 7.7  | First metal layer of the digital ground network mapped to a tree where              |     |

|      | each node represents a substrate contact and the root is assumed to be              |     |

|      | the ideal ground where the local tree is connected to the global mesh:              |     |

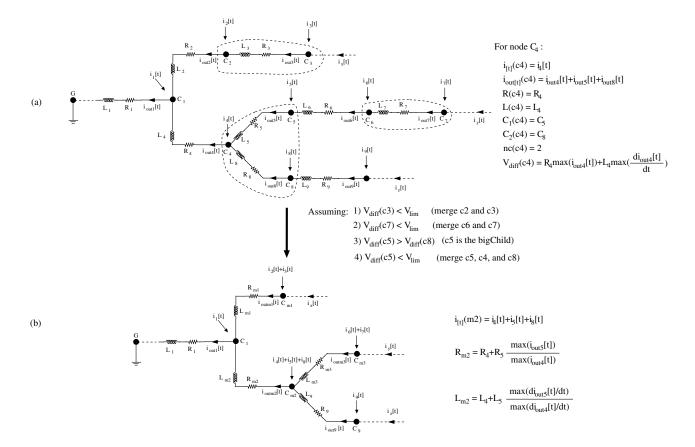

|      | (a) Before merging. All seven elements are illustrated for node $C_4$ , (b)         |     |

|      | After merging. Note that $i_{[t]}(node)$ , $R(node)$ , and $L(node)$ are updated    |     |

|      | as shown for node $C_{m2}$ to maintain the voltage on the node with the             |     |

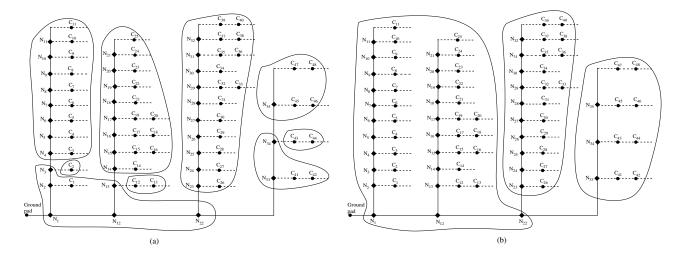

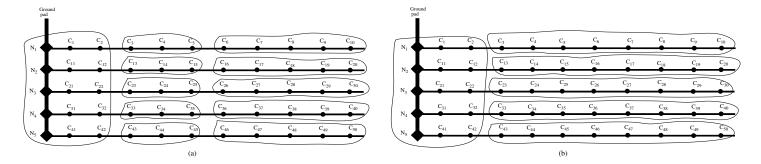

|      | least error                                                                         | 205 |

| 7.8  | Pseudo-code to merge the substrate contacts on the ground network                   |     |

|      | based on spatial transient voltage differences                                      | 207 |

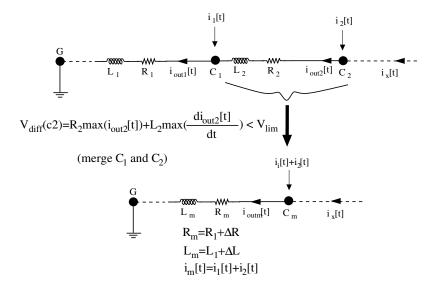

| 7.9  | Illustration of impedance updated after merging two nodes. The resis-               |     |

|      | tance and inductance are incremented, respectively, by $\Delta R$ and $\Delta L$ to |     |

|      | maintain the original voltage with the least error                                  | 208 |

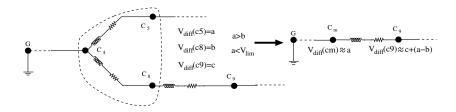

| 7.10 | Illustration of the $Correct$ function. After the nodes $C_4$ , $C_5$ , and $C_8$   |     |

|      | are merged based on $V_{diff}(c5)$ , $V_{diff}(c9)$ shifts by $(a-b)$ which is      |     |

|      | compensated by the $Correct$ function                                               | 210 |

| 7.11 | Pseudo-code of the $Correct$ function to prevent error accumulation                 |     |

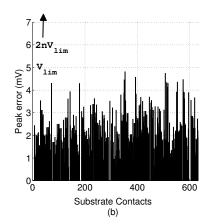

|      | after merging a set of contacts                                                     | 211 |

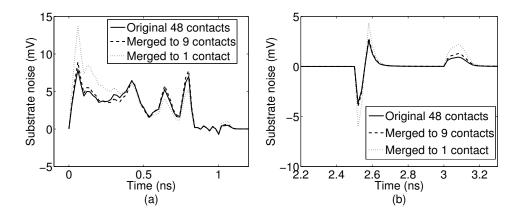

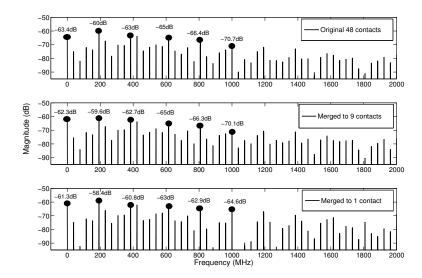

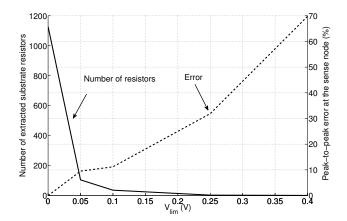

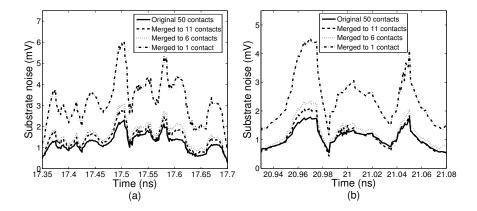

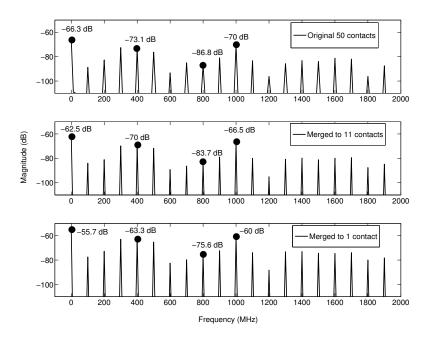

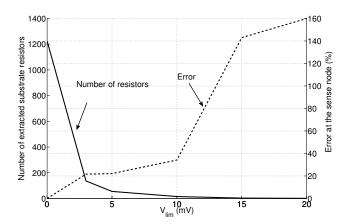

| 7.12 | Maximum error in the voltage of each contact due to merging: (a)                    |     |

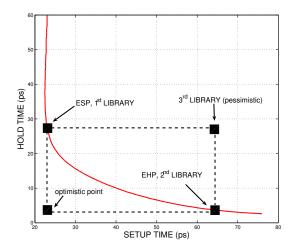

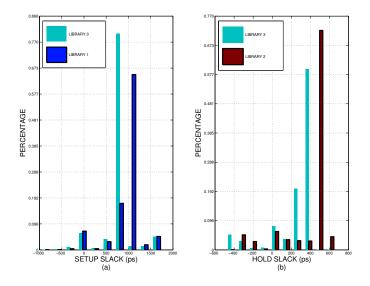

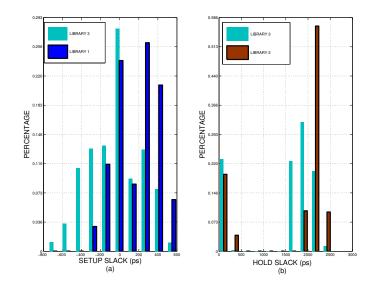

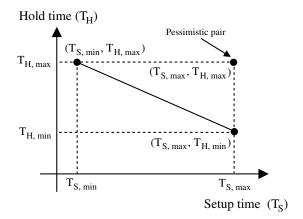

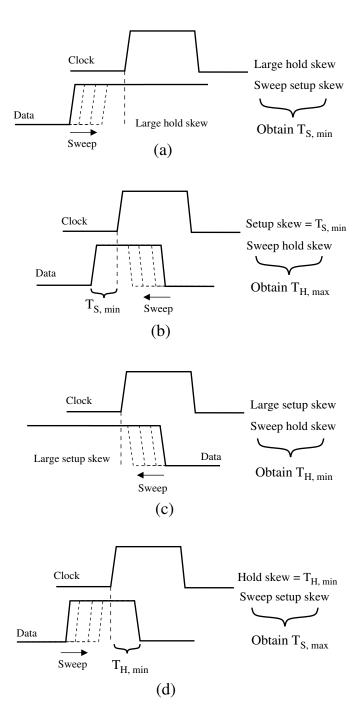

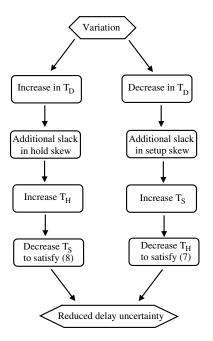

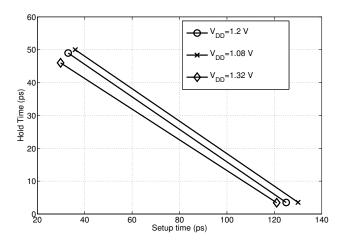

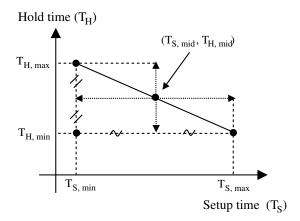

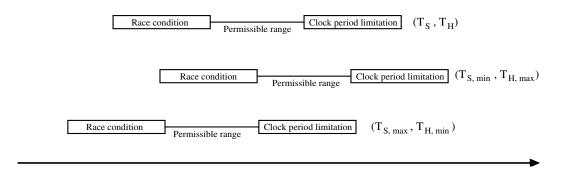

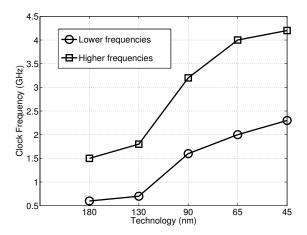

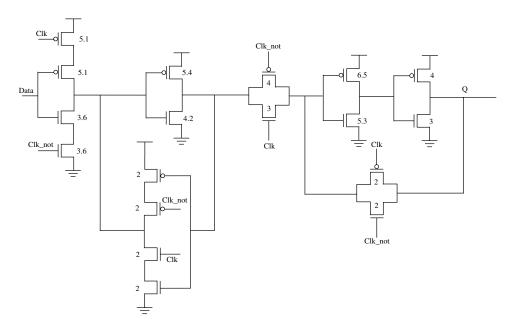

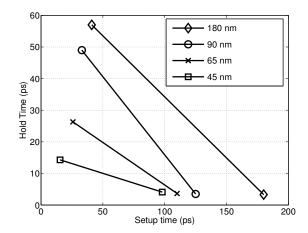

|      | Ground network is composed of a single line with 60 substrate contacts,             |     |