### Design and Modeling of High Speed Global On-Chip Interconnects

by

Guoqing Chen

Submitted in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Supervised by Professor Eby G. Friedman

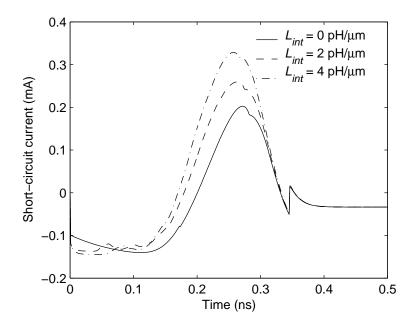

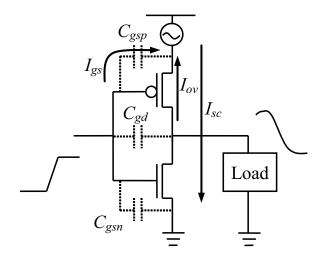

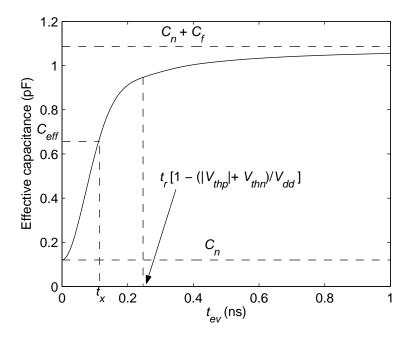

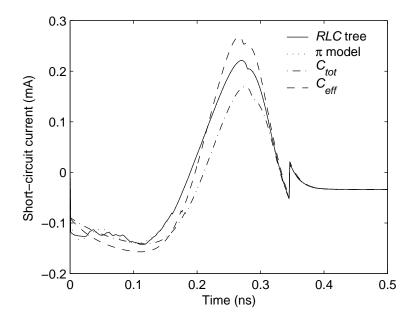

Department of Electrical and Computer Engineering

The College

School of Engineering and Applied Sciences

University of Rochester Rochester, New York

2007

# Dedication

This work is dedicated to my parents, Mr. Xiusheng Chen and Mrs. Yalan Zhang, my wife Ning, and my daughter Ariana.

#### Curriculum Vitae

Guoqing Chen was born in Beijing, China in 1975. He received the B.S. (with honors) and M.S degrees in electronic engineering from Tsinghua University, Beijing, China, in 1998 and 2001, respectively. In 2002, he received his second M.S. degree in electrical engineering from University of Rochester, Rochester, NY. He is currently a Ph.D. candidate in the area of high performance VLSI/IC design at the University of Rochester.

In the summers of 2004 and 2005, he was with Manhattan Routing, Inc., New York City, NY, where his work was focused on the development of an EDA tool for the timing closure procedure in the IC design process. His research interests include high speed interconnect design and modeling, signal integrity, and low power circuit design.

### Acknowledgments

The time I spent at the University of Rochester is definitely one of the most important and cherishable periods in my life. During these years of studies, I received invaluable support and encouragement from my colleagues, friends, and family, for whom I would like to make grateful acknowledgments.

First of all, I would like to express my deep appreciation to my academic advisor, Professor Eby G. Friedman, for his kind and patient mentorship on my academic and personal growth. His vast knowledge and nice personality made my research work successful and highly enjoyable. It is my great pleasure to perform the Ph.D. studies under his supervision.

I thank Professors Mitsunori Ogihara, Philippe M. Fauchet, David H. Albonesi, and Daniel Stefankovic for their service on my committee and valuable suggestions for this dissertation. Special thanks to Professors Philippe M. Fauchet, David H. Albonesi, and other members in the Nanoscale Interdisciplinary Research Team, Mikhail Haurylau, Hui Chen, Nicholas A. Nelson, and Jidong Zhang for their collaborations

and support in the on-chip optical interconnect project. I'm grateful to Tor Ekenberg and Erhan Ergin for providing me the opportunity of summer internship in Manhattan Routing, Inc., where I obtained real industrial experience and enjoyed the colorful life in New York City.

I would like to thank those previous and current members in the High Performance VLSI/IC Design and Analysis Lab, Andrey Mezhiba, Dimitris Velenis, Volkan Kursun, Boris Andreev, Weize Xu, Magdy El-Moursy, Junmou Zhang, Mikhail Popovich, Vasilis Pavlidis, Jonathan Rosenfeld, Emre Salman, Renatas Jakushokas, and Ioannis Savidis, for their help and accompanyship. I would also like to thank RuthAnn Williams for her support in preparing all the paperwork in these years.

Finally, I would like to express my great gratitude to my wife Ning and my daughter Ariana for their support to my work and the happiness they bring to my life. This gratitude is also extended to my family, friends, and relatives in China for their understanding and encouragement which accompanies me through my life.

This work is supported in part by the Semiconductor Research Corporation under Contract No. 2003-TJ-1068 and 2004-TJ-1207, the National Science Foundation under Contract Nos. CCR-0304574 and CCF-0541206, grants from the New York State Office of Science, Technology & Academic Research to the Center for Advanced Technology in Electronic Imaging Systems, and by grants from Intel Corporation, Eastman Kodak Company, Manhattan Routing, and Intrinsix Corporation.

#### Abstract

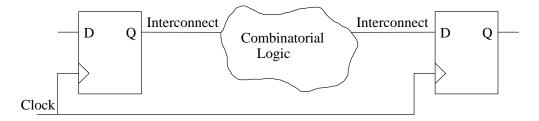

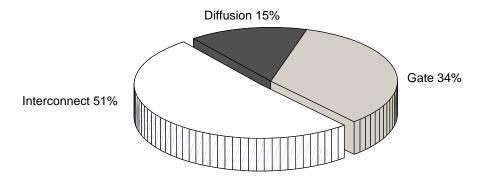

Interconnect has become a dominant factor in deep submicrometer (DSM) integrated circuits (ICs). With increasing levels of on-chip integration, more functional units are integrated onto a single die, such as a multi-core microprocessor and a system-on-chip. Global interconnect, which acts as a communication media among these functional units, plays an increasingly important role and can significantly limit the performance of advanced systems.

With decreasing on-chip clock periods, the timing characteristics of on-chip signals need to be determined and controlled more precisely. Accurate interconnect models are therefore critical to the IC design process. In this dissertation, two global interconnect models are presented. Closed-form expressions of the signal waveform are developed, which achieve good agreement with Spectre simulations.

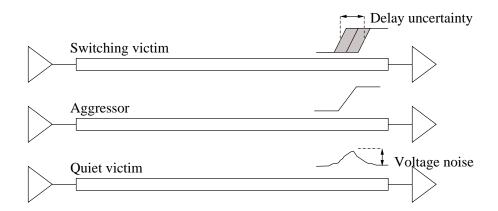

During the interconnect design process, multiple design criteria are considered, such as delay, power, bandwidth, and noise. Repeaters are widely used in digital ICs to reduce interconnect delay and signal transition time with the penalty of additional

power and area. A repeater insertion methodology is presented for achieving a tradeoff among different design criteria. Closed-form expressions for the number and size of the power optimal repeaters are developed.

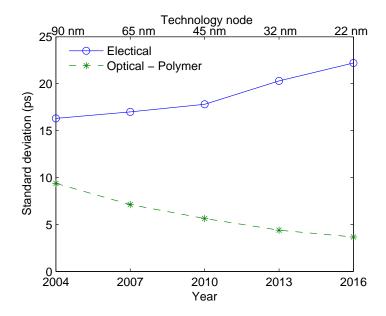

With the scaling of CMOS technology, the requirements of different design criteria have become more stringent. It is increasingly difficult for conventional copper interconnect to satisfy these requirements. On-chip optical interconnect is shown to be a promising substitute for electrical interconnect in future advanced architectures. Critical lengths at which optical interconnect becomes advantageous are shown to be approximately one tenth of the chip edge length at the 22 nm technology node.

The focus of the IC design process in the DSM regime has shifted from logic optimization to interconnect optimization. The research presented in this dissertation provides several interconnect design and modeling methods to support this interconnect-centric design strategy.

# Contents

| Dedication     |                        |                     |                         |     |  |  |

|----------------|------------------------|---------------------|-------------------------|-----|--|--|

| $\mathbf{C}_1$ | Curriculum Vitae       |                     |                         |     |  |  |

| $\mathbf{A}$   | ckno                   | wledgr              | m nents                 | iv  |  |  |

| $\mathbf{A}$   | bstra                  | $\operatorname{ct}$ |                         | vi  |  |  |

| Li             | $\operatorname{st}$ of | Table               | ${f s}$                 | xii |  |  |

| Li             | st of                  | Figur               | es                      | хv  |  |  |

| 1              | Intr                   | oduct               | ion                     | 1   |  |  |

| <b>2</b>       | On-                    | Chip 1              | Electrical Interconnect | 9   |  |  |

|                | 2.1                    | Design              | n Flows for DSM ASICs   | 10  |  |  |

|                | 2.2                    | Interc              | onnect Design Criteria  | 12  |  |  |

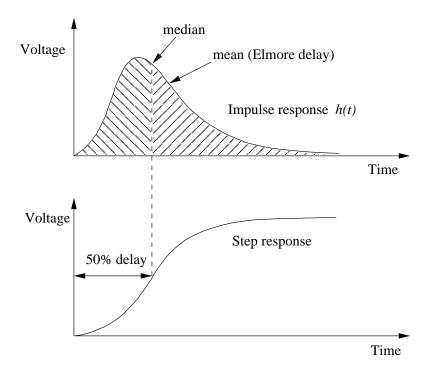

|                |                        | 2.2.1               | Delay                   | 13  |  |  |

|                |                        | 2.2.2               | Power Dissipation       | 14  |  |  |

|                |                        | 2.2.3               | Noise                   | 15  |  |  |

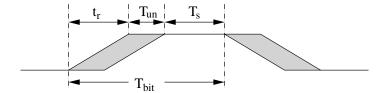

|                |                        | 2.2.4               | Bandwidth               | 16  |  |  |

|                |                        | 2.2.5               | Physical Area           | 18  |  |  |

|                | 2.3                    | Interc              | onnect Characteristics  | 18  |  |  |

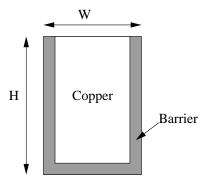

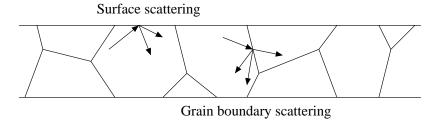

|                |                        | 2.3.1               | Resistance              | 19  |  |  |

|                |                        | 2.3.2               | Capacitance             | 24  |  |  |

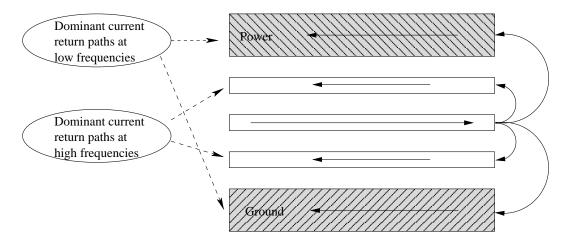

|   |          | 2.3.3   | Inductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26 |

|---|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 2.4      | Interco | onnect Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30 |

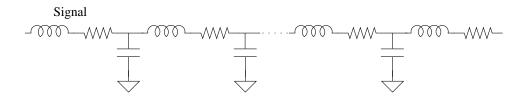

|   |          | 2.4.1   | Single Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30 |

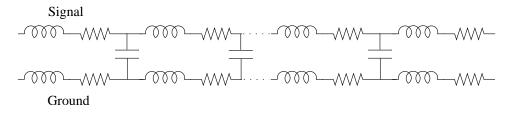

|   |          | 2.4.2   | Parallel Coupled Interconnects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39 |

|   |          | 2.4.3   | Model Order Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42 |

|   | 2.5      | Design  | Methodologies for Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46 |

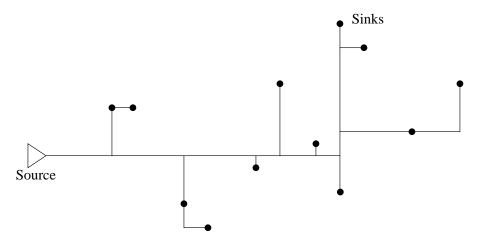

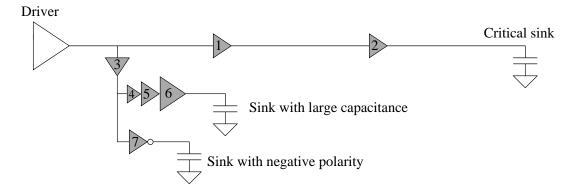

|   |          | 2.5.1   | Constructing an Interconnect Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47 |

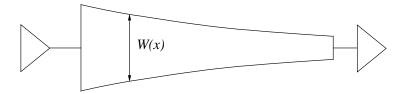

|   |          | 2.5.2   | Wire Sizing, Shaping, and Spacing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48 |

|   |          | 2.5.3   | Repeater Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50 |

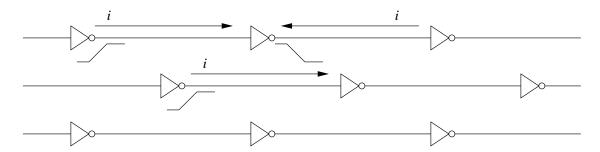

|   |          | 2.5.4   | Shielding Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53 |

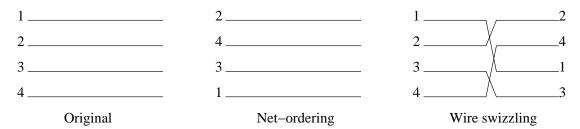

|   |          | 2.5.5   | Net-Ordering and Wire Swizzling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53 |

|   | 2.6      | Conclu  | asions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55 |

| n | <b>A</b> | DICT    | water and the second of the se | ۲. |

| 3 |          |         | nterconnect Model Based on Fourier Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56 |

|   | 3.1      |         | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56 |

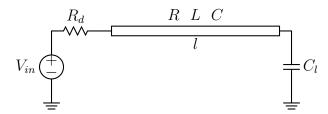

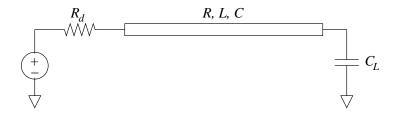

|   | 3.2      | _       | Interconnect Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58 |

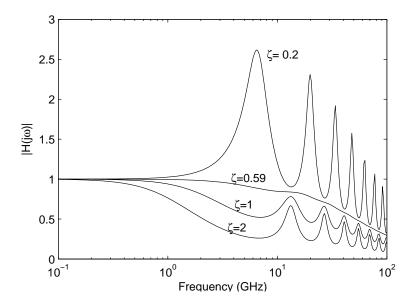

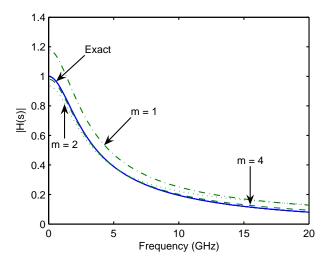

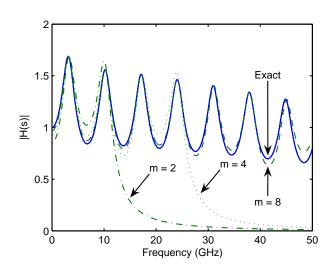

|   |          | 3.2.1   | Interconnect Transfer Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59 |

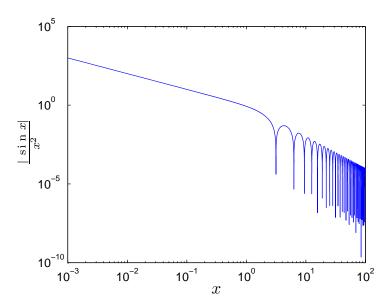

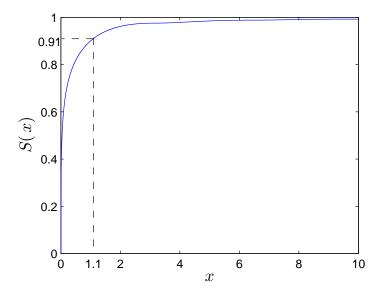

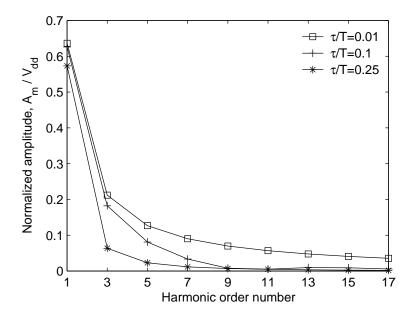

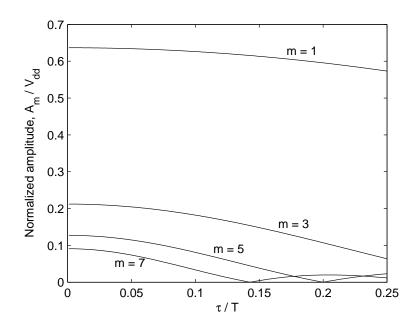

|   |          | 3.2.2   | Fourier Series Representation of Input Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62 |

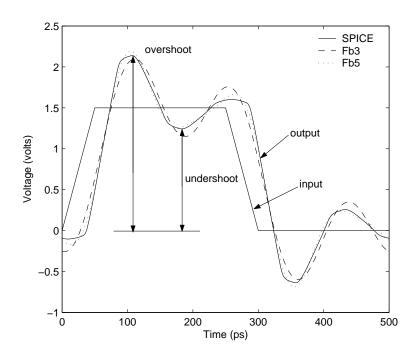

|   |          | 3.2.3   | Far End Time Domain Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64 |

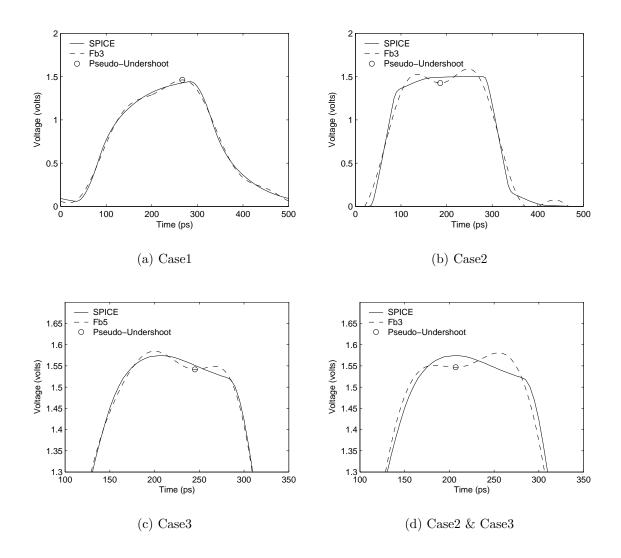

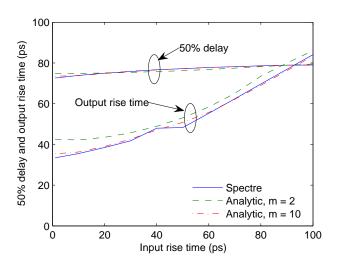

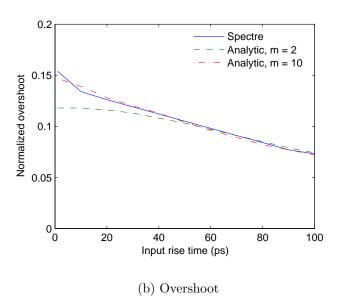

|   |          | 3.2.4   | The 50% Delay and Overshoots/Undershoots $\dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66 |

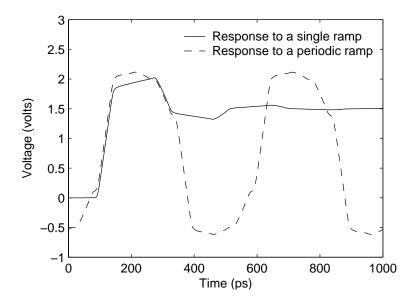

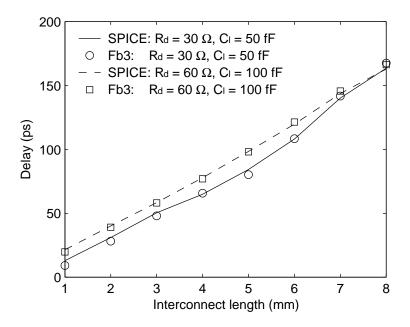

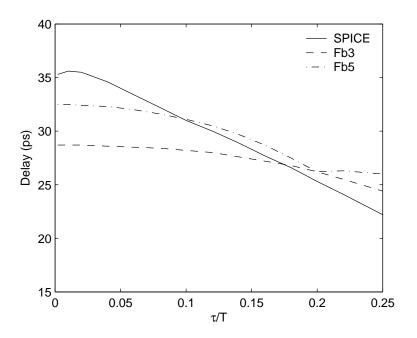

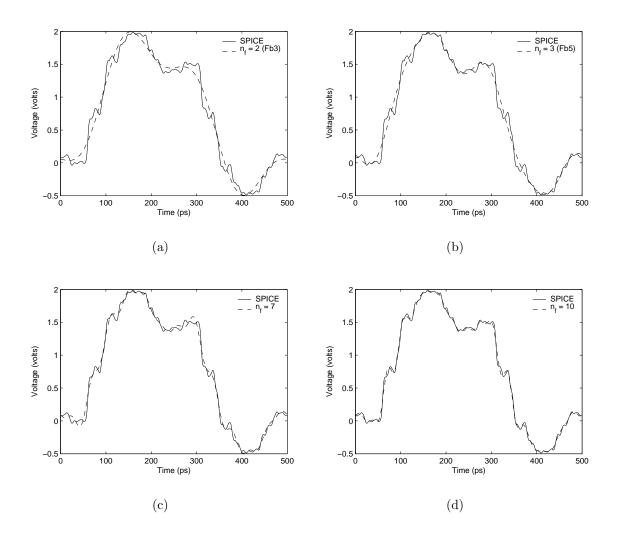

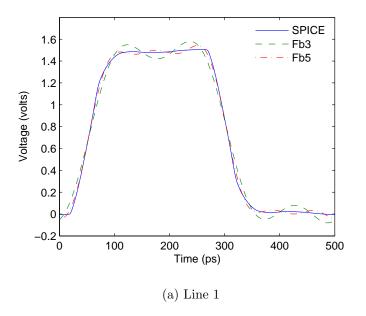

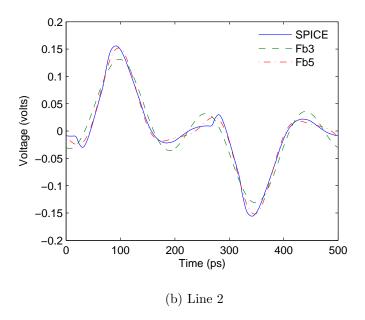

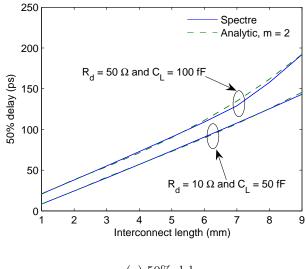

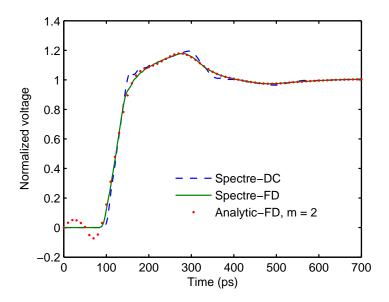

|   |          | 3.2.5   | Model Verification and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71 |

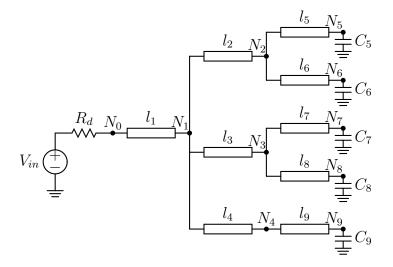

|   | 3.3      | Distrib | outed RLC Trees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79 |

|   |          | 3.3.1   | Transfer Function of Distributed $RLC$ Trees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79 |

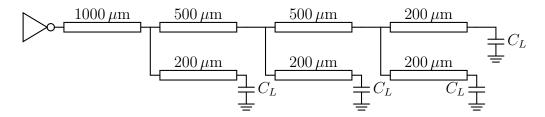

|   |          | 3.3.2   | Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81 |

|   | 3.4      | Multip  | ble Coupled Interconnect Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87 |

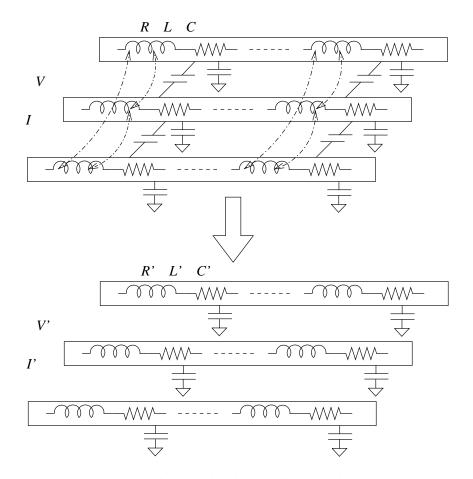

|   |          | 3.4.1   | Decoupling Multiconductor Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88 |

|   |          | 3.4.2   | Far End Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91 |

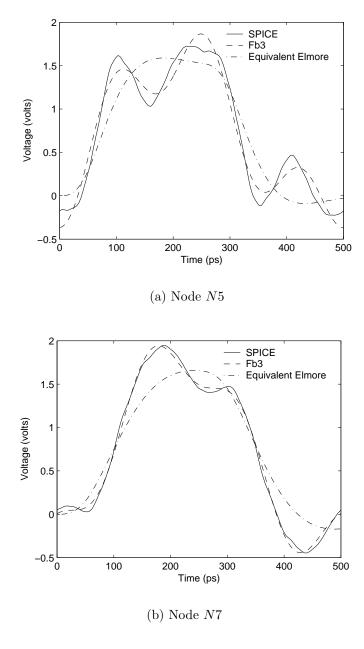

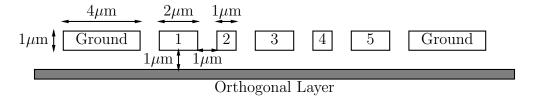

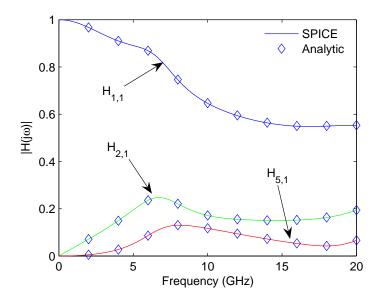

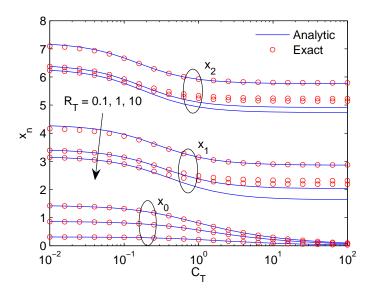

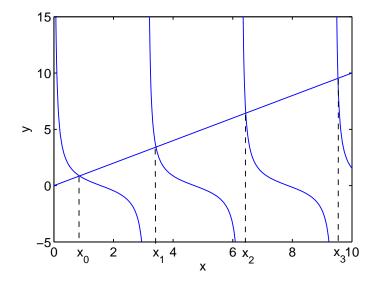

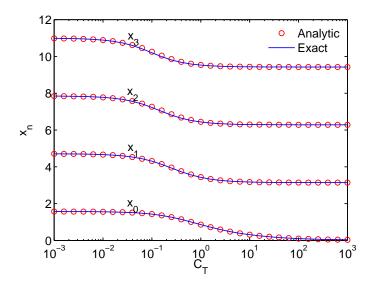

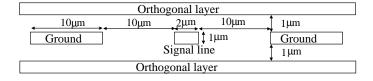

|   |          | 3.4.3   | Model Verification and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95 |

|   | 3.5      | Concli  | isions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 98 |

| 4 | Tra                       | nsient  | Response of a Distributed RLC Interconnect Based on          | 1        |  |  |

|---|---------------------------|---------|--------------------------------------------------------------|----------|--|--|

|   | Direct Pole Extraction 99 |         |                                                              |          |  |  |

|   | 4.1                       | Introd  | uction                                                       | 99       |  |  |

|   | 4.2                       | Specia  | l Cases of a Single Interconnect System                      | 101      |  |  |

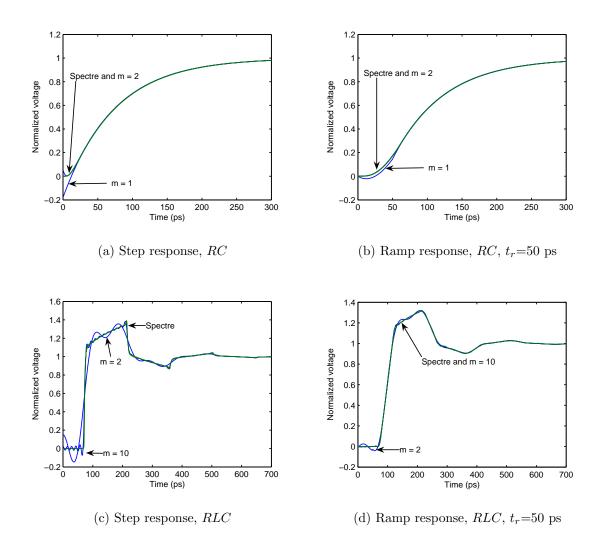

|   |                           | 4.2.1   | RC interconnect                                              | 102      |  |  |

|   |                           | 4.2.2   | $RLC$ interconnect with a zero $R_d$                         | 106      |  |  |

|   |                           | 4.2.3   | Step and Ramp Response                                       | 109      |  |  |

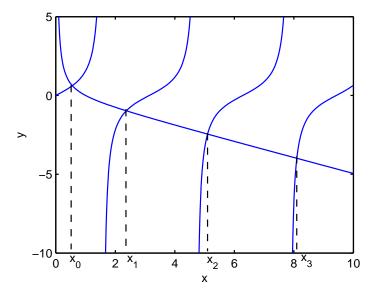

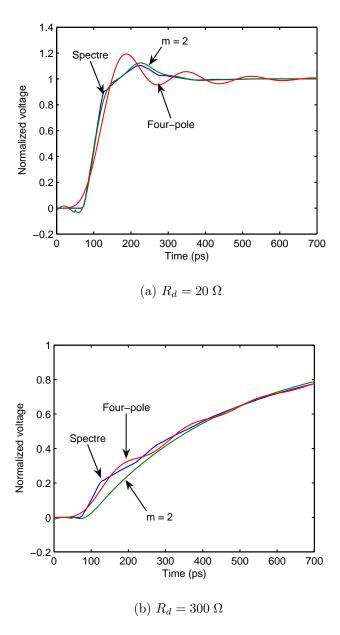

|   | 4.3                       | Distrib | outed <i>RLC</i> Interconnect with Driver Resistance         | 113      |  |  |

|   |                           | 4.3.1   | System Transform                                             | 114      |  |  |

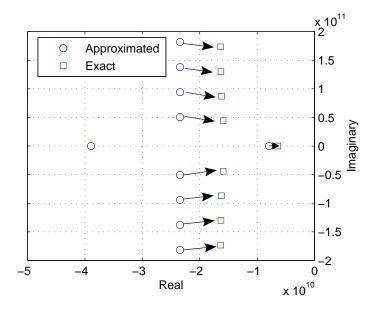

|   |                           | 4.3.2   | Improve the Accuracy of the Poles                            | 117      |  |  |

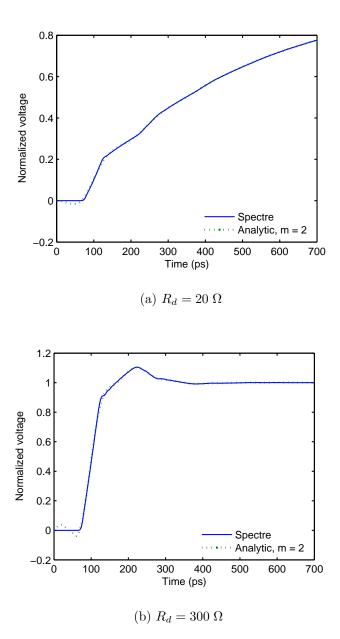

|   |                           | 4.3.3   | Model Accuracy and Efficiency                                | 121      |  |  |

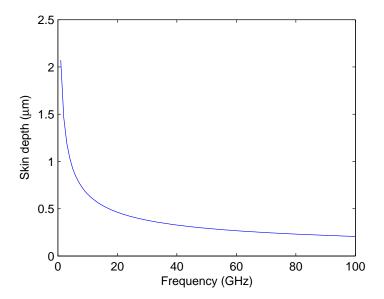

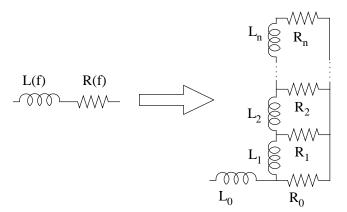

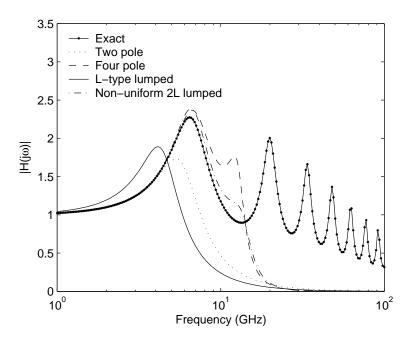

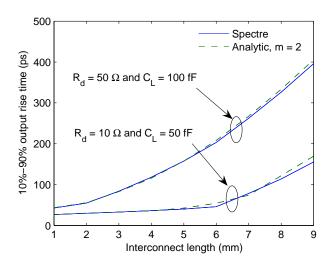

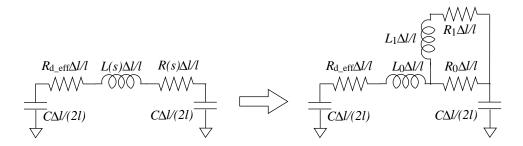

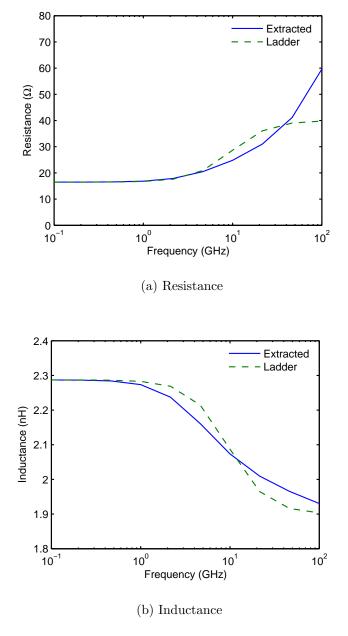

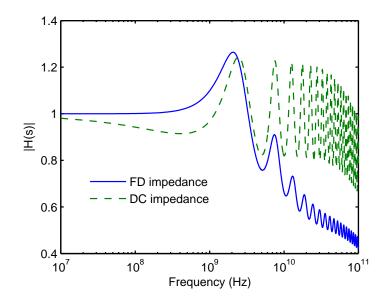

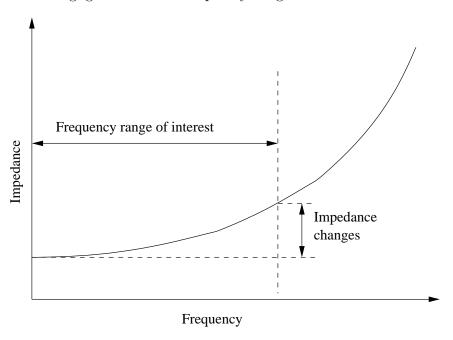

|   | 4.4                       | Freque  | ency Dependent Effects                                       | 123      |  |  |

|   | 4.5                       | Conclu  | asions                                                       | 130      |  |  |

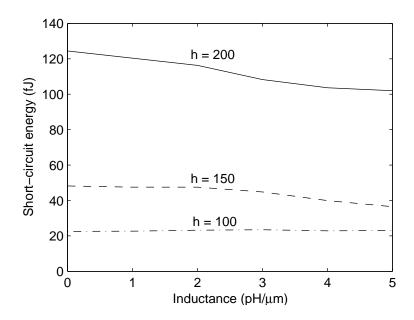

| 5 | Ffo                       | etivo ( | Capacitance of $RLC$ Loads for Estimating Short-Circui       | <b>+</b> |  |  |

| J | Pow                       |         | Capacitance of 11110 Loads for Estimating Short-Official     | 132      |  |  |

|   | 5.1                       |         | uction                                                       | 132      |  |  |

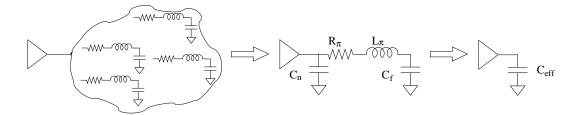

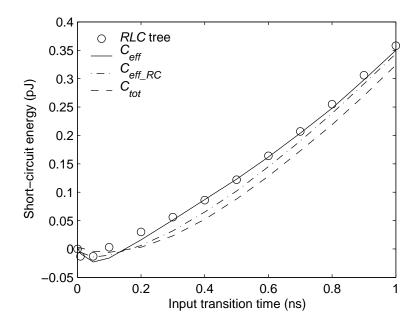

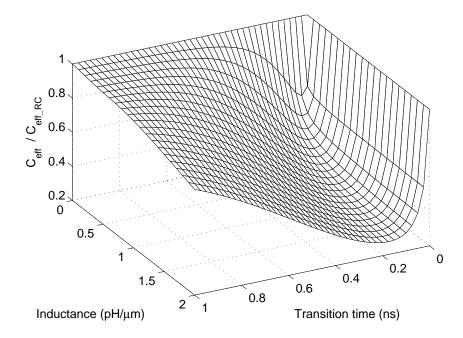

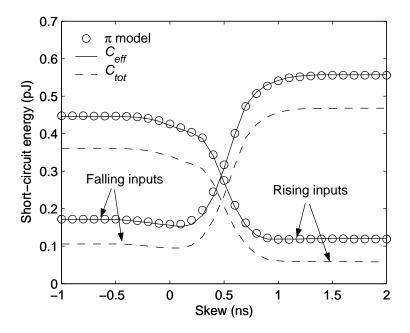

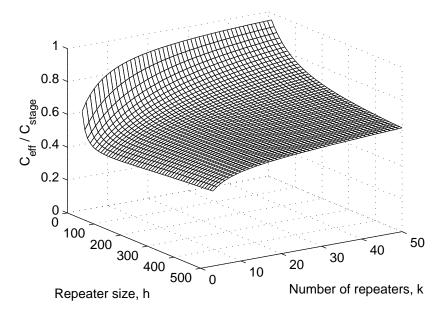

|   | 5.2                       |         | ve Capacitance of an $RLC$ Load                              | 133      |  |  |

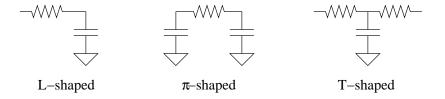

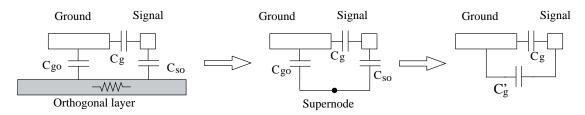

|   | J                         | 5.2.1   | $\pi$ -Model Representation of $RLC$ Interconnects           | 134      |  |  |

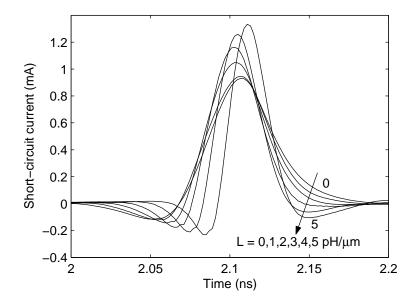

|   |                           | 5.2.2   | Effective Capacitance for Short-Circuit Power                | 136      |  |  |

|   | 5.3                       | Model   | Verification                                                 | 142      |  |  |

|   | 5.4                       |         | isions                                                       | 147      |  |  |

|   |                           |         |                                                              |          |  |  |

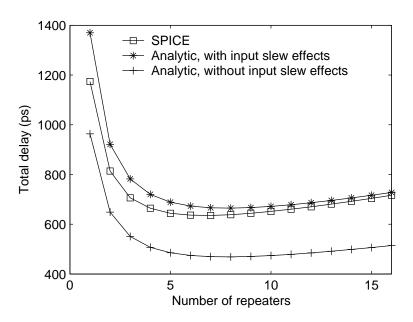

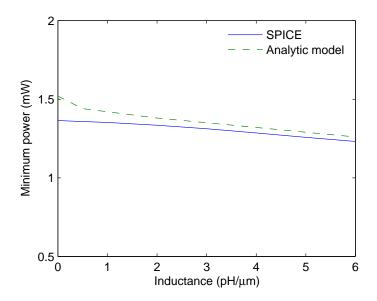

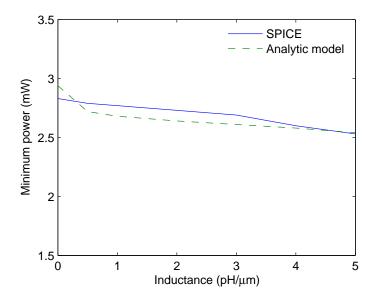

| 6 |                           |         | r Repeaters Driving $RC$ and $RLC$ Interconnects with Delay  | V        |  |  |

|   |                           | Bandy   | width Constraints                                            | 148      |  |  |

|   | 6.1                       |         | uction                                                       | 148      |  |  |

|   | 6.2                       | Power   | Dissipation in an $RC$ Interconnect with Delay and Bandwidth |          |  |  |

|   |                           | Constr  | raints                                                       | 150      |  |  |

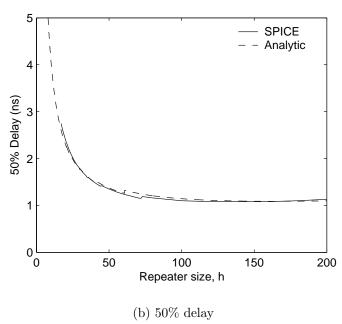

|   |                           | 6.2.1   | Delay and Transition Time Model of $RC$ Interconnects        | 150      |  |  |

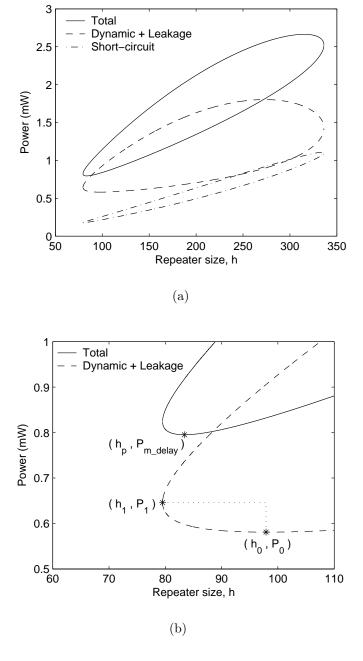

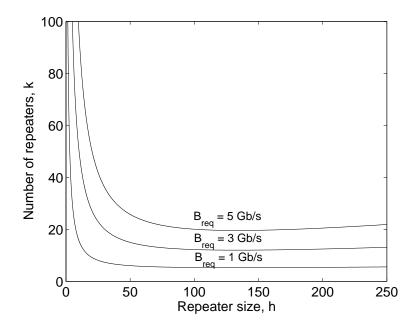

|   |                           | 6.2.2   | Power Dissipation Components in Interconnects with Repeaters | 156      |  |  |

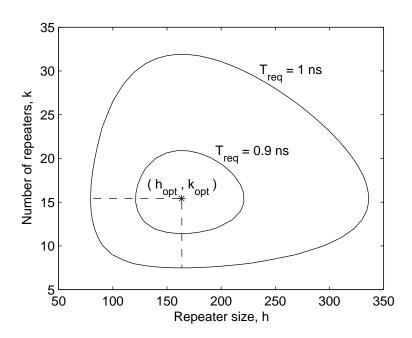

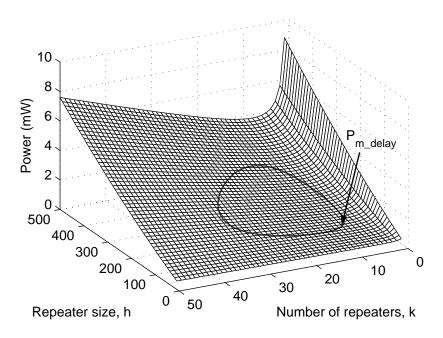

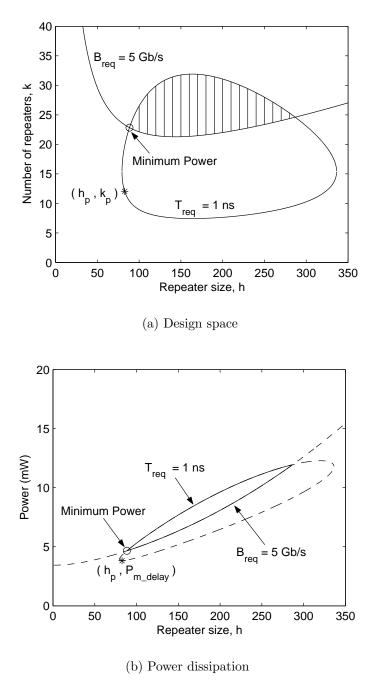

|   |                           | 6.2.3   | Power Dissipation with Delay Constraints                     | 160      |  |  |

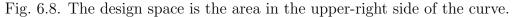

|   |                           | 6.2.4   | Power Dissipation with Bandwidth Constraints                 | 168      |  |  |

|   |      | 6.2.5                    | Power Dissipation with both Delay and Bandwidth Constraints | 171 |

|---|------|--------------------------|-------------------------------------------------------------|-----|

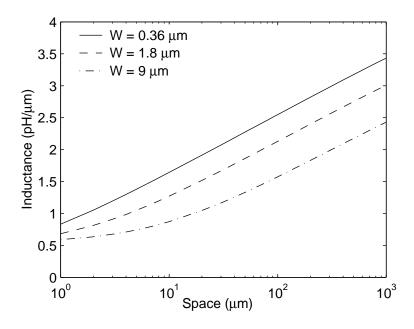

|   | 6.3  | Effects                  | of Inductance on the Repeater Insertion Methodology         | 173 |

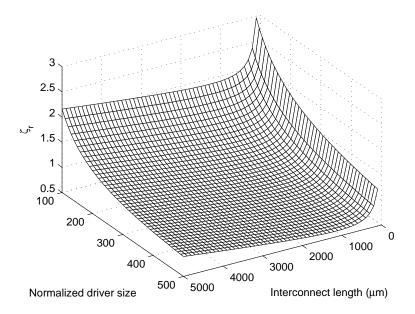

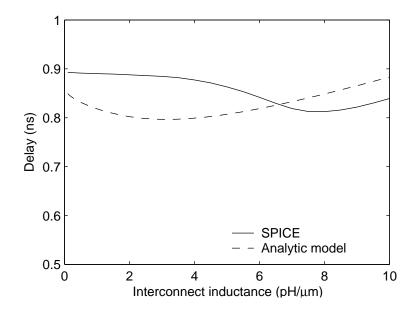

|   |      | 6.3.1                    | Timing Model of $RLC$ Interconnects                         | 173 |

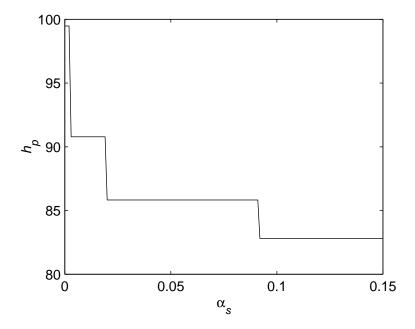

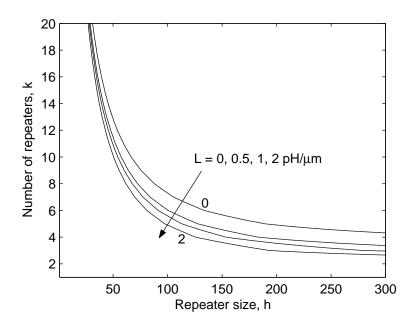

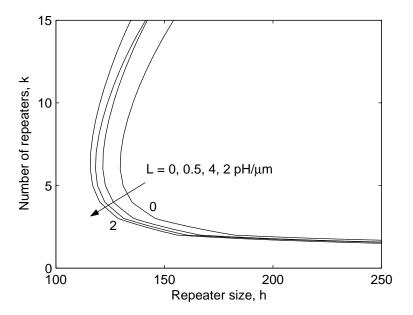

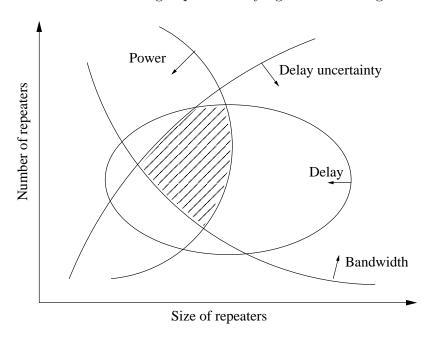

|   |      | 6.3.2                    | Effects of Inductance on the Repeater Design Space          | 176 |

|   |      | 6.3.3                    | Power Dissipation with Delay and Bandwidth Constraints      | 180 |

|   | 6.4  | Conclu                   | sions                                                       | 185 |

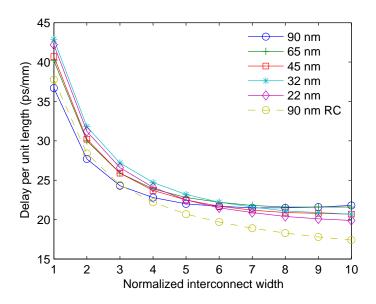

| 7 | Pre  | $\operatorname{diction}$ | s of CMOS Compatible On-Chip Optical Interconnect           | 187 |

|   | 7.1  | Introdu                  | uction                                                      | 187 |

|   | 7.2  | Electri                  | cal Interconnect                                            | 189 |

|   |      | 7.2.1                    | Delay Optimal Design                                        | 189 |

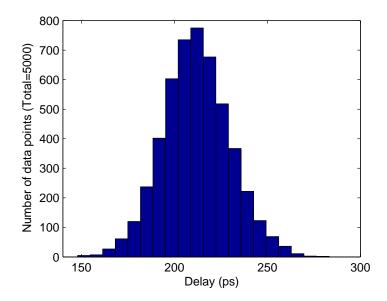

|   |      | 7.2.2                    | Delay Uncertainty Model                                     | 192 |

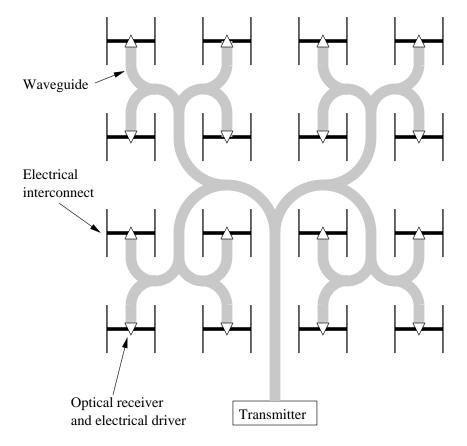

|   | 7.3  | On-Ch                    | ip Optical Data Path                                        | 193 |

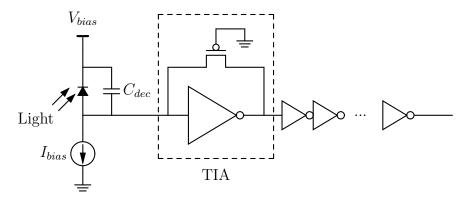

|   |      | 7.3.1                    | Transmitters                                                | 194 |

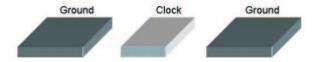

|   |      | 7.3.2                    | Waveguides                                                  | 197 |

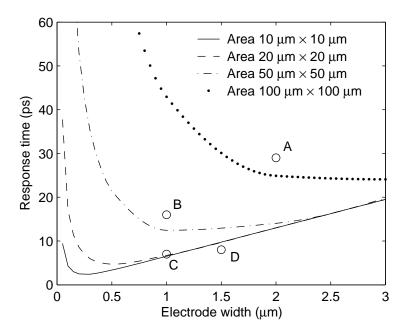

|   |      | 7.3.3                    | Receivers                                                   | 198 |

|   | 7.4  | Compa                    | arison between Electrical and Optical                       |     |

|   |      | Interco                  | onnects                                                     | 201 |

|   |      | 7.4.1                    | Delay Uncertainty                                           | 202 |

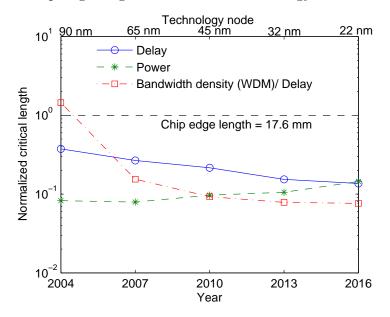

|   |      | 7.4.2                    | Delay                                                       | 210 |

|   |      | 7.4.3                    | Power                                                       | 212 |

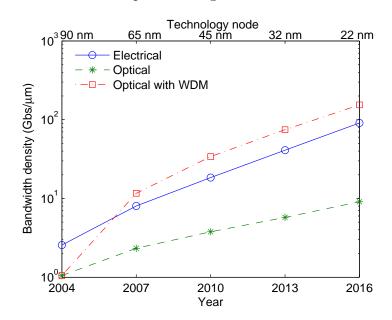

|   |      | 7.4.4                    | Bandwidth Density                                           | 213 |

|   |      | 7.4.5                    | Discussion                                                  | 215 |

|   | 7.5  | Potent                   | ial Challenges in Optical Interconnects                     | 216 |

|   | 7.6  | Conclu                   | sions                                                       | 218 |

| 8 | Con  | clusior                  | ns                                                          | 219 |

| 9 | Futi | ıre Re                   | search                                                      | 223 |

|   | 9.1  | Effect                   | of Repeaters on Delay Uncertainty                           | 224 |

|   | 9.2  | Figure                   | of Merit to Characterize the Importance of Frequency Depen- |     |

|   |      | dent E                   | ffects                                                      | 225 |

|                           | 9.3   | Design Methodology for Optical Clock Distribution Networks          | 227 |

|---------------------------|-------|---------------------------------------------------------------------|-----|

|                           | 9.4   | 3-D Integration with Optical Interconnects                          | 228 |

|                           | 9.5   | Summary                                                             | 229 |

| Bi                        | bliog | graphy                                                              | 230 |

| $\mathbf{A}_{\mathbf{J}}$ | ppen  | dices                                                               |     |

| $\mathbf{A}$              | Min   | simizing $P_{total}$ with a Delay Constraint for $RC$ Interconnects | 249 |

| В                         | Mo    | deling of MOSFET Transistors                                        | 253 |

|                           | B.1   | Threshold voltage                                                   | 254 |

|                           |       | B.1.1 Effect of $L$ variation                                       | 257 |

|                           |       | B.1.2 Effect of $T_{ox}$ variation                                  | 258 |

|                           |       | B.1.3 Effect of $N_{sub}$ variation                                 | 259 |

|                           |       | B.1.4 Effect of $T$ variation                                       | 259 |

|                           |       | B.1.5 Effect of $V_{dd}$ variation                                  | 260 |

|                           | B.2   | Mobility                                                            | 260 |

|                           | В.3   | I-V characteristics                                                 | 264 |

|                           | B.4   | Transconductance and output resistance                              | 265 |

| $\mathbf{C}$              | Pub   | olications                                                          | 267 |

# List of Tables

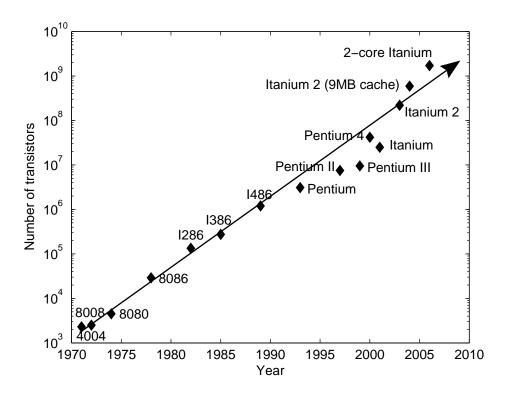

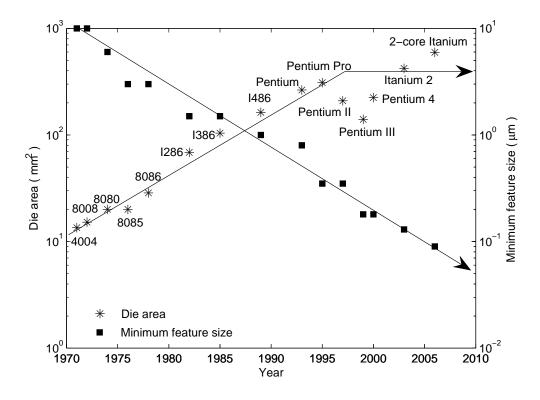

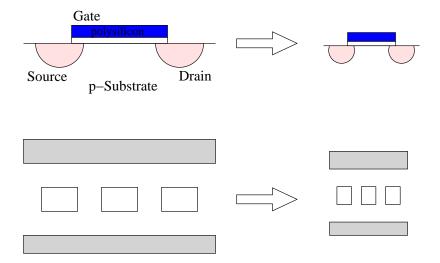

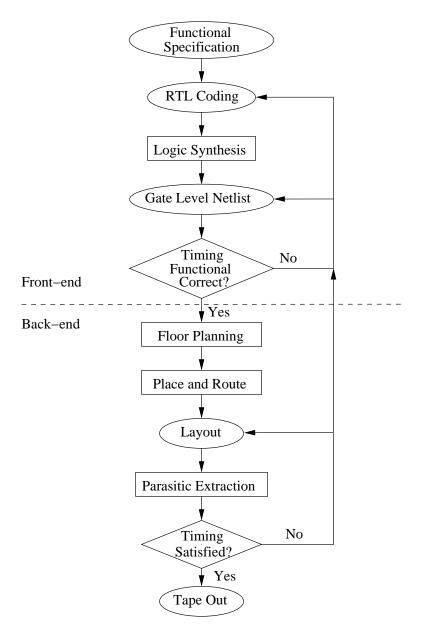

| 1.1 | Scaling trends in semiconductor device dimensions                                                                                                                                                                                            | 4   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

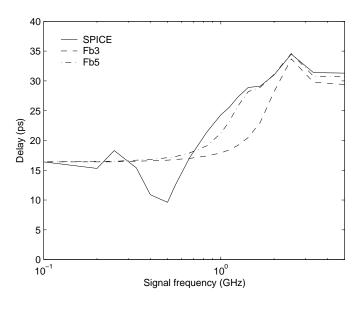

| 3.1 | Comparison of the 50% delay of Fb3 and Fb5 with SPICE and a single pole model. The input signal parameters are $T=500\mathrm{ps},\ \tau=50\mathrm{ps},$ and $V_{dd}=1.5\mathrm{volts}.$ The interconnect parameters are $l=2\mathrm{mm}$ and |     |

|     | $h=1\mu\mathrm{m}.$                                                                                                                                                                                                                          | 73  |

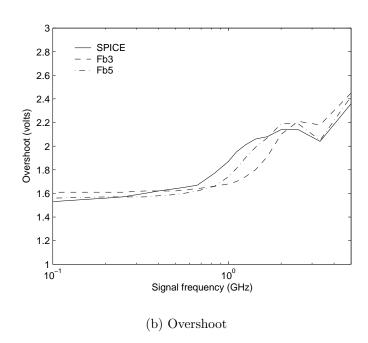

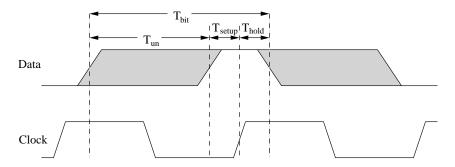

| 3.2 | Comparison of overshoots/undershoots of Fb3 and Fb5 with SPICE                                                                                                                                                                               |     |