# Transient Power in CMOS Gates Driving LC Transmission Lines

Yehea I. Ismail, Eby G. Friedman, and Jose L. Neves<sup>1</sup>

Department of Electrical Engineering University of Rochester Rochester, New York 14627 <sup>1</sup>IBM Microelectronics 1580 Route 52 East Fishkill, New York 12533

#### **Abstract**

The dynamic and short-circuit power consumption of a CMOS gate driving an LC transmission line as a limiting case of an RLC transmission line is investigated in this paper. Closed form solutions for the output voltage and short-circuit power of a CMOS gate driving an LC transmission line are presented. These solutions agree with circuit simulations within 11% error for a wide range of transistor widths and line impedances for a 0.25  $\mu$ m CMOS technology. The ratio of the short-circuit to dynamic power is shown to be less than 7% for CMOS gates driving LC transmission lines where the line is matched or underdriven. The total power consumption is expected to decrease as inductance effects becomes more significant as compared to an RC dominated interconnect line.

# I. Introduction

Historically, interconnect wires have been modeled as a single lumped capacitance in the performance analysis of on-chip interconnects [1]-[6]. With the scaling of technology and increasing chip size, the crosssectional area of the wires has scaled down while interconnect length has increased. The resistance of the interconnect has therefore become significant, requiring more accurate RC delay models [7]. Initially, the interconnect was modeled as a lumped RC circuit. To further improve accuracy, the interconnect is often modeled as a distributed RC circuit (as multiple T or  $\Pi$  sections) for those nets requiring increased accuracy.

Currently, inductance is becoming more important with decreasing on-chip rise times and longer wire lengths [10]-[16]. Wide wires are frequently encountered in clock distribution networks and in data busses. These wires, often at the upper metal layers, are low resistance wires that can exhibit significant inductive effects [15], [16]. Furthermore performance requirements are accelerating the introduction of new materials such as low resistivity copper interconnect [17]. In the limiting case, high temperature superconductors may possibly become commercially available [18]. More accurate *RLC* transmission line models are therefore becoming necessary in the analysis of VLSI-based interconnect.

The RC model can be viewed as a limiting case of the RLC transmission line model where the inductance is considered to be negligible. This case has been thoroughly investigated and is well represented in the literature [19]-[24]. The other limiting case is an

LC transmission line where the resistance is negligible. This case approximates the low loss lines encountered in Multi-Chip Modules (MCM) and Printed Circuit Boards (PCB). Although it is highly improbable that the resistance of on-chip interconnects will become negligible in the near term, an LC analysis provides an upper limit for analyzing inductance effects in VLSI circuits. The behavior of an RLC transmission line can therefore be bounded by analyzing the behavior of the RC and the LC cases.

The focus of this paper is the investigation of dynamic and short-circuit power in CMOS gates driving LC transmission lines. The dynamic and short-circuit power consumption of a CMOS gate driving an LC transmission line is discussed in section II. The analysis in section II is performed for the case where the transition time of the signal at the input of the CMOS gate driving a transmission line is smaller than twice the time of flight of the waves propagating across the transmission line. The short-circuit to dynamic power ratio for a lossless transmission line load is examined in section III and compared to the same ratio when the load is a simple capacitor or an RC line. Finally, some conclusions are offered in section IV.

#### II. Dynamic and short-circuit power

The dynamic power consumption can be derived from analyzing the behavior of a transmission line interacting with a CMOS gate. This topic is discussed in subsection A. It is shown that the dynamic power consumption of a CMOS gate driving a transmission line is the same as the dynamic power consumption of a gate driving a capacitor equal to the total capacitance of the transmission line. In subsection B, the short-circuit power consumption of a CMOS gate driving a lossless transmission line is investigated for the regime where  $t_r < 2T_o$  where  $t_r$  is the rise time of the input signal of the CMOS gate and  $T_o$  is the time of flight of the signals across the transmission line.

### A. Dynamic power

A MOS transistor driving a lossless transmission line launches an initial voltage wave with a value  $V_1 = I_{sat}$ ,  $Z_0$  where  $I_{sat}$  is the saturation current of the CMOS gate and  $Z_0$  is the characteristic impedance of the line. In estimating this initial voltage, the transmission line is modeled as a resistance with a value  $Z_0$  at the beginning of the transition, as shown in Fig. 1. This initial voltage signal propagates towards the load and reaches the load at time  $T_0$ . Assuming the load is open or is a small capacitor, a voltage wave propagates back towards the transistor with a magnitude  $V_1$  and a current wave  $I_{sat}$ . This wave returns to the MOS transistor at time  $2T_0$ . At that moment the current of the two waves cancels and the voltage adds to  $2V_1$ . For this period of time (from 0 to  $2T_0$ ), a current of  $V_1/Z_0$  is drawn from the power supply. At  $t=2T_0$ , a new voltage wave is initiated with a value  $V_2=I(V_{DD}-2V_1-1)$

This research was supported in part by the National Science Foundation under Grant No. MIP-9423886 and Grant No. MIP-9610108, the Army Research Office under Grant No. DAAH04-93-G-0323, a grant from the New York State Science and Technology Foundation to the Center for Advanced Technology - Electronic Imaging Systems, and by grants from the Xerox Corporation, IBM Corporation, and Intel Corporation.

$V_2$ ) $Z_0$ , where  $I(V_{DD}-2V_1-V_2)$  is the current of the transistor with  $V_{out} = 2V_1 + V_2$ . The cycle is repeated and a current  $V_2/Z_0$  is drawn from the supply for the period of time from  $2T_0$  to  $4T_0$ . This cycle repeats until the voltage at the output of the transistor reaches  $V_{DD}$ . The last voltage wave is assumed to be  $V_n$ , where n is the number of traversals of the line required to reach steady state. The number of iterations can in general be infinite or only one in the perfectly matched case (where the geometric width of the driving transistors is adjusted so that the output impedance of the CMOS gate is equal to the characteristic impedance of the transmission line).

Summing these voltages, the following condition is satisfied,

$$V_1+V_2+...+V_n=\frac{V_{DD}}{2}, \tag{1}$$

where the final voltage is  $V_{DD}$  once the transient response reaches

the steady state value. From this analysis, the energy taken from the power supply for a low to high transition is

$$E_{dyn} / Cycle = V_{DD} \cdot \frac{2T_o}{Z_0} \cdot (V_1 + V_2 + ... + V_n) \cdot$$

(2)

Using (1) and noting that  $T_o/Z_o$  is equal to  $C_p$  the total capacitance

of the line, (2) evaluates to

$$E_{dyn} / Cycle = C_t \cdot V_{DD}^2. (3)$$

This energy is stored in the capacitance of the line and is passed to the ground in the following high to low transition as the line is discharged. Thus, (3) represents the energy per cycle of the output of a CMOS gate. The dynamic power is therefore

$$P_{dyn} = C_t \cdot V_{DD}^2 f, \tag{4}$$

where f is the frequency of the signal at the output of the CMOS gate. This formula is the same as the dynamic power for a capacitor which equals the total capacitance of the line.

#### B. Short-circuit power

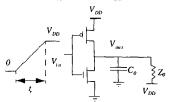

The other component of switching transient power in CMOS circuits is the short-circuit power that occurs when both the NMOS and the PMOS transistors conduct current at the same time. This power is consumed during the transition time of the input signal when the input signal is between  $V_{DD}+V_{Tp}$  and  $V_{Tn}$  (where  $V_{Tn}$  is the threshold voltage of the N-channel device and  $V_{Tp}$  is the threshold voltage of the P-channel device and is negative for an enhancement mode device). The case considered here is when the transition time (or rise/fall time) is less than twice the propagation delay across the line  $(t < 2T_0)$ . In this case, the reflections do not affect the short-circuit power because the signal returns to the driver after the input signal has reached its final value. Under this condition, the transmission line appears as a resistance with a value  $Z_0$ . The equivalent circuit of a CMOS inverter driving a lossless transmission line for the period of time 0 to  $2T_0$  is shown in Fig. 1, where  $C_0$  is the intrinsic drain capacitance of a CMOS inverter.

The differential equation describing the KCL for the output node is

$$(I_n - I_p) = C_0 \cdot \frac{d(V_{DD} - V_{out})}{dt} + \frac{(V_{DD} - V_{out})}{Z_0},$$

(5) where  $I_n$  and  $I_p$  are the currents of the NMOS transistor and the

PMOS transistor, respectively. Note that the resistance  $Z_n$ characterizing the transmission line impedance is connected between  $V_{\rm DD}$  and  $V_{\rm out}$  because the line is assumed to be charged to  $V_{DD}$  and that  $d(V_{DD}-V_{out})/dt=-d(V_{out})/dt$ . The NMOS transistor is assumed to be in the saturation region during the rise time of the input signal. This assumption is even more accurate in deep submicrometer technologies because of the early saturation phenomenon [25]. On the other hand, the PMOS transistor starts in the linear region and then enters the saturation region. Note that the short-circuit current is the current through the PMOS transistor during a rising input. The signal at the input of the CMOS driver is

$$V_{in} = kt = \frac{V_{DD}}{t_r} t^{\gamma}$$

(6) before the input reaches  $V_{DD}$  (i.e.,  $t < V_{DD}/k$ ).

Fig. 1. Equivalent circuit of a CMOS driver driving a lossless transmission line for  $0 < t < 2T_0$ .

Based on the alpha power law [25], when the PMOS transistor

is in saturation the short-circuit current is

$$I_{SC} = P_{Cp} \cdot \frac{W_p}{L_p} \cdot (V_{DD} - kt - |V_{Tp}|)^{\alpha p}. \tag{7}$$

where  $P_c$  is a constant that characterizes the drive current of the transistor in saturation, W and L are the geometric width and length, respectively, of the transistor, and  $\alpha$  is a constant between one (strong velocity saturation) and two (weak velocity saturation) [25]. p indicates the PMOS transistor and n indicates the NMOS transistor. When the PMOS transistor operates in the linear region, the solution of (5) appears intractable because  $V_{DS}$  is a function of  $V_{out}$ . Therefore, the current from the output capacitor  $C_o$ is assumed to be small compared to the current from the transmission line. This assumption is accurate in deep submicrometer technologies, because the transistors have small parasitic capacitances and high current levels. The magnitude of the drive current is relevant because smaller transistors are needed to match the transmission line impedance, implying a smaller  $C_{o}$ . Also  $Z_0$  is typically in the range of 30 to 60 ohms, which results in large currents compared to the parasitic capacitance  $C_0$ . Under this assumption and using the alpha power law model, the output voltage is

$$V_{out} = V_{DD} - \frac{Z_0 \cdot P_{Cn} \cdot \frac{W_n}{L_n} \cdot (kt - V_{Tn})^{out}}{1 + \frac{P_{Cp}}{P_{Vp}} \cdot \frac{W_p}{L_p} \cdot (V_{DD} - kt - |V_{Tp}|)^{\frac{oup}{2}} \cdot Z_o},$$

(8)

for the time  $0 < t < t_r$  where  $t_r < 2T_0$ . Noting that  $V_{DD}$ - $V_{out}$  is  $V_{SD}$  of the PMOS transistor, the short-circuit current of a CMOS inverter driving an LC transmission line is

$$I_{SC} = \frac{Z_0 \cdot P_{C_n} \cdot \frac{W_n}{L_n} \cdot (kt - V_{T_n})^{\alpha n}}{P_{C_p} \cdot \frac{L_p}{W_p} \cdot (V_{DD} - kt - |V_{T_p}|)^{-\frac{\alpha p}{2}} + Z_o}.$$

(9)

A CMOS gate driving a transmission line can be most efficiently characterized by the matching factor  $\lambda$ , where

$$\lambda = \frac{2S_p W_p Z_0}{V_{DD}},\tag{10}$$

where  $S_n$  is a technology dependent constant. When  $\lambda = 1$ , the transistor is optimally matched to the transmission line. If  $\lambda$  is less than one, the transmission line is underdriven and the response suffers from a slow output rise time. If  $\lambda$  is greater than one, the transmission line is overdriven and the response suffers from overshoots and undershoots that can cause reliability problems. If the overshoots and undershoots are sufficiently large, logical errors can occur. Voltages higher than the supply voltage and lower than ground create large electric fields that can deteriorate the oxide and create hot electron effects. Also, out of rail voltages can forward bias the junctions between the drain and source and the substrate, the n-well, or the p-well. When these junctions are forward biased, current flows directly into the wells or the substrate. This behavior is undesirable because it wastes current, dissipating extra power, and can induce other reliability problems within the substrate. Thus, the range defined by  $0.3 < \lambda < 1.6$  is arbitrarily chosen to represent the range of interest characterizing practical matching conditions.

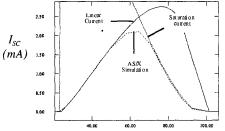

The analytical solution for  $I_{SC}$  in (7) and (9) shows good agreement with the circuit simulations for a 0.25  $\mu$ m CMOS technology. Note that the short-circuit current has the shape of a triangle as shown in Fig. 2.

Fig. 2. Analytical solution for short-circuit current  $I_{SC}$  in (7) and (9) compared to AS/X simulations [26] for  $\lambda=1$ .

The short-circuit energy per transition can be calculated from

$$E_{SC}$$

/ Transition =  $Area_{SC} \cdot V_{DD}$ , (11)

where  $Area_{SC}$  (in coulombs) is the area under the short-circuit current curve. This area can be approximated by a triangle [21] whose base is given by  $(V_{DD}-V_{TR}+V_{TP})t_{I}/V_{DD}$  and height is given by  $I_{peak}$  (the maximum point on the short-circuit current curve). Thus, the short-circuit energy per transition is

$$E_{SC}/Transition = \frac{I_{peak}}{2} (V_{DD} - V_{Tn} - |V_{Tp}|) t_r K_c,$$

(12)

where  $K_c$  is a correction factor and is calibrated at  $\lambda=1$ .  $I_{peak}$  can be calculated by equating (7) and (9). Alternatively,  $I_{peak}$  can be calculated as

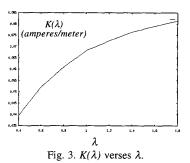

$$I_{peak} = K(\lambda)W_p, \tag{13}$$

where  $K(\lambda)$  is determined from varying  $\lambda$  and calculating  $I_{peak}/W_{p}$ ,  $K(\lambda)$  for a specific 0.25  $\mu$ m CMOS technology is plotted in Fig. 3.

$K(\lambda)$  quantifies in  $I_{peak}$  the effect of the output waveform shape on the short-circuit current. Note that  $K(\lambda)$  saturates to an asymptotic value. The current of the PMOS transistor depends on the bias voltage and the geometric width. The AS/X circuit simulator [26] is used to quantify the accuracy of these analytic equations, such as the comparison of (12) with AS/X in Table 1. The analytical solution shows good agreement (less than 1% error for  $\lambda \geq 1$ ) with the circuit simulations for a wide range of  $\lambda$  and exhibits a maximum error of 11% for small  $\lambda$ .

Table 1: AS/X simulations compared to analytical solution for  $E_{sc}$ /transition (in joules).

| λ   | AS/X<br>Simulation<br>x10 <sup>-15</sup> | Analytical x10 <sup>-15</sup> | %<br>Error |

|-----|------------------------------------------|-------------------------------|------------|

| 0.4 | 131.20                                   | 116.00                        | 11.00      |

| 0.6 | 161.45                                   | 152.50                        | 5.50       |

| 0.8 | 182.77                                   | 178.95                        | 2.09       |

| 1.0 | 199.60                                   | 199.60                        | 0.00       |

| 1.2 | 212.55                                   | 212.30                        | 0.12       |

| 1.4 | 224.55                                   | 223.20                        | 0.60       |

| 1.6 | _231.93                                  | 231.37                        | 0.24       |

| 1.8 | 239.68                                   | 238.20                        | 0.62       |

## III. Short-circuit to dynamic power ratio

Assuming a symmetric CMOS gate, the short-circuit power is

$$P_{SC} = I_{peak}(V_{DD} - V_{Tn} - |V_{Tp}|)t_r f.$$

(14)

As described previously, the dynamic power is

$$P_{dyn} = \frac{T_0}{Z_0} \cdot V_{DD}^2 f. {15}$$

Dividing (14) by (15), the magnitude of the dynamic power can be compared to the magnitude of the short-circuit power. The resulting ratio is

$$\frac{P_{SC}}{P_{dvn}} = K(\lambda)\lambda \cdot \frac{\left(V_{DD} - V_{Tn} - \left|V_{Tp}\right|\right)}{V_{DD}} \frac{t_r}{T_0} \cdot \frac{K_c}{2S_p}$$

(16)

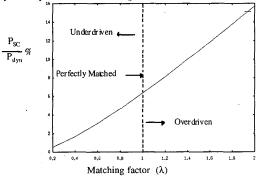

The ratio between the short circuit power and the dynamic power depends upon the matching condition  $\lambda$  of the transmission line impedance to the output impedance of the CMOS gate and the ratio between the rise time of the input signal to the time of flight of the waves across the transmission line  $(t/T_0)$ . The dependence on the supply voltage is fairly weak. The dependence exists only if the supply voltage and the threshold voltages scale differently. The dependence of the short-circuit to dynamic power ratio on  $\lambda$  is shown in Fig. 4. As the matching condition moves from underdriven to matched to overdriven, the short-circuit to dynamic power ratio increases. This ratio is less than 7% for the matched  $(\lambda=1)$  and underdriven cases  $(\lambda<1)$ . In the matched case, the input signal transitions approximately twice as fast as the output signal since the input signal transitions from  $\theta$  to  $V_{DD}$  at the same time as the output signal transitions from  $\theta$  to  $V_{DD}/2$ . For the underdriven case, the output voltage transitions from  $\theta$  to  $V_f$  where  $V_f$  is less than  $V_{DD}/2$ . For the overdriven case,  $V_f$  is greater than  $V_{DD}/2$ . Therefore, it is preferable to not overdrive the line (i.e., make  $\lambda$  > 1) in order to decrease the short-circuit power. The classical design criterion for driving a capacitive load is to maintain the input transition time  $(t_{rin})$  equal to the output transition time  $(t_{rout})$ , i.e.,  $t_{row}/t_{rin}=1$ , which gives rise to a short-circuit power of approximately 20% of the dynamic power [3]. The low output to input transition time ratio for the matched and underdriven cases  $(t_{rou}/t_{rin})$  less than or equal to 0.5) provides an explanation for the cause of the lower short-circuit to dynamic power ratio in a matched or underdriven circuit as compared to a simple capacitive load. For RC loads, the  $P_{SC}/P_{Dyn}$  ratio is even greater than that of a capacitive load because the voltage drop across the load resistance makes the source to drain voltage large once the transistor begins

As the rise time of the input signal  $t_r$  increases, the shortcircuit power increases, since there is more time for the shortcircuit current to flow. The rise time  $t_r$  does not affect the dynamic power and thus increasing  $t_r$  increases the ratio of the short-circuit power to the dynamic power. Dynamic power increases with increasing  $T_0$  because the total capacitance of the line is  $T_0/Z_0$ . Thus, as  $T_0$  increases, the capacitance of the line increases linearly which increases the dynamic power linearly. The short-circuit power is not affected by  $T_0$  as long as  $T_0$  is greater than half the input rise time, making the ratio of the short-circuit power to the dynamic power decrease as  $T_0$  is increased.

Fig. 4. Dependence of short circuit to dynamic power ratio on  $\lambda$ .

## IV. Conclusions

The dynamic and short-circuit power consumed by a CMOS gate driving a lossless transmission line is investigated. It is shown that the dynamic power of a CMOS gate driving a lossless transmission line is the same as that of a CMOS gate driving a capacitor equal to the total capacitance of the line. A closed form solution for the short-circuit power is presented that agrees with circuit simulations within 11% error for a wide range of the matching factor  $\lambda$ . An expression for the short-circuit to dynamic power ratio is presented that shows that the short-circuit power is below 7% of the dynamic power for  $\lambda$  less than or equal to one. The short-circuit power for the case of LC loads is much less than that of the case of RC loads. In the case of RLC loads, the shortcircuit power is in the middle, greater than the case of LC loads but less than the case of RC loads.

#### References

T. Sakurai and K. Tamaru, "Simple Formulas for Two- and Three-[1] Dimensional Capacitances," IEEE Transactions on Electron

- Devices, Vol. ED-30, No. 2, pp. 183 185, February 1983.

E. Barke, "Line-to-Ground Capacitance Calculation for VLSI: A Comparison," *IEEE Transactions on Computer-Aided Design*, Vol. CAD-7, No. 2, pp. 295 298, February 1988.

H. J. M. Veendrick, "Short-Circuit Dissipation of Static CMOS Circuits and its Impact on the Design of Parties," *IEEE Circuits* "IEEE [2]

- Circuitry and its Impact on the Design of Buffer Circuits," IEEE Journal of Solid-State Circuits, Vol. SC-19, No. 4, pp. 468 473,

- McLandrian J. Huang, L. Arledge, P. Li, and P. Yang, "Multilevel Metal capacitance Models for CAD Design Synthesis Systems," *IEEE Electron Device Letters*, Vol. EDL-13, No. 1, pp. 32 34,

- January 1992.

S. R. Vemuru and N. Scheinberg "Short-Circuit Power Dissipation Estimation for CMOS Logic Gates," *IEEE Transactions on Circuits and Systems*, Vol. CAS-41, No. 11, pp. 762 765, November 1994.

J. M. Rabaey, *Digital Integrated Circuits, A Design Perspective*, Prentice Hall, Inc., New Jersey, 1996.

S. Bothra, B. Rogers, M. Kellam, and C. M. Osburn "Analysis of the Effects of Scaling on Interconnect Delay in ULSI Circuits," *IEEE Transactions on Electron Devices* Vol. ED-40, No. 3, pp. 591 597, March 1993

- March 1993. T. Sakurai, "Approximation of Wiring Delay in MOSFET LSI," *IEEE Journal of Solid-State Circuits*, Vol. SC-18, No. 4, pp. 418 -

- [9]

- 18, No. 3, pp. 21 30, June 1988.

D. A. Priore, "Inductance on Silicon for Sub-Micron CMOS VLSI." 1101 Proceedings of the IEEE Symposium on VLSI Circuits, pp. 17-18,

- May 1993.

D. B. Jarvis, "The Effects of Interconnections on High-Speed Logic [11] Circuits," IEEE Transactions on Electronic Computers, Vol. EC-10, No. 4, pp. 476 - 487, October 1963.

- [12]

- M. Shoji, High-Speed Digital Circuits, Addison Wesley, Massachusetts, 1996.

Y. Eo and W. R. Eisenstadt, "High-Speed VLSI Interconnect Modeling Based on S-Parameter Measurement," IEEE Transactions

- [14]

- Modeling Based on S-Parameter Measurement," IEEE Transactions on Components, Hybrids, and Manufacturing Technology, Vol. CHMT-16, No. 5, pp. 555 562, August 1993.

A. Deutsch et al., "High-Speed Signal Propagation on Lossy Transmission Lines," IBM Journal of Research and Development, Vol. 34, No. 4, pp. 601 615, July 1990.

A. Deutsch et al., "Modeling and Characterization of Long Interconnections for High-Performance Microprocessors," IBM Journal of Research and Development, Vol. 39, No. 5, pp. 547 667 September 1995 [15] 667, September 1995

- A. Deutsch et al., "When are Transmission-Line Effects Important for On-Chip Interconnections?," *IEEE Transactions on Microwave Theory and Techniques*, Vol. MTT-45, No. 10, pp. 1836-46, [16] October 1997

- J. Torres, "Advanced Copper Interconnections for Silicon CMOS Technologies," *Applied Surface Science*, Vol. 91, No. 1, pp. 112-123, October 1995. [17]

- K. K. Likharev and V. K. Semenov, "RSFQ Logic/Memory Family: [18]

- K. K. Likharev and V. K. Semenov, "RSFQ Logic/Memory Family: A New Josephson-Junction Technology for Sub-Terahertz-Clock Frequency Digital System," *IEEE Transactions on Applied Superconductivity*, Vol. AS-1, No. 1, pp. 3 28, March 1991.

E. G. Friedman and J. H. Mulligan, Jr., "Ramp Input Response of RC Tree Networks," *Analog Integrated Circuits and Signal Processing*, Vol. 14, No. 1/2, pp. 53-58, September 1997.

L. V. Ginneken, "Buffer Placement in Distributed RC-tree Networks for Minimal Elmore Delay," *Proceedings of the International Symposium on Circuits and Systems*, pp. 865 868, May 1990. [20]

- V. Adler and E. G. Friedman, "Delay and Power Expressions for a CMOS Inverter Driving a Resistive-Capacitive Load," Analog Integrated Circuits and Signal Processing, Vol. 14, No. 1/2, pp. 29 September 1997.

- J. Rubinstein, P. Penfield, and M. Horowitz, "Signal Delay in RC Tree Networks," IEEE Transactions on Computer-Aided Design, [22]

- M. Horowitz and R. W. Dutton, "Resistance Extraction from Mask [23]

- [24]

- M. Horowitz and R. W. Dutton, "Resistance Extraction from Mask Layout Data," *IEEE Transactions on Computer-Aided Design*, Vol. CAD-2, No. 3, pp. 145 150, July 1983.

R. J. Antinone and G, W. Brown, "The Modeling of Resistive Interconnects for Integrated Circuits," *IEEE Journal of Solid-State Circuits*, Vol. SC-18, No. 2, pp. 200 203, April 1983.

T. Sakurai and A. R. Newton "Alpha-Power Law MOSFET Model and its Applications to CMOS Inverter Delay and Other Formulas," *IEEE Journal of Solid-State Circuits*, Vol. SC-25, No. 2, pp. 584 593. April 1990. [25]

- AS/X User's Guide, IBM Corporation, New York, 1996. [26]