# Noise Aware Decoupling Capacitors for Multi-Voltage Power Distribution Systems

Mikhail Popovich and Eby G. Friedman

Department of Electrical and Computer Engineering University of Rochester, Rochester, New York 14627 nhlover@ece.rochester.edu, friedman@ece.rochester.edu

*Abstract*— Multiple power supply voltages are often used in modern high performance ICs such as microprocessors to decrease power consumption without affecting circuit speed. The system of decoupling capacitors used in power distribution systems with multiple power supplies is described in this paper. In order to minimize the total impedance of a multi-voltage power delivery system as seen from a particular power supply, a decoupling capacitor is placed between the power supplies. The noise at one power supply can couple into the other power supply, causing power and signal integrity problems in the overall system. With the introduction of a second power supply, therefore, the interaction between the two power distribution networks should be considered.

The dependence of the magnitude of the voltage transfer function on the parameters of the power distribution system is investigated. It is shown that it is highly desirable to maintain the effective series inductance of the decoupling capacitors as low as possible to decrease the overshoots in the response of a dual voltage power distribution system over a wide range of operating frequencies. A criterion for an overshoot-free voltage response is presented in this paper. It is noted that the frequency range of the overshoot-free voltage response can be traded off with the magnitude of the response.

### I. INTRODUCTION

The use of multiple on-chip supply voltages has recently become common practice [1]. This strategy has the advantage of allowing modules along the critical paths to operate at the highest available voltage (in order to satisfy target timing constraints) while permitting modules along the non-critical paths to use a lower voltage (thereby reducing energy consumption). In this manner, the energy consumption is decreased without degrading circuit speed. This scheme results in smaller area as compared with parallel architectures. The use of multiple supply voltages for reducing power has been investigated in the area of high level synthesis for low power [2,3]. While it is possible to use many supply voltages, in practice such a scenario is expensive. Practically, the availability of a small number of voltage supplies (two or three) is reasonable. The design of the power distribution system has become an increasingly difficult challenge in modern CMOS circuits [4]. By introducing a second power supply, the power supplies become coupled through a decoupling capacitor effectively placed between the two power supply voltages. Assuming a power delivery system with dual power supplies and only a small per cent of the power supply voltage is permitted as ripple voltage (noise), the following inequality for the magnitude of a voltage transfer function  $K_V$  should be satisfied,

$$|K_V| \le \frac{r \times V_{dd1}}{V_{dd2}},\tag{1}$$

where  $V_{dd1}$  is a lower voltage power supply, r is the allowed ripple voltage on a lower voltage power supply, and  $V_{dd2}$  is a higher voltage power supply. For typical values of the power supply voltages and allowed ripple voltage for a 0.18  $\mu$ m CMOS technology,  $|K_V|$  is chosen to be less than or equal to 0.1 to effectively decouple a noisy power supply from a quiet power supply.

Noise coupling among multiple power distribution systems is discussed in this paper. A methodology for designing the decoupling capacitors is presented and a criterion for producing an overshoot-free voltage response is determined. In certain cases, it is difficult to satisfy this criterion over the entire range of operating frequencies. In such a scenario, the frequency range of an overshoot-free voltage response is divided by the self resonant frequency of the system into two ranges. Alternatively, the frequency range of an overshoot-free voltage response can be traded off with the magnitude of the response. Case studies are also presented in this paper to quantitatively illustrate the proposed methodology for designing a system of decoupling capacitors.

The paper is organized as follows. The voltage transfer function of a power distribution system with multiple supply voltages is presented in Section II. A case study of a power distribution system is discussed in Section III. Some specific conclusions are summarized in Section IV.

# II. VOLTAGE TRANSFER FUNCTION OF A POWER DISTRIBUTION SYSTEM WITH MULTIPLE SUPPLY VOLTAGES

Classical methodologies for designing power distribution systems with a single power supply voltage primarily focus on the target output impedance of the network. By introducing

This research was supported in part by the Semiconductor Research Corporation under Contract No. 2003-TJ-1068 and 2004-TJ-1207, the National Science Foundation under Contract No. CCR-0304574, the Fulbright Program under Grant No. 87481764, a grant from the New York State Office of Science, Technology & Academic Research to the Center for Advanced Technology in Electronic Imaging Systems, and by grants from Xerox Corporation, IBM Corporation, Intel Corporation, Lucent Technologies Corporation, and Eastman Kodak Company.

a second power supply voltage, a decoupling capacitor is effectively placed between the two power supply voltages [5,6]. The problem of noise propagating from one power supply to the other power supply is aggravated if multiple power supply voltages are employed in a power distribution system. The voltage transfer function of a power distribution system with dual power supplies is described in subsection II-A. The dependence of the magnitude of the voltage transfer function on certain parameters of the power distribution system is described in subsection II-B.

#### A. Voltage transfer function of a power distribution system

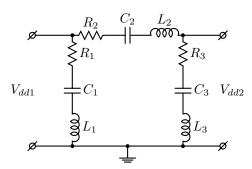

A power distribution system with two power supply voltages and the decoupling capacitors represented by an RLC series network is shown in Fig. 1. All of the following formulae describing this system are symmetric in terms of the power supply voltages. The Effective Series Resistance (ESR) and Effective Series Inductance (ESL) represent, respectively, the parasitic resistance and inductance of a decoupling capacitor. The ESR and ESL of the three decoupling capacitors are represented by  $R_1$ ,  $R_2$ ,  $R_3$  and  $L_1$ ,  $L_2$ ,  $L_3$ , respectively.

Fig. 1. Power distribution system with two supply voltages where the decoupling capacitors are represented as series *RLC* networks.

The voltage transfer function  $K_V$  of a dual-voltage power distribution system is

$$K_V = \frac{a_2 s^2 + a_1 s + a_0}{b_2 s^2 + b_1 s + b_0},$$

$$a_2 = L_3 C_3,$$

(2)

$$a_{1} = R_{3}C_{3},$$

$$a_{0} = C_{2},$$

$$b_{2} = C_{2}C_{3}(L_{2} + L_{3}),$$

$$b_{1} = C_{2}C_{3}(R_{2} + R_{3}),$$

$$b_{0} = C_{2} + C_{3}.$$

Rearranging, (2) can be written as

$$K_V = \frac{1}{\frac{a_2 s^2 + a_1 s + a_0}{b_2 s^2 + b_1 s + b_0} + 1},$$

(3)

$$\begin{array}{rcl} a_2 &=& L_2 C_2 C_3,\\ a_1 &=& R_2 C_2 C_3,\\ a_0 &=& C_3,\\ b_2 &=& L_3 C_2 C_3,\\ b_1 &=& R_3 C_2 C_3,\\ b_0 &=& C_2. \end{array}$$

Equations (2) and (3) are valid only for non-zero frequency, *i.e.*, for s > 0. The dependence of the voltage transfer function on the parameters of the power distribution system is discussed below.

# B. Dependence of voltage transfer function on power distribution system parameters

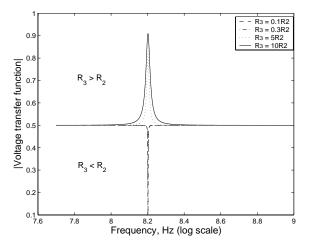

The dependence of the magnitude of the voltage transfer function on frequency for different values of the ESR of the decoupling capacitors is shown in Fig. 2. Reducing the ESR of a decoupling capacitor decreases the magnitude and range of the operating frequency of the transfer function. Note that to produce an overshoot-free voltage response, the following inequality has to be satisfied,

$$R_3 \le R_2. \tag{4}$$

Fig. 2. Dependence of the magnitude of the voltage transfer function on frequency of a dual  $V_{dd}$  power distribution system for different values of ESR of the decoupling capacitors.  $R_2 = 10 \text{ m}\Omega$ ,  $C_2 = C_3 = 1 \text{ nF}$ , and  $L_2 = L_3 = 1 \text{ nH}$ .

This behavior can be explained as follows. From (3), to produce an overshoot-free voltage response,

$$\frac{L_2C_2C_3s^2 + R_2C_2C_3s + C_3}{L_3C_2C_3s^2 + R_3C_2C_3s + C_2} + 1 \ge 2.$$

(5)

For equal decoupling capacitors and parasitic inductances, (5) leads directly to (4). In order to maintain the magnitude of the voltage transfer function overshoot-free, the ESR and ESL of the decoupling capacitors should be chosen to satisfy (5).

To investigate the dependence of the magnitude of the voltage transfer function on the decoupling capacitors and

associated parasitic impedances, the roots of the characteristic equation, the denominator of (2), should be analyzed. To produce an overshoot-free response, the roots of the characteristic equation must be real, yielding

$$R_2 + R_3 \ge 2\sqrt{\frac{(L_2 + L_3)(C_2 + C_3)}{C_2 C_3}}.$$

(6)

In the case where  $R_2 = R_3 = R$ ,  $L_2 = L_3 = L$ , and  $C_2 = C_3 = C$ , (6) reduces to the well known formula [7],

$$R \ge 2\sqrt{\frac{L}{C}}.\tag{7}$$

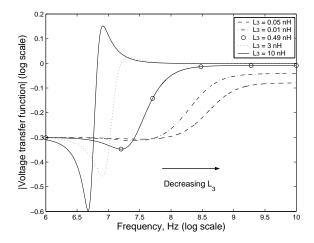

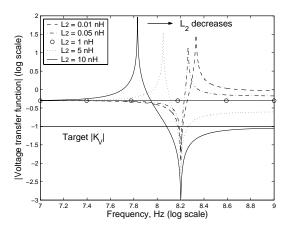

The dependence of the magnitude of the voltage transfer function on the ESL of a power distribution system is shown in Fig. 3. For the power distribution system parameters listed in Fig. 3, the critical value of  $L_3$  to ensure an overshootfree response is 0.49 nH. Therefore, in order to produce an overshoot-free response, the ESL of  $C_3$  should be smaller than or equal to 0.49 nH.

Fig. 3. Frequency dependence of the voltage transfer function of a dual  $V_{dd}$  power distribution system for different values of ESL of the decoupling capacitors.  $R_2 = R_3 = 100 \text{ m}\Omega$ ,  $C_2 = C_3 = 100 \text{ nF}$ , and  $L_2 = 10 \text{ pH}$ .

As shown in Fig. 3, the magnitude of the voltage transfer function is strongly dependent on the ESL, decreasing with smaller ESL. It is highly desirable to maintain the ESL as low as possible to achieve a small overshoot-free response characterizing a dual  $V_{dd}$  power distribution system over a wide range of operating frequencies. Criterion (6) is strict and produces an overshoot-free voltage response. In most applications, if small overshoots (about 1%) are permitted, (6) is less strict, permitting the parameters of a power distribution network to vary over a wider range.

For the parameters listed in Fig. 3, the minimum overshootfree voltage response equals 0.5. It is often necessary to maintain an extremely low magnitude voltage transfer function over a specific frequency range. This behavior can be achieved by varying one of the three design parameters (ESR, ESL or C) characterizing a decoupling capacitor while maintaining the other parameters at predefined values. In this case, for different decoupling capacitors, the magnitude of the voltage transfer function is maintained as low as 0.1 over the frequency range from DC to the self-resonant frequency of the decoupling capacitor induced by the RLC series circuit (heretofore called the *break frequency*).

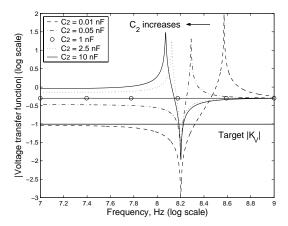

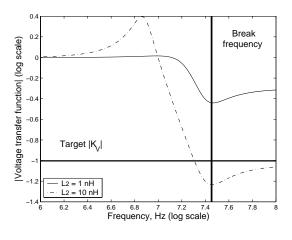

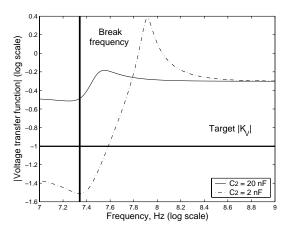

The inductance of the decoupling capacitor has an opposite effect on the magnitude of the voltage transfer function. By increasing the ESL of a dual  $V_{dd}$  power distribution system, the magnitude of the voltage transfer function can be maintained below 0.1 from the self-resonant frequency (or break frequency) of the decoupling capacitor to the maximum operating frequency. From (3), for frequencies smaller than the break frequency, the magnitude of the voltage transfer function is approximately  $\frac{C_2}{C_3}$ . For frequencies greater than the break frequency, the magnitude of the voltage transfer function is approximately  $\frac{L_3}{L_2}$ . To maintain  $|K_V|$  below 0.1, it is difficult to satisfy (6), and the range of operating frequency is divided by the break frequency into two ranges. This phenomenon is illustrated in Figs. 4(a) and 4(b).

### III. CASE STUDY OF A POWER DISTRIBUTION SYSTEM

The dependence of the voltage transfer function on the parameters of a power distribution system is described in this section to quantitatively illustrate the concepts presented in Section II. An on-chip power distribution system is assumed in this example. In modern high performance ICs, the total on-chip decoupling capacitance can exceed 300 nF, occupying about 20% of the total area of an IC [8]. In this example, the on-chip decoupling capacitance is assumed to be 160 nF. The total budgeted on-chip decoupling capacitance is arbitrarily distributed among the low voltage power supply ( $C_1 = 100$  nF), high voltage power supply ( $C_3 = 40$  nF), and the capacitance placed between the two power supplies ( $C_2 = 20$  nF). The ESR and ESL of the decoupling capacitor are chosen to be 0.1 ohms and 1 nH, respectively.

In designing a power distribution system with dual power supply voltages, it is crucial to produce an overshoot-free voltage response over the range of operating frequencies. Depending on the system parameters, it can be necessary to further decouple the power supplies, requiring the magnitude of the voltage transfer function to be decreased. In this case, it is difficult to satisfy (6) and the range of operating frequencies is therefore divided into two. There are two possible scenarios: 1) the two power supplies are decoupled as much as possible from DC to the break frequency, and 2) the two power supplies are decoupled as much as possible from the break frequency to infinity.

Note that infinite frequency is constrained by the maximum operating frequency of a specific system. Also note that the ESR, ESL, and magnitude of the decoupling capacitors can be considered as design parameters. The ESR is limited by the target impedance of the power distribution network. The ESL, however, can vary significantly. The total budgeted decoupling capacitance is distributed among  $C_1$ ,  $C_2$ , and  $C_3$ . Note that  $C_2$  can range from zero (no decoupling capacitance between

the two power supplies) to  $C_2 = C_{total} - C_1 - C_3$  (the maximum available decoupling capacitance between the two power supplies), where  $C_{total}$  is the total budgeted decoupling capacitance.

(a) To maintain the voltage transfer function below 0.1 for frequencies smaller than the break frequency, both the capacitor placed between the two power supplies and the ESL of all of the decoupling capacitors should be decreased.  $R_2 = R_3 = 10 \text{ m}\Omega$ ,  $C_3 = 1 \text{ nF}$ , and  $L_2 = L_3 = 1 \text{ nH}$

(b) To decouple the power supplies in frequencies ranging from the break frequency to infinity, both the ESL of the capacitor placed between the two power supply voltages and the decoupling capacitors should be increased.  $R_2 = R_3 = 10 \text{ m}\Omega$ ,  $C_2 = C_3 = 1 \text{ nF}$ , and  $L_3 = 1 \text{ nH}$

Fig. 4. Frequency dependence of the voltage transfer function of a dual  $V_{dd}$  power distribution system. The ESR and ESL of the decoupling capacitors for each power supply are represented by  $R_2$  and  $R_3$  and  $L_2$  and  $L_3$ , respectively.

### A. Overshoot-free magnitude of voltage transfer function

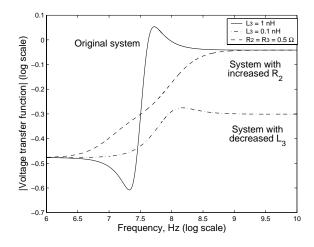

To quantitatively illustrate the criterion to produce an overshoot-free voltage response as discussed in section II, two systems with increased ESR and decreased ESL are analyzed. For typical values of an example power distribution system, (6) is not satisfied and the response of the voltage transfer function produces an overshoot as shown in Fig. 5  $(L_3 = 1 \text{ nH})$ . To produce an overshoot-free voltage response, the capacitor placed between the two power supplies should be significantly increased, permitting the ESR and ESL to be varied. Increasing the ESR of the decoupling capacitors to 0.5 ohms produces an overshoot-free response. By decreasing the ESL of  $C_3$ , the overshoot-free voltage response can be further decreased, also shown in Fig. 5 ( $L_3 = 0.1$  nH). As described in subsection II-B, at low frequency the magnitude of the voltage transfer function is approximately  $\frac{C_2}{C_3}$ . Note that all curves start from the same point. By increasing the ESR, the system becomes overdamped and produces an overshoot-free voltage response. Since the ESR does not change the  $\frac{L_3}{L_2}$  ratio, the voltage response of the overdamped system is the same as the voltage response of the initial underdamped system. Note that the dashed line and solid line converge to the same point at high frequencies, where the magnitude of the voltage transfer function is approximately  $\frac{L_3}{L_2}$ . By decreasing  $L_3$ , the total ESL of the system is lowered and the system becomes overdamped, producing an overshoot-free voltage response. Also, since the  $\frac{L_3}{L_2}$  ratio is lowered, the magnitude of the voltage response is significantly reduced at high frequencies.

Fig. 5. Dependence of the voltage transfer function of a dual  $V_{dd}$  power distribution system on frequency for different values of the ESL and ESR of the decoupling capacitors.  $R_2 = R_3 = 0.1 \Omega$ ,  $C_2 = 20 \text{ nF}$ ,  $C_3 = 40 \text{ nF}$ , and  $L_2 = L_3 = 1 \text{ nH}$ . The initial system with  $L_3 = 1 \text{ nH}$  produces an overshoot (solid line). To produce an overshoot-free voltage response, either the ESR of the system should be increased (dashed line) or the ESL should be decreased (dash-dotted line).

In general, a design methodology for producing an overshoot-free response of a power distribution system with dual power supply voltages is as follows. Based on the available decoupling capacitance for each power supply, the value of the decoupling capacitor placed between the two power supplies is determined by  $C_2 = C_{total} - C_1 - C_3$ . The ESR is chosen to be less than or equal to the target impedance to satisfy the impedance constraint. The critical ESL of the capacitors  $C_2$  and  $C_3$  is determined from (6). If the parasitic inductance of  $C_2$  and  $C_3$  is less than or equal

| Tradeoff<br>Scenario    | Power<br>Distribution<br>System                                                                                                                                                                                                                                                                                                                                                                                                   | Minimum $ K_V $      | Maximum $ K_V $      | Minimum<br>frequency | Maximum<br>frequency           |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|--------------------------------|

| I                       | Original<br>Increased $L_2$<br>Decreased $C_2$                                                                                                                                                                                                                                                                                                                                                                                    | 0.30<br>0.09<br>0.05 | 0.50<br>0.56<br>0.60 | DC<br>63 kHz<br>DC   | $\infty$<br>$\infty$<br>63 kHz |

| II                      | Original<br>Increased $L_2$<br>Decreased $C_2$                                                                                                                                                                                                                                                                                                                                                                                    | 0.20<br>0.09<br>0.03 | 0.50<br>0.50<br>0.60 | DC<br>3 MHz<br>DC    | $\infty$<br>$\infty$<br>3 MHz  |

| III                     | Original<br>Increased $L_2$<br>Decreased $C_2$                                                                                                                                                                                                                                                                                                                                                                                    | 0.20<br>0.09<br>0.05 | 0.50<br>0.50<br>0.45 | DC<br>3 GHz<br>DC    | $\infty$<br>$\infty$<br>3 GHz  |

| Scenario I<br>Board     | Original circuit: $R_2 = R_3 = 2 \mathrm{m}\Omega$ , $L_2 = L_3 = 1 \mathrm{nH}$ , $C_2 = 2 \mathrm{mF}$ , $C_3 = 4 \mathrm{mF}$<br>Increased $L_2$ : $R_2 = R_3 = 2 \mathrm{m}\Omega$ , $L_2 = 10 \mathrm{nF}$ , $L_3 = 1 \mathrm{nH}$ , $C_2 = 2 \mathrm{mF}$ , $C_3 = 4 \mathrm{mF}$<br>Decreased $C_2$ : $R_2 = R_3 = 2 \mathrm{m}\Omega$ , $L_2 = L_3 = 1 \mathrm{nH}$ , $C_2 = 200 \mu\mathrm{F}$ , $C_3 = 4 \mathrm{mF}$   |                      |                      |                      |                                |

| Scenario II<br>Package  | Original circuit: $R_2 = R_3 = 10 \text{ m}\Omega$ , $L_2 = L_3 = 100 \text{ pH}$ , $C_2 = 10 \mu\text{F}$ , $C_3 = 40 \mu\text{F}$<br>Increased $L_2$ : $R_2 = R_3 = 10 \text{ m}\Omega$ , $L_2 = 1 \text{ nH}$ , $L_3 = 100 \text{ pH}$ , $C_2 = 10 \mu\text{F}$ , $C_3 = 40 \mu\text{F}$<br>Decreased $C_2$ : $R_2 = R_3 = 10 \text{ m}\Omega$ , $L_2 = L_3 = 100 \text{ pH}$ , $C_2 = 1 \mu\text{F}$ , $C_3 = 40 \mu\text{F}$ |                      |                      |                      |                                |

| Scenario III<br>On-chip | Original circuit: $R_2 = R_3 = 10 \text{ m}\Omega$ , $L_2 = L_3 = 100 \text{ fH}$ , $C_2 = 20 \text{ nF}$ , $C_3 = 40 \text{ nF}$<br>Increased $L_2$ : $R_2 = R_3 = 10 \text{ m}\Omega$ , $L_2 = 1 \text{ pH}$ , $L_3 = 100 \text{ fH}$ , $C_2 = 20 \text{ nF}$ , $C_3 = 40 \text{ nF}$<br>Decreased $C_2$ : $R_2 = R_3 = 10 \text{ m}\Omega$ , $L_2 = L_3 = 100 \text{ fH}$ , $C_2 = 2 \text{ nF}$ , $C_3 = 40 \text{ nF}$       |                      |                      |                      |                                |

TABLE I TRADEOFF BETWEEN THE MAGNITUDE AND FREQUENCY RANGE OF THE VOLTAGE RESPONSE

to the critical ESL, the system will produce an overshoot-free voltage response and no adjustment is required. Otherwise, the total decoupling capacitance budget should be redistributed among  $C_1$ ,  $C_2$ , and  $C_3$  until (6) is satisfied. In certain cases, the total budgeted decoupling capacitance should be increased to satisfy (6).

#### B. Tradeoff between the Magnitude and Frequency Range

If it is necessary to further decouple the power supplies, the frequency range of the overshoot-free voltage response can be traded off with the magnitude of the voltage response, as described in Section II. There are two ranges of interest. The magnitude of the voltage transfer function can be decreased over the frequency range from DC to the break frequency or from the break frequency to the highest operating frequency. For the example power distribution system, as shown in Fig. 6(a), the magnitude of the voltage transfer function is overshoot-free from the break frequency to the highest operating frequency. To further decrease the magnitude of the voltage transfer function over a specified frequency range, the ESL of the decoupling capacitor placed between the two power supply voltages should be increased and  $C_2$  should be the maximum available decoupling capacitance,  $C_2 = C_{total} - C_1 - C_3$ .

To decrease the magnitude of the voltage transfer function of a power distribution system with dual power supply voltages for frequencies less than the break frequency, the ESL of all of the decoupling capacitors and the value of  $C_2$  should be decreased, as shown in Fig. 6(b). If it is necessary to completely decouple the two power supply voltages,  $C_2$  should be minimized. This behavior can be explained as follows. The initial system produces an overshoot-free voltage response in the frequency range from DC to the highest operating frequency of the system. In order to satisfy the target  $|K_V|$  at high frequencies,  $L_2$  should be increased in order to decrease the  $\frac{L_3}{L_2}$ ratio. By increasing  $L_2$ , the magnitude of the voltage response falls below the target  $|K_V|$  in the frequency range from the break frequency to the highest operating frequency of the system. At the same time, the system becomes underdamped and produces an overshoot as shown in Fig. 6(a). Similarly, by decreasing  $C_2$ , the  $\frac{C_2}{C_3}$  ratio is lowered and the magnitude of the voltage response falls below the target  $|K_V|$  in the frequency range from DC to the break frequency. The system becomes underdamped and produces an overshoot as shown in Fig. 6(b).

Three different tradeoff scenarios similar to the case study shown in Fig. 6 are summarized in Table I. The design parameters for each scenario represent typical values of board, package, and on-chip decoupling capacitors. The original system in each scenario produces an overshoot-free voltage response over a wide range of operating frequencies from DC to the highest operating frequency of the system. By increasing the ESL of the decoupling capacitor placed between the two power supplies, the system produces an overshoot and the range of operating frequencies is divided by two. The same phenomenon takes place if the value of the decoupling capacitor placed between the two power supplies is decreased. In the first case, when the ESL is increased by an order of magnitude, the magnitude of the voltage response is lowered by more than an order of magnitude from the break frequency to infinity. When  $C_2$  is decreased by an order of magnitude, the magnitude of the voltage response is lowered by more than an order of magnitude from DC to the break frequency. Note from the table that the location of the break point depends upon the particular system parameters. The break frequency of the board system occurs at a lower frequency as compared to the break point of the package power delivery network. Similarly, the break frequency of the package power distribution system is lower than the break frequency of the on-chip system. As previously mentioned, for typical power supplies values and allowed ripple voltage,  $|K_V|$  should be less than 0.1 to decouple a noisy power supply from a quiet power supply. As listed in Table I, this requirement is satisfied for the power distribution system if  $L_2$  is increased or  $C_2$  is decreased. The magnitude of the overshoot falls rapidly with decreasing ESL of the decoupling capacitors. Due to the extremely low value of the ESL in an on-chip power network, typically several hundred femtohenrys, the magnitude of the overshoot does not exceed the maximum magnitude of the overshoot-free voltage response.

(a) To maintain the magnitude of the voltage transfer function below 0.1 for frequencies greater than the break frequency, both the ESL of the capacitor placed between the two power supplies and the decoupling capacitor should be increased.  $R_2 = R_3 = 0.1 \Omega$ ,  $C_3 = 40 \text{ nF}$ , and  $L_3 = 1 \text{ nH}$

(b) To decouple the power supplies in frequencies ranging from DC to the break frequency, both the capacitor placed between the two power supplies and the ESL of all of the decoupling capacitors should be decreased.  $R_2 = R_3 = 0.1 \Omega$ ,  $C_3 = 40 \text{ nF}$ , and  $L_3 = L_2 = 1 \text{ nH}$

Fig. 6. Magnitude of the voltage transfer function of an example dual  $V_{dd}$  power distribution system as a function of frequency. The ESR and ESL of the decoupling capacitors are represented by  $R_2$  and  $R_3$  and  $L_2$  and  $L_3$ , respectively.

Unlike the design methodology for producing an overshoot-

free response described in subsection III-A, a design methodology to trade off the magnitude of the voltage response of the power distribution system with the frequency range of an overshoot-free response is as follows. Based upon the available decoupling capacitance, the decoupling capacitances for each power supply are determined. Depending upon the target frequency range with respect to the break frequency, the ESL of the capacitor placed between the two power supplies and the decoupling capacitors should both be increased (above the break frequency). Otherwise, the capacitor placed between the two power supplies and the ESL of all of the decoupling capacitors should both be decreased (below the break frequency).

## **IV.** CONCLUSIONS

It has become common practice to use multiple on-chip power supply voltages to reduce power dissipation without degrading system speed. To maintain the impedance of a power distribution system below a specified impedance, multiple decoupling capacitors are placed at different levels of the power grid hierarchy. To maintain an overshoot-free voltage response over an applicable frequency range, the total ESR of the decoupling capacitors should be greater than the two characteristic impedances of the system, represented by (6). To further decouple the power supplies in frequencies ranging from DC to the break frequency, both the capacitor placed between the two power supply voltages and the ESL of all of the decoupling capacitors should be decreased. Conversely, to decouple the power supplies in frequencies ranging from the break frequency to infinity, both the ESL of the capacitor placed between the two power supply voltages and the decoupling capacitors should be increased. If it is not possible to design a power distribution system that satisfies the overshootfree voltage response criterion, the objective of maintaining  $|K_V|$  at a required level will not be satisfied. Alternatively, the frequency range of an overshoot-free voltage response can be traded off with the magnitude of the response.

#### REFERENCES

- K. Usami and M. Horowitz, "Clustered Voltage Scaling Technique for Low-Power Design," *Proceedings of the IEEE International Workshop* on Low Power Design, pp. 3–8, April 1995.

- [2] J.-M. Chang and M. Pedram, "Energy Minimization Using Multiple Supply Voltages," *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, Vol. 5, No. 4, pp. 425–435, December 1997.

- [3] S. Raje and M. Sarrafzadeh, "Variable Voltage Scheduling," Proceedings of the ACM International Symposium on Low Power Design, pp. 9–14, April 1995.

- [4] A. V. Mezhiba and E. G. Friedman, Power Distribution Networks in High Speed Integrated Circuits, Kluwer Academic Publishers, 2004.

- [5] M. Popovich and E. G. Friedman, "Decoupling Capacitors for Power Distribution Systems with Multiple Power Supply Voltages," *Proceedings of the IEEE SOC Conference*, pp. 331–334, September 2004.

- [6] M. Popovich and E. G. Friedman, "Impedance Characteristics of Decoupling Capacitors in Multi-Power Distribution Systems," *Proceedings of the IEEE International Conference on Electronics, Circuits and Systems*, December 2004.

- [7] C. R. Paul, Analysis of Linear Circuits, McGraw-Hill, 1989.

- [8] M. K. Gowan, L. L. Biro, and D. B. Jackson, "Power Considerations in the Design of the Alpha 21264 Microprocessor," *Proceedings of the* ACM/IEEE Design Automation Conference, pp. 726–731, June 1998.