# On-Chip Resonance in Nanoscale Integrated Circuits

By

Jonathan Rosenfeld

Submitted in Partial Fulfillment

of the

Requirements for the Degree

Doctor of Philosophy

Supervised by

Professor Eby G. Friedman

Department of Electrical and Computer Engineering

Arts, Sciences, and Engineering

School of Engineering and Applied Sciences

University of Rochester

Rochester, New York

2009

*“In this short life

That only lasts an hour,

How much, how little,

Is within our power!”*

*Emily Dickinson*

# Curriculum Vitae

Jonathan Rosenfeld was born in Simferopol, Ukraine in 1973. He grew up in Israel, served in the Israeli Defense Force - IDF, and received a bachelor degree in mechanical engineering in 1999 from the Technion - Israel Institute of Technology, Department of Mechanical Engineering.

He worked as a process development engineer, conducting research on electro-chemical polishing methods at HAM-LET. He then joined CAMTEK, where he provided world-wide customer support services for the company's automated optical inspection (AOI) systems used by the semiconductor manufacturing and packaging, IC substrate, and printed circuit board (PCB) industries.

He obtained a second bachelor degree, this time in electrical engineering, from Ort Braude College, Department of Electrical Engineering in 2003, graduating with honors. In 2003, Jonathan Rosenfeld began his Ph.D. studies at the University of Rochester, Department of Electrical and Computer Engineering, under the supervision of Professor Eby G. Friedman. In 2005, Jonathan obtained his Masters degree in Electrical and Computer Engineering.

Jonathan Rosenfeld was an intern at Intrinsix Corporation, Fairport, NY, in 2005, where he designed Gm-C circuits for an  $\Sigma\Delta$ -modulator ADC for an FM tuner. In 2007, he was an intern at the Eastman Kodak Company, Rochester, NY, where he developed a column-based multiple ramp integrated ADC for CMOS image sensors. His primary research interests are in the areas of interconnect design, resonant clock and data distribution networks, on-chip DC-DC converters, and the design of analog and mixed-signal integrated circuits.

## Acknowledgments

It is quite difficult to express gratitude to all of the individuals who have affected my life since my day of birth until the moment these lines are written. I truly believe that all of these people have shaped my personality, contributing to my achievements. Naturally, my parents had the greatest impact on my early life and education and the pursuit for excellence. I would like to thank them dearly for their encouragement, patience, understanding, and support throughout these past years and the many years to come.

Undoubtedly, my dearest wife Merav and our lovely and joyful son, Blaze Barak, have impacted my life during the recent intense years of my PhD studies. The support, happiness, and enjoyment they provide me every day is priceless. The years I spent pursuing my PhD degree would not be the same without them. Thank you so much my little dearests.

Obtaining a PhD degree could not be realized without Professor Eby G. Friedman. I was extremely lucky to be embraced by one of the leading researchers in the country in the area of VLSI circuits. Professor Friedman gave me the unique opportunity to bring my creativity and scientific enthusiasm to higher levels. The exceptional way Professor Friedman manages his PhD program allowed me to thrive and brought out the best from me. His ability to foresee future and challenging areas of potential research resulted in this PhD thesis as many others before. I learned so much from his remarkable verbal and writing presentation skills, realizing how important it is to deliver your ideas in a clear, consistent, and accurate way. His attention to my academic and personal requests is highly appreciated. Thank you so much for being my mentor!

Spending my days in Professor Friedman's lab would not have been the same without his assistant, Ms. RuthAnn Williams. Ms. Williams was always there for me (as she was for the other students), providing me help and advice on many issues. Her bubbly personality and happiness of life is one of a kind and unmatched in any person I know. I would like to thank her for years of support and, of course, for her delicious lasagna. Many thanks Ruthie (and thank you for the cookbooks you gave me).

I would like to thank Professor Yaakov Bar-Shlomo and Dr. Pinchas Schechner from the Ort-Braude College in Israel, who chose me to pioneer an internship program that Professor Friedman established with the College. Their confidence in my abilities brought me to this moment.

I would also like to thank Dr. Mücahit Kozak, who supervised me during my internship in Professor Friedman's lab. His encouragement, positive spirit, and technical knowledge helped me to develop a basic understanding of analog integrated circuit design. This precious knowledge has helped me tremendously during my PhD studies. His positive approach to life inspired me throughout my PhD studies. Thank you Mujo.

I would like to thank Professors Jacob Jorne, Hui Wu, and Zeljko Ignjatovic for serving on my proposal and PhD committees. Their suggestions, comments, and valuable time are highly appreciated.

Last but certainly not least, I would like to thank my PhD colleges: Dr. Guoqing Chen, Dr. Mikhail Popovich, Dr. Vasilis Pavlidis, Emre Salman, Renatas Jakushokas, Ioannis Savidis, and Salçuk Köse. I learned new things from all of you. The technical and personal discussions I had with each of you definitely enriched my PhD experience. Dear gentlemen, thank you for your attention.

# Abstract

Relentless scaling of integrated circuits has resulted in significant performance improvements. Although active devices mostly benefit from scaling, passive interconnect networks have degraded in performance with scaling. Interconnect parasitic effects therefore must be considered throughout the design process. Furthermore, novel and innovative design methodologies for interconnect networks are required to maintain high performance in these highly complex integrated circuits.

The focus of this thesis is on three important interconnect networks: clock, data, and power generation and distribution networks. Design and analysis methodologies to improve the performance of these networks have been developed. Specifically, the following three topics have been addressed in this thesis.

Exploiting resonance for distributing high frequency clock signals is a promising technology to reduce power dissipation, clock skew, and jitter. A comprehensive methodology for designing these resonant networks has been developed. A case study of a 5 GHz clock signal within a resonant H-tree network has been demonstrated in a 180 nm CMOS technology, resulting in a substantial 84% reduction in power consumption as compared to a traditional H-tree network.

On-chip resonance has also been used to design a novel data distribution network. By eliminating the need for traditional buffer insertion, a significant reduction in power and latency has been observed. A methodology for designing these networks has been developed. A case study of a 5 Gbps data signal distributed within a 5 mm long interconnect has been

demonstrated, exhibiting 90% and 40% improvements in power consumption and latency, respectively, as compared to repeater insertion and several different exotic techniques.

A distributed rectifier for a buck converter implemented in three-dimensional (3-D) technology has also been developed. The proposed rectifier eliminates the need for a traditional *LC* filter, enabling the on-chip integration of DC-DC converters. A test circuit of the distributed rectifier has been designed for manufacture in the MIT Lincoln Laboratories 150 nm CMOS technology. Additionally, an on-chip hybrid buck converter based on switching and linear DC-DC converters has been developed, demonstrating superior efficiency and conversion range as compared to conventional buck converters.

The development of these novel design methodologies will compensate for the detrimental effects of scaling on interconnect networks. High performance operation of highly complex integrated circuits has been demonstrated to be feasible. A combination of novel design methodologies, materials, and integration technologies, is required for future nanometer integrated circuits.

# Contents

|                                                                        |             |

|------------------------------------------------------------------------|-------------|

| <b>Curriculum Vitae .....</b>                                          | <b>iii</b>  |

| <b>Acknowledgments .....</b>                                           | <b>iv</b>   |

| <b>Abstract</b>                                                        | <b>vi</b>   |

| <b>Contents</b>                                                        | <b>viii</b> |

| <b>List of Tables .....</b>                                            | <b>xiv</b>  |

| <b>List of Figures.....</b>                                            | <b>xvi</b>  |

| <b>Chapter 1 Introduction .....</b>                                    | <b>1</b>    |

| 1.1    Where Are We Heading? Trends and Predictions .....              | 3           |

| 1.2    Thesis Outline .....                                            | 8           |

| <b>Chapter 2 Global Clock and Data Distribution Networks.....</b>      | <b>11</b>   |

| 2.1    Clock Networks in Synchronous Digital Integrated Circuits ..... | 11          |

| 2.2    Design Methodologies of Data Distribution Networks .....        | 16          |

| 2.2.1    Low Swing Interconnects.....                                  | 17          |

| 2.2.2    Repeater Insertion .....                                      | 18          |

| 2.2.3    Shielding .....                                               | 19          |

| 2.2.4    Differential Signaling.....                                   | 21          |

| 2.2.5    Bus Swizzling .....                                           | 23          |

| 2.2.6    Tapered Interconnects .....                                   | 23          |

|                                                                                          |                                                                           |           |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------|

| 2.3                                                                                      | Criteria for Designing Interconnects and Clock Distribution Networks..... | 25        |

| 2.3.1                                                                                    | Clock Skew .....                                                          | 25        |

| 2.3.2                                                                                    | Jitter .....                                                              | 28        |

| 2.3.3                                                                                    | Power Consumption.....                                                    | 33        |

| 2.3.4                                                                                    | Delay .....                                                               | 34        |

| 2.4                                                                                      | Summary.....                                                              | 35        |

| <b>Chapter 3 Oscillatory Clock and Signal Modulated Data Distribution Networks .....</b> |                                                                           | <b>37</b> |

| 3.1                                                                                      | Introduction to Transmission Line Theory .....                            | 37        |

| 3.2                                                                                      | Novel Global Clock Distribution Networks .....                            | 40        |

| 3.2.1                                                                                    | Coupled Standing Wave Oscillators (SWO).....                              | 41        |

| 3.2.1.1                                                                                  | Theoretical Principles and Design Guidelines .....                        | 41        |

| 3.2.1.2                                                                                  | Circuit Implementation .....                                              | 49        |

| 3.2.2                                                                                    | Rotary Traveling Wave Oscillators (RTWO) .....                            | 50        |

| 3.2.3                                                                                    | Resonant Distributed Differential Oscillators (DDO).....                  | 56        |

| 3.2.3.1                                                                                  | Theoretical Principles and Design Guidelines .....                        | 56        |

| 3.2.3.2                                                                                  | Circuit Implementation .....                                              | 59        |

| 3.2.4                                                                                    | Comparison of Clock Distribution Networks .....                           | 60        |

| 3.3                                                                                      | Novel Transmission Line Networks .....                                    | 63        |

| 3.3.1                                                                                    | Inductance Dominated Interconnects.....                                   | 63        |

| 3.3.1.1                                                                                  | Theoretical Principles .....                                              | 64        |

| 3.3.1.2                                                                                  | Circuit Implementation .....                                              | 67        |

| 3.3.2                                                                                    | Pulse Signal Interconnects .....                                          | 70        |

| 3.3.2.1                                                                                  | Pulsed Current-Mode Signaling.....                                        | 72        |

| 3.3.2.2                                                                                  | Pulsed Voltage-Mode Signaling .....                                       | 74        |

|                  |                                                                         |            |

|------------------|-------------------------------------------------------------------------|------------|

| 3.3.3            | Comparison of Data Distribution Networks .....                          | 76         |

| 3.4              | Summary.....                                                            | 76         |

| <b>Chapter 4</b> | <b>On-Chip Inductors.....</b>                                           | <b>78</b>  |

| 4.1              | Types of On-Chip Inductors .....                                        | 79         |

| 4.1.1            | Spiral (Planar) On-Chip Inductors .....                                 | 79         |

| 4.1.2            | Advanced On-Chip Inductors .....                                        | 83         |

| 4.1.3            | Active Inductors.....                                                   | 88         |

| 4.1.3.1          | Principles of Active Inductors.....                                     | 88         |

| 4.1.3.2          | Performance Comparison between Passive and Active Inductors .....       | 90         |

| 4.2              | Modeling On-Chip Spiral Inductors .....                                 | 91         |

| 4.2.1            | Loss Mechanisms in On-Chip Spiral Inductors .....                       | 91         |

| 4.2.2            | Models and Performance Metrics of Spiral Inductors .....                | 93         |

| 4.2.2.1          | Basic Model, $Q$ , and Self-Resonance of On-Chip Inductors .....        | 93         |

| 4.2.2.2          | Advanced Models of On-Chip Inductors .....                              | 96         |

| 4.3              | Design of On-Chip Inductors.....                                        | 98         |

| 4.3.1            | First Order Inductance Equations .....                                  | 98         |

| 4.3.2            | Design Practices and Tradeoffs.....                                     | 101        |

| 4.4              | Summary.....                                                            | 104        |

| <b>Chapter 5</b> | <b>Design Methodology for Global Resonant H-Tree Clock Distribution</b> |            |

|                  | <b>Networks.....</b>                                                    | <b>106</b> |

| 5.1              | Introduction .....                                                      | 107        |

| 5.2              | Background and Problem Formulation.....                                 | 108        |

| 5.3              | Design Guidelines for H-Tree Sector .....                               | 111        |

|       |                                                                          |     |

|-------|--------------------------------------------------------------------------|-----|

| 5.3.1 | H-Tree Sector Model .....                                                | 111 |

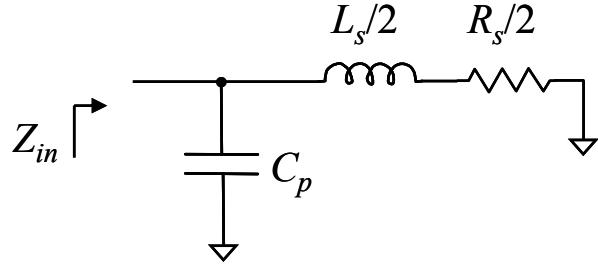

| 5.3.2 | Model of On-chip Inductor .....                                          | 114 |

| 5.3.3 | On-Chip Inductor, Capacitor, and Output Resistance of the Driving Buffer | 116 |

| 5.4   | Case Study .....                                                         | 121 |

| 5.5   | Sensitivity of H-Tree Sector .....                                       | 130 |

| 5.6   | Summary.....                                                             | 140 |

## **Chapter 6 Quasi-Resonant Interconnects: A Low Power, Low Latency Design**

|       |                                                     |            |

|-------|-----------------------------------------------------|------------|

|       | <b>Methodology .....</b>                            | <b>142</b> |

| 6.1   | Introduction .....                                  | 143        |

| 6.2   | Principle of Quasi-Resonant Interconnect .....      | 145        |

| 6.3   | Interconnect and Spiral Inductor Models.....        | 148        |

| 6.3.1 | Interconnect Model .....                            | 148        |

| 6.3.2 | On-Chip Spiral Inductor Model .....                 | 149        |

| 6.4   | Design Methodology .....                            | 150        |

| 6.4.1 | Transmitter Design.....                             | 150        |

| 6.4.2 | Receiver Design.....                                | 153        |

| 6.4.3 | Network Input Impedance and Transfer Function ..... | 156        |

| 6.4.4 | Power Consumption Model .....                       | 158        |

| 6.4.5 | Signal Delay Model .....                            | 160        |

| 6.4.6 | Design Guidelines.....                              | 161        |

| 6.5   | Case Study .....                                    | 163        |

| 6.6   | Simulation Results and Comparison.....              | 173        |

| 6.7   | Summary.....                                        | 177        |

**Chapter 7 Power Supply Generation and Distribution for Three-Dimensional ICs . 178**

|       |                                                                        |     |

|-------|------------------------------------------------------------------------|-----|

| 7.1   | Introduction .....                                                     | 178 |

| 7.2   | Background.....                                                        | 180 |

| 7.3   | Principle of a Distributed Rectifier.....                              | 184 |

| 7.4   | Design Methodology .....                                               | 188 |

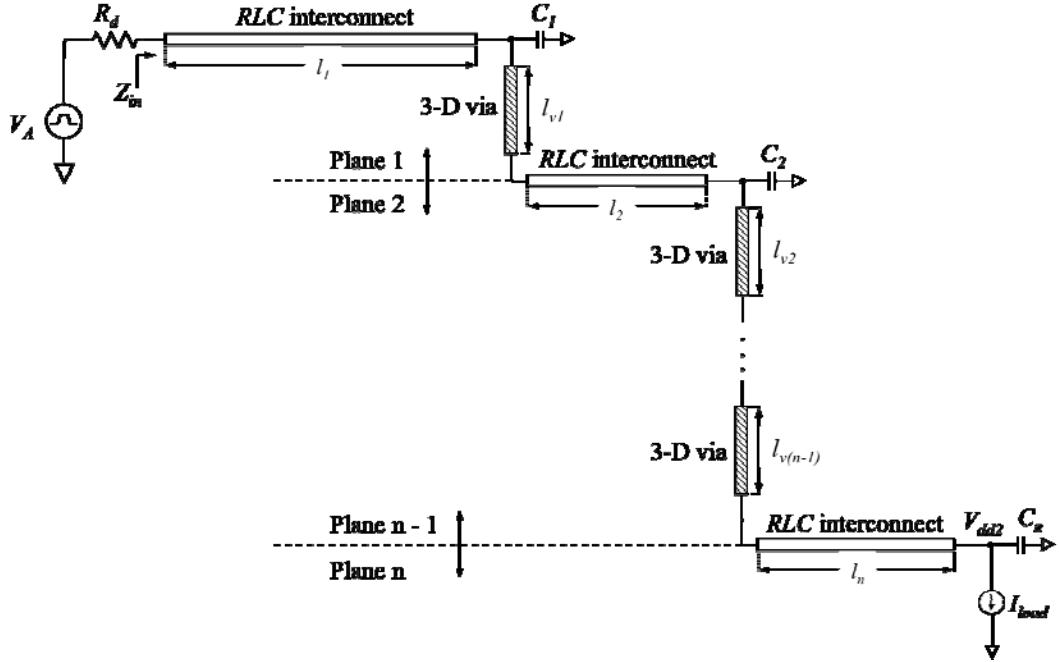

| 7.4.1 | Physical Structure and Current Load Properties of a 3-D Rectifier..... | 188 |

| 7.4.2 | Transfer Function of a 3-D Rectifier.....                              | 192 |

| 7.4.3 | Efficiency and Area of a 3-D Rectifier .....                           | 196 |

| 7.4.4 | Design Guidelines.....                                                 | 197 |

| 7.5   | Case Study .....                                                       | 202 |

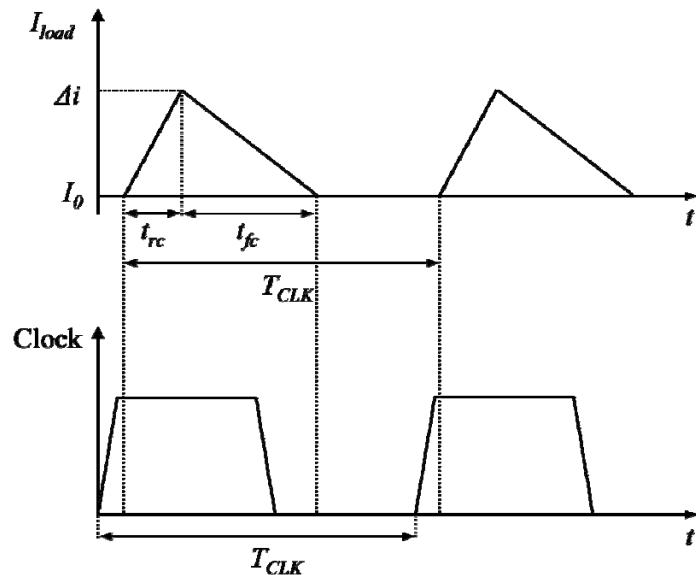

| 7.5.1 | Current Load Characterization.....                                     | 202 |

| 7.5.2 | Conventional Rectifier .....                                           | 203 |

| 7.5.3 | Distributed 3-D Rectifier .....                                        | 204 |

| 7.6   | Performance Analysis.....                                              | 207 |

| 7.7   | Conclusions .....                                                      | 211 |

**Chapter 8 3-D Distributed Rectifier Test Circuit ..... 212**

|     |                                                                      |     |

|-----|----------------------------------------------------------------------|-----|

| 8.1 | Analysis and Design of a Distributed Rectifier .....                 | 212 |

| 8.2 | Design of Current Load, Control, and Noise Measurement Circuits..... | 216 |

| 8.3 | MIT Lincoln Laboratories 3-D Fabrication Process.....                | 220 |

| 8.4 | Rectifier Layout Design.....                                         | 223 |

| 8.5 | Summary.....                                                         | 229 |

**Chapter 9 A Hybrid Methodology for Wide Range DC-DC Conversion in 3-D Circuits**

|       |     |

|-------|-----|

| ..... | 230 |

|-------|-----|

|                                                                     |                                                                          |            |

|---------------------------------------------------------------------|--------------------------------------------------------------------------|------------|

| 9.1                                                                 | Introduction .....                                                       | 230        |

| 9.2                                                                 | Background.....                                                          | 234        |

| 9.3                                                                 | Design Methodology .....                                                 | 238        |

| 9.3.1                                                               | Evaluation of Switching Converter Efficiency .....                       | 238        |

| 9.3.2                                                               | A Linear Converter in 3-D Technology .....                               | 241        |

| 9.3.3                                                               | A Switching Converter in 3-D Technology .....                            | 245        |

| 9.4                                                                 | Case Study .....                                                         | 250        |

| 9.4.1                                                               | 3.3 Volts to 2.5 Volts Conversion.....                                   | 251        |

| 9.4.2                                                               | 3.3 Volts to 1.0 Volt Conversion .....                                   | 252        |

| 9.5                                                                 | Performance Comparison .....                                             | 257        |

| 9.6                                                                 | Conclusions .....                                                        | 261        |

| <b>Chapter 10 Conclusions.....</b>                                  |                                                                          | <b>263</b> |

| <b>Chapter 11 Future Research.....</b>                              |                                                                          | <b>267</b> |

| 11.1                                                                | Spectral Analysis of Jitter in Resonant Clock Distribution Networks..... | 268        |

| 11.2                                                                | On-Chip Resonant Buck Converters.....                                    | 268        |

| 11.3                                                                | On-Chip Buck Converter Rectifier (Filter).....                           | 269        |

| 11.4                                                                | On-Chip Inductors in 3-D Circuits .....                                  | 270        |

| 11.5                                                                | Summary.....                                                             | 273        |

| <b>Bibliography .....</b>                                           |                                                                          | <b>274</b> |

| <b>Appendix A Modeling of a Resonant H-Tree Clock Network .....</b> |                                                                          | <b>295</b> |

| <b>Appendix B Modeling of a Quasi-Resonant Interconnect.....</b>    |                                                                          | <b>304</b> |

# List of Tables

|                                                                                                                                                                                              |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1 Comparison of signal distribution networks .....                                                                                                                                   | 25  |

| Table 3.1 Comparison of clock distribution networks .....                                                                                                                                    | 62  |

| Table 3.2 Comparison of data distribution networks .....                                                                                                                                     | 76  |

| Table 4.1 Coefficients for the current sheet inductance [112] .....                                                                                                                          | 100 |

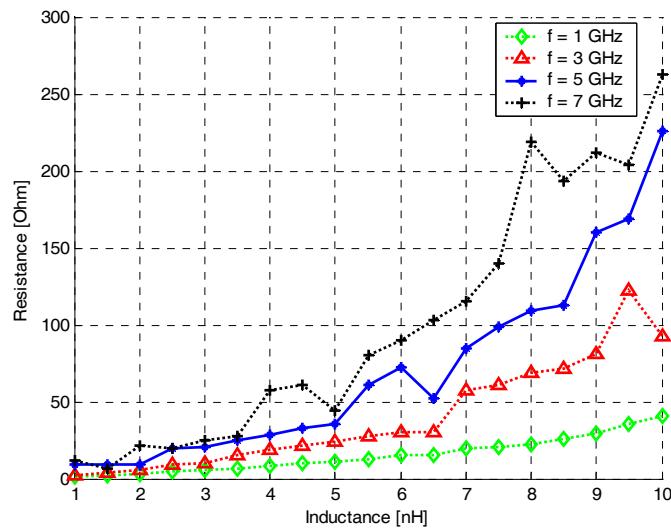

| Table 5.1 ESRs of spiral inductors at 5 GHz .....                                                                                                                                            | 116 |

| Table 5.2 Resonant H-tree parameters .....                                                                                                                                                   | 122 |

| Table 5.3 Resonant H-tree extracted transmission line parameters .....                                                                                                                       | 122 |

| Table 5.4 Buffer sizes in the non-resonant case .....                                                                                                                                        | 127 |

| Table 5.5 Sensitivity evaluation of resonant H-tree network .....                                                                                                                            | 137 |

| Table 5.6 Four cases of unbalanced inductor and capacitor variations .....                                                                                                                   | 139 |

| Table 6.1 Transistor width of the receiver and transmitter circuits, $L = 0.18 \mu\text{m}$ channel length .....                                                                             | 165 |

| Table 6.2 Simulated and analytic power consumption and delay of the receiver, transmitter, and QRN .....                                                                                     | 171 |

| Table 6.3 Comparison of QRN model with simulation: (a) power and delay using analytical model, (b) power and delay using simulation, (c) error between analytical model and simulation ..... | 174 |

| Table 6.4 Comparison of power consumption and delay .....                                                                                                                                    | 175 |

| Table 6.5 Performance comparison of quasi-resonant method with different approaches ...                                                                                                      | 176 |

| Table 6.6 Area comparison of repeaters and on-chip spiral inductors for different technologies .....                                                                                         | 177 |

|                                                                                                |     |

|------------------------------------------------------------------------------------------------|-----|

| Table 7.1 <i>RLC</i> Interconnect and 3-D via impedances .....                                 | 205 |

| Table 8.1 Electrical parameters of interconnects and 3-D vias.....                             | 214 |

| Table 9.1 Width of the transistors within the 3-D linear converter .....                       | 252 |

| Table 9.2 Performance comparison of different on-chip DC-DC converters in the literature ..... | 252 |

| .....                                                                                          | 261 |

| Table 9.3 Performance summary of the proposed 3-D hybrid converter (this work) .....           | 261 |

# List of Figures

|                                                                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 Taxonomy of digital VLSI challenges.....                                                                                                                    | 2  |

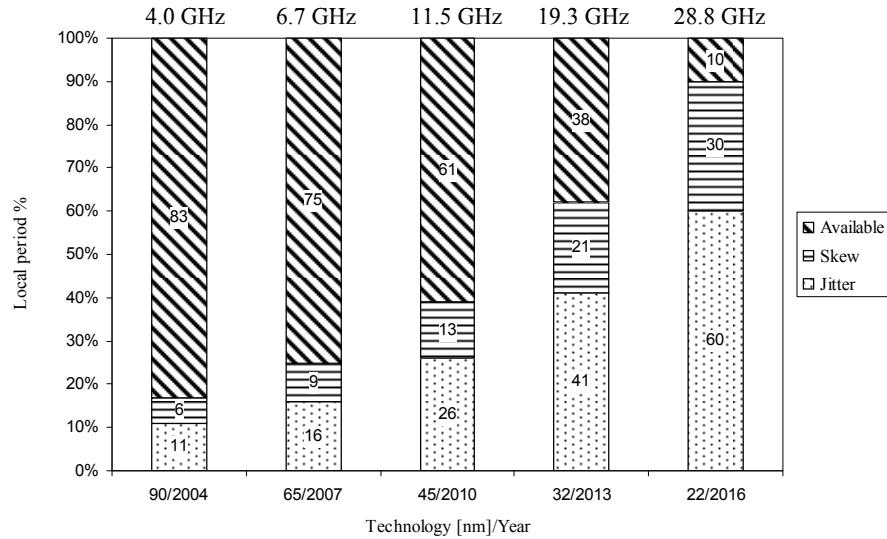

| Figure 1.2 Predictions of skew and jitter [9].....                                                                                                                     | 5  |

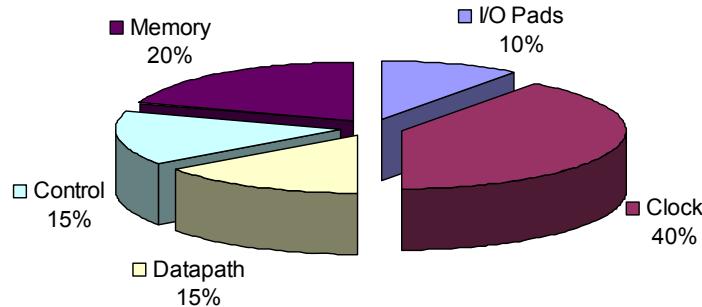

| Figure 1.3 The power budget breakdown for several microprocessors [20].....                                                                                            | 5  |

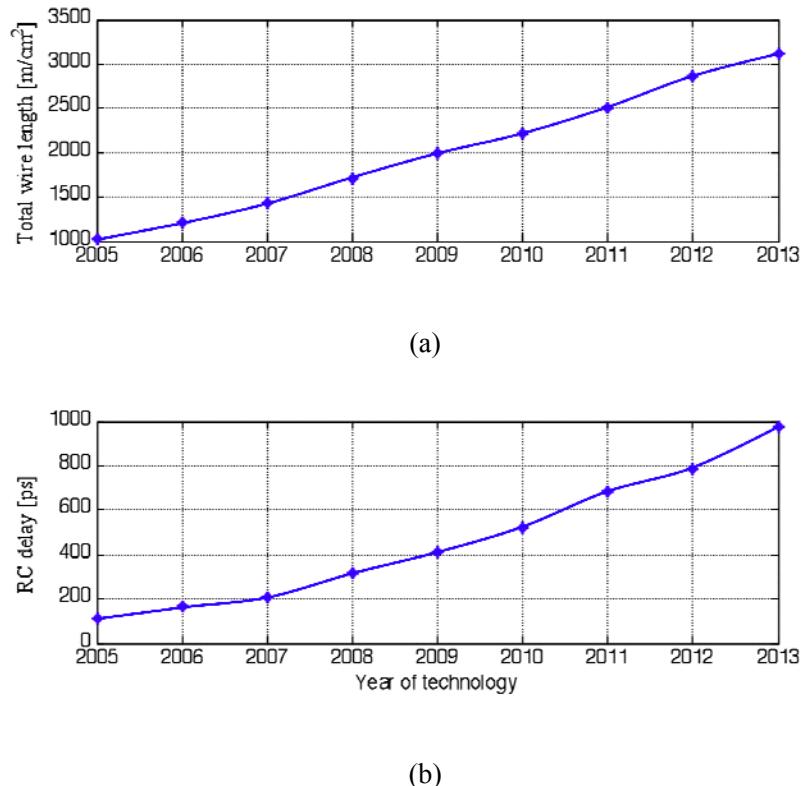

| Figure 1.4 2005 ITRS predictions: (a) total interconnect length of Metal 1 and five intermediate levels, (b) interconnect $RC$ delay for a 1 mm Cu global wire [12]... | 7  |

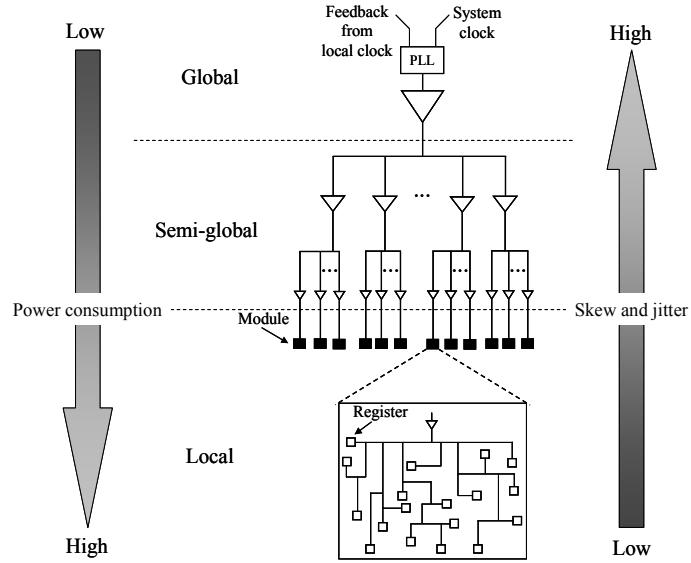

| Figure 2.1 Hierarchical topology of a clock distribution network .....                                                                                                 | 12 |

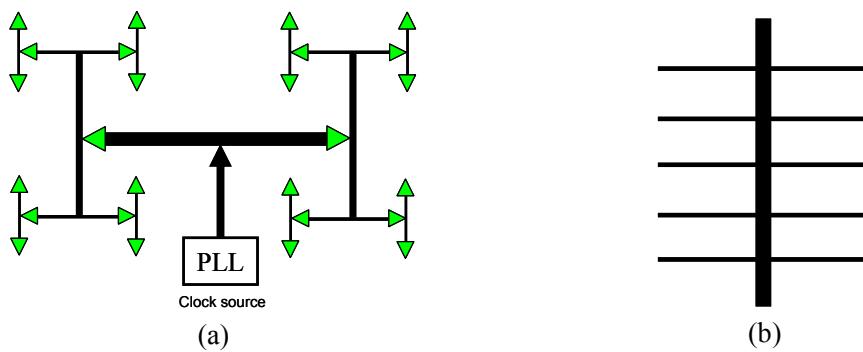

| Figure 2.2 Global level distribution networks: (a) H-tree, (b) trunk.....                                                                                              | 13 |

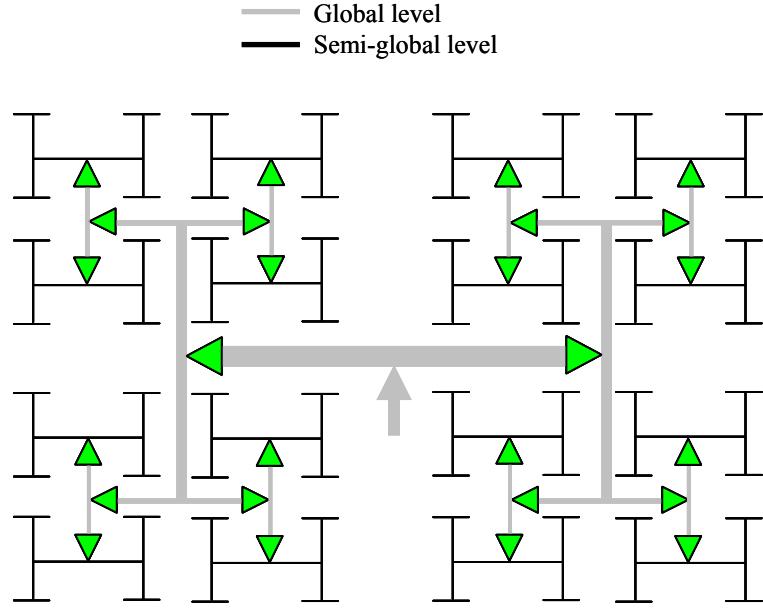

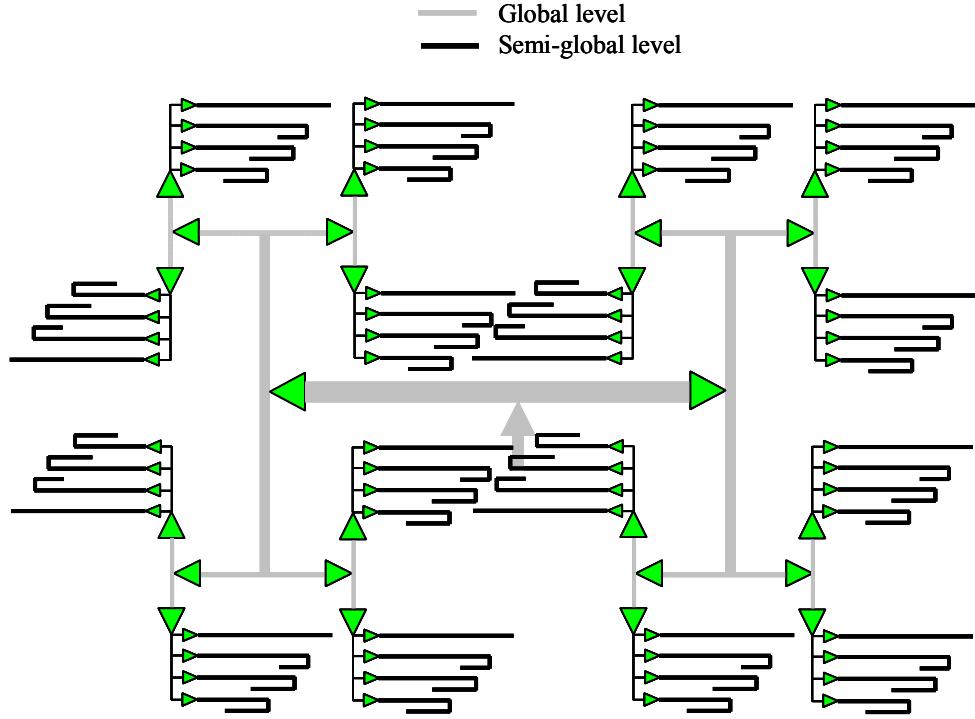

| Figure 2.3 Global and semi-global H-tree network .....                                                                                                                 | 14 |

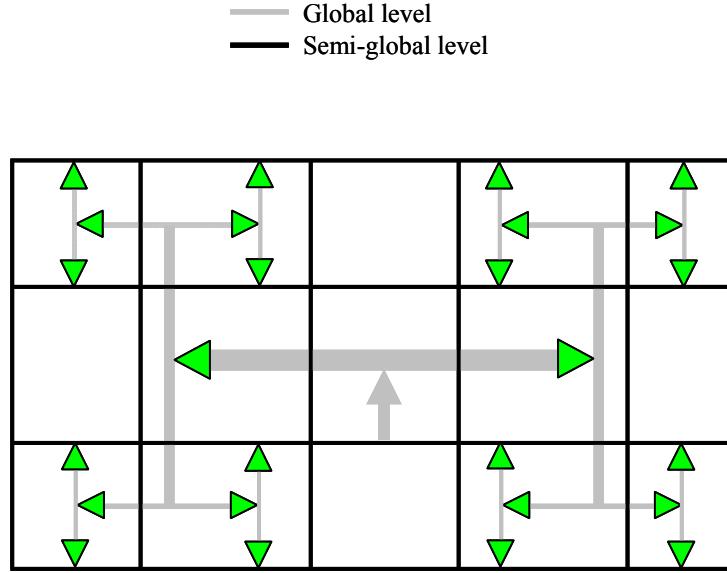

| Figure 2.4 Global H-tree and semi-global grid network .....                                                                                                            | 15 |

| Figure 2.5 Global H-tree and semi-global length matched serpentine network.....                                                                                        | 16 |

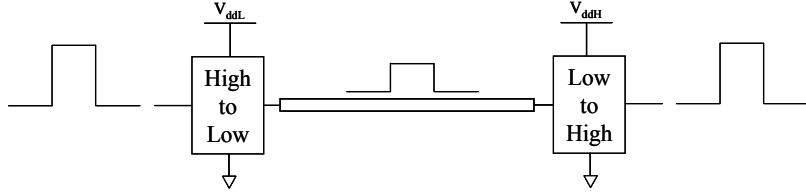

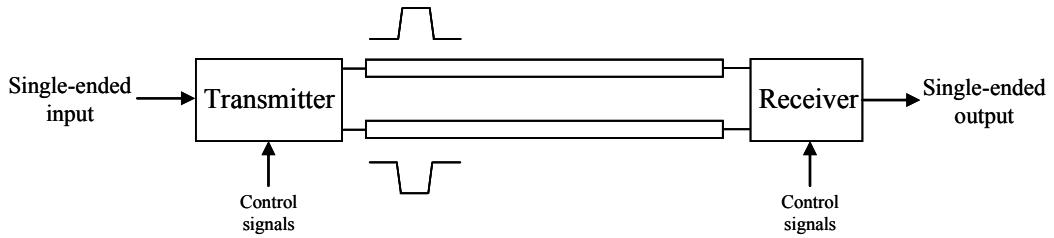

| Figure 2.6 Principle of low swing interconnects.....                                                                                                                   | 18 |

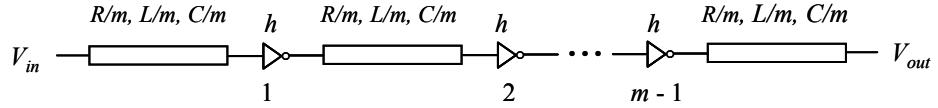

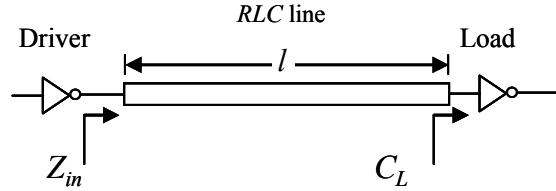

| Figure 2.7 Repeater insertion in $RLC$ interconnect.....                                                                                                               | 19 |

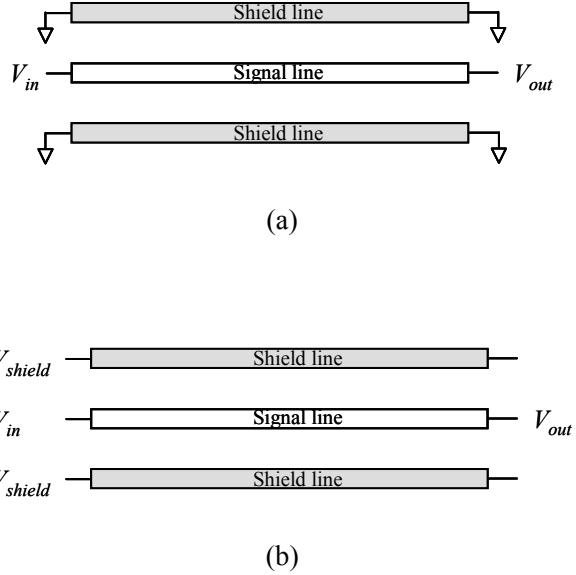

| Figure 2.8 Shielded interconnect: (a) passive shielding, (b) active shielding.....                                                                                     | 20 |

| Figure 2.9 Differential transmission network .....                                                                                                                     | 21 |

| Figure 2.10 Differential low swing interconnect .....                                                                                                                  | 22 |

| Figure 2.11 Example of bus swizzling.....                                                                                                                              | 23 |

| Figure 2.12 Example of shielded clock lines: (a) tapered interconnect, (b) uniform interconnect [68] .....                                                             | 24 |

| Figure 2.13 Local data path .....                                                                                                                                      | 26 |

| Figure 2.14 Clock timing diagrams .....                                                                                                                                | 27 |

| Figure 2.15 H-tree with eight leafs .....                                                                                                                              | 28 |

|                                                                                                                                                                  |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

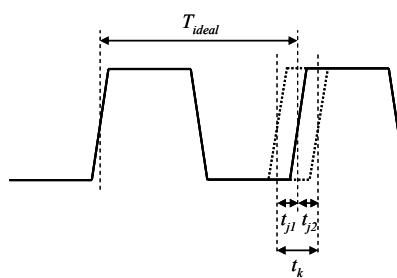

| Figure 2.16 Illustration of clock jitter .....                                                                                                                   | 29 |

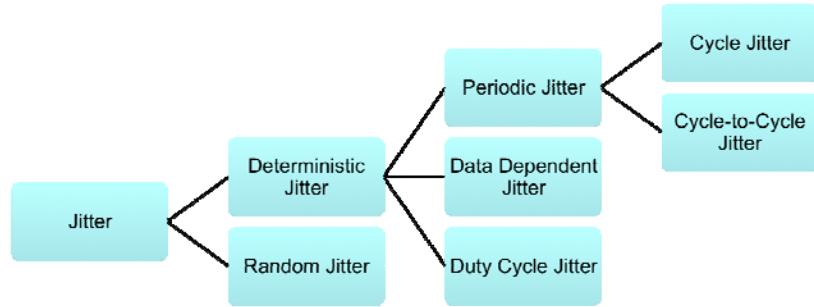

| Figure 2.17 Taxonomy of different jitter forms .....                                                                                                             | 30 |

| Figure 2.18 Cycle jitter .....                                                                                                                                   | 30 |

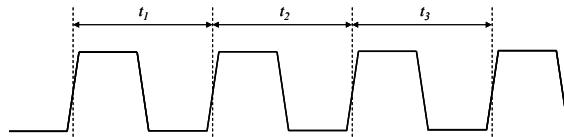

| Figure 2.19 Cycle-to-cycle jitter .....                                                                                                                          | 31 |

| Figure 2.20 Typical section of a clock and interconnect network .....                                                                                            | 33 |

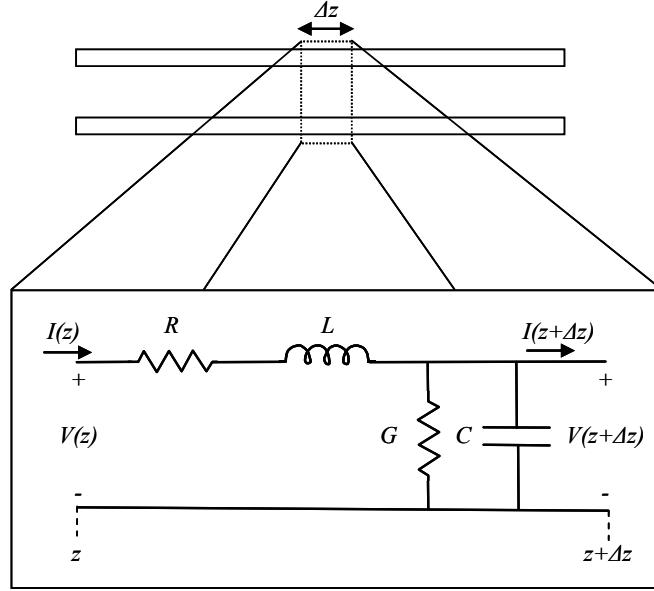

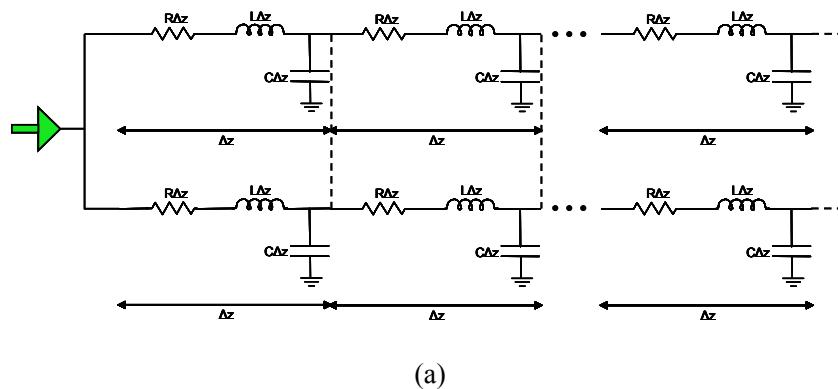

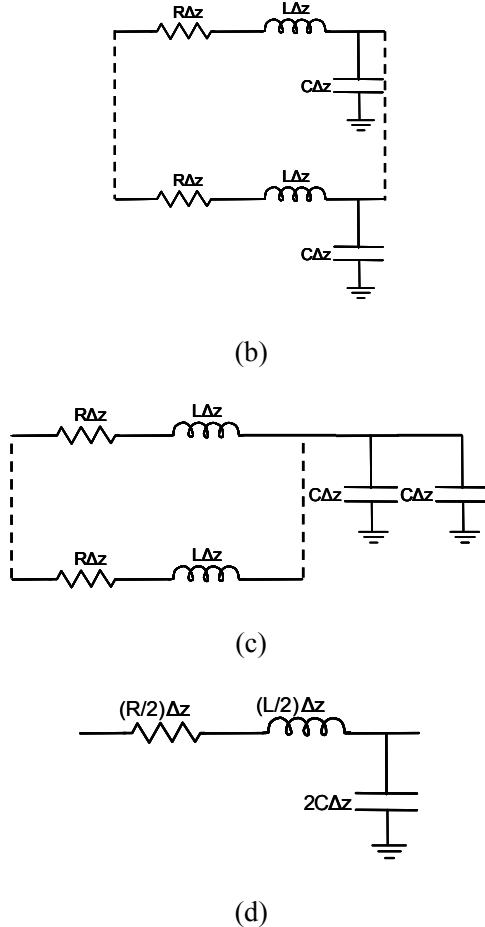

| Figure 3.1 Infinitesimal segment of a transmission line .....                                                                                                    | 38 |

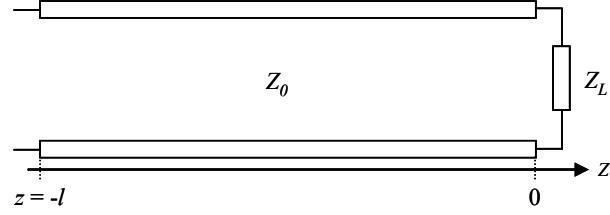

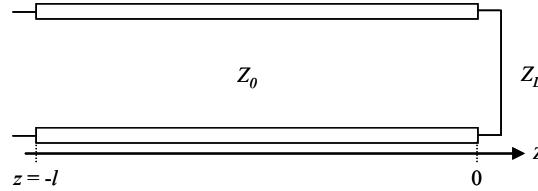

| Figure 3.2 Terminated transmission line with load $Z_L$ .....                                                                                                    | 40 |

| Figure 3.3 Transmission line terminated with a shorted load .....                                                                                                | 42 |

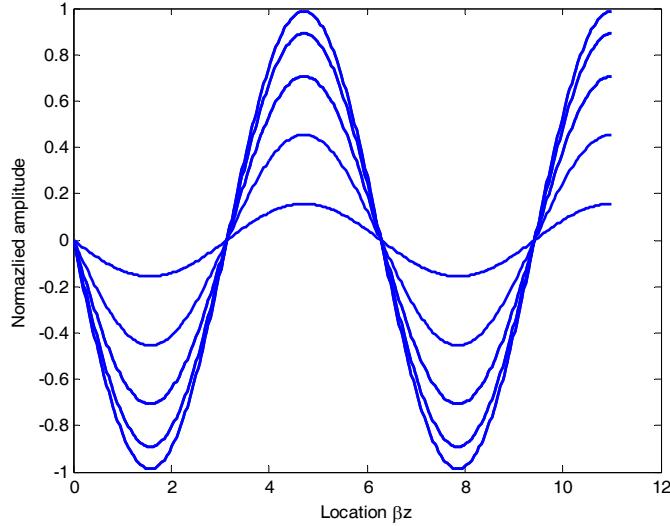

| Figure 3.4 Standing waves in a lossless transmission line .....                                                                                                  | 43 |

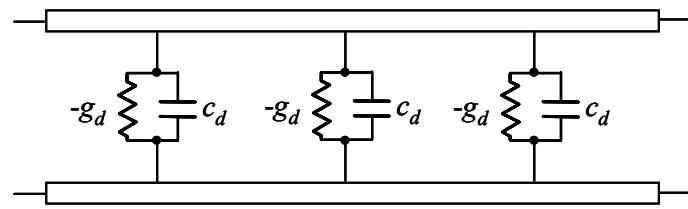

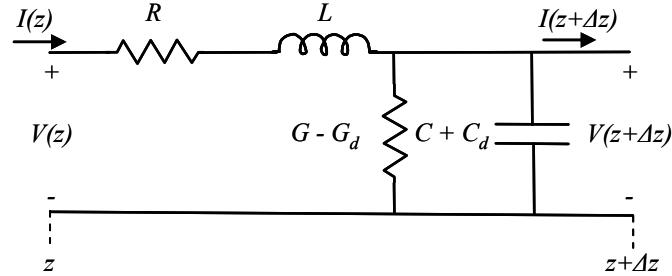

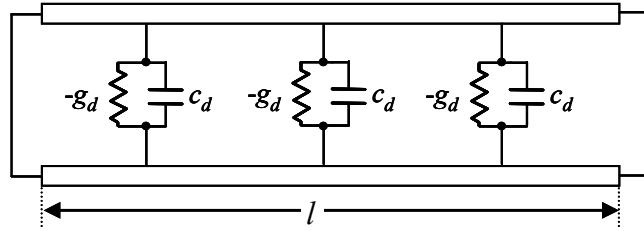

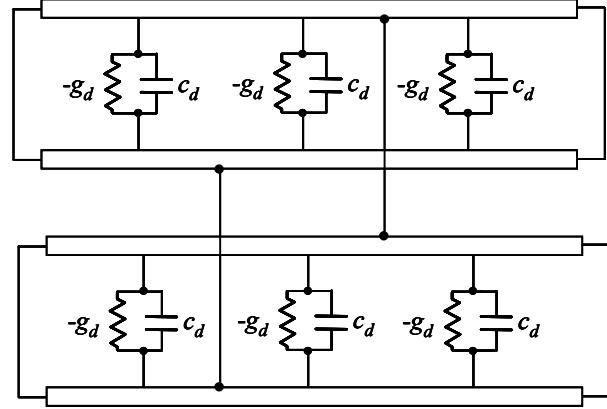

| Figure 3.5 Transmission line with distributed negative transconductance .....                                                                                    | 43 |

| Figure 3.6 Equivalent infinitesimal segment .....                                                                                                                | 44 |

| Figure 3.7 A standing wave oscillator .....                                                                                                                      | 46 |

| Figure 3.8 Two coupled SWOs .....                                                                                                                                | 47 |

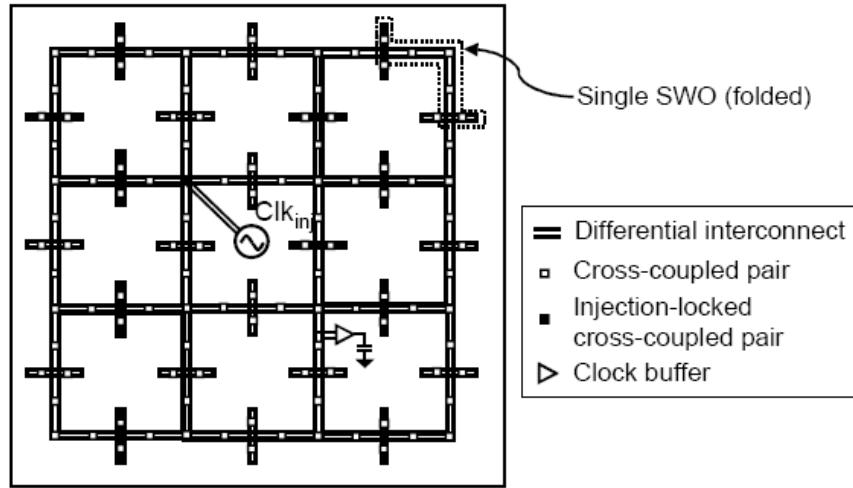

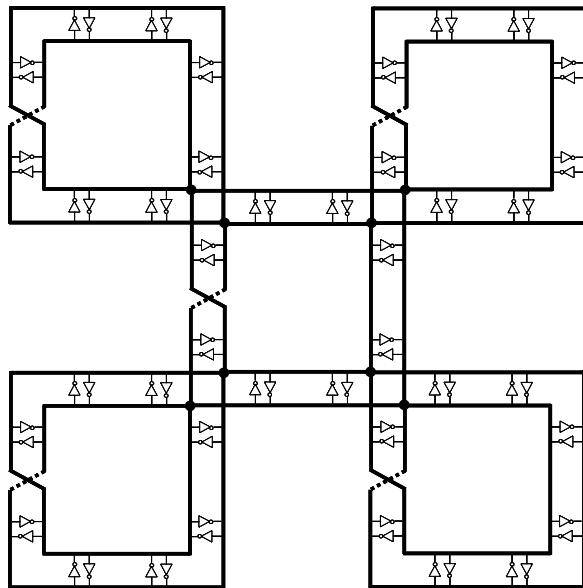

| Figure 3.9 Grid of coupled SWOs [70] .....                                                                                                                       | 48 |

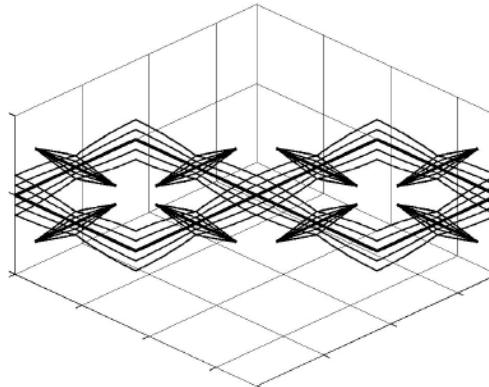

| Figure 3.10 Voltage waveforms of a SWOs grid [70] .....                                                                                                          | 48 |

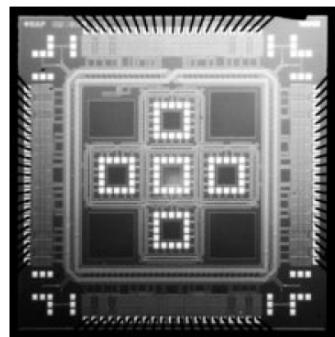

| Figure 3.11 A micrograph of a 10 GHz circuit composed of eight coupled SWOs [70] .....                                                                           | 49 |

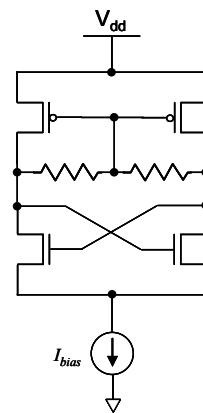

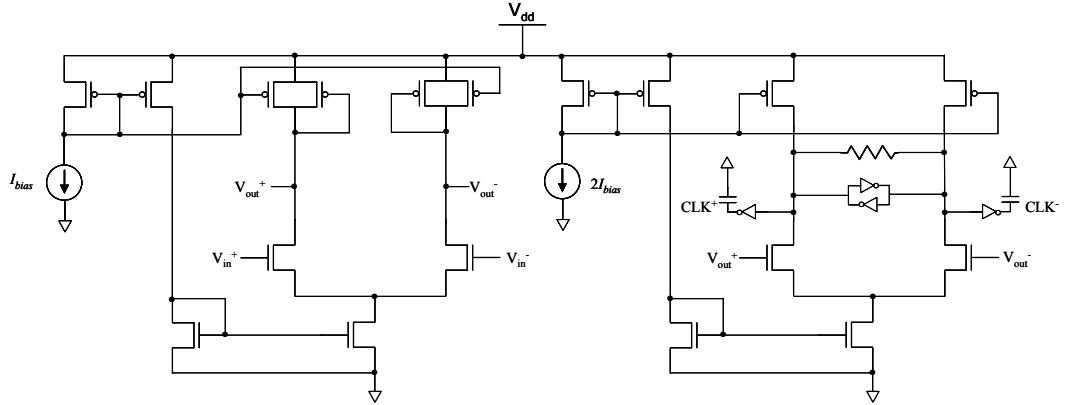

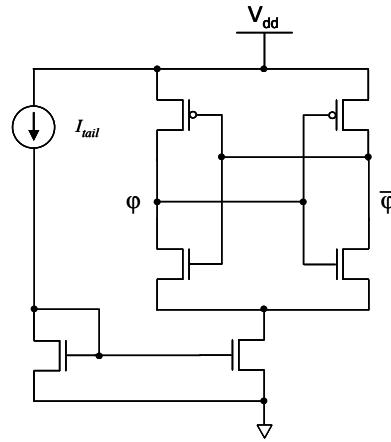

| Figure 3.12 Negative resistance circuit .....                                                                                                                    | 49 |

| Figure 3.13 Clock buffer .....                                                                                                                                   | 50 |

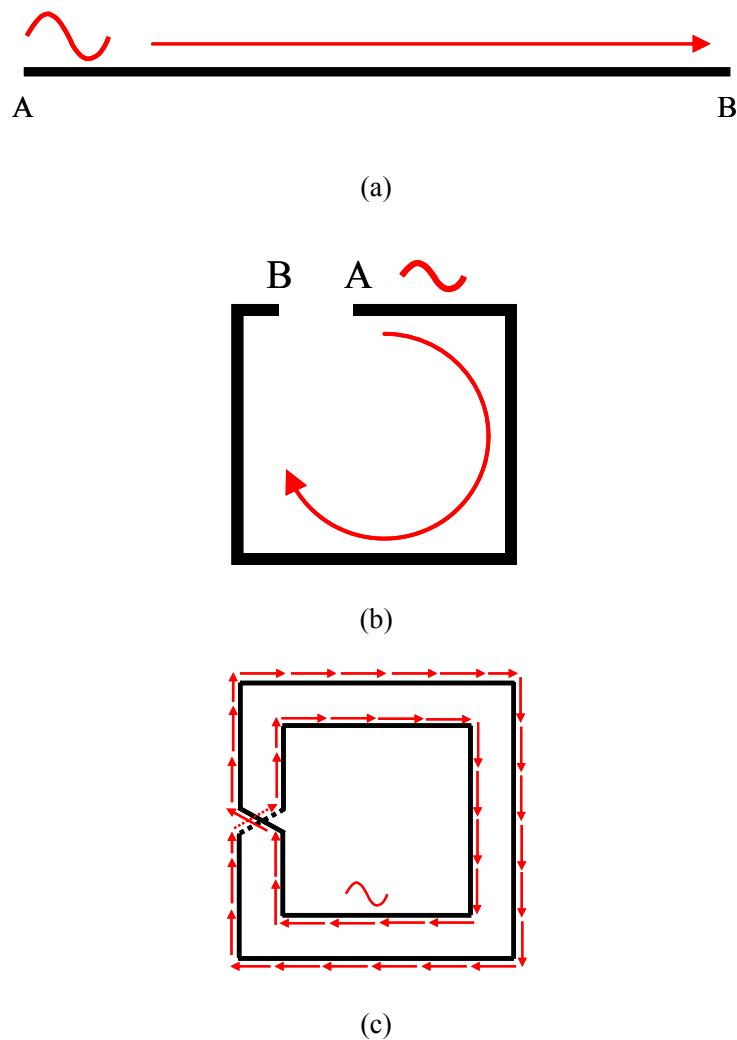

| Figure 3.14 Operation of a traveling wave loop: (a) in a transmission line, (b) in a square<br>shaped transmission line, (c) in a differential closed loop ..... | 51 |

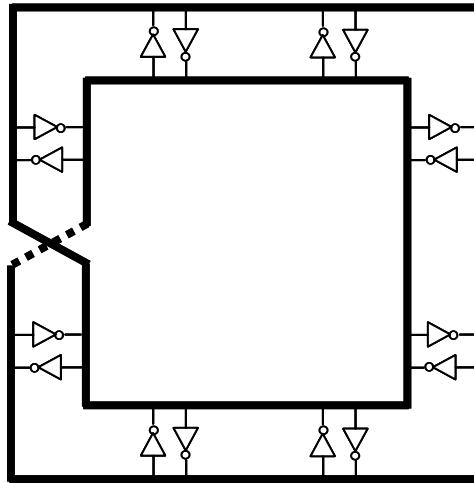

| Figure 3.15 Rotary clock ring .....                                                                                                                              | 52 |

| Figure 3.16 Section of a rotary clock ring .....                                                                                                                 | 53 |

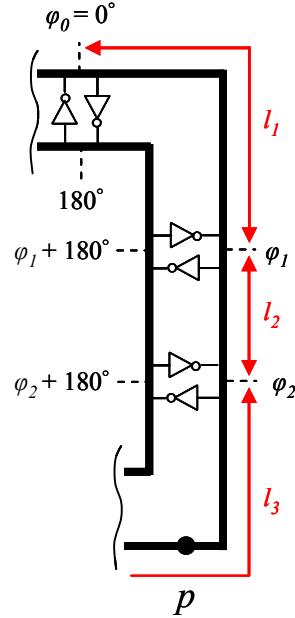

| Figure 3.17 Rotary clock distribution network .....                                                                                                              | 55 |

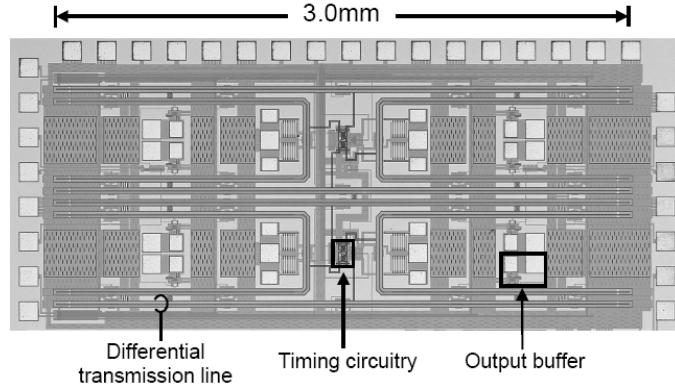

| Figure 3.18 A micrograph of a 965 MHz four coupled RTWOS [71] .....                                                                                              | 55 |

|                                                                                                                                                                                                                                                                         |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.19 Resonant differential oscillator.....                                                                                                                                                                                                                       | 57 |

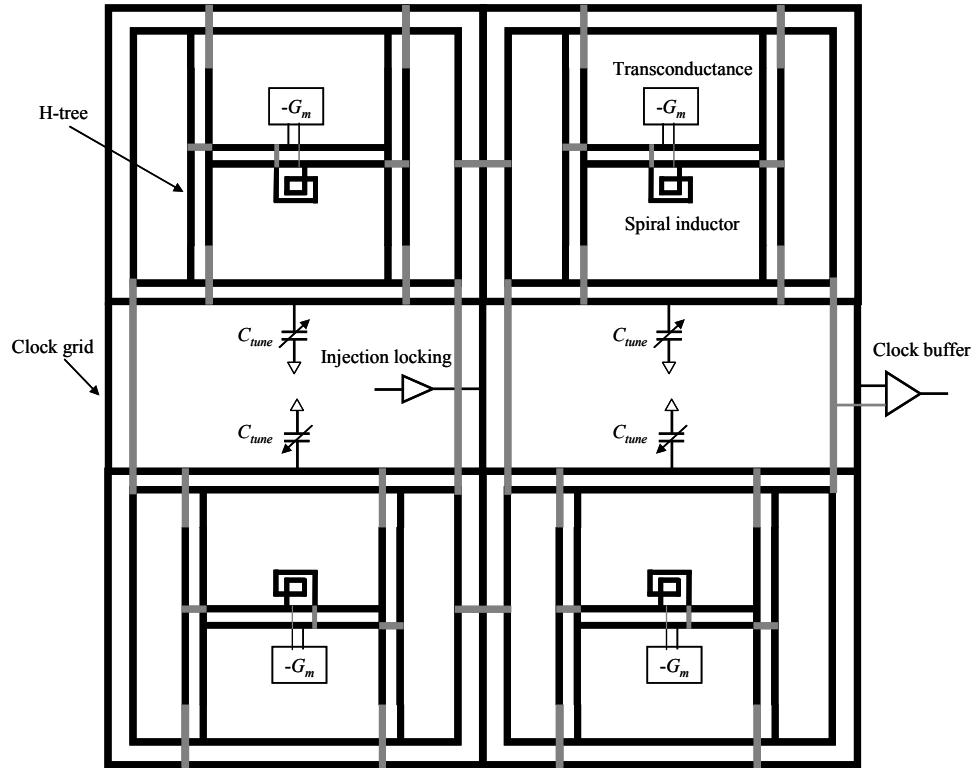

| Figure 3.20 Circuit model of the DDO .....                                                                                                                                                                                                                              | 58 |

| Figure 3.21 Transconductance circuit.....                                                                                                                                                                                                                               | 59 |

| Figure 3.22 Clock buffer.....                                                                                                                                                                                                                                           | 60 |

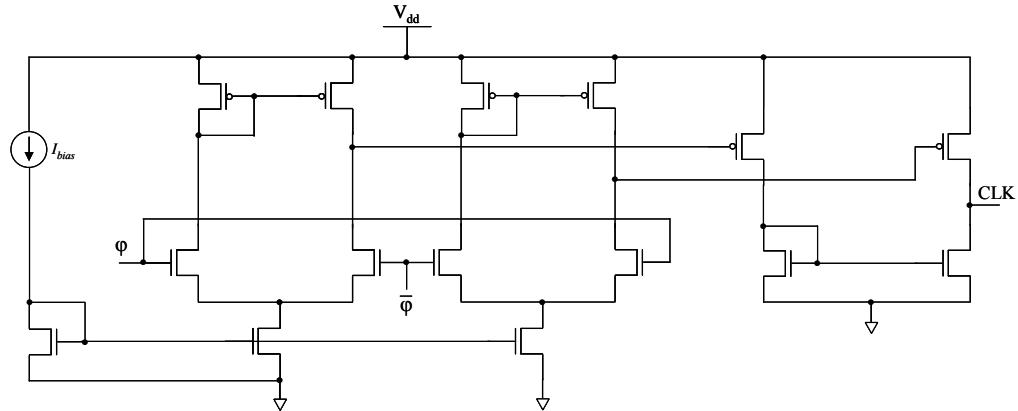

| Figure 3.23 Micrograph of a 1.1 GHz DDO with four differential on-chip inductors [74]....                                                                                                                                                                               | 60 |

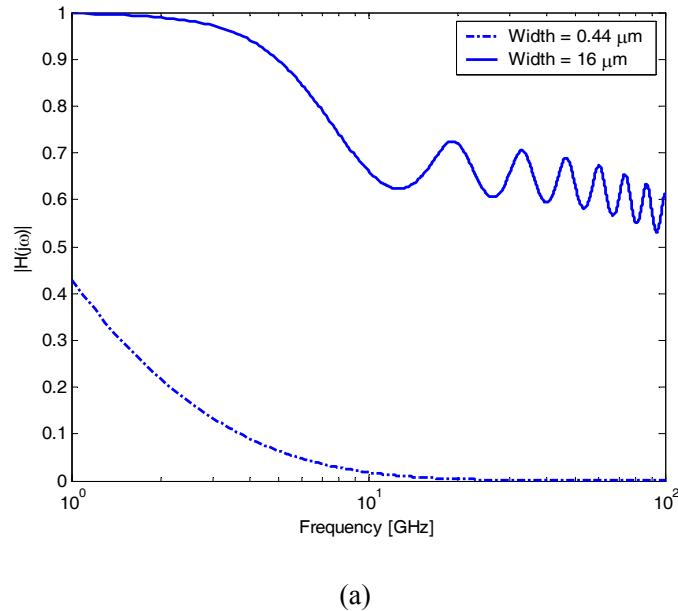

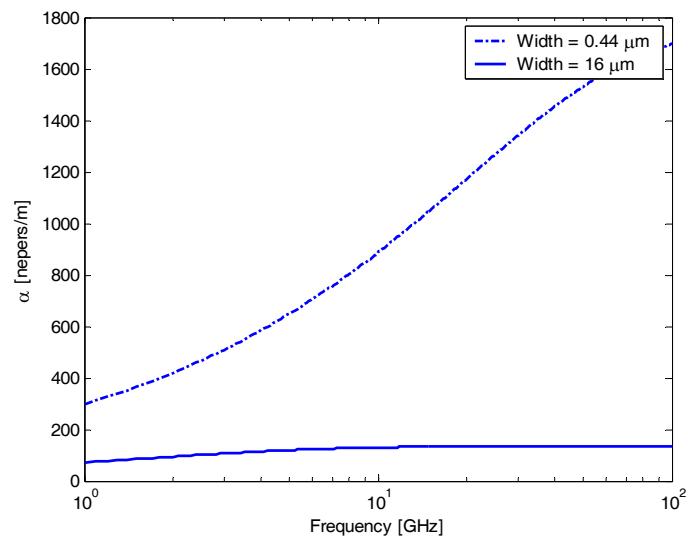

| Figure 3.24 Example of <i>LC</i> dominated interconnects: (a) transfer function, (b) attenuation coefficient, (c) phase velocity .....                                                                                                                                  | 66 |

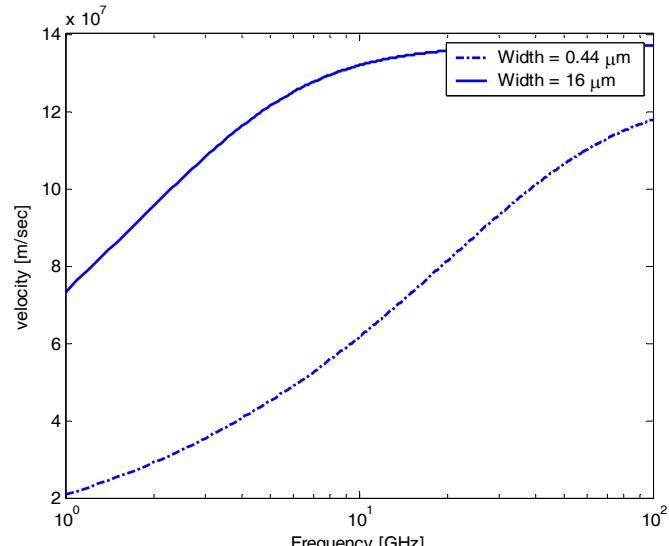

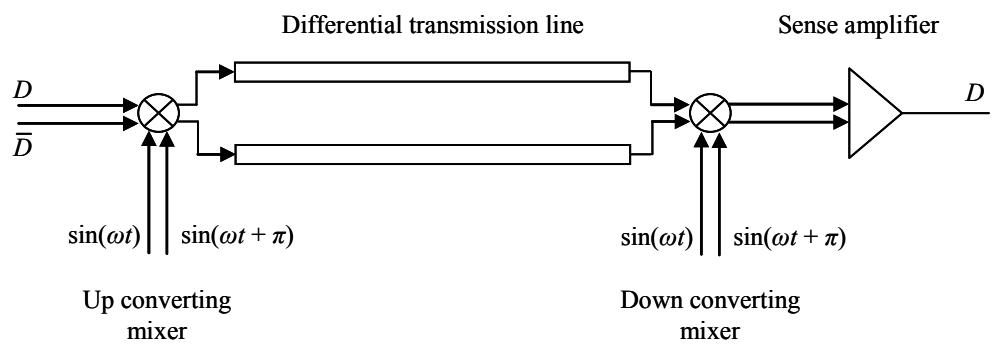

| Figure 3.25 Block diagram of the near speed of light interconnect network .....                                                                                                                                                                                         | 67 |

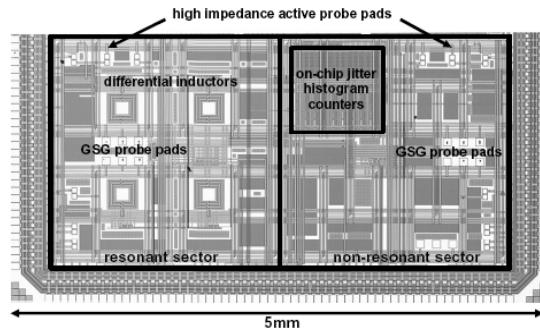

| Figure 3.26 Modulation of the transmitted signal.....                                                                                                                                                                                                                   | 68 |

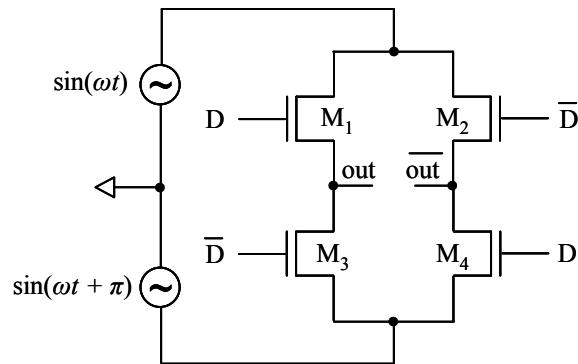

| Figure 3.27 Passive ring mixer .....                                                                                                                                                                                                                                    | 68 |

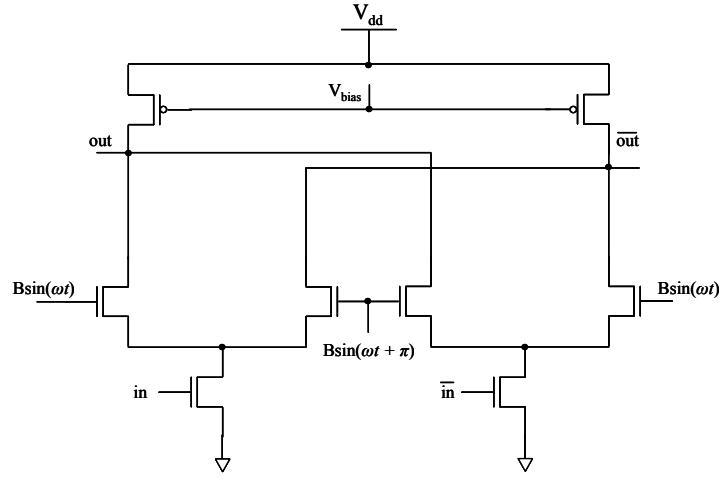

| Figure 3.28 Active double-balanced mixer.....                                                                                                                                                                                                                           | 69 |

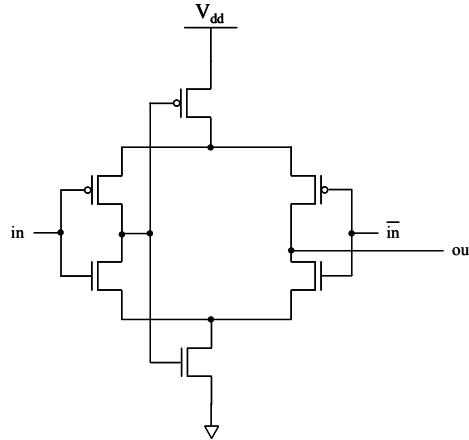

| Figure 3.29 Self biased differential amplifier .....                                                                                                                                                                                                                    | 69 |

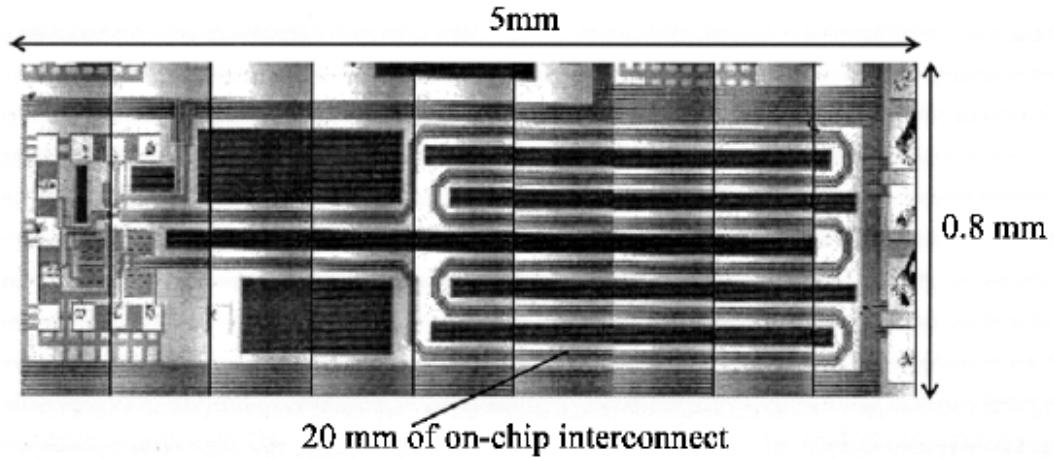

| Figure 3.30 Micrograph of a 20 mm interconnect long transmission network [81] .....                                                                                                                                                                                     | 70 |

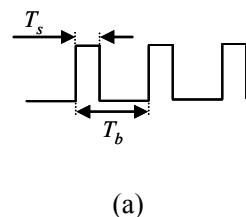

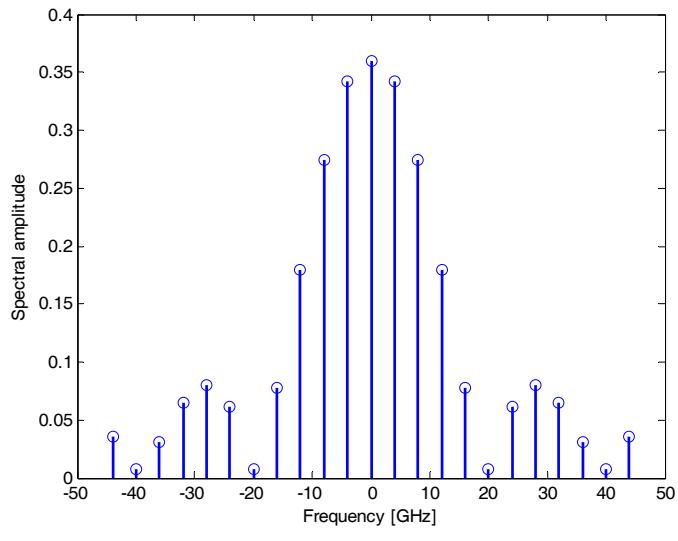

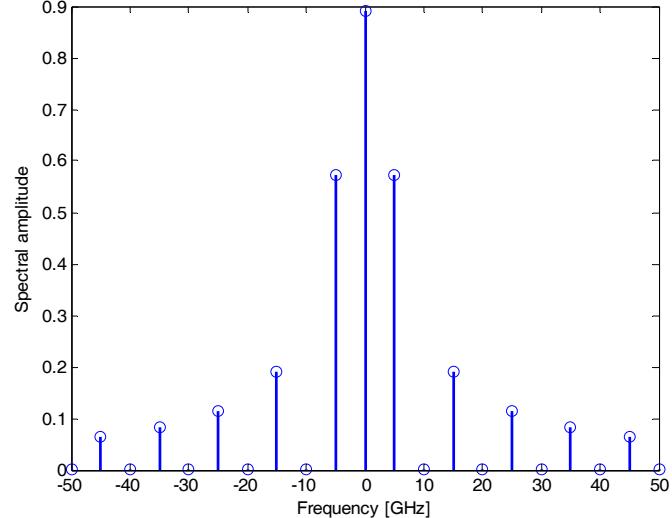

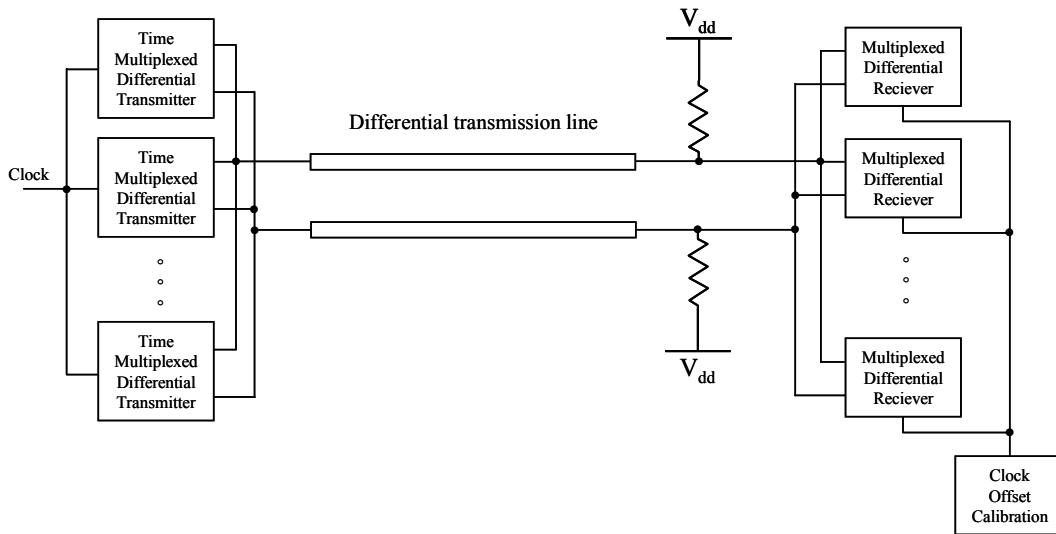

| Figure 3.31 Spectrum of a periodic pulse signal: (a) periodic pulse with width $T_s$ and a period $T_b$ , (b) spectral amplitudes of a pulse with $T_s = 50$ ps and $T_b = 250$ ps, and (c) spectral amplitudes of a pulse with $T_s = 100$ ps and $T_b = 200$ ps ..... | 71 |

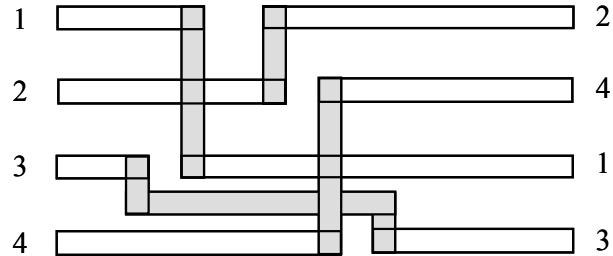

| Figure 3.32 Pulsed current interconnect network .....                                                                                                                                                                                                                   | 73 |

| Figure 3.33 Micrograph of a 3 mm pulsed current interconnect [84].....                                                                                                                                                                                                  | 73 |

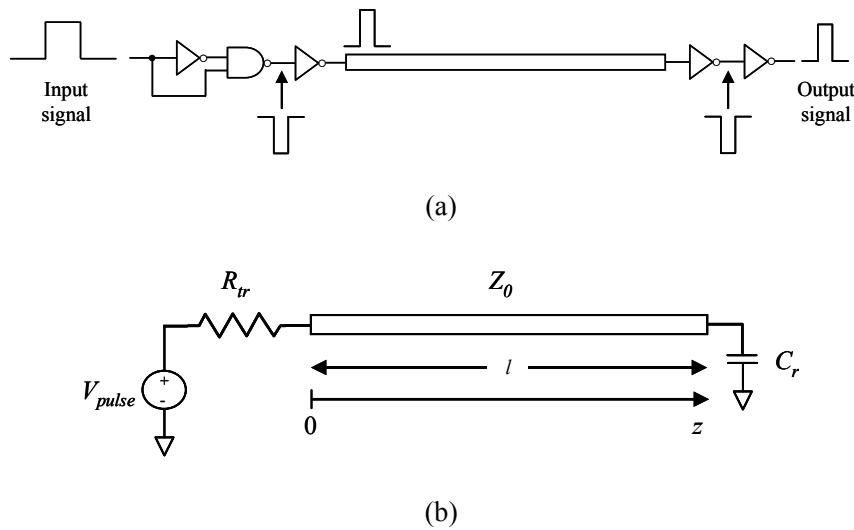

| Figure 3.34 Pulsed wave interconnect: (a) generation and transmission of a pulse signal, and (b) network model .....                                                                                                                                                    | 74 |

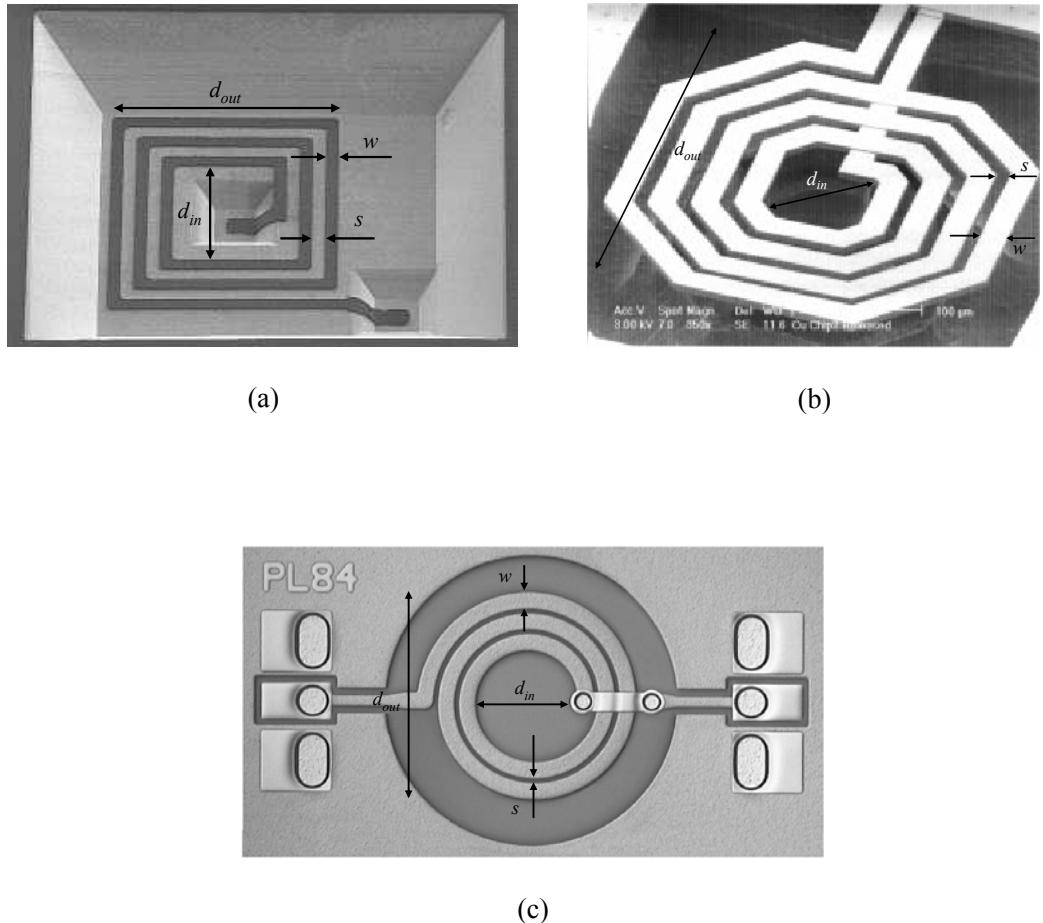

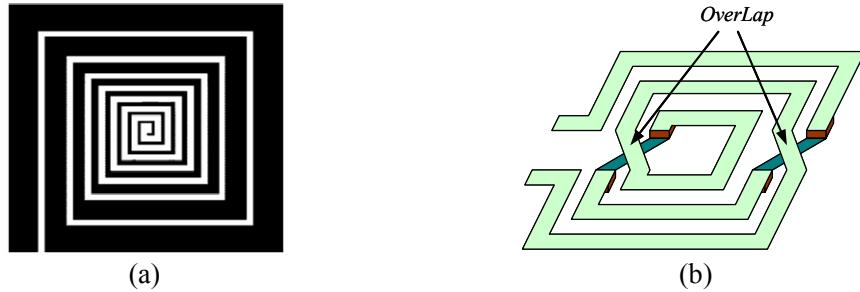

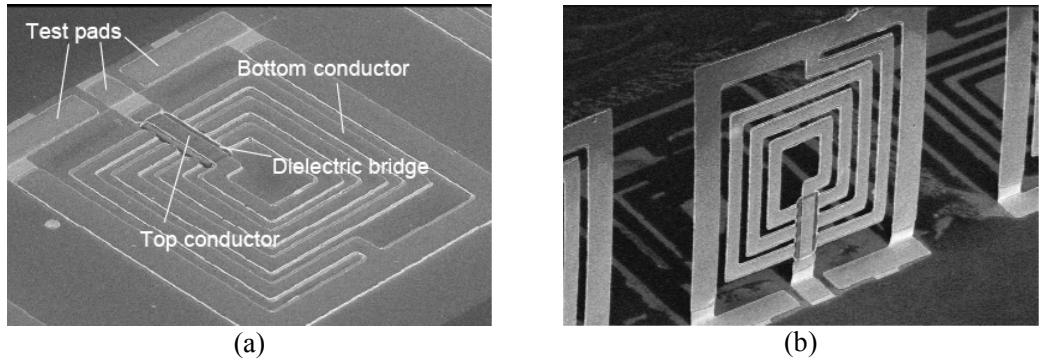

| Figure 4.1 Planar spiral inductors: (a) square inductor [89], (b) octagonal inductor [90], (c) circular inductor [91].....                                                                                                                                              | 80 |

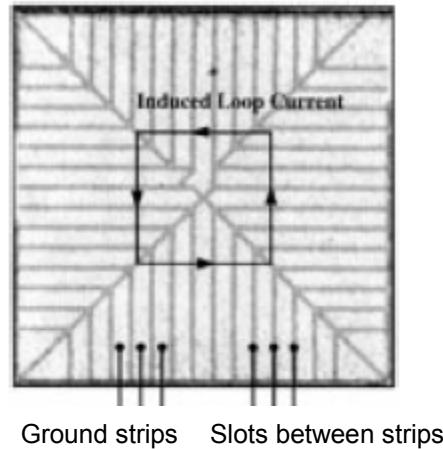

| Figure 4.2 Patterned ground shield [93] .....                                                                                                                                                                                                                           | 81 |

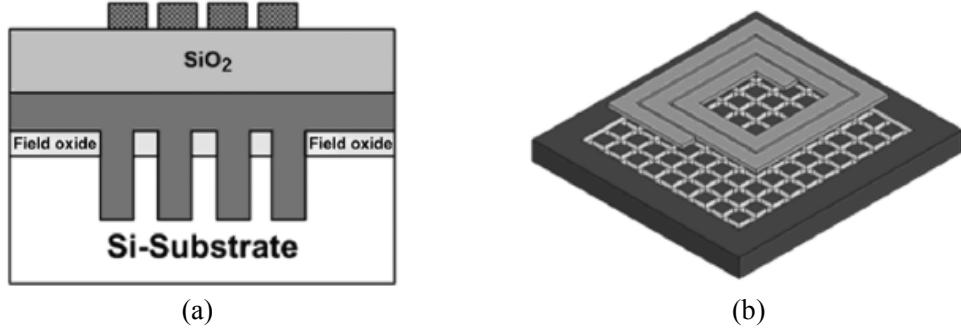

| Figure 4.3 Deep trench inductor [96]: (a) side view, (b) three dimensional view .....                                                                                                                                                                                   | 82 |

|                                                                                                                                                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.4 Reduced loss inductors [90]: (a) tapered spiral, (b) symmetric spiral .....                                                                                                                                 | 82  |

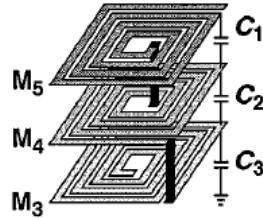

| Figure 4.5 Three layer stacked inductor [94] .....                                                                                                                                                                     | 83  |

| Figure 4.6 Suspended inductor [95]: (a) single level, (b) double level .....                                                                                                                                           | 84  |

| Figure 4.7 A toroidal inductor [97] .....                                                                                                                                                                              | 84  |

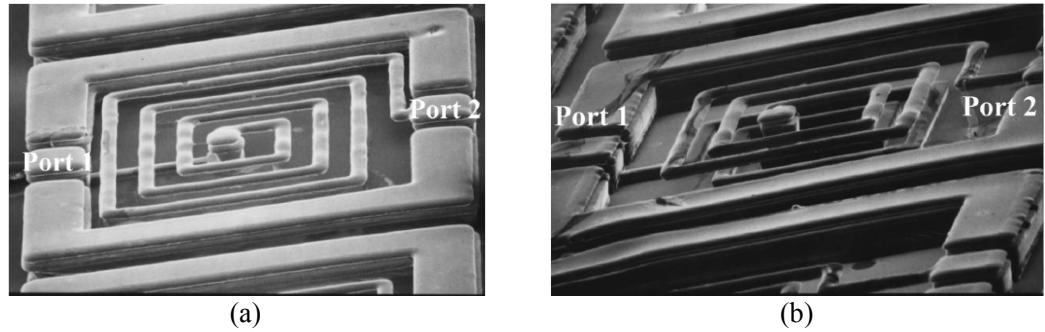

| Figure 4.8 Vertical planar inductor [98]: (a) before the PDMA process, (b) after the PDMA process .....                                                                                                                | 85  |

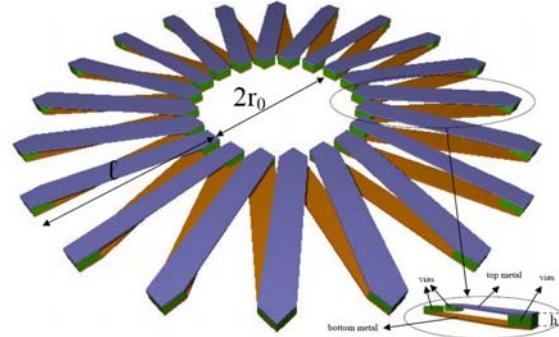

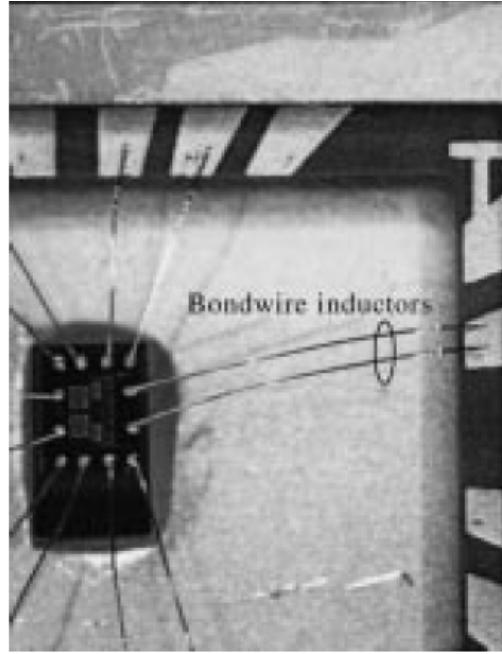

| Figure 4.9 A bond wire inductor [99] .....                                                                                                                                                                             | 86  |

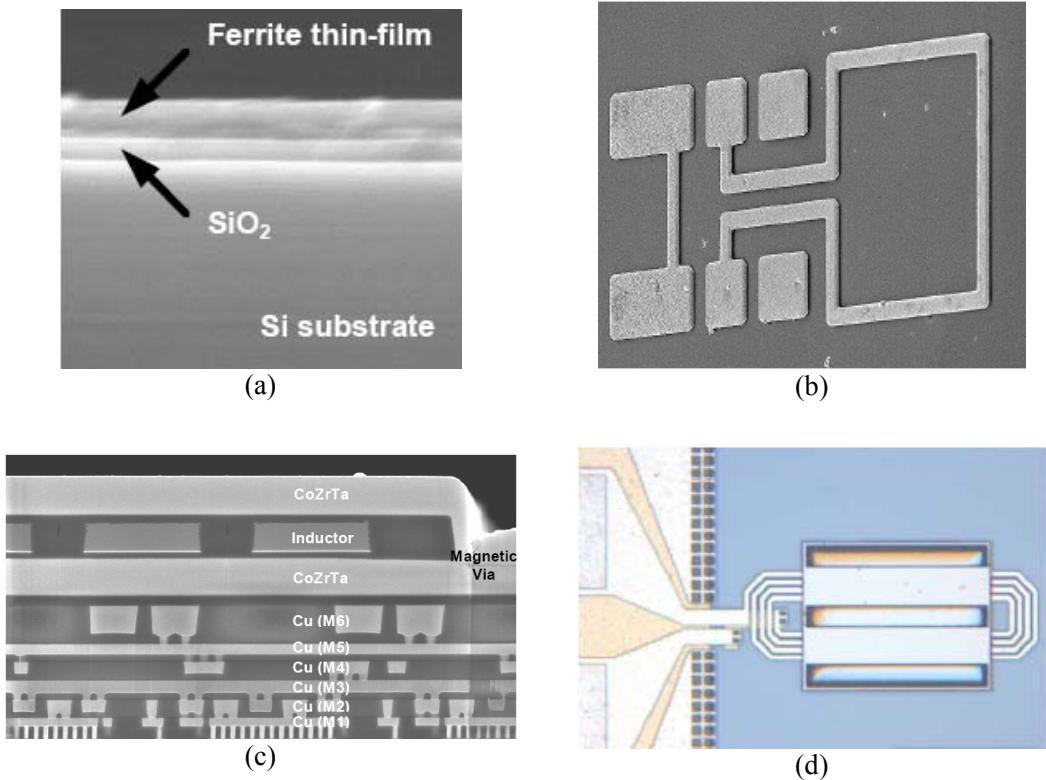

| Figure 4.10 Magnetic thin film inductors: (a) thin film ferrite [100], (b) magnetic thin film inductor [100], (c) cross section of metal and magnetic layers [101], (d) spiral inductor with magnetic film [101] ..... | 87  |

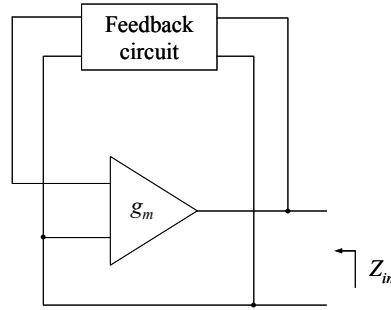

| Figure 4.11 A typical configuration of an active inductor .....                                                                                                                                                        | 89  |

| Figure 4.12 Generic lumped model of a spiral inductor .....                                                                                                                                                            | 93  |

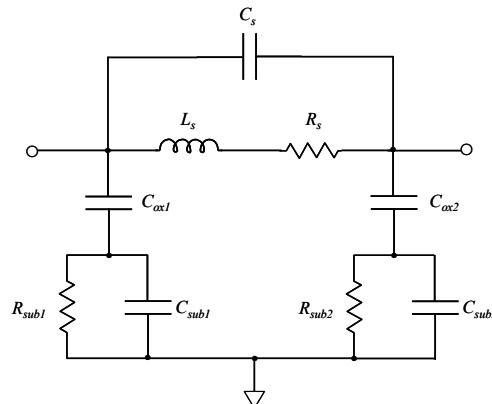

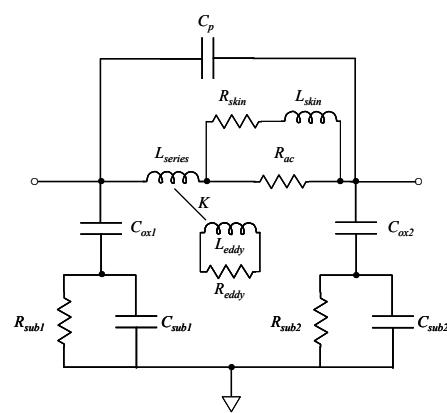

| Figure 4.13 On-chip inductor model considering high frequency effects .....                                                                                                                                            | 96  |

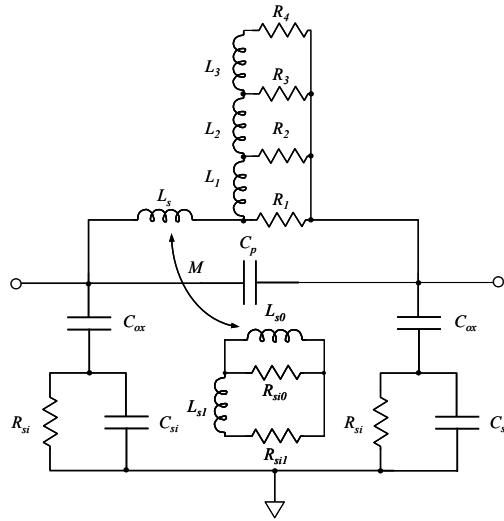

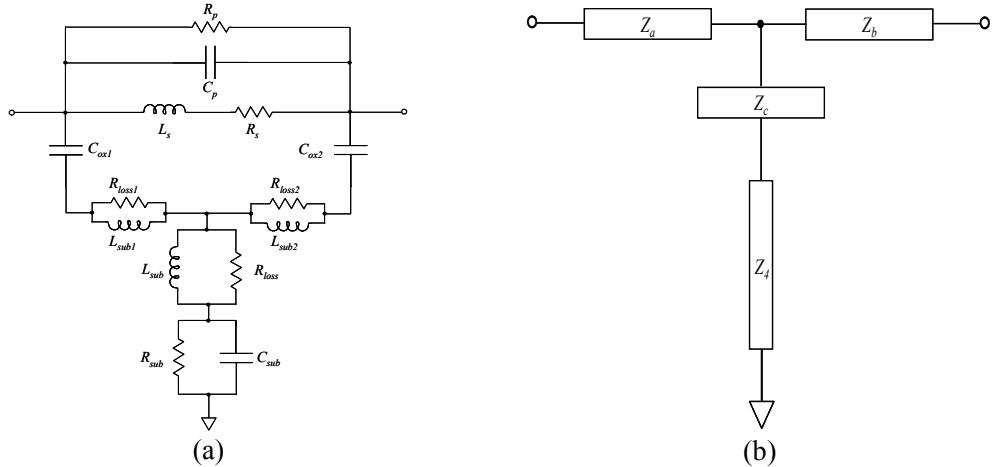

| Figure 4.14 An on-chip spiral inductor model: (a) lumped model, (b) simplified T model ..                                                                                                                              | 97  |

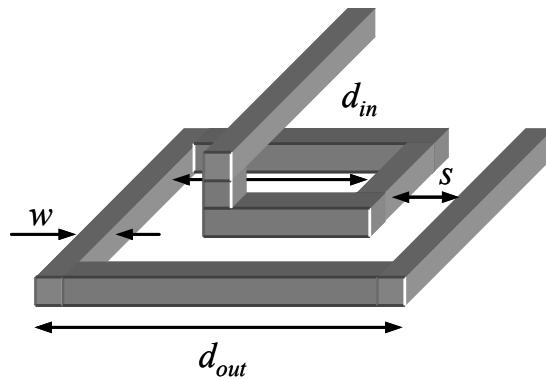

| Figure 4.15 A square spiral inductor .....                                                                                                                                                                             | 99  |

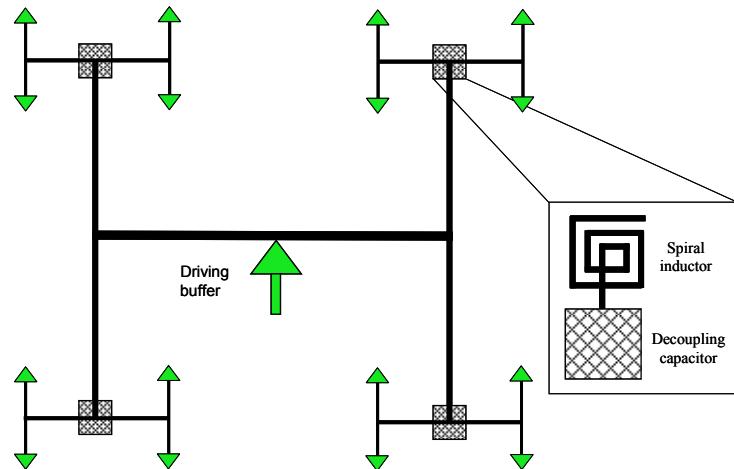

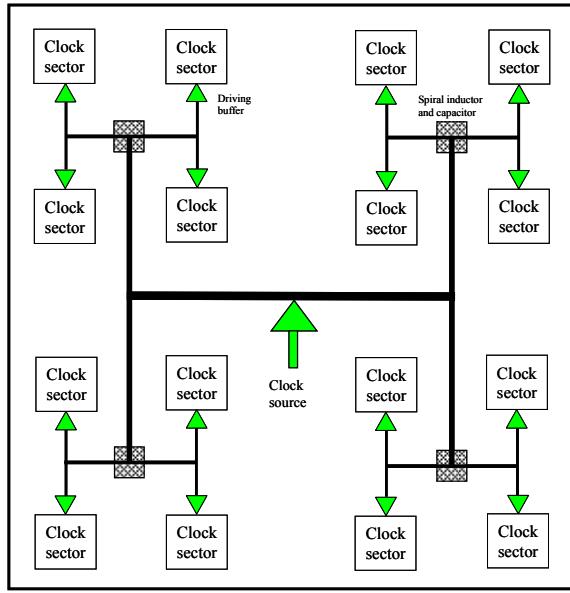

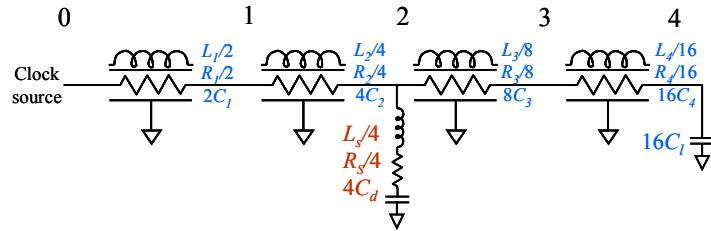

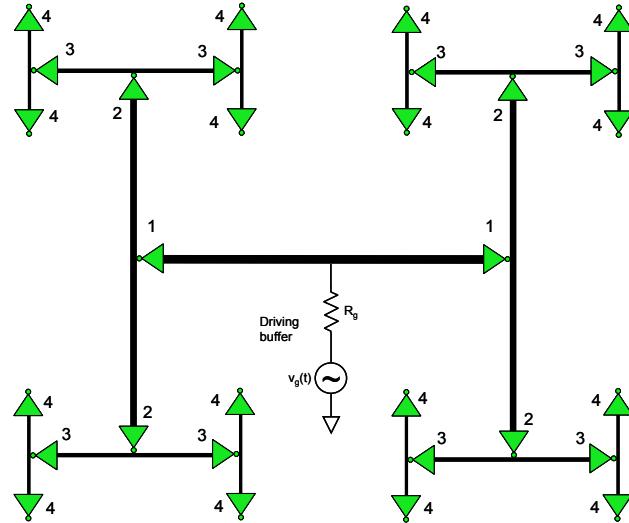

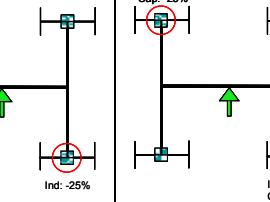

| Figure 5.1 H-tree sector with on-chip inductors and capacitors .....                                                                                                                                                   | 109 |

| Figure 5.2 A global clock distribution network, consisting of 16 resonant clock sectors and a total of 256 leafs .....                                                                                                 | 110 |

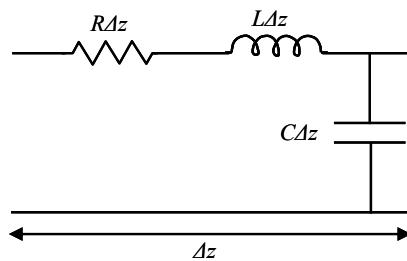

| Figure 5.3 Distributed model of a transmission line .....                                                                                                                                                              | 111 |

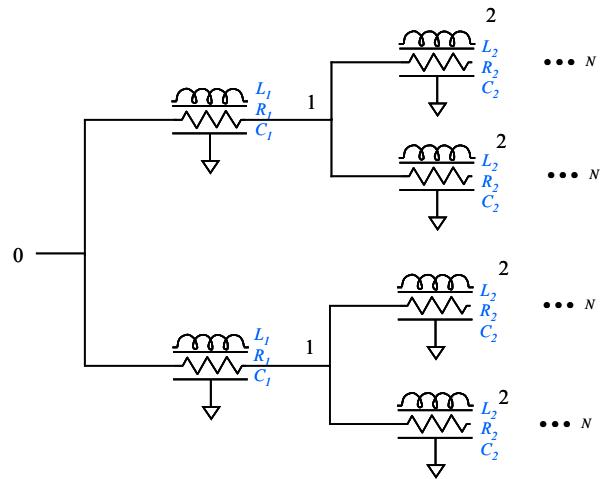

| Figure 5.4 Distributed <i>RLC</i> network representation of an H-tree network .....                                                                                                                                    | 112 |

| Figure 5.5 Resonant H-tree network simplified to a distributed <i>RLC</i> line .....                                                                                                                                   | 113 |

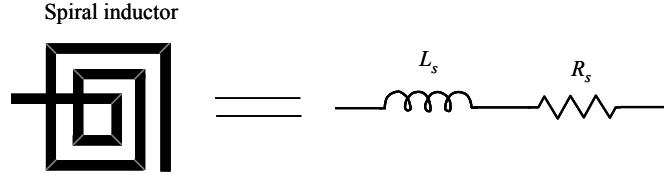

| Figure 5.6 Simplified model of an on-chip spiral inductor .....                                                                                                                                                        | 115 |

| Figure 5.7 Effective series resistance of spiral inductors .....                                                                                                                                                       | 115 |

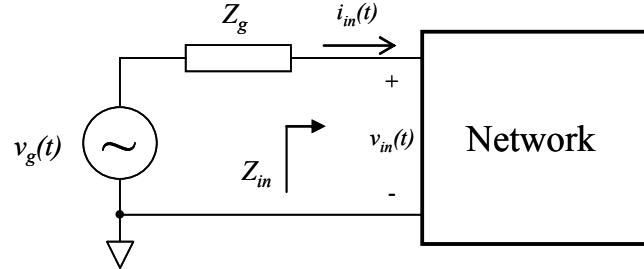

| Figure 5.8 One-port network driven by a voltage source .....                                                                                                                                                           | 116 |

|                                                                                                                                                                              |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.9 Structure of resonant H-tree sector .....                                                                                                                         | 122 |

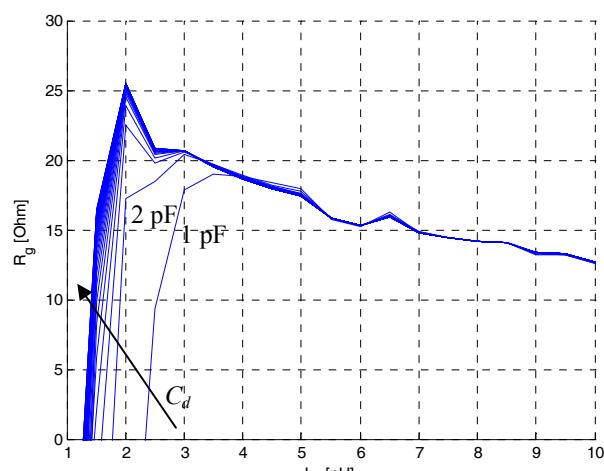

| Figure 5.10 Design tradeoffs for an H-tree sector: (a) Output resistance as a function of the spiral inductor, (b) $\rho$ as a function of the on-chip spiral inductor ..... | 124 |

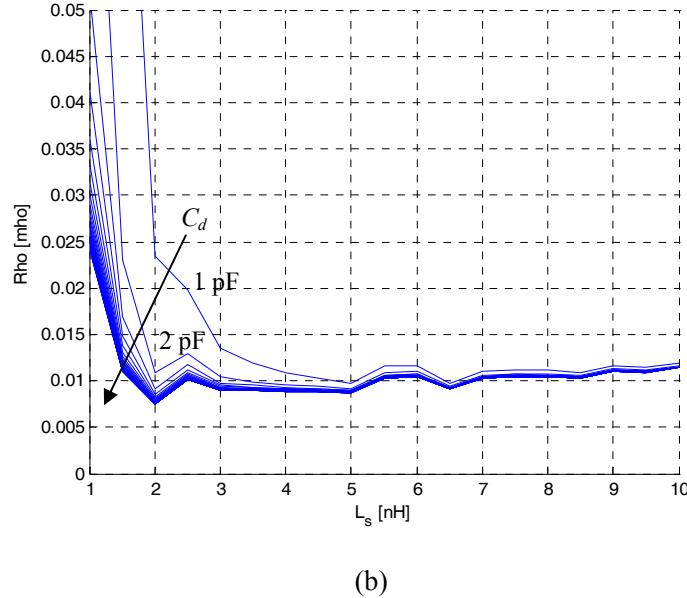

| Figure 5.11 Output resistance and $\rho$ as a function of the on-chip capacitance with $L_s = 2$ nH .....                                                                    | 125 |

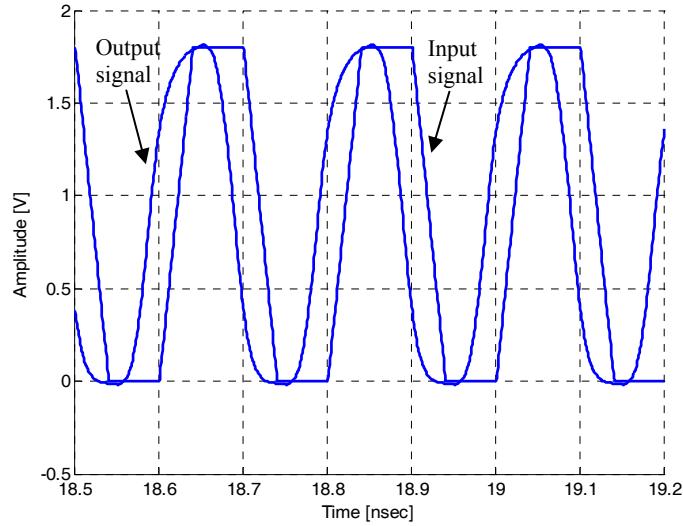

| Figure 5.12 Output waveform at the leaf nodes .....                                                                                                                          | 126 |

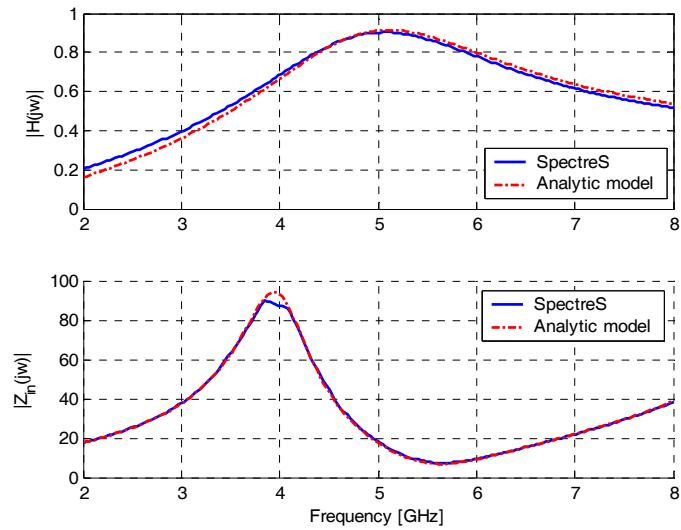

| Figure 5.13 Magnitude of the transfer function and input impedance .....                                                                                                     | 126 |

| Figure 5.14 H-tree sector with buffers .....                                                                                                                                 | 127 |

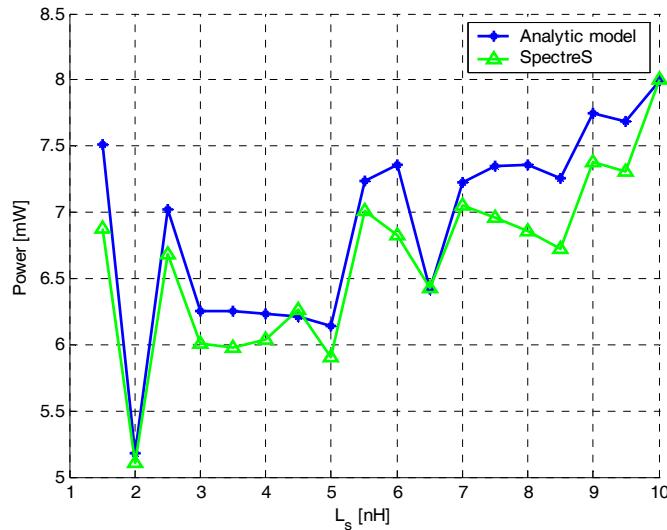

| Figure 5.15 Comparison of power consumption between analytic model and SpectreS Spice simulation .....                                                                       | 128 |

| Figure 5.16 Normalized voltage swing at the leaf node .....                                                                                                                  | 129 |

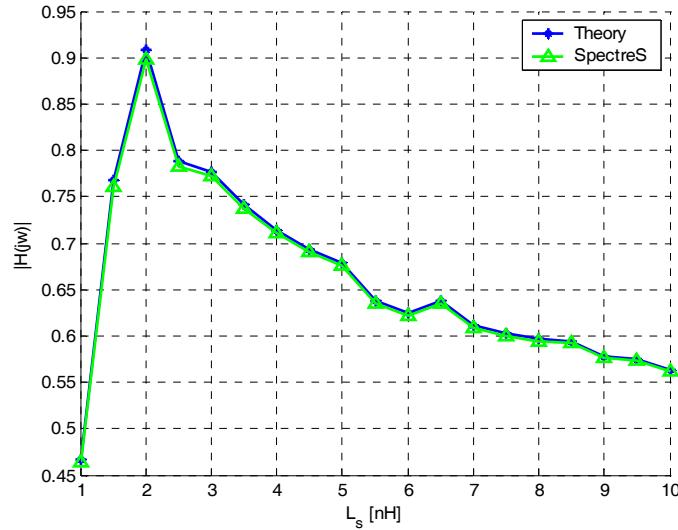

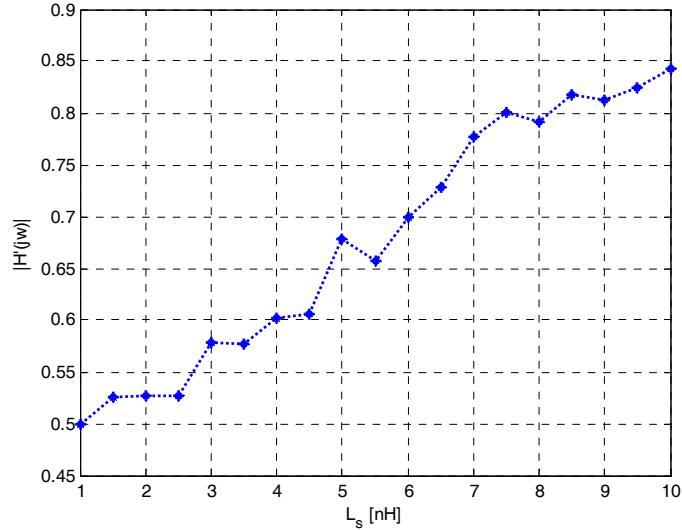

| Figure 5.17 Magnitude of the transfer function as a function of the inductance at a 5 GHz operating frequency .....                                                          | 130 |

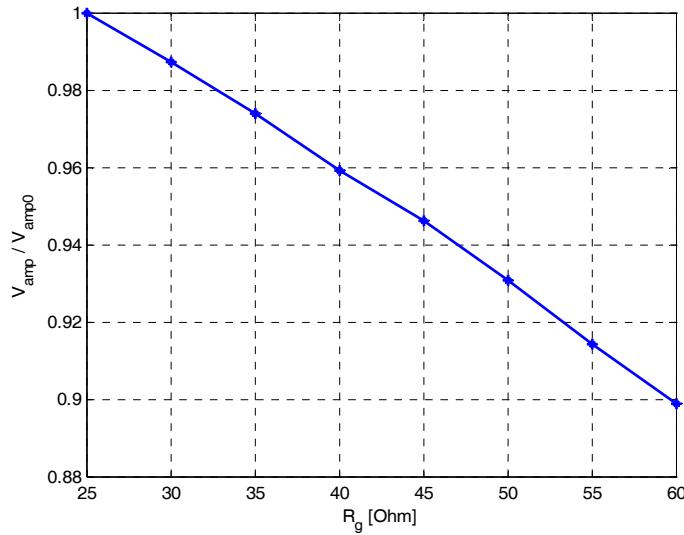

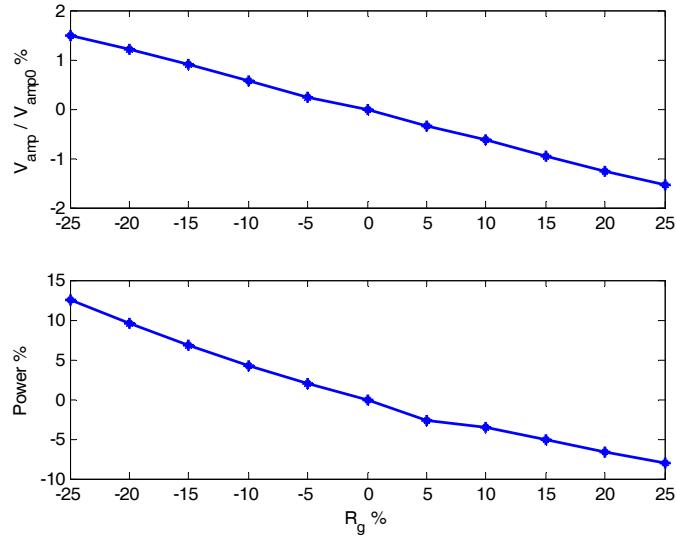

| Figure 5.18 Voltage swing and power consumption as a function of variations in the output resistance .....                                                                   | 131 |

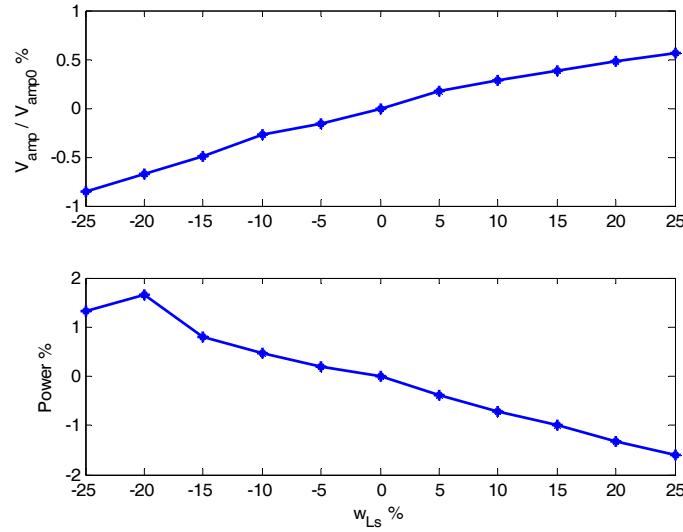

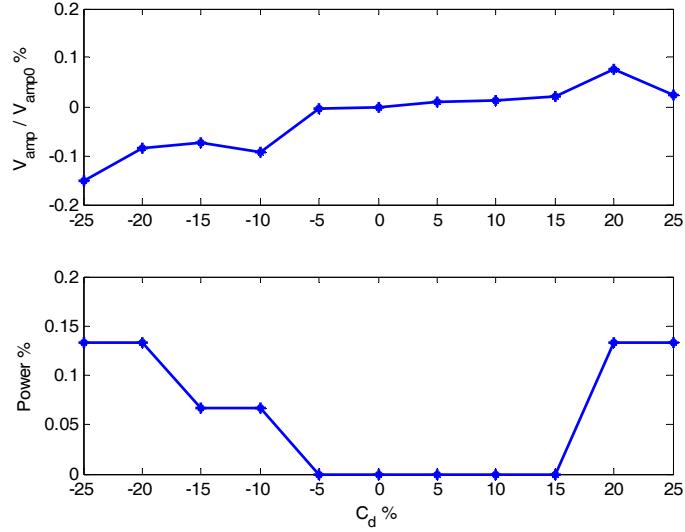

| Figure 5.19 Voltage swing and power consumption as a function of variations in the on-chip inductor width .....                                                              | 132 |

| Figure 5.20 Voltage swing and power consumption as a function of variations of the on-chip capacitor .....                                                                   | 133 |

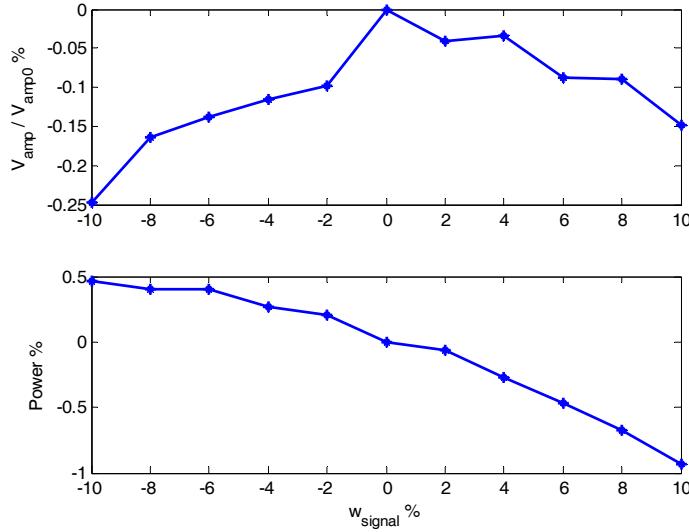

| Figure 5.21 Voltage swing and power consumption as a function of variations in the signal line width .....                                                                   | 135 |

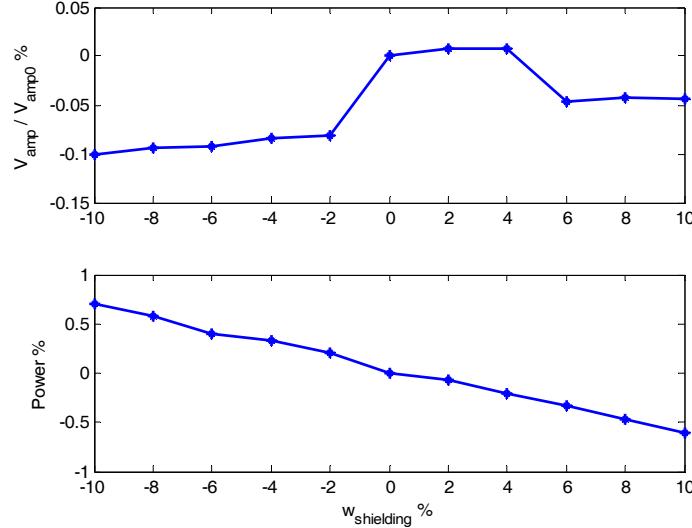

| Figure 5.22 Voltage swing and power consumption as a function of variations in the shield line width .....                                                                   | 136 |

|                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

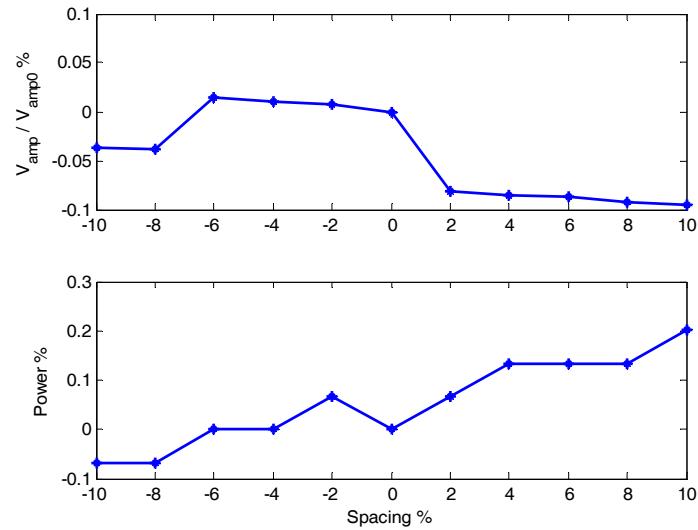

| Figure 5.23 Voltage swing and power consumption as a function of spacing variations<br>between the signal and shield lines .....                                                                                                                                                                                                                                                                                              | 137 |

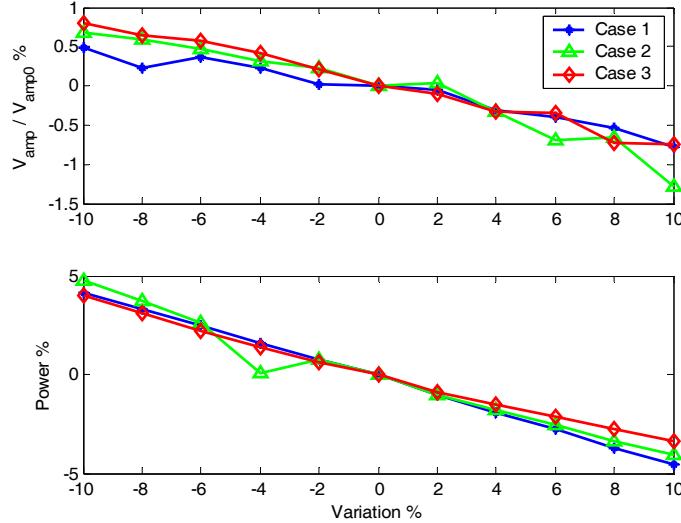

| Figure 5.24 Three cases of voltage swing and power consumption as a function of four<br>simultaneous variations: Case 1 - buffer output resistance, spiral inductors,<br>capacitors, and signal line width are varied; Case 2 - buffer output resistance,<br>spiral inductors, capacitors, and shield line width are varied; Case 3 - buffer<br>output resistance, spiral inductors, capacitors, and spacing are varied ..... | 138 |

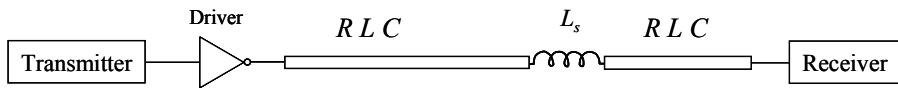

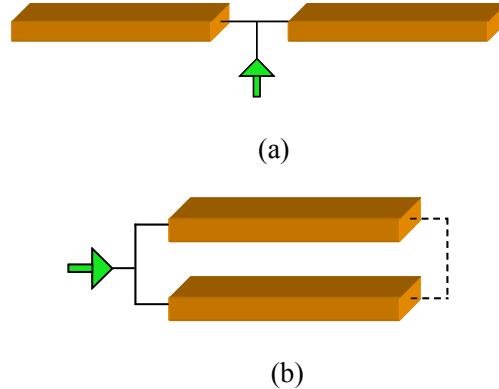

| Figure 6.1 Quasi-resonant network .....                                                                                                                                                                                                                                                                                                                                                                                       | 146 |

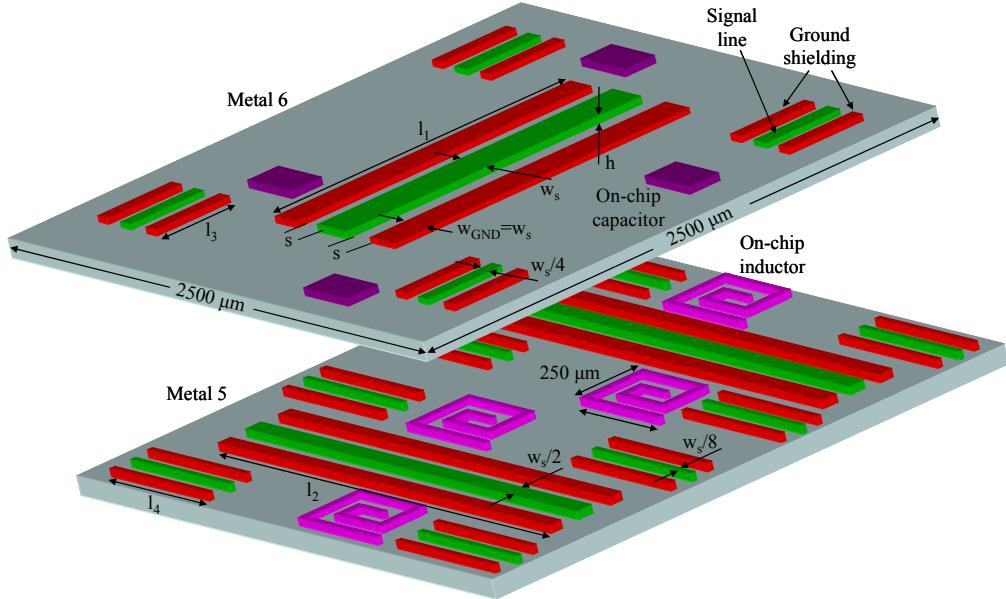

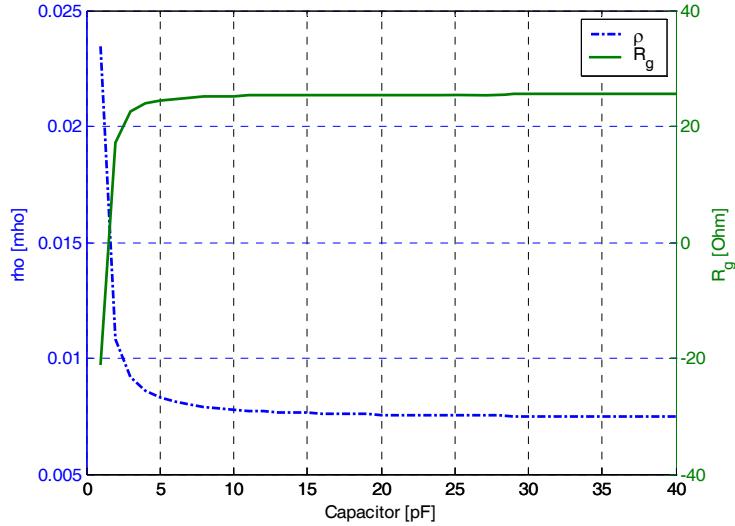

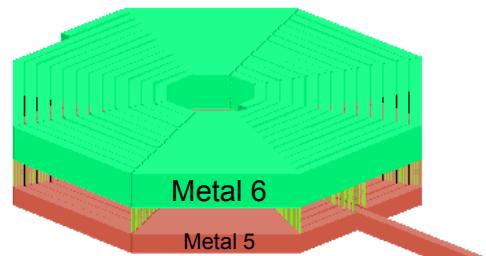

| Figure 6.2 Model of an on-chip spiral inductor: (a) structure of an octagonal on-chip spiral<br>inductor, (b) lumped model of the spiral inductor.....                                                                                                                                                                                                                                                                        | 149 |

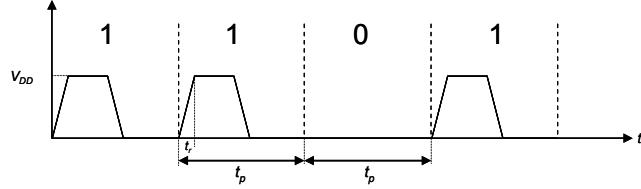

| Figure 6.3 Example of transmitting a “1011” bit stream .....                                                                                                                                                                                                                                                                                                                                                                  | 151 |

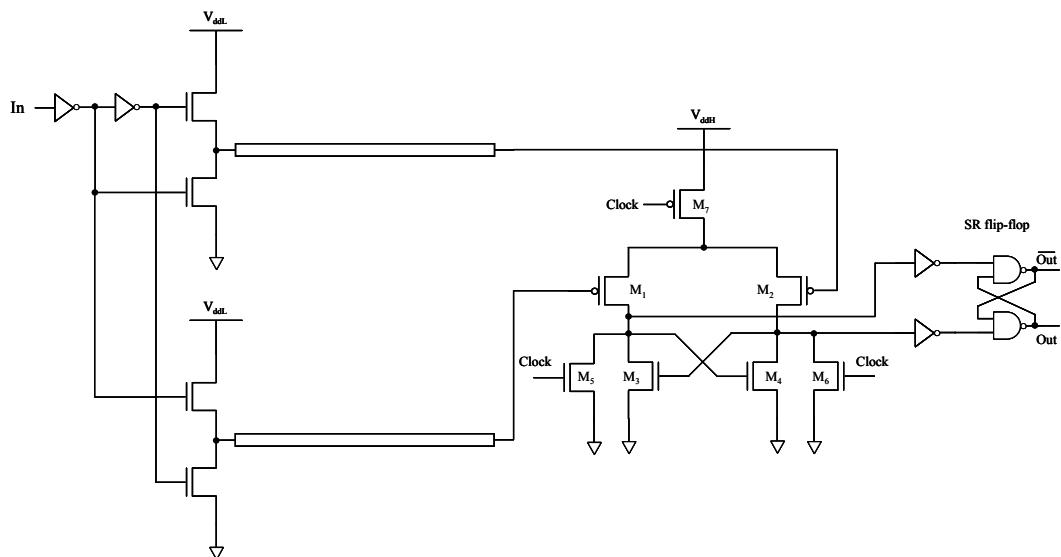

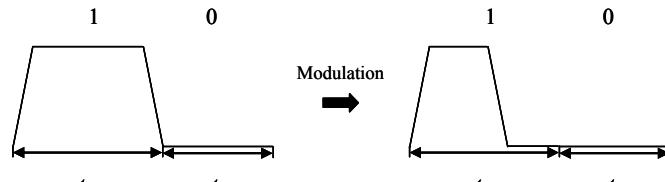

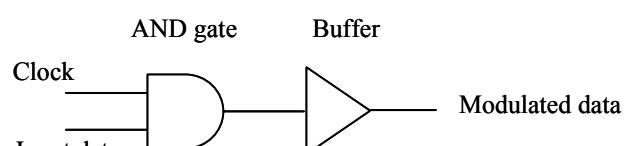

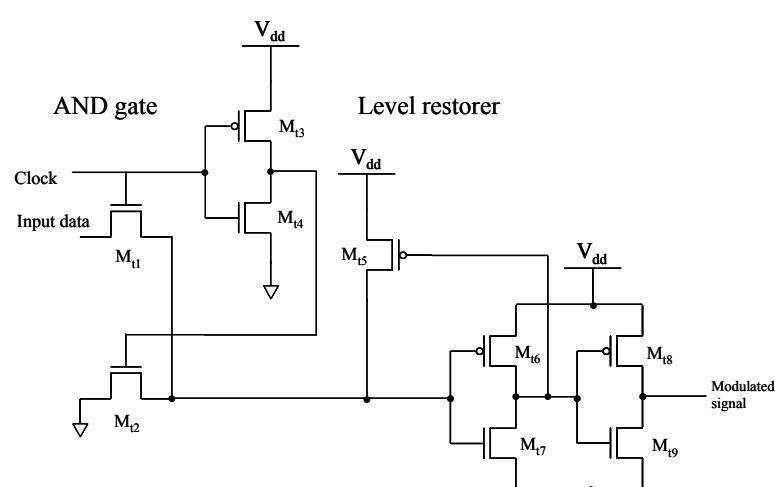

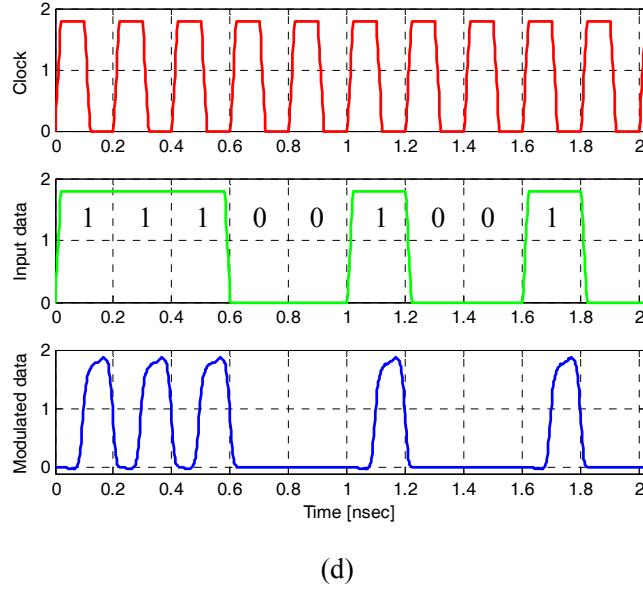

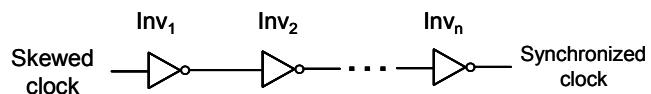

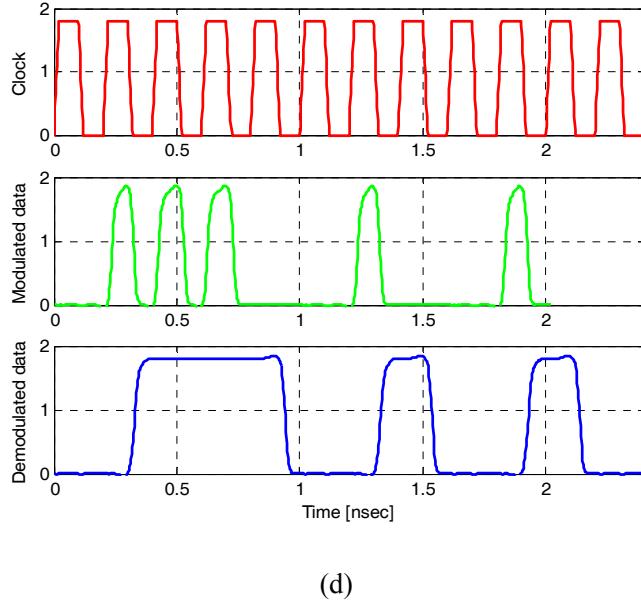

| Figure 6.4 Transmitter circuit: (a) modulation scheme, (b) gate level circuit, (c) transistor<br>level circuit, (d) signal waveforms .....                                                                                                                                                                                                                                                                                    | 153 |

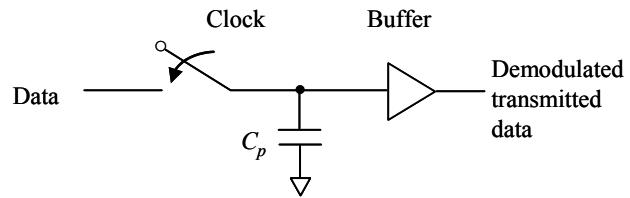

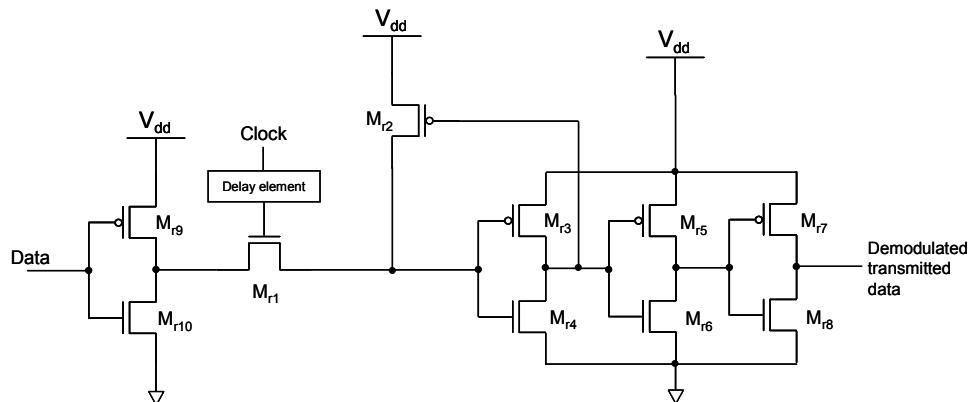

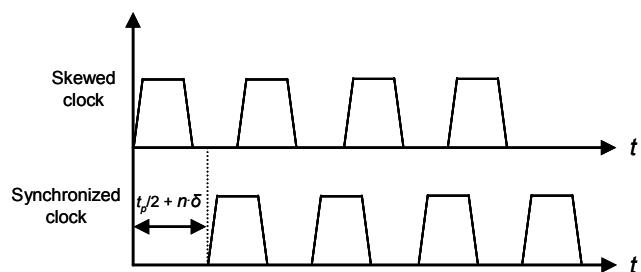

| Figure 6.5 Receiver circuit: (a) sample and hold circuit, (b) transistor level circuit, (c) delay<br>element circuit, (d) signal waveforms .....                                                                                                                                                                                                                                                                              | 155 |

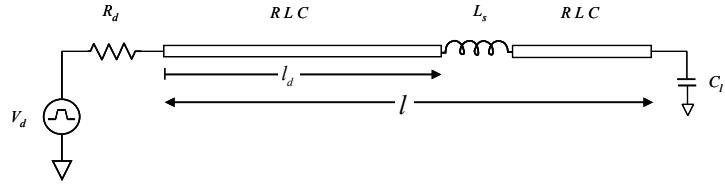

| Figure 6.6 Quasi-resonant network .....                                                                                                                                                                                                                                                                                                                                                                                       | 157 |

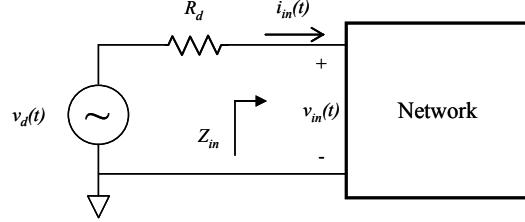

| Figure 6.7 One-port network driven by a voltage source.....                                                                                                                                                                                                                                                                                                                                                                   | 159 |

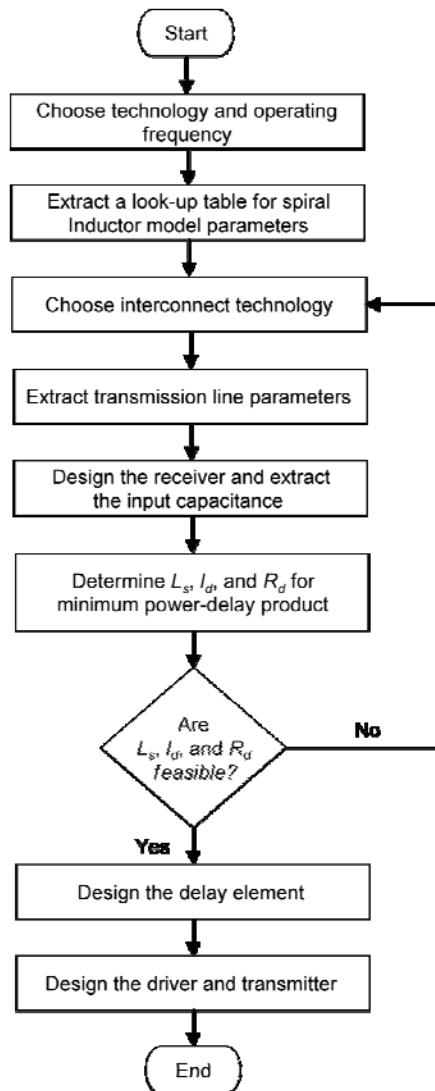

| Figure 6.8 Flow diagram of QRN design process.....                                                                                                                                                                                                                                                                                                                                                                            | 163 |

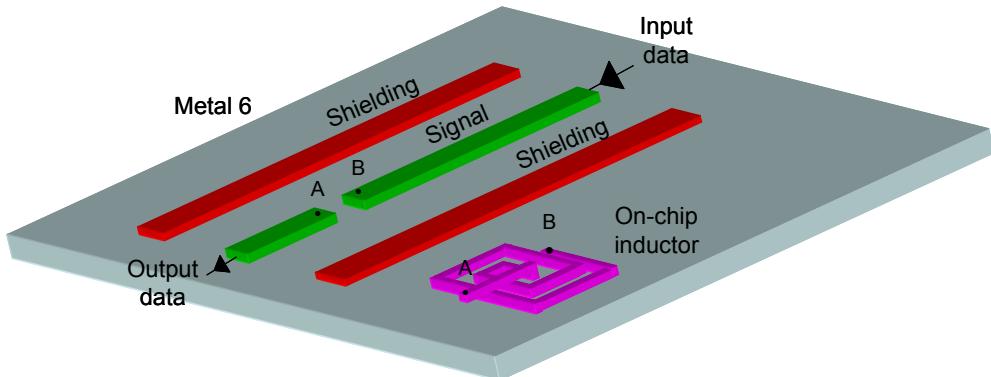

| Figure 6.9 Layout of a resonant transmission line network .....                                                                                                                                                                                                                                                                                                                                                               | 164 |

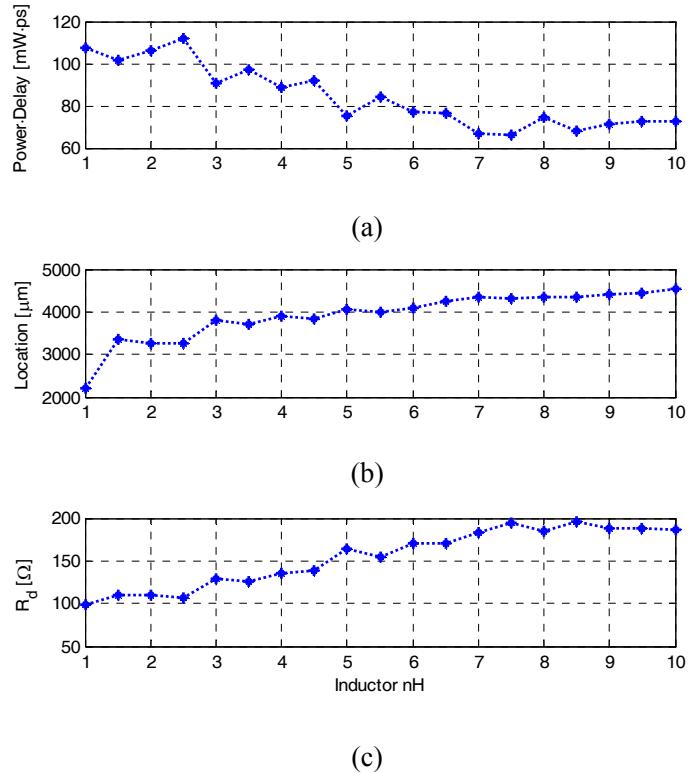

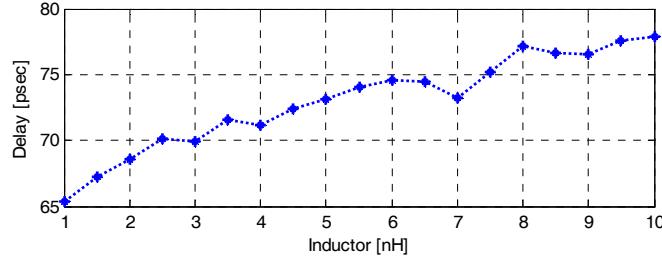

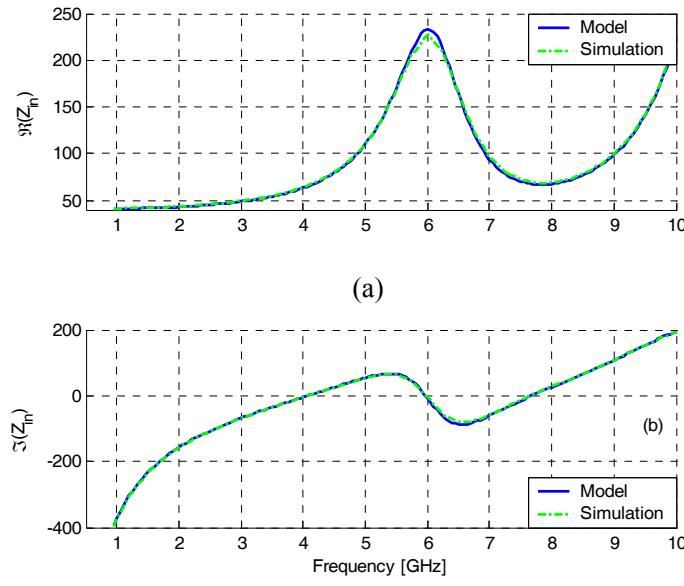

| Figure 6.10 A design example of a 5 mm long interconnect operating at a 5 Gbps<br>transmission frequency: (a) minimum power-delay product as a function of<br>inductance, (b) insertion location as a function of inductance, (c) driver resistance<br>as a function of inductance .....                                                                                                                                      | 166 |

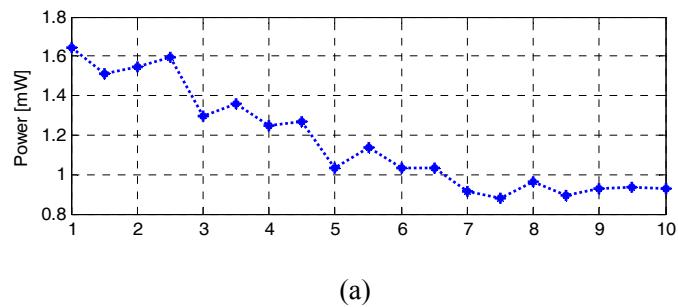

| Figure 6.11 Power and delay: (a) power consumption, (b) signal delay.....                                                                                                                                                                                                                                                                                                                                                     | 167 |

|                                                                                                                                                                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

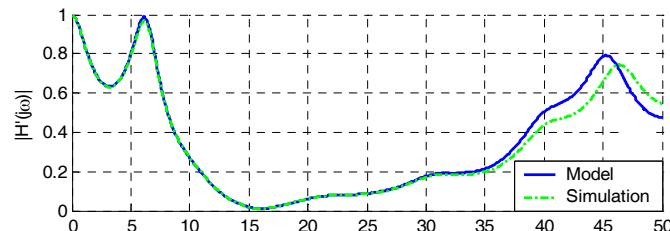

| Figure 6.12 Frequency response of the transfer function: (a) magnitude, (b) phase.....                                                                                                                                                                  | 168 |

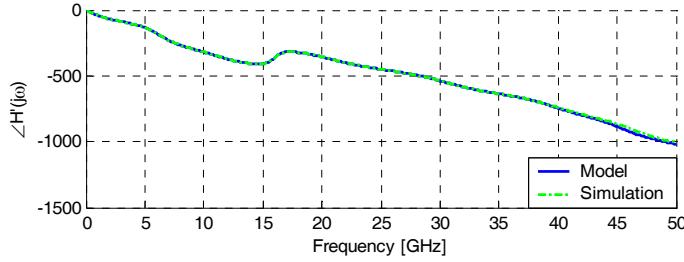

| Figure 6.13 QRN input impedance: (a) real part, (b) imaginary part .....                                                                                                                                                                                | 168 |

| Figure 6.14 Magnitude of the transfer function as a function of the inductance at a 5 GHz<br>operating frequency.....                                                                                                                                   | 169 |

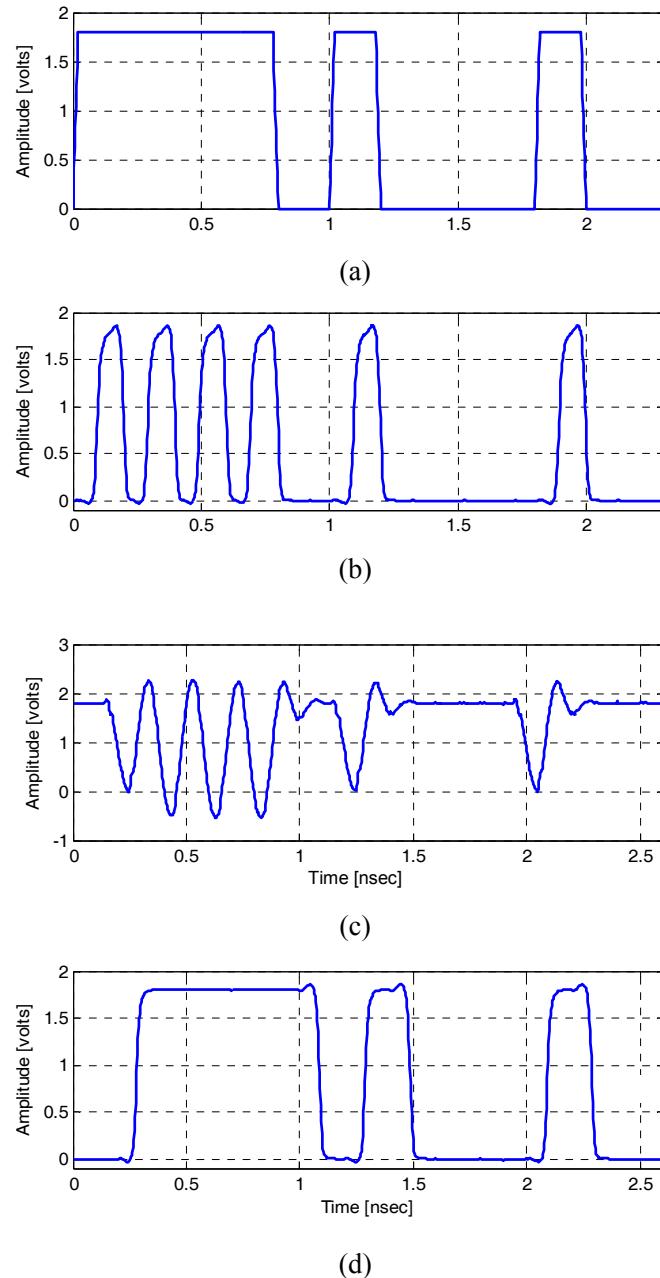

| Figure 6.15 Ten bit data stream example: (a) data at input of transmitter, (b) data at output of<br>transmitter, (c) data at input of receiver, (d) data at output of receiver.....                                                                     | 170 |

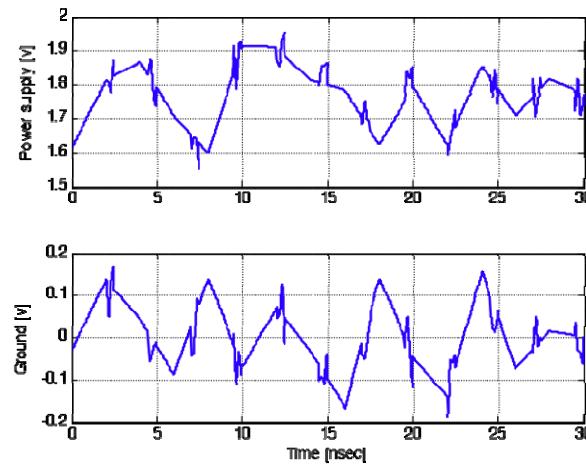

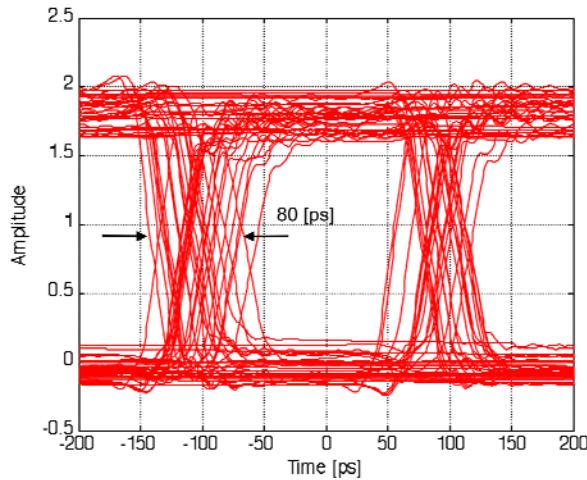

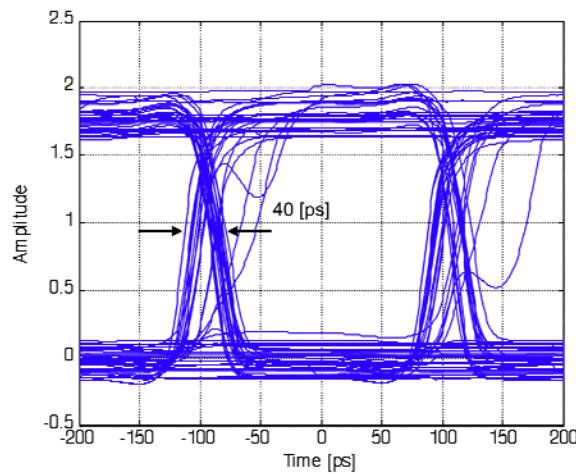

| Figure 6.16 Noise analysis: (a) noisy power supply and ground signals, (b) eye diagram of an<br>interconnect with repeaters, (c) eye diagram of quasi-resonant interconnect ...                                                                         | 172 |

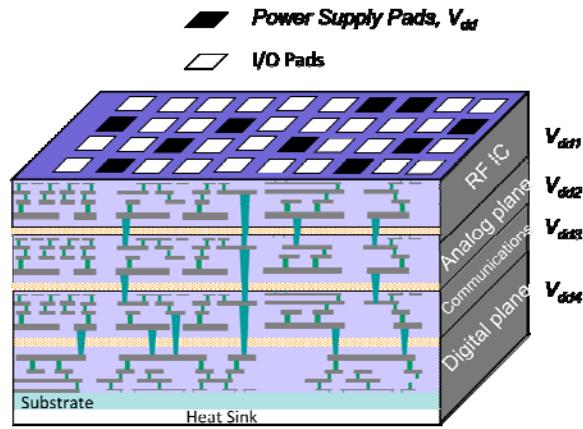

| Figure 7.1 Three-dimensional circuit with multiple power supplies .....                                                                                                                                                                                 | 179 |

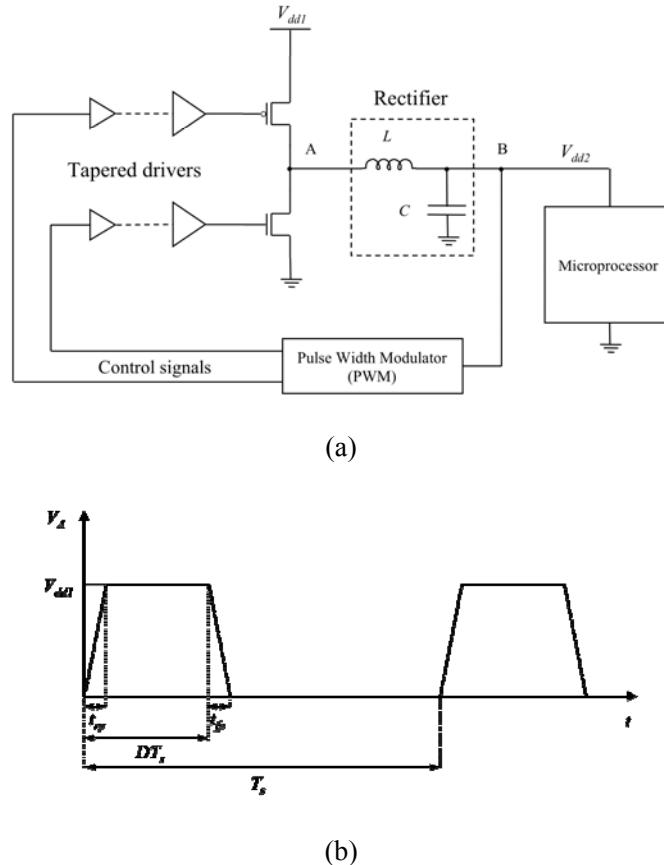

| Figure 7.2 Conventional DC-DC converter: (a) buck converter circuit [139], (b) signal at the<br>output of the power MOSFETs (node A).....                                                                                                               | 181 |

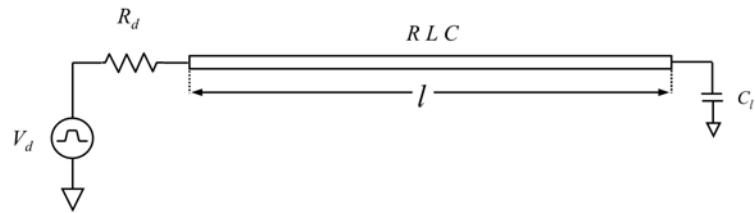

| Figure 7.3 <i>RLC</i> transmission line.....                                                                                                                                                                                                            | 185 |

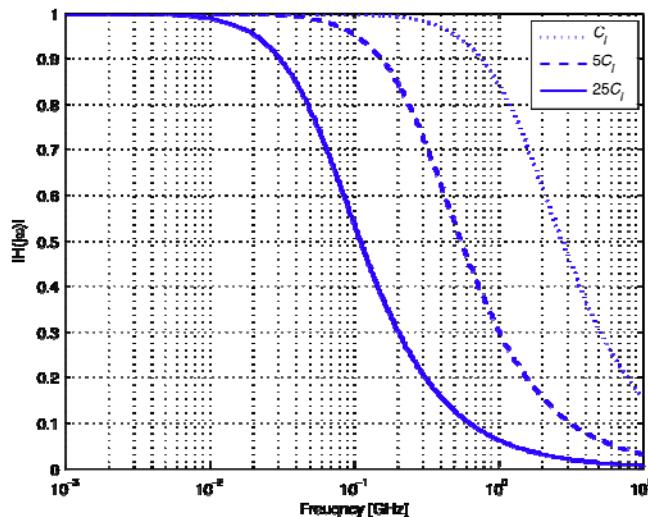

| Figure 7.4 Transfer function of the magnitude of an interconnect for different capacitive loads<br>.....                                                                                                                                                | 185 |

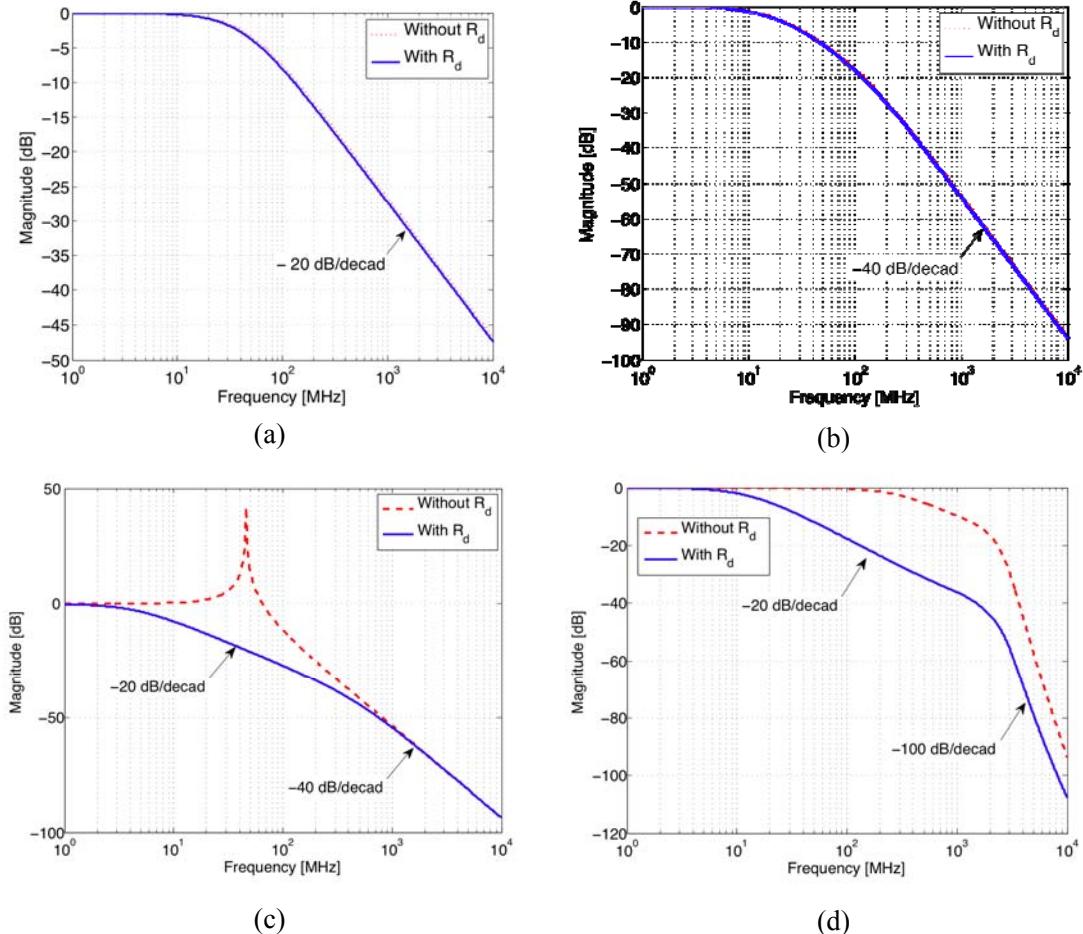

| Figure 7.5 Magnitude of transfer function: (a) single stage <i>RC</i> filter, (b) two stages <i>RC</i> filter,<br>(c) <i>LC</i> rectifier, (d) distributed rectifier.....                                                                               | 187 |

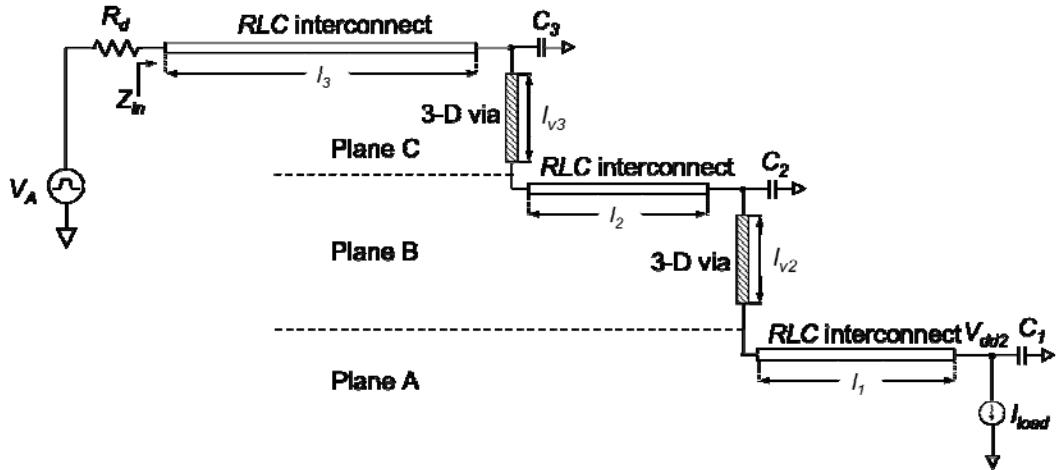

| Figure 7.6 A distributed rectifier .....                                                                                                                                                                                                                | 189 |

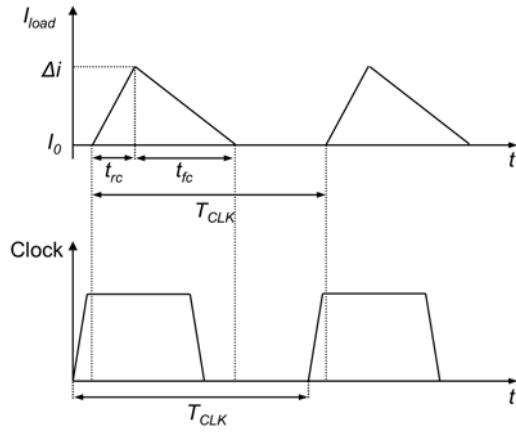

| Figure 7.7 Current load profile in high speed digital circuits .....                                                                                                                                                                                    | 190 |

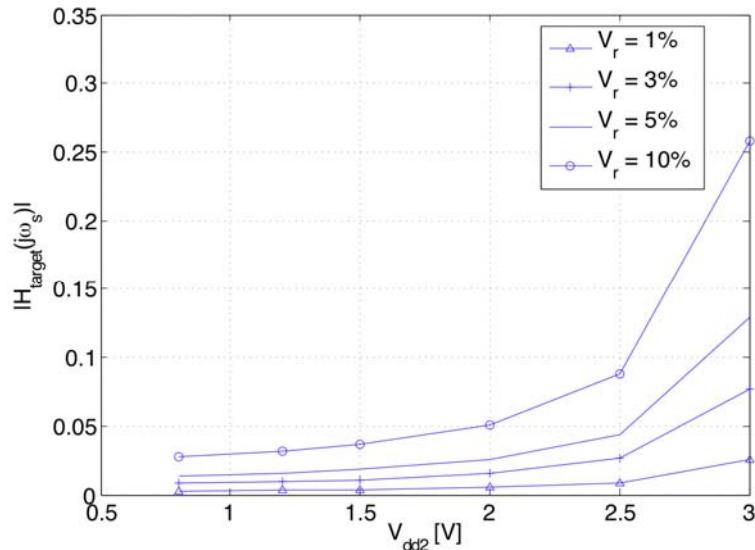

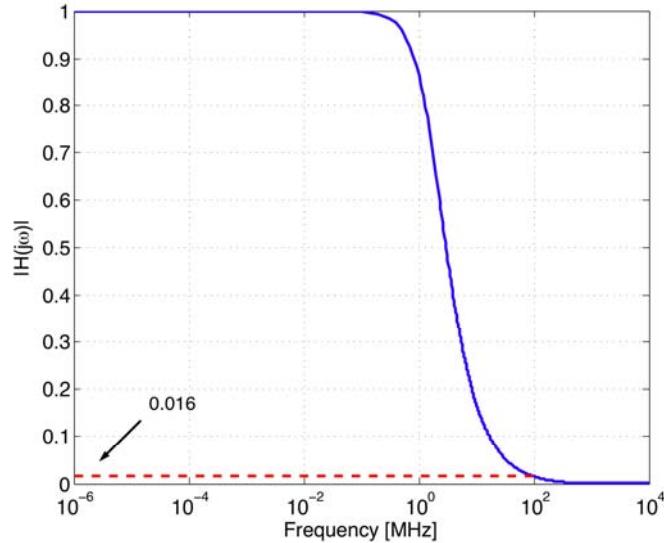

| Figure 7.8 Required magnitude of the transfer function .....                                                                                                                                                                                            | 198 |

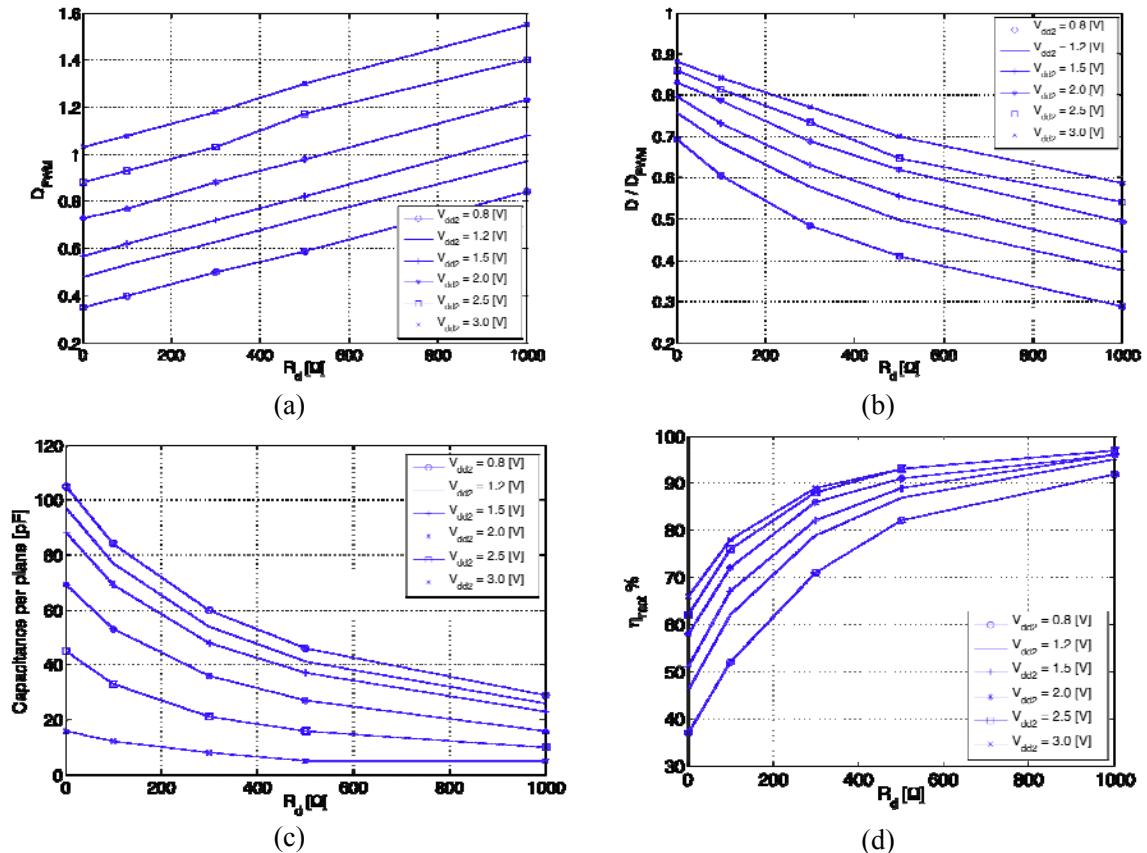

| Figure 7.9 Design space of a distributed rectifier: (a) modified duty cycle as a function of $R_d$ ,<br>(b) duty cycle ratio as a function of $R_d$ , (c) capacitance as a function of $R_d$ , (d)<br>rectifier efficiency as a function of $R_d$ ..... | 199 |

|                                                                                                                                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

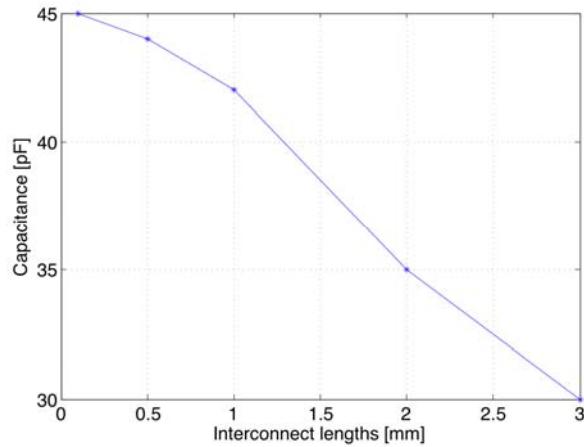

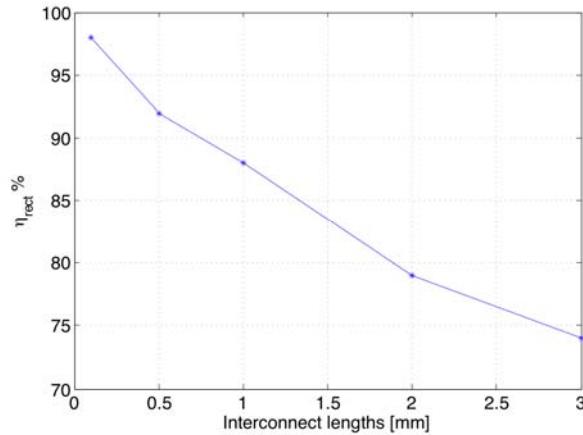

| Figure 7.10 Effect of interconnect length on performance: (a) capacitance as a function of interconnect length, (b) rectifier efficiency as a function of interconnect length | 201 |

| Figure 7.11 Magnitude of the transfer function of an <i>LC</i> rectifier                                                                                                      | 204 |

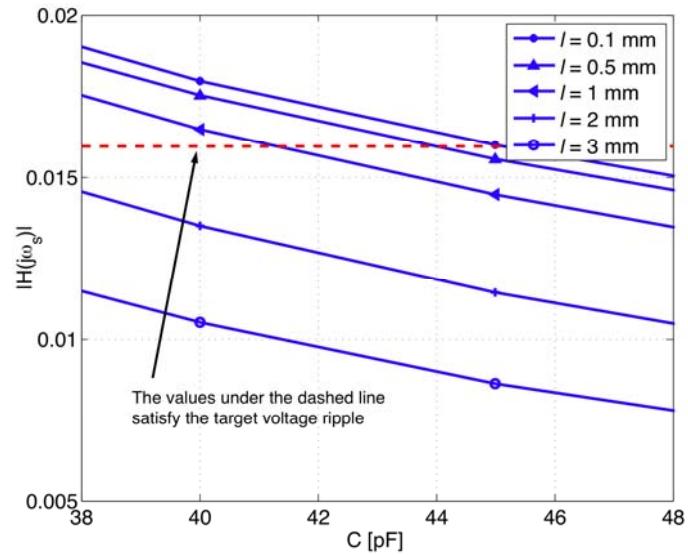

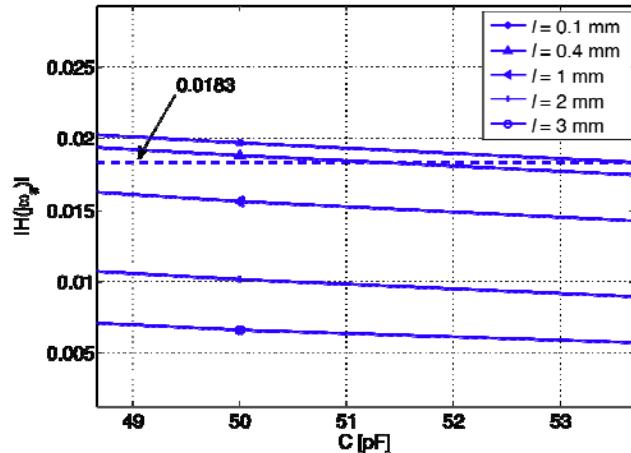

| Figure 7.12 Magnitude of the transfer function at $\omega_s$ for different lengths and capacitances                                                                           | 206 |

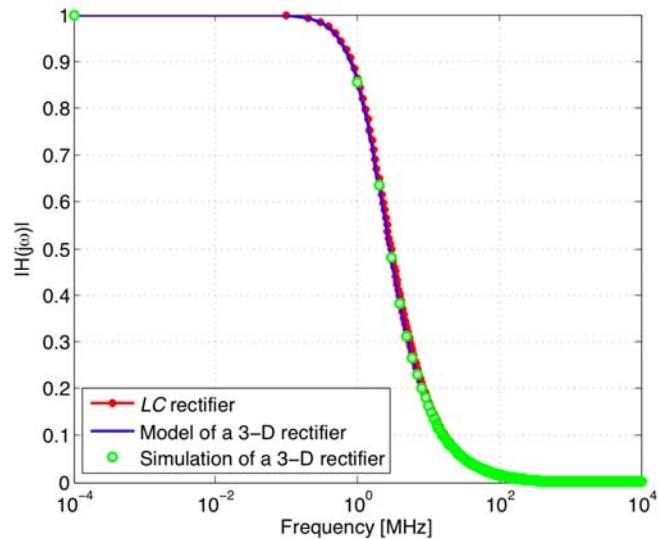

| Figure 7.13 Simulation and model of the magnitude of the transfer function of a 3-D rectifier and a conventional <i>LC</i> rectifier circuit                                  | 206 |

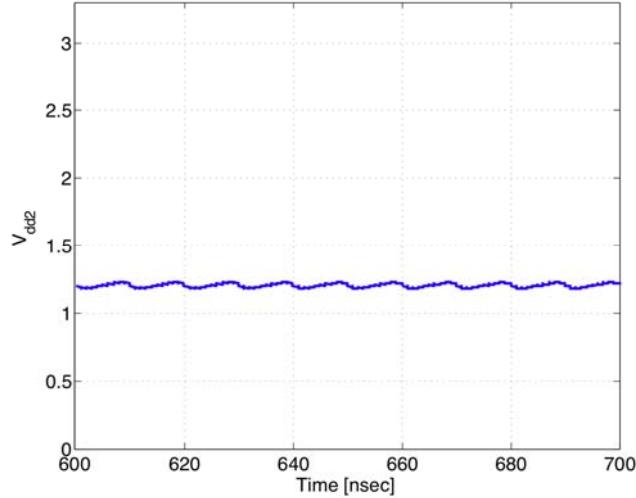

| Figure 7.14 DC voltage at the output of a distributed rectifier                                                                                                               | 207 |

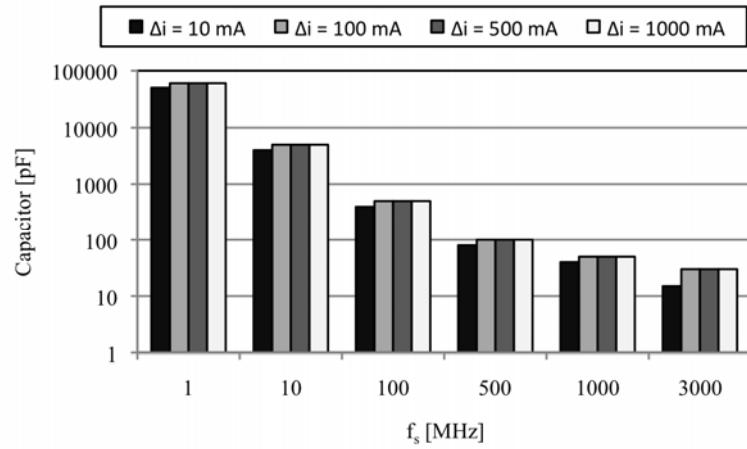

| Figure 7.15 Conventional <i>LC</i> rectifier: (a) capacitance, (b) inductance                                                                                                 | 209 |

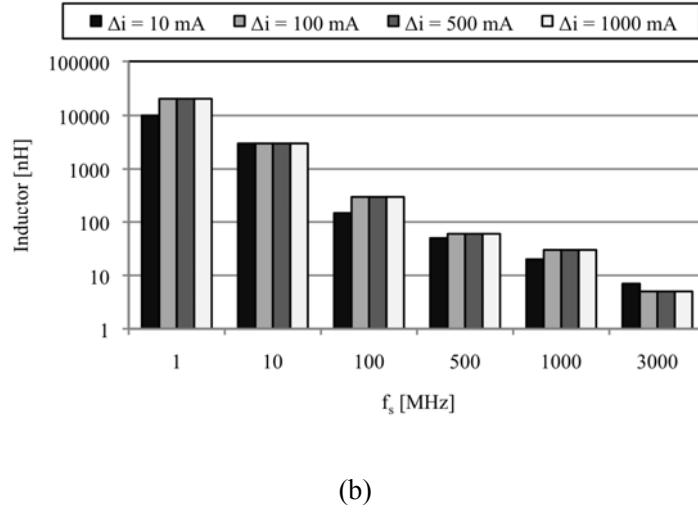

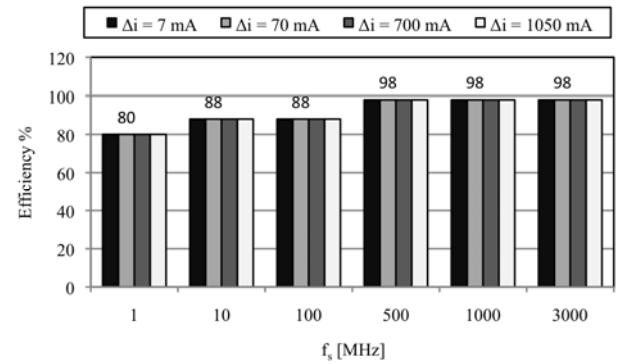

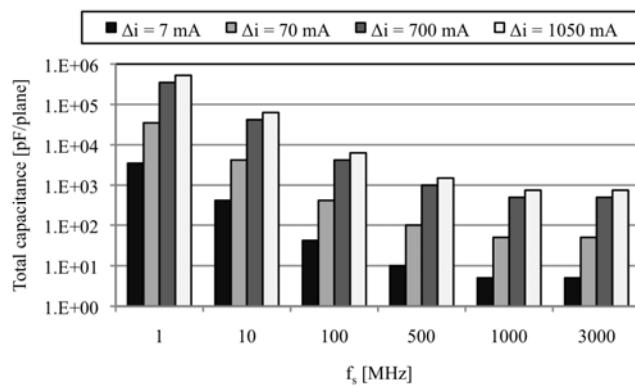

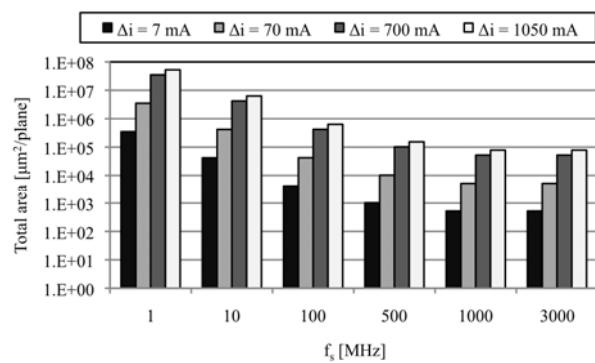

| Figure 7.16 3-D distributed rectifier: (a) efficiency, (b) total capacitance per plane, (c) total area per plane                                                              | 210 |

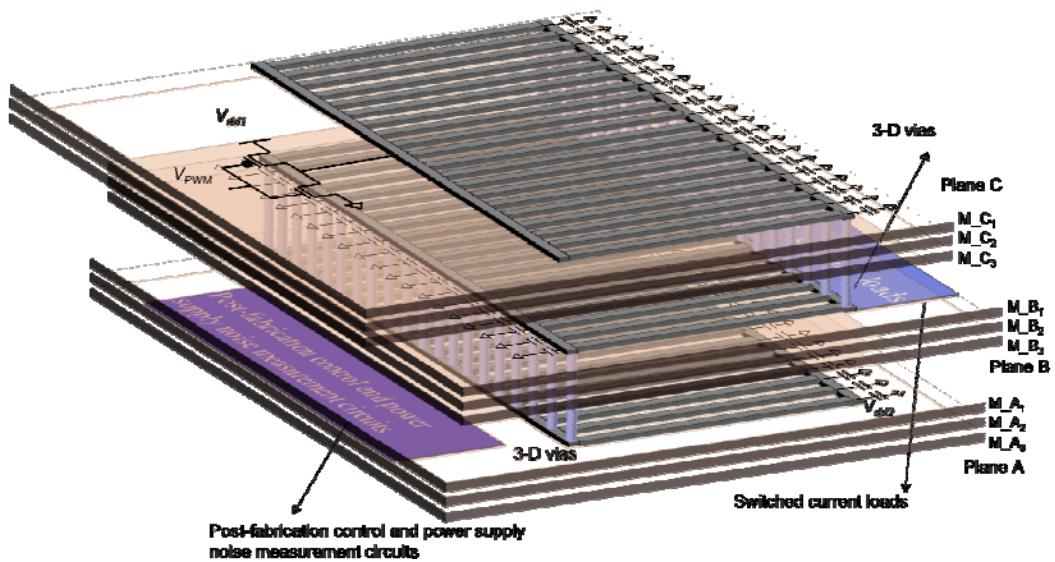

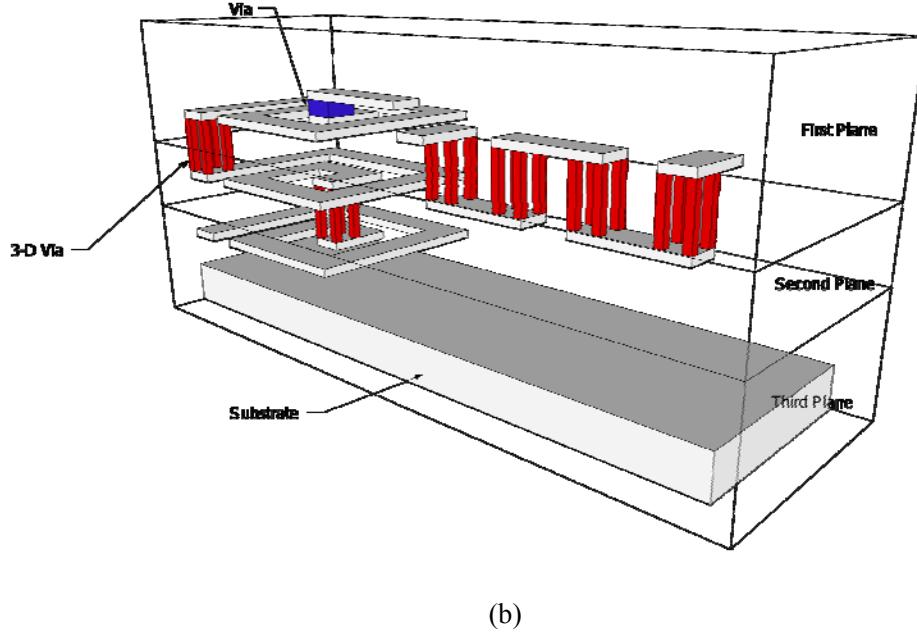

| Figure 8.1 A distributed rectifier of a DC-DC power converter in a three-plane structure ..                                                                                   | 213 |

| Figure 8.2 Current load profile                                                                                                                                               | 214 |

| Figure 8.3 Magnitude of the transfer function for different line lengths and capacitor magnitudes                                                                             | 215 |

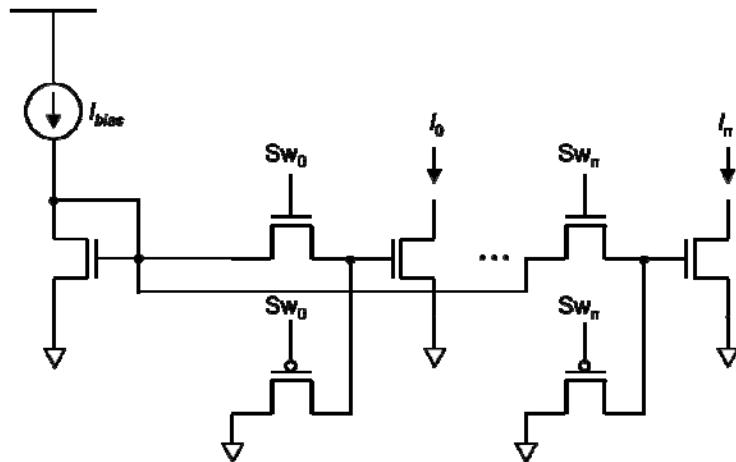

| Figure 8.4 Current load controlled by switches                                                                                                                                | 216 |

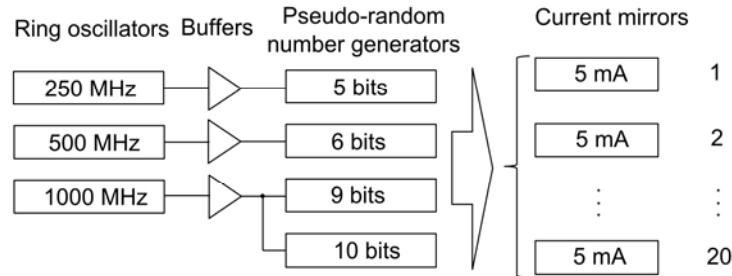

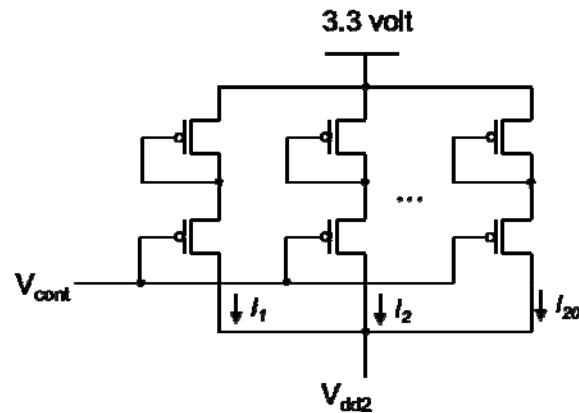

| Figure 8.5 Control logic for the current mirrors                                                                                                                              | 217 |

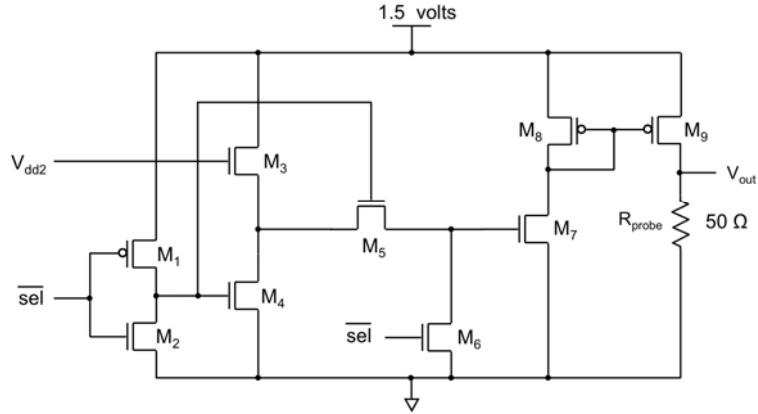

| Figure 8.6 Post-fabrication control circuit                                                                                                                                   | 217 |

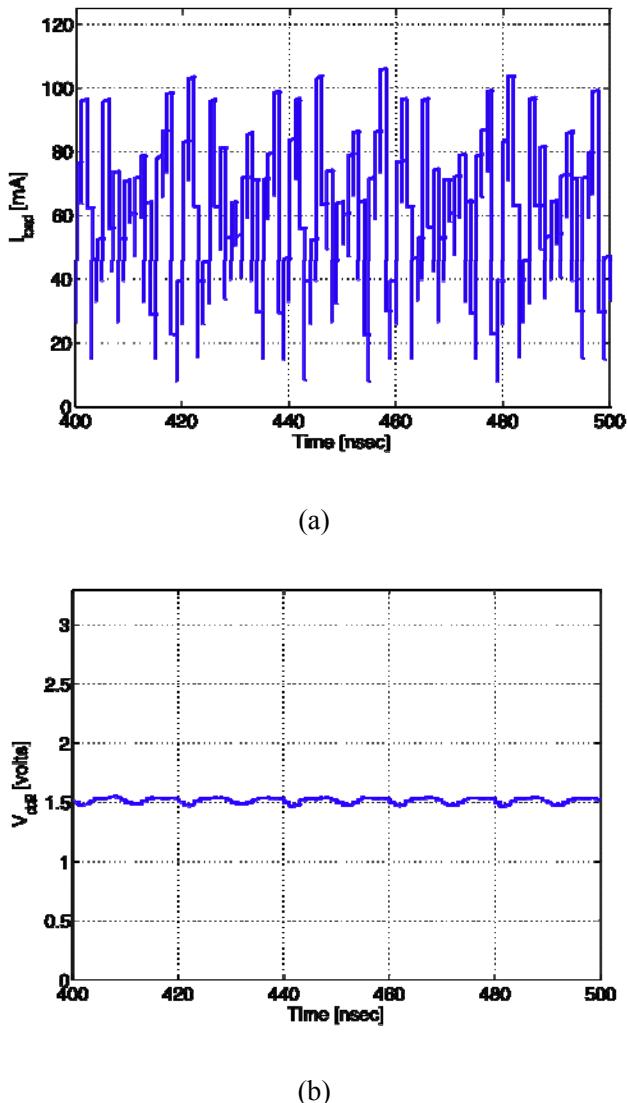

| Figure 8.7 Distributed rectifier: (a) current load, (b) output voltage supply                                                                                                 | 218 |

| Figure 8.8 Power supply noise detector                                                                                                                                        | 219 |

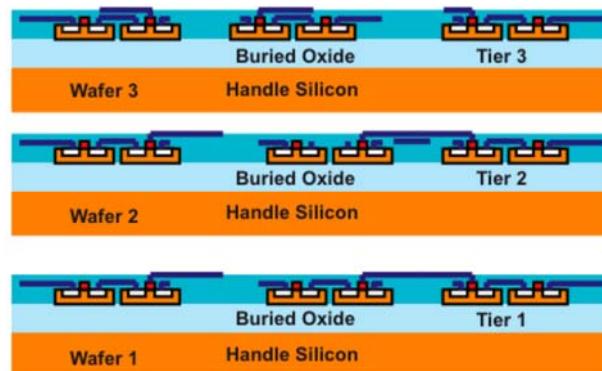

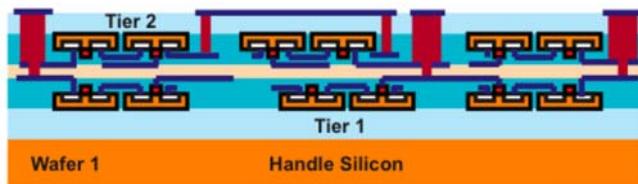

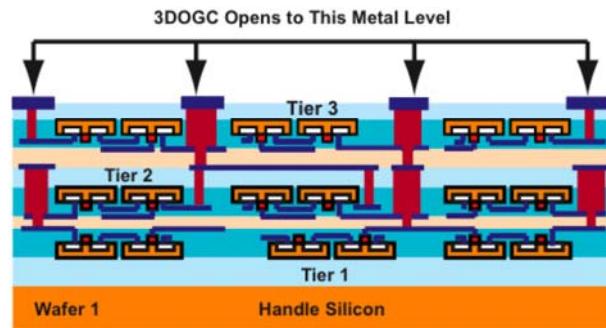

| Figure 8.9 Three independent tiers fabricated using a conventional 2-D technology [156].                                                                                      | 220 |

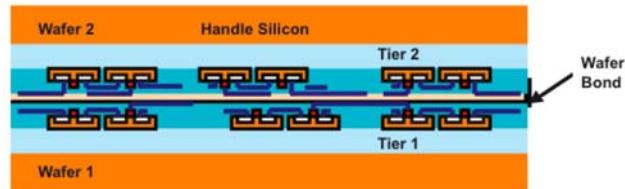

| Figure 8.10 Tier 2 aligned and bonded to tier 1 [156]                                                                                                                         | 221 |

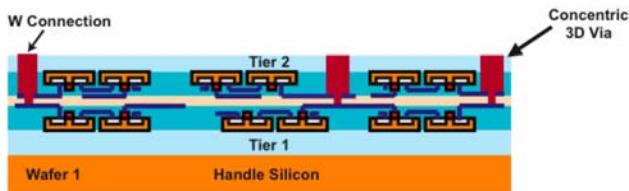

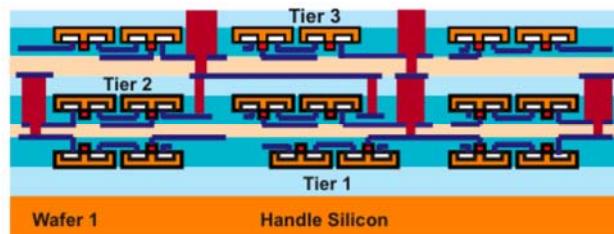

| Figure 8.11 Tier 2 electrically connected to tier 1 with Tungsten 3-D vias [156]                                                                                              | 221 |

| Figure 8.12 Formation of the back side vias and metal on tier 2 [156]                                                                                                         | 221 |

|                                                                                                                                                          |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 8.13 Tier 3 is aligned and bonded to the back side metal of tier 2 [156].....                                                                     | 221 |

| Figure 8.14 Formation of the back side metal on tier 3 [156].....                                                                                        | 222 |

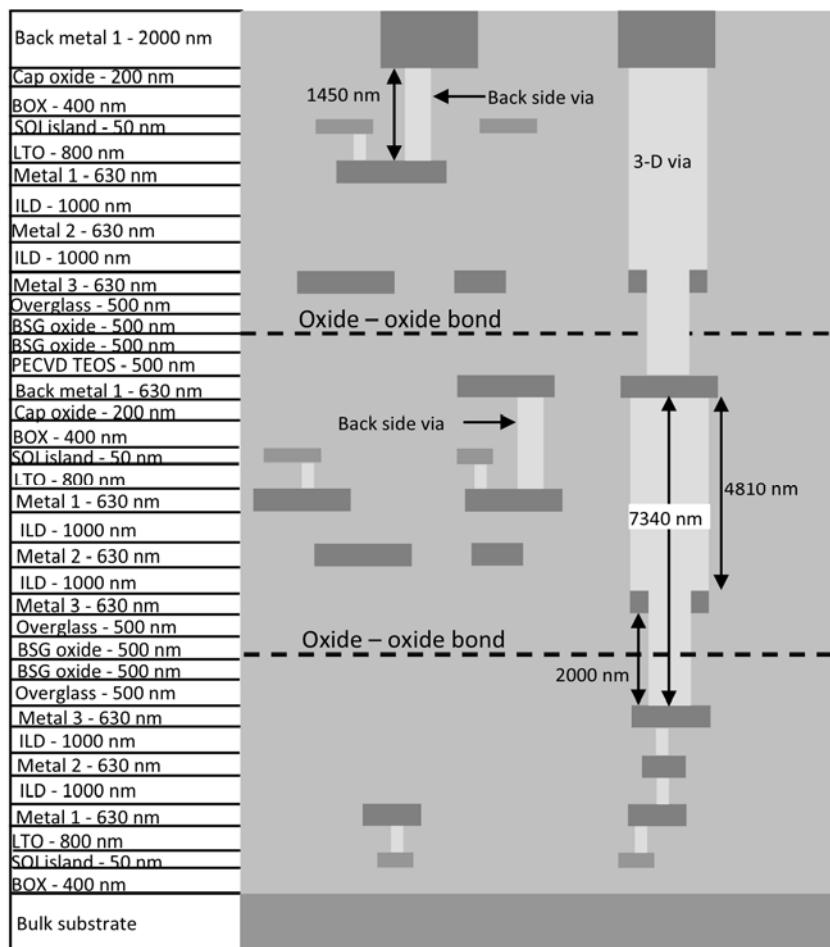

| Figure 8.15 Layer thicknesses within the three-tier structure [156] .....                                                                                | 222 |

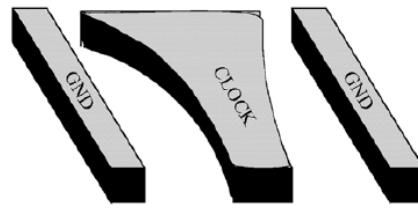

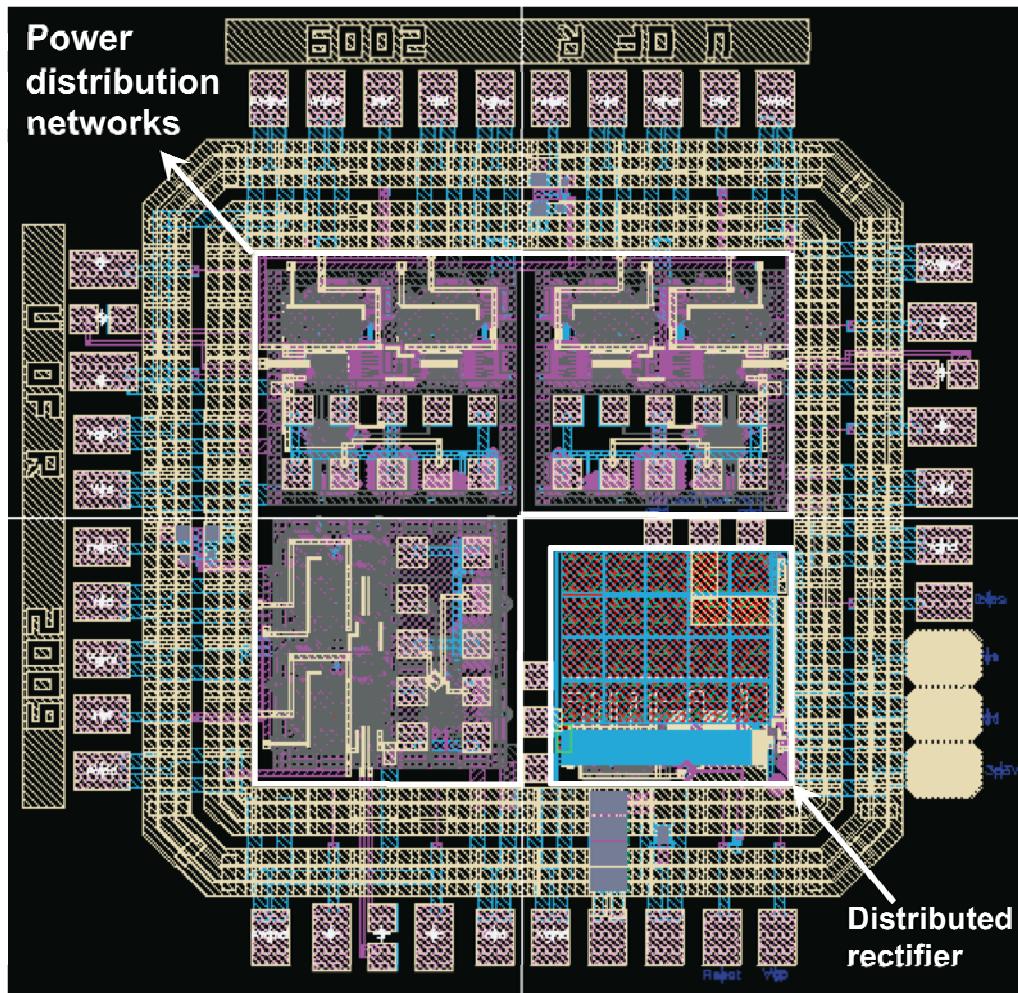

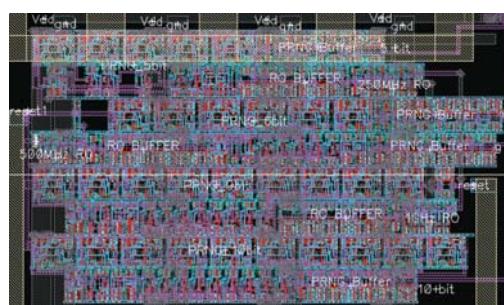

| Figure 8.16 Four blocks within the power delivery test circuit .....                                                                                     | 223 |

| Figure 8.17 Schematic illustration of the distributed rectifier circuit .....                                                                            | 224 |

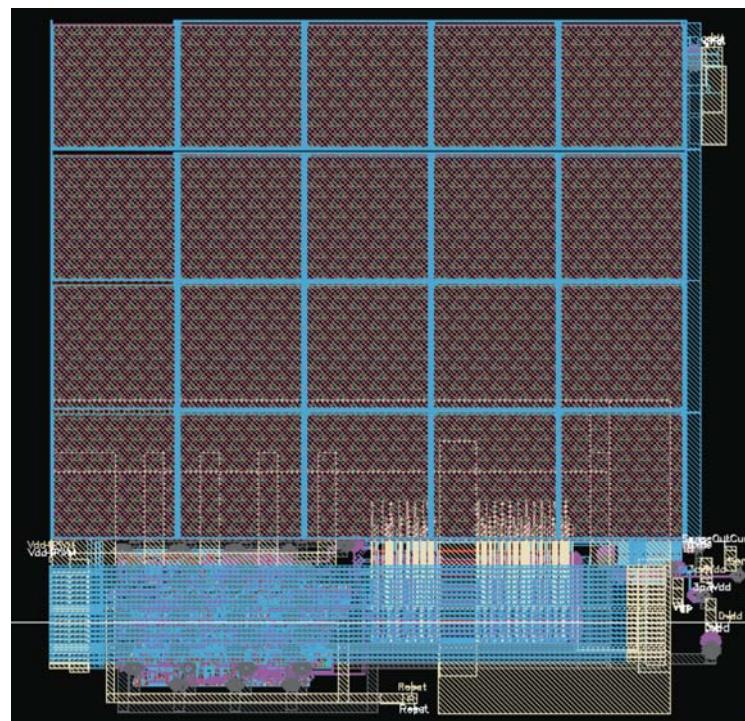

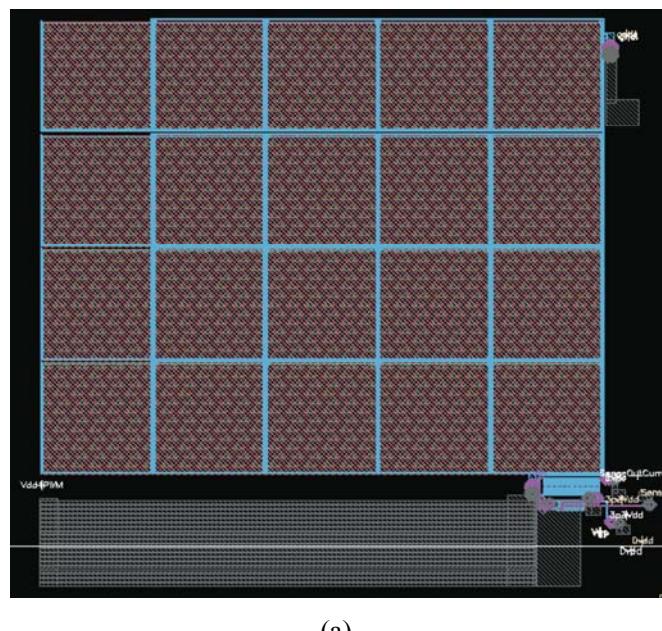

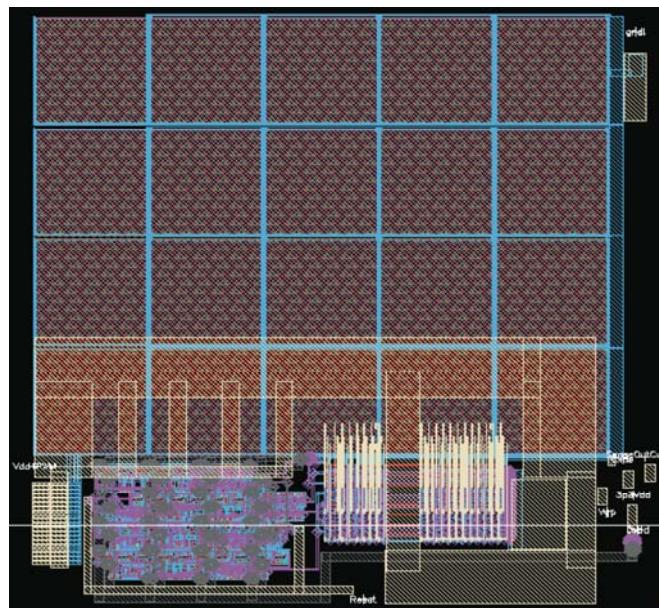

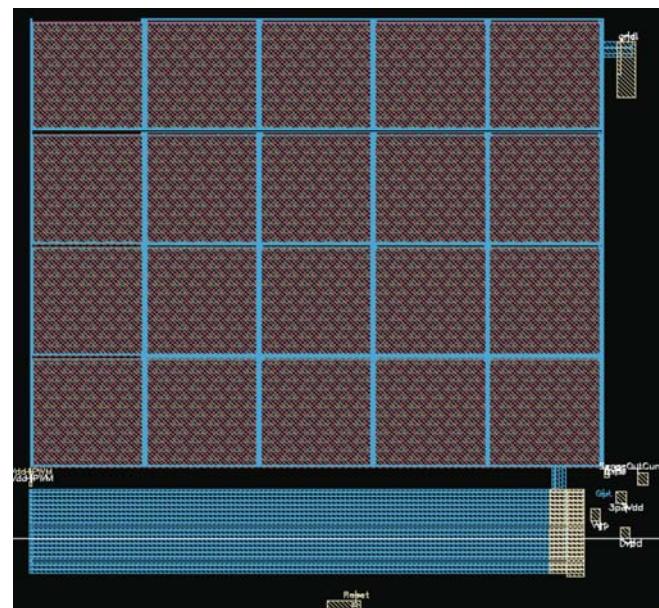

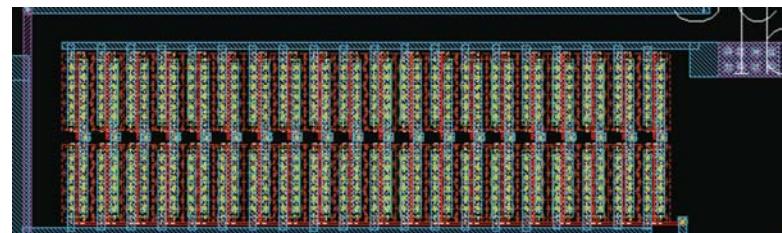

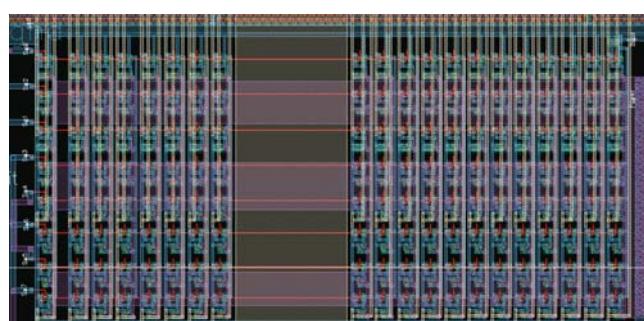

| Figure 8.18 Physical layout of the 3-D rectifier circuit (all three planes).....                                                                         | 224 |

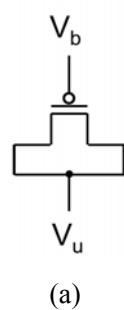

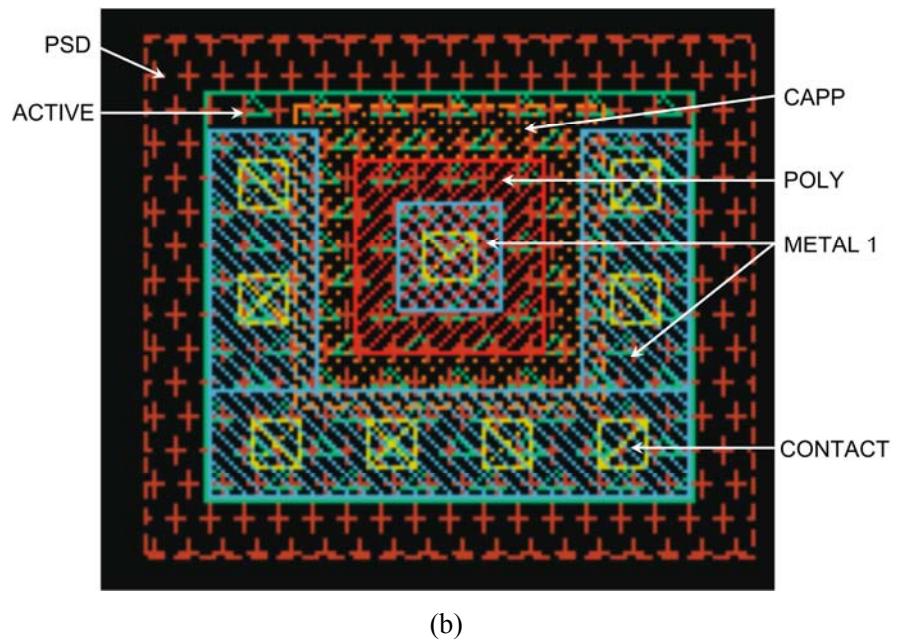

| Figure 8.19 P-type capacitor: (a) model, (b) layout.....                                                                                                 | 226 |

| Figure 8.20 Distributed rectifier structure: (a) plane A (bottom), (b) plane B (middle), (c) plane C (upper).....                                        | 227 |

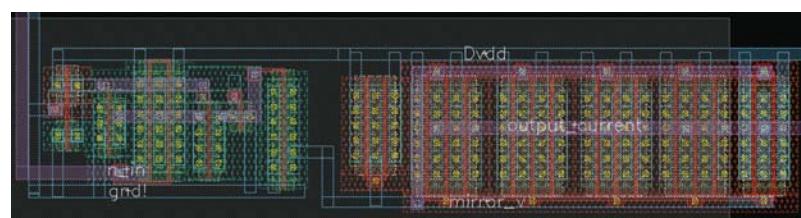

| Figure 8.21 Circuitry on plane A: (a) post-fabrication control circuit, (b) power supply noise measurement circuit .....                                 | 228 |

| Figure 8.22 Circuitry on plane B: (a) ring oscillators and buffers, (b) switched current loads .....                                                     | 228 |

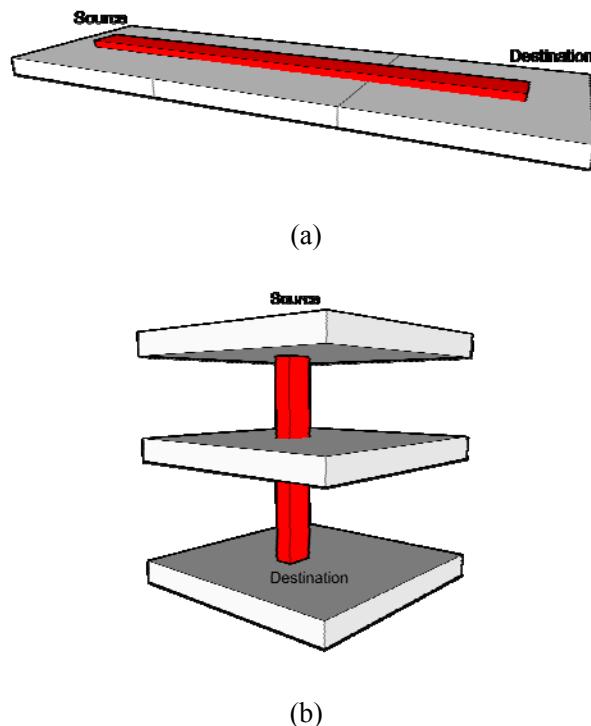

| Figure 9.1 2-D and 3-D cells: (a) 2-D horizontal plane, (b) three stacked planes .....                                                                   | 231 |

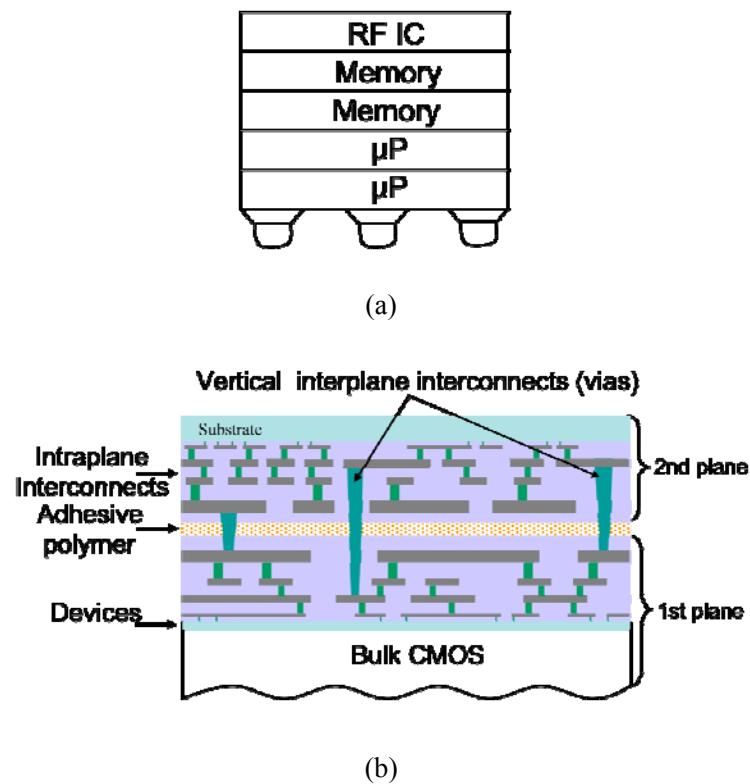

| Figure 9.2 3-D circuit: (a) multi-core processor combined from stacked planes, (b) cross section of a 3-D circuit .....                                  | 232 |

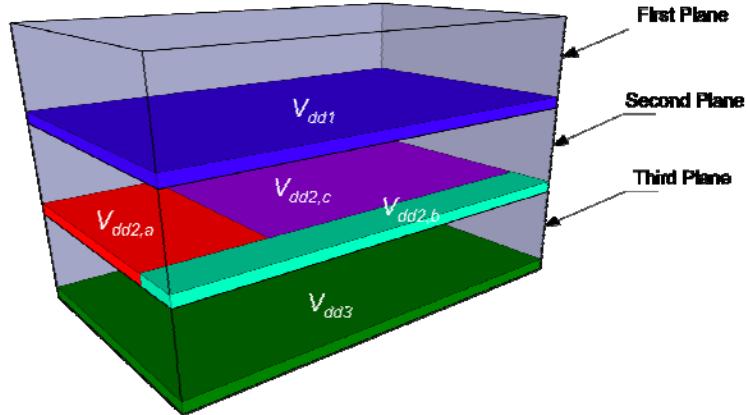

| Figure 9.3 Different partitions of voltage domains within a 3-D circuit .....                                                                            | 233 |

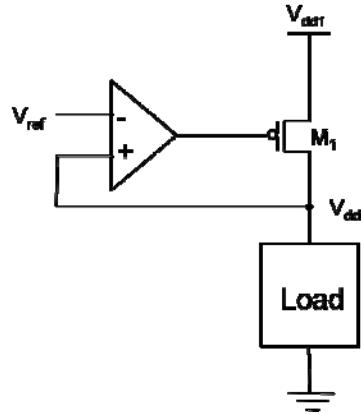

| Figure 9.4 Linear converter.....                                                                                                                         | 235 |

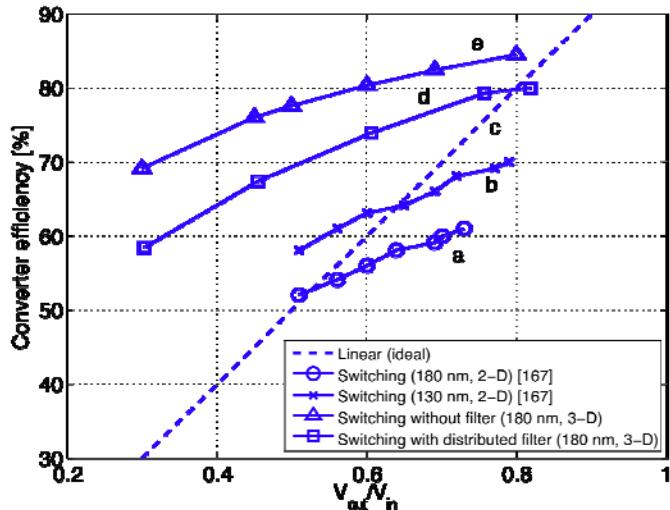

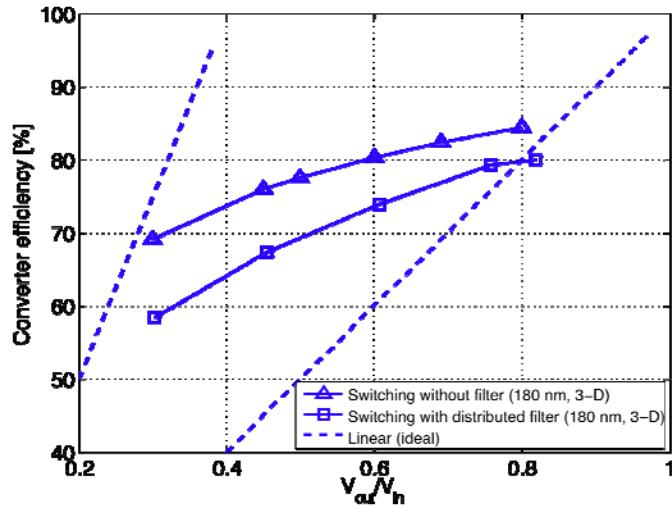

| Figure 9.5 Efficiency as a function of conversion ratios in different technologies .....                                                                 | 239 |

| Figure 9.6 Efficiency of linear and switching converters with dual- $V_{dd}$ input voltage (the two dashed lines represent the two input voltages) ..... | 241 |

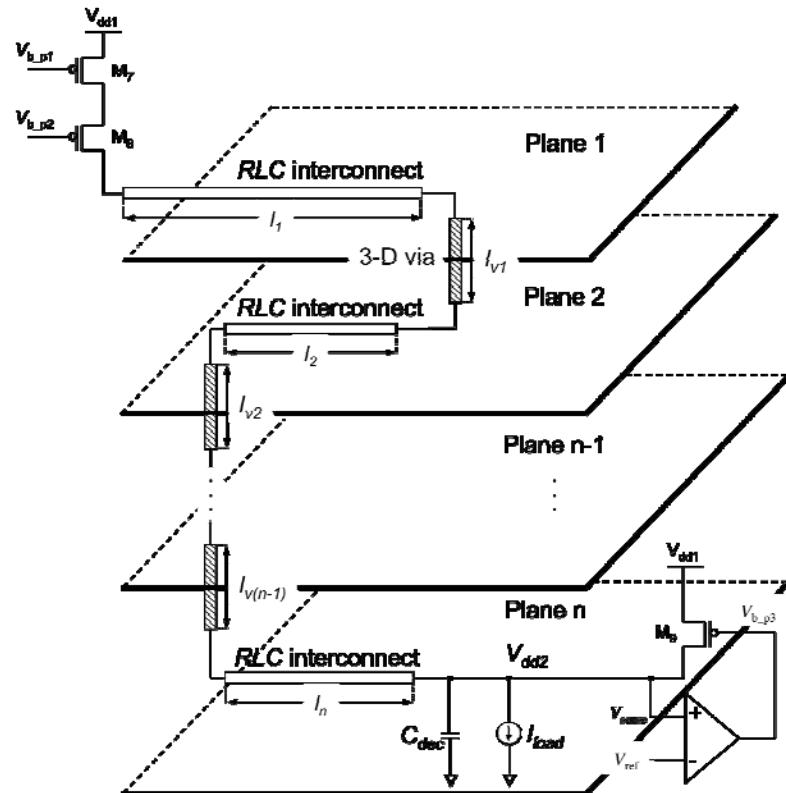

| Figure 9.7 Linear converter within a 3-D circuit .....                                                                                                   | 242 |

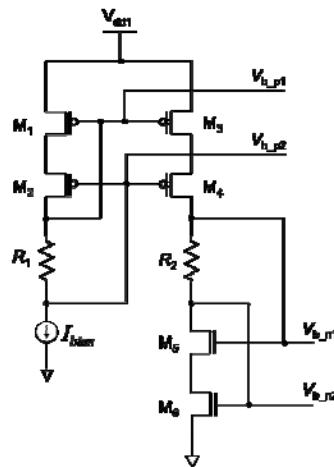

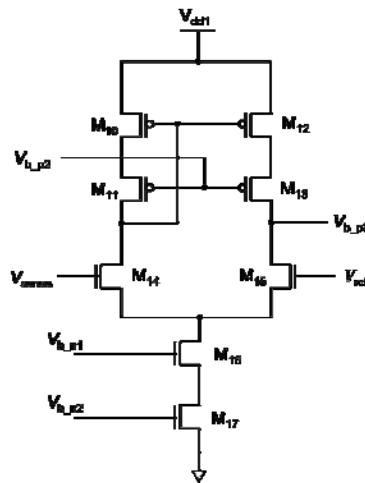

| Figure 9.8 Current mirror bias circuit .....                                                                                                             | 243 |

| Figure 9.9 A single-ended differential amplifier .....                                                                                                   | 243 |

|                                                                                                                                           |     |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

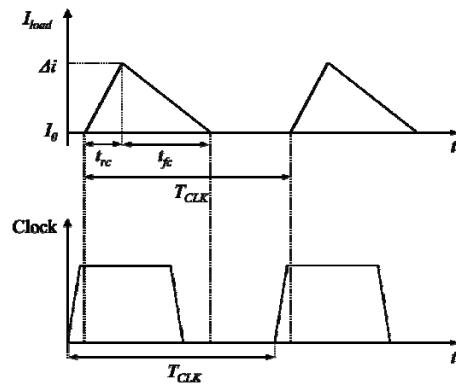

| Figure 9.10 A typical current load profile in a high performance processor .....                                                          | 244 |

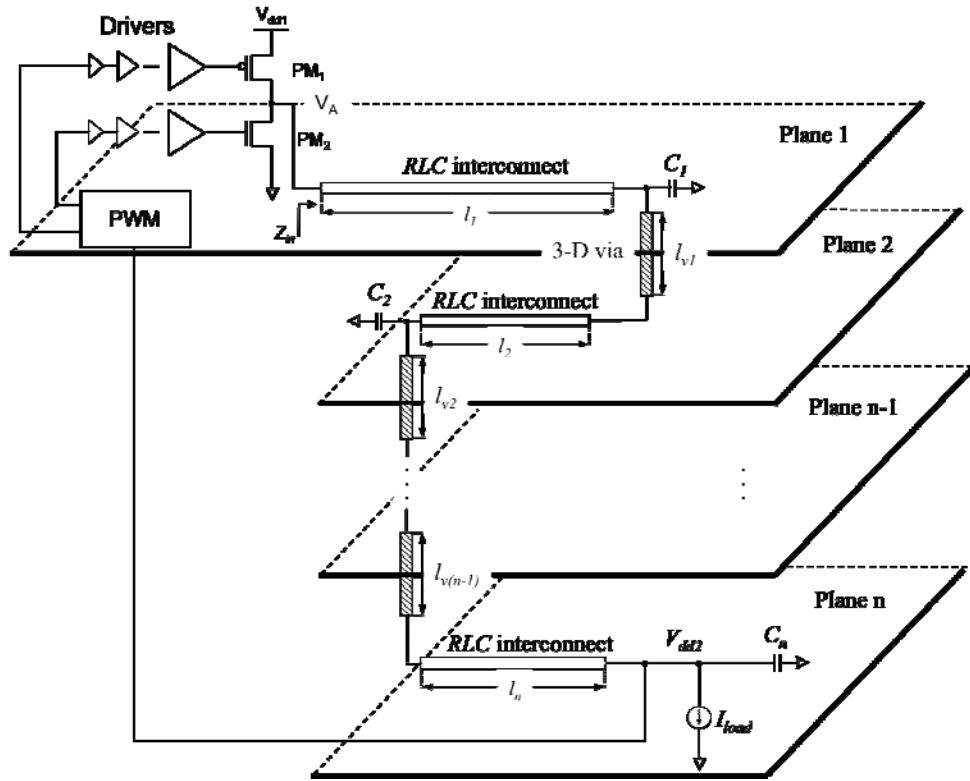

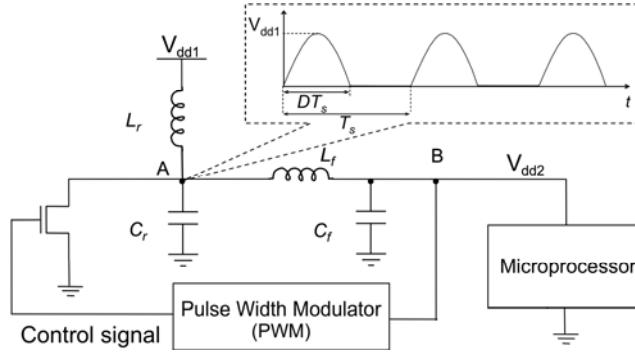

| Figure 9.11 A switching converter with the 3-D distributed rectifier.....                                                                 | 246 |

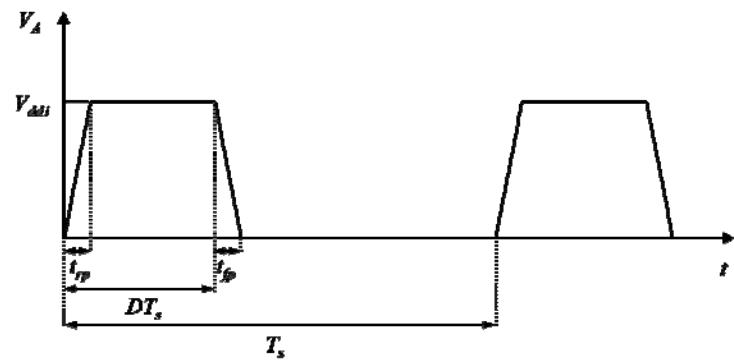

| Figure 9.12 Voltage signal at the input of the rectifier .....                                                                            | 246 |

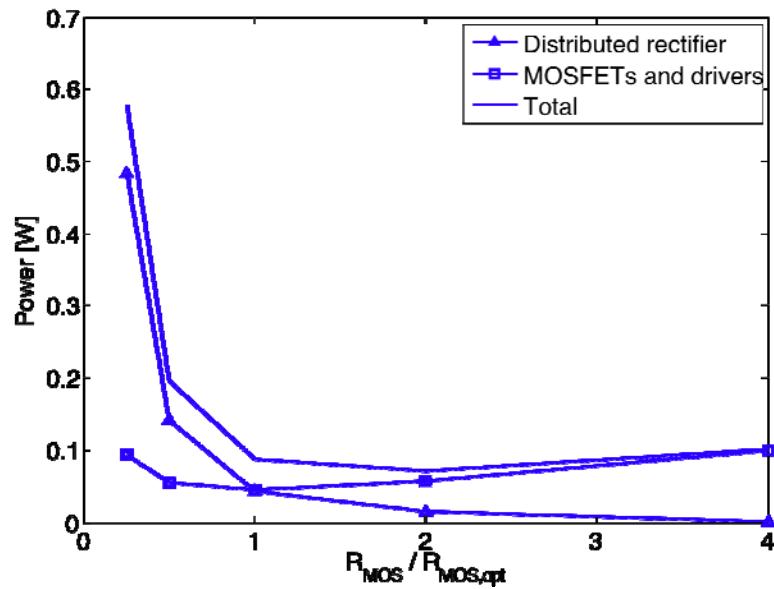

| Figure 9.13 Power breakdown of the power MOSFETs and rectifier filter, distributing a 200 mA peak current .....                           | 250 |

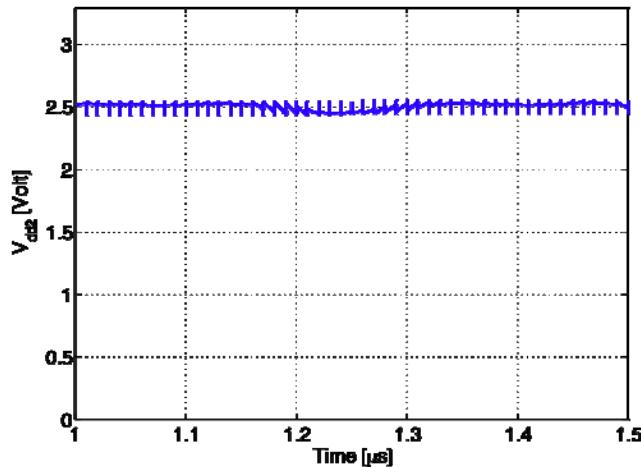

| Figure 9.14 Output voltage of the linear 3-D converter.....                                                                               | 253 |

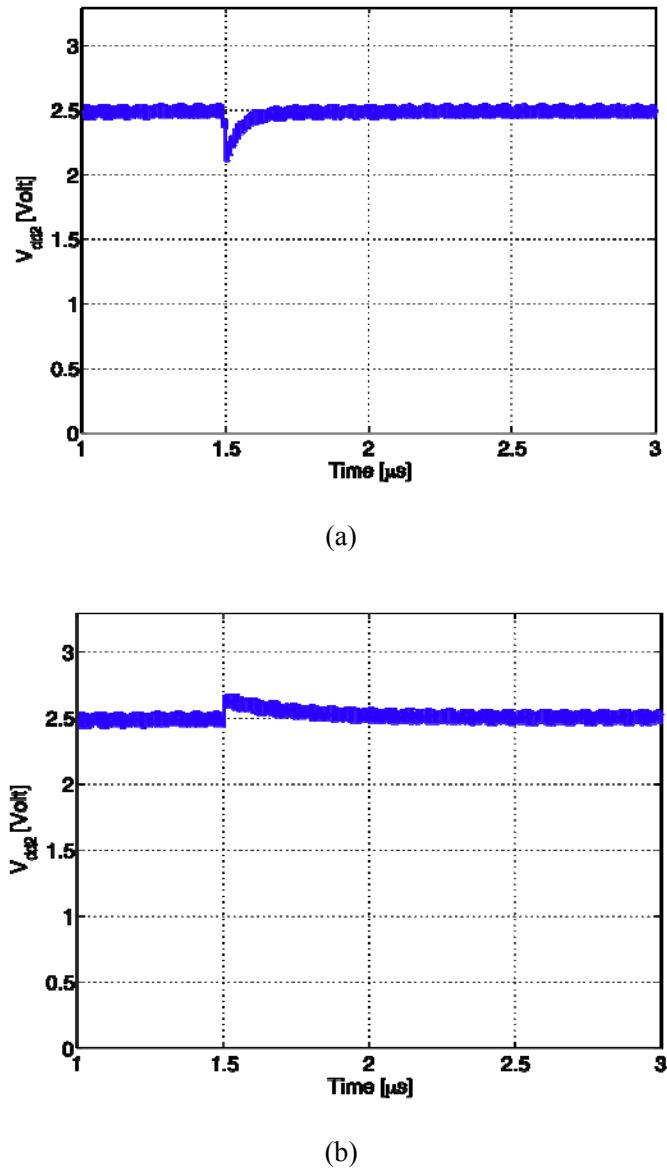

| Figure 9.15 Transient output voltage response: (a) 200 mA increase in current load, (b) 100 mA decrease in current load.....              | 254 |

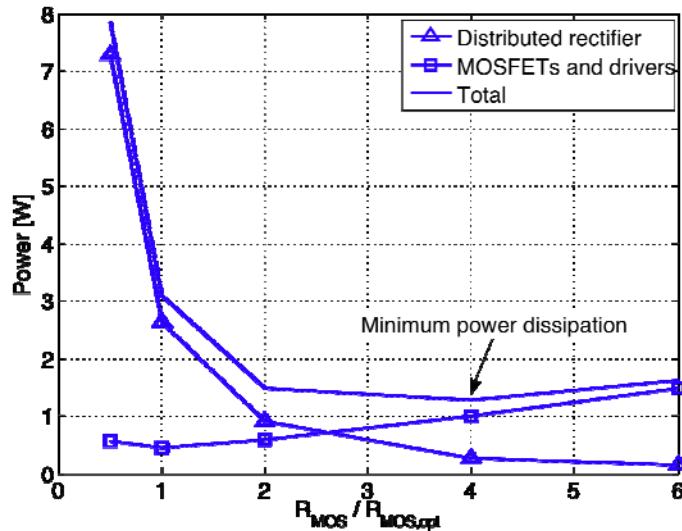

| Figure 9.16 Power components of the 3-D switching converter, distributing 2.5 Amperes of peak current .....                               | 255 |

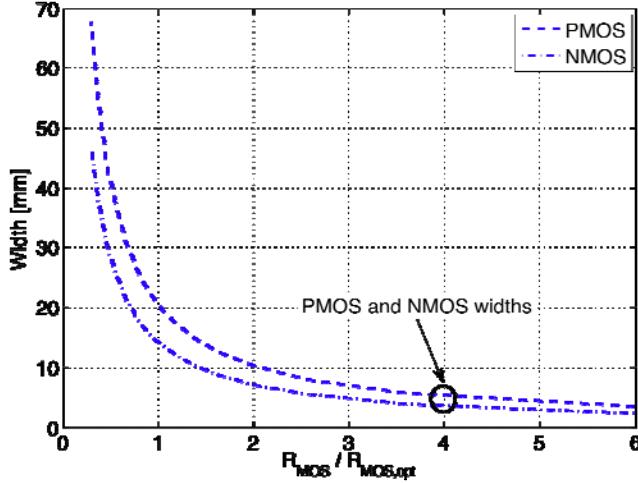

| Figure 9.17 Power MOSFET widths as a function of $R_{MOS}/R_{MOS,opt}$ .....                                                              | 256 |

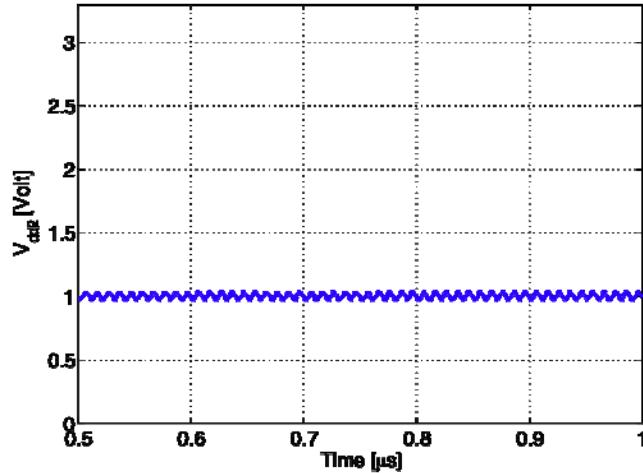

| Figure 9.18 Output voltage of the switching converter .....                                                                               | 257 |

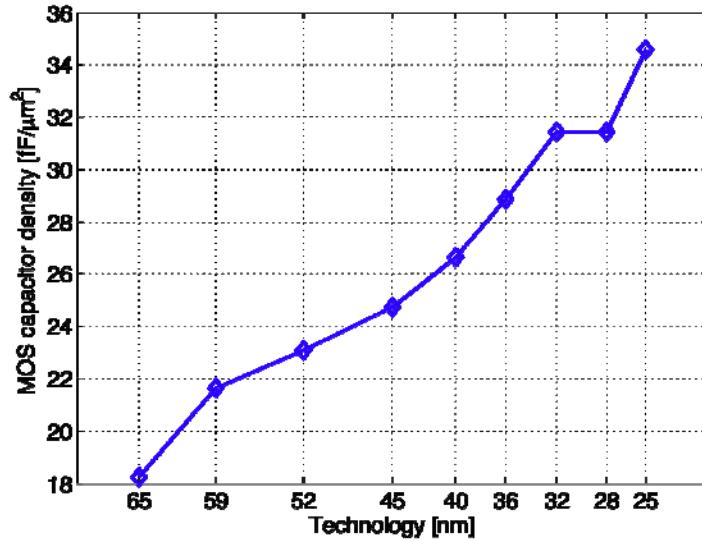

| Figure 9.19 MOS capacitor density for different technologies.....                                                                         | 258 |

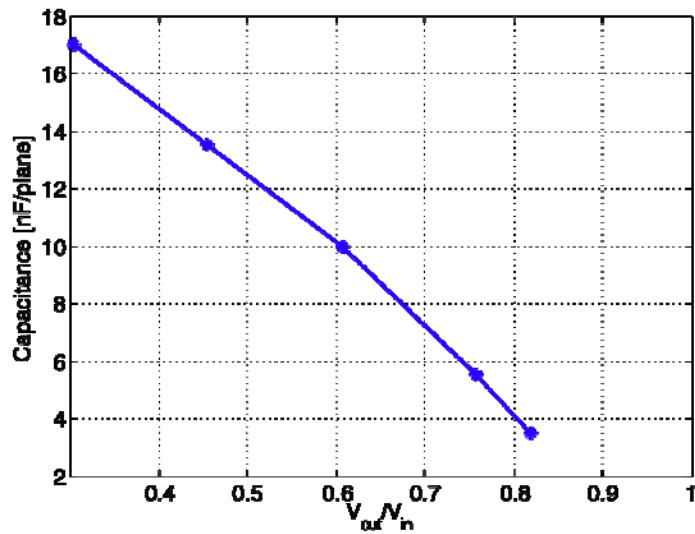

| Figure 9.20 Capacitance per plane as a function of $V_{out}/V_{in}$ .....                                                                 | 259 |

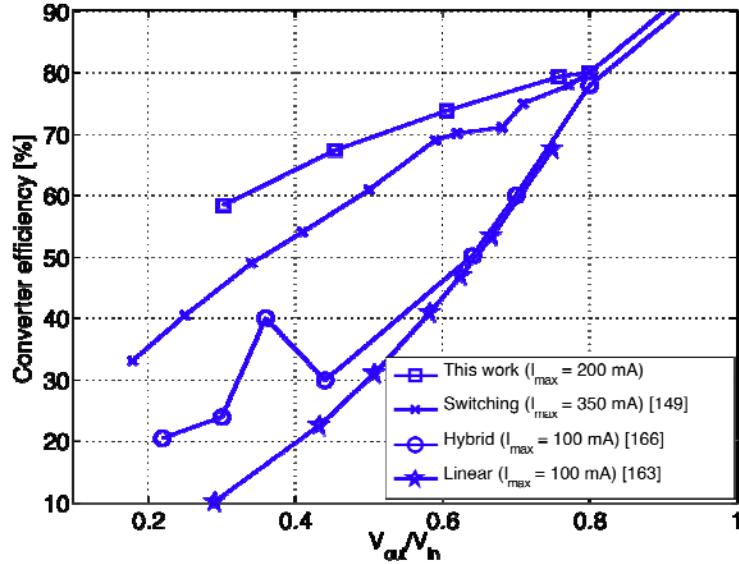

| Figure 9.21 Power efficiency of different approaches as a function of $V_{out}/V_{in}$ .....                                              | 260 |

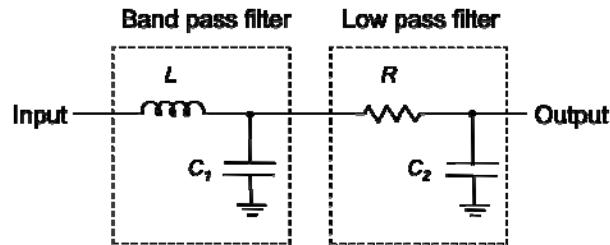

| Figure 11.1 Resonant buck converter .....                                                                                                 | 269 |

| Figure 11.2 Proposed filter within the buck converter.....                                                                                | 270 |

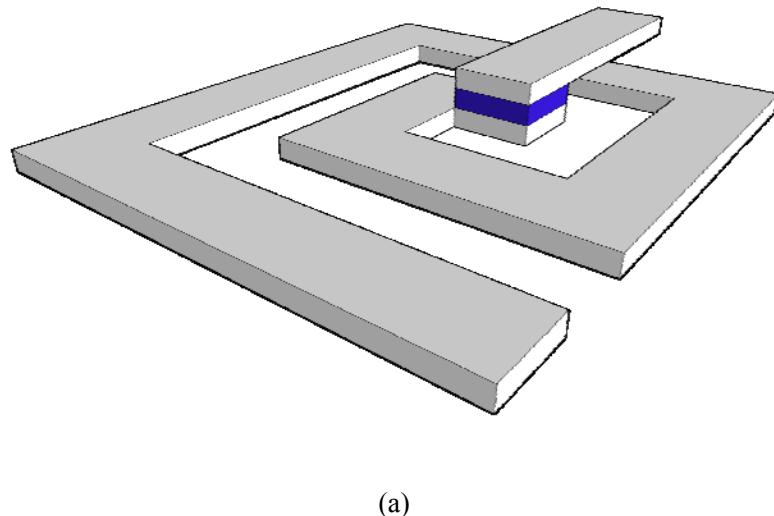

| Figure 11.3 On-chip inductor topologies in 3-D circuits: (a) planar 2-D inductor, (b) stacked planar 2-D and vertical 3-D inductors ..... | 272 |

# Chapter 1

## Introduction

*“So I toyed around in my mind: How can I do this experiment -- I was still being lazy; of course I could have evacuated the thing, but that was the sample that had been fixed up to put down in this thermos and it wasn't exactly conducive to evacuation; and it would have taken some time to do this.*

*I think I suggested, 'Why, John, we'll wax the point.' One of the problems was how do we do this, so we'd just coat the point with paraffin all over, and then we'd push it down on the crystal. The metal will penetrate the paraffin and make contact with the semi-conductor, but still we'd have it perfectly insulated from the liquid, and we'll put a drop of tap water around it. That day, we in principle, created an amplifier.”* -- Walter Brattain, January 1964 [1]

*“This circuit was actually spoken over and by switching the device in and out a distinct gain in speech level could be heard and seen on the scope presentation with no noticeable change in quality.”* -- Walter Brattain, December 24, 1947, lab notebook [1]

Events that took place at Bell Laboratories between November 17 and December 23, 1947 ignited the microelectronics era. Inventing the transistor led to the most important economic development of the 20<sup>th</sup> century: the information revolution. The driving force at the heart of what has proven to be an exceptionally productive industry is microelectronic integrated circuit technology. Since the invention of the integrated circuit in 1959 by Fairchild Semiconductor, the productivity of silicon integrated circuit technology has increased more than a billion fold while performance has increased more than one hundred thousand fold [2]. The accomplishments of the microelectronic integrated circuit technology can be attributed to the continuous scaling of semiconductor devices and the use of digital signal processing paradigms. Inevitably, the leading semiconductor technology, *i.e.*,

complementary metal-oxide-semiconductor (CMOS), is approaching both physical and economic limits that will severely restrain the current rate of advance.

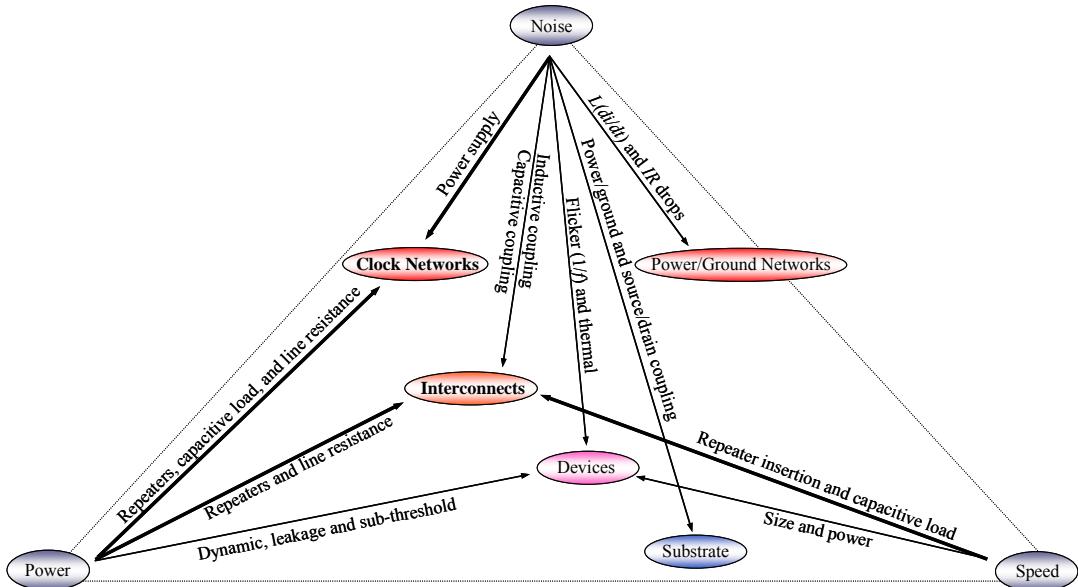

The taxonomy of the current challenges of very large scale integration (VLSI) systems and the relations among the sub-networks are shown in Figure 1.1. Noise, power, and speed are the three vertices of the triangle, indicating the primary performance criteria of digital VLSI circuits.

Figure 1.1 Taxonomy of digital VLSI challenges

The location inside the triangle of Figure 1.1 illustrating the primary design criteria in VLSI circuits, including clock networks, power/ground networks, interconnect, devices, and substrate, are analogous to the physical location within an integrated circuit. The arrows show the relationship among the different components and performance criteria, as well as the primary sources of performance degradation. Clock and interconnect distribution networks

(bold titles) and the related design issues (bold arrows) are the primary focus of this thesis with respect to noise, power, and speed.

## 1.1 Where Are We Heading? Trends and Predictions

The prediction of the international technology roadmap for semiconductors (ITRS) [3] ends in the year 2020 with more than a 100 billion transistors occupying a single IC with a typical transistor channel length of 10 nm. At this transistor size, semiconductor technologies have reached fundamental physical limitations, requiring the development of new technologies. In order to support a system with 10 nm length transistors, four requirements have been identified [4]:

- 1) Develop a cost efficient 10 nm fabrication technology;

- 2) Devise effective methods to handle low yield and defective devices;

- 3) Manage power and heat dissipation; and

- 4) Develop global interconnect technology to complement 10 nm transistors.

Interconnect networks included in the requirements for future technologies since interconnects do not scale well, consume a significant amount of power, and place severe limitations on processor clock speeds.

Clock signals in digital systems are simultaneously distributed to physically remote locations across an integrated circuit (IC). The clock signal provides a time reference that permits different parts of a circuit to operate in the correct order, thereby producing correct logical operation [7]. A clock signal is usually distributed from a common global source through metal interconnect networks and clock drivers, introducing delay. Unfortunately, the delay at every point on an IC cannot be precisely maintained, due to delay uncertainty [8].

Clock skew, which is the difference in the arrival time of the clock signal between sequentially-adjacent registers, can lead to catastrophic logic failure [7]. Another undesirable effect is clock jitter which occurs when the edges of the clock signal fluctuate in time. This behavior occurs due to imperfections in the clock generator and power supply noise [18]. Changes in the coupling capacitance and variations of the input capacitance of the registers also add random noise while increasing jitter.