Contents lists available at ScienceDirect

Microelectronics Journal

journal homepage: www.elsevier.com/locate/mejo

# Temperature–frequency boundary of cryogenic dynamic logic\*

## Nurzhan Zhuldassov<sup>\*</sup>, Eby G. Friedman

Department of Electrical and Computer Engineering, University of Rochester, Rochester, NY 14627, United States of America

## ARTICLE INFO

#### Keywords: Cryogenics Liquid helium temperature CMOS MOSFET Dynamic logic

## ABSTRACT

Cloud computing is increasing the demand for large scale, energy efficient, and fast computing systems. A CMOS circuit style satisfying these goals is dynamic logic. Since portability is not required for cloud computing centers, these systems can support cryogenic operation. Cryogenic operation eliminates the seminal issue of dynamic circuits, loss of the logic state due to leakage currents. At higher temperatures, static logic circuits are preferable since these circuits are unaffected by leakage currents. The operating temperature therefore affects the choice of circuit style: dynamic or static. The operation of dynamic CMOS circuits at different temperatures and the temperature at which dynamic logic is preferable to static logic are discussed here. Dynamic logic operating above 1.209 GHz can be used at temperatures up to 300 K, room temperature for a 160 nm technology node. At lower frequencies, static circuits should be used. Below 77 K, liquid nitrogen temperature, dynamic logic is stable above 29.7 MHz. At temperatures below 11 K, dynamic logic circuits operating above one hertz can be used. Since dynamic logic circuits operate at DC below 4.5 K, dynamic logic is preferable at any frequency below this temperature, including liquid helium temperature, 4.2 K.

#### 1. Introduction

Cloud computing requires high performance, energy efficient processors and can support cryogenic operation since portability is not desired. Higher frequency circuits, required in cloud computing systems, can utilize dynamic logic circuits for improved performance. As compared to static logic circuits, dynamic circuits are faster, lower power, and require less area. Room temperature (RT, 300 K) dynamic logic circuits cannot however operate at low frequencies due to leakage currents and are highly sensitive to noise. Dynamic circuits at RT operate correctly only above certain frequencies since the state is temporarily stored on a capacitor. This drawback makes developing complex systems based on dynamic circuits challenging, since low frequency operation of these circuits is a difficult issue. Dynamic circuits operating at cryogenic temperatures bypass these issues [1].

Significant improvements in performance can be achieved by cooling the environment [2]. Cryogenic electronics plays an important role in meteorology, quantum computing, high energy physics, and spacebased technologies. Furthermore, applications which require a high signal-to-noise ratio and/or receive weak input signals benefit when operated at cryogenic temperatures [3]. Cryogenic environments also avoid thermal runaway in semiconductors [4]. Nevertheless, static logic is preferable at RT since these circuits are not affected by leakage currents. At cryogenic temperatures, alternatively, dynamic circuits are preferable due to the aforementioned speed, power, and area advantages [5]. One issue is at what temperature does dynamic logic outperform static logic. In this paper, this temperature is determined for different frequencies. The key temperatures discussed in this paper are liquid helium temperature (LHT) 4 K, liquid nitrogen temperature (LNT) 77 K, and room temperature 300 K. The relative performance of dynamic logic at these temperatures is also discussed.

The paper is organized as follows: the characteristics of static and dynamic circuits are highlighted, and insight into MOSFET operation at cryogenic temperatures is summarized in Section 2. Dynamic circuit operation is characterized at different temperatures, and the temperature boundary at which dynamic logic should be used rather than static logic is discussed in Section 3. Some conclusions are offered in Section 4.

## 2. Background

Modern high complexity digital systems primarily deploy static logic. These systems can be enhanced by dynamic logic if operated at cryogenic temperatures. The temperature at which static logic should be replaced by dynamic logic depends upon the leakage currents; specifically, the subthreshold leakage current. The effects of subthreshold leakage current varies based on the style of logic circuit. Differences between static and dynamic logic are described in Section 2.1. The

\* Corresponding author.

https://doi.org/10.1016/j.mejo.2023.105763

Received 31 January 2023; Received in revised form 18 March 2023; Accepted 20 March 2023 Available online 21 March 2023 0026-2692/© 2023 Elsevier Ltd. All rights reserved.

<sup>\*</sup> This research is supported in part by the National Science Foundation under Grant No. CCF-1716091, IARPA under Grant No. W911NF-17-9-001, and by a grant from Qualcomm.

E-mail address: nzhuldas@ur.rochester.edu (N. Zhuldassov).

behavior of a MOSFET operating at cryogenic temperatures is reviewed in Section 2.2.

#### 2.1. Static and dynamic logic

Many types of MOSFET logic have been developed since the 1970's. These circuits primarily fall into two categories, static logic and dynamic logic.

To reduce power consumption, static logic can operate at lower frequencies or placed into standby mode [1]. Dynamic logic, alternatively, temporarily stores information on a capacitor. Gate and stray capacitances store the charge in these circuits, maintaining the logic state. Dynamic circuits require a periodic refresh since the charge decays over time. In dynamic circuits, the logic and memory elements are the same circuit, and the charge is transferred between capacitors. This signal flow between capacitors is controlled by an external signal. Thus, dynamic logic cannot operate at low frequencies due to the leakage of charge on the capacitors, exhibiting a low tolerance to noise [6]. Since leakage current at cryogenic temperatures becomes negligible, the charge on the capacitors requires significant time for the state to leak. This property allows dynamic logic to operate at lower frequencies, essentially DC at 4.2 K, which reduces the power consumption and supports low frequency, albeit cryogenic, testing. Dynamic logic requires less area and consumes less power than static logic. Furthermore, dynamic logic can operate at higher clock frequencies.

At cryogenic temperatures, a MOSFET exhibits enhanced physical properties such as higher transient currents, negligible leakage currents, and increased subthreshold slope [7]. These properties are discussed in the following subsection.

#### 2.2. MOSFET characteristics operating at cryogenic temperatures

Silicon MOSFETs operating at cryogenic temperatures exhibit significant improvements in performance and reliability as compared to room temperature operation. Since the late 1980's, cryogenic MOSFETs have, until recently, received little attention. Early studies on the behavior of MOSFETs at cold temperatures are described in [8–14]. The topic has once again become important due to the growing interest in cloud computing, enhancing the need for energy efficient, stationary computing platforms.

The carriers within the substrate of a CMOS transistor start to freeze out at 77 K [15]. With a voltage applied between the source and drain, the carriers, driven by energy from an applied electric field, form an inversion layer, becoming conductive. The mobility of the channel increases at lower temperatures due to less carrier scattering caused by lattice vibrations, but is limited by Coulombic scattering at lower gate voltages and surface roughness at higher gate voltages [16]. As a result, the speed of MOSFET devices operating at cryogenic temperatures is greater than at room temperature. For example, a 62% improvement in speed has been observed in a ring oscillator operating at 4 K [15]. A MOSFET operating at cryogenic temperatures exhibits the following advantages as compared to 300 K behavior: negligible leakage currents, higher subthreshold slope, insignificant electromigration, fewer thermal induced failures such as oxide degradation, higher transconductance, and no latch-up [15].

The MOSFET considered in this study is a 160 nm CMOS transistor [5]. The transistor has a width of 2.32  $\mu$ m and a channel length of 160 nm with a thin oxide. The drain current  $I_D$  at 4.2 K is 40% larger than the drain current at room temperature due to the higher carrier mobility. As compared to room temperature operation, the threshold voltage increases from 0.55 V to 0.7 V and the subthreshold slope (SS) is 3.8 times steeper at LHT than RT, increasing from 87.0 mV/decade to 22.8 mV/decade [17].

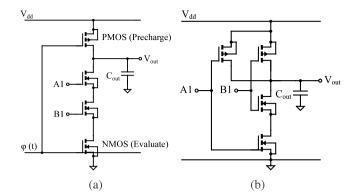

Fig. 1. Two input NAND gate, (a) dynamic logic, and (b) static logic.

#### 3. Temperature breakpoint of static and dynamic logic

The operating temperature at which dynamic logic (Fig. 1(a)) is preferable to static logic (Fig. 1(b)) is discussed here as the breakpoint (or boundary) temperature. The range of temperature being considered is between 4.2 K (LHT) and 300 K (RT). The simulation setup is presented in Section 3.1. Operation of dynamic circuits at LHT, LNT, RT, and at certain transitional temperatures are described in Section 3.2. The breakpoint temperatures are also described in Section 3.2 at different frequencies.

#### 3.1. Simulation setup for evaluating dynamic logic

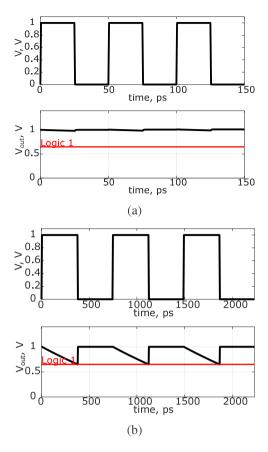

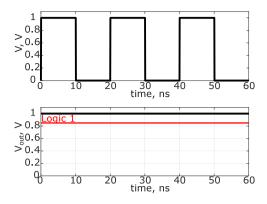

A two input dynamic NAND gate is shown in Fig. 1(a). The circuit consists of four transistors and a capacitive load,  $C_{out} = 0.1$  fF [18]. The voltage supply  $V_{DD}$  is 1 V. The NMOS logic network behaves as a composite switch. The output voltage  $V_{out}$  is stored on a capacitive load  $C_{out}$ . As previously noted, at RT,  $V_{out}$  decays due to leakage currents. Operation of a dynamic NAND gate where the leakage current is a significant issue is exemplified by the following case. In a dynamic NAND gate during the precharge phase (see Fig. 1(a)), A1 is set to 1 and B1 is set to 0, while the voltage across the output charges to logic 1. During the evaluation phase, although some NMOS transistors are on, the output remains at logic 1 since a signal is only transmitted if both A1 and B1 are on. The clock signal and output voltage at RT operating at a frequency of 20 GHz are shown in Fig. 2(a). During the evaluation phase, the output voltage degrades due to leakage currents. If the frequency is sufficiently high, the voltage does not drop below the noise margin high (which, in this example, is 0.65 V at RT, labeled in Fig. 2 as logic 1).

The Phillips MOS11 HSpice model is used to model a 160 nm CMOS transistor operating at cryogenic temperatures [5]. Temperature dependent parameters, such as the threshold voltage, subthreshold slope factor, and carrier mobility, have been modified to fit experimental data. The subthreshold slope factor n for LHT, LNT, and RT, and the carrier mobility are extracted from [17]. The subthreshold slope factor changes exponentially [17,19] and is extrapolated at other temperatures. In thin oxide CMOS considered here, the kink effect is not present and therefore ignored [17]. For smaller technology nodes, the precise breakpoint temperature changes. However, as the temperature dependent characteristics of CMOS devices experience similar changes at cryogenic temperatures [7], the cryogenic behavior of the 160 nm CMOS technology model [5] used here can be extended to more deeply scaled, thin oxide CMOS technologies.

Subthreshold leakage current, the primary power loss mechanism at cryogenic temperatures, can be modeled [7] as

$$I_{DS} \approx I_{S} e^{\frac{q(V_{GS} - V_{T})}{nkT}} \left( 1 - e^{-\frac{qV_{DS}}{kT}} \right), \tag{1}$$

Fig. 2. Dynamic circuit operating at RT, (a) 20 GHz, and (b) 1.344 GHz. Note that the circuit operates normally at 20 GHz while 1.344 GHz is the minimum operational frequency.

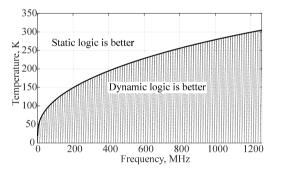

Fig. 3. Breakpoint temperature at which dynamic logic is preferable to static logic at different frequencies, 160 nm CMOS technology.

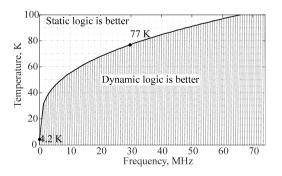

Fig. 4. Breakpoint temperature below 100 K at which dynamic logic is preferable to static logic at different frequencies.

Table 1

| Temperature | Minimum frequency |            | % Error |

|-------------|-------------------|------------|---------|

|             | (Simulated)       | (Analytic) |         |

| 300 K (RT)  | 1.209 GHz         | 1.344 GHz  | 10.0%   |

| 90 K        | 49.9 MHz          | 56.8 MHz   | 12.1%   |

| 77 K (LNT)  | 29.7 MHz          | 33.6 MHz   | 11.6%   |

| 4.2 K (LHT) | DC                | DC         | -       |

where  $I_S$  is the current at the threshold voltage of the device, q is the charge of an electron, n is the subthreshold slope factor, k is the Boltzmann constant, and T is the absolute temperature. Note that  $I_{DS}$  is exponentially dependent on the threshold voltage, temperature, and subthreshold slope factor.

To determine the decay time, the subthreshold current, described by (1), is equated to the capacitor current,

$$I_{S} e^{\frac{-qV_{T}}{nkT}} \left( 1 - e^{-\frac{qV_{out}}{kT}} \right) = C_{out} \frac{\partial V_{out}}{\partial t}.$$

(2)

The decay time t of capacitor  $C_{out}$  is

4:66

$$t = \frac{C_{out}kT}{I_S q} e^{\frac{qV_T}{nkT}} \ln\left[e^{\frac{q}{kT}} \left(V_{dd} - V_{out}\right) - 1\right].$$

(3)

The threshold voltage is highly temperature dependent due to the carrier freeze out effect and subsequent changes in the Fermi potential [20]. The threshold voltage increases by about 30% when the temperature decreases from 300 K to 4 K [17]. For a 1 V system, the threshold voltage at RT is 0.25 V, and at LHT is 0.33 V [21].

#### 3.2. Temperature breakpoint

Dynamic circuit operation at a specific temperature depends upon the frequency of operation. If the dynamic logic cannot operate at a specific temperature and frequency due to leakage currents, static logic is preferred. This temperature–frequency boundary where the output voltage of the dynamic logic drops below the noise margin high is the breakpoint temperature. To determine this breakpoint temperature, (3) is evaluated at different temperatures and frequencies.

Based on (3), the decay time of  $V_{out}$  for  $V_T = 0.25$  V and T = 300 K is 0.414 ns. The minimum frequency to correctly operate at room temperature is analytically determined to be 1.209 GHz. In simulation, the minimum frequency of operation is 1.344 GHz, within 11% of the analytically determined frequency. The simulated output voltage at this frequency is shown in Fig. 2(b). During the evaluation phase, the charge on the output capacitor drops below the threshold voltage. In the next stage, this voltage is no longer at logic 1. 1.344 GHz represents a decay time of 0.372 ns. The difference between the simulation and analytic solutions for the decay time is 10%. These delay times are listed in Table 1.

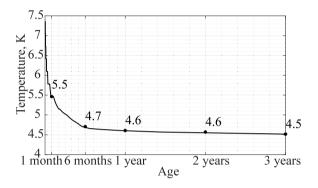

The breakpoint temperature at different frequencies is shown in Fig. 3. The breakpoint temperature–frequency characteristic is exponential, as described by (3). A scaled version of the temperature–frequency characteristic at temperatures below 100 K is shown in Fig. 4.

As noted in Fig. 3, when operating at RT at frequencies below 1.344 GHz, the charge leaks away before arrival of the following clock pulse. At these lower frequencies, static logic is necessary. At lower temperatures, the frequency at which dynamic logic functions correctly can be decreased. As the temperature approaches liquid nitrogen, the breakpoint curve becomes steep due to the exponential nature of the subthreshold leakage current. At 77 K, dynamic logic should be used when operating at frequencies above 29.7 MHz.

Note that the frequency can be further reduced at lower temperatures, allowing dynamic logic at 4.2 K to operate at DC. An example of this condition is shown in Fig. 5. The circuit at LHT exhibits no drop in

Fig. 5. Dynamic circuit operating at 50 MHz at LHT. The circuit operates properly at LHT.

Fig. 6. Age of application at different temperatures to maintain DC operation.

voltage at 50 MHz, agreeing with the analytic solution. Dynamic logic is therefore preferable at LHT.

DC operation, however, is available at temperatures higher than LHT. The charge leakage time at different temperatures is shown in Fig. 6. The concept of application age is introduced here, where the age of the application indicates the time during which a circuit has to retain sufficient charge to maintain the logic state. As shown in Fig. 6, the application age is one month at 5.5 K, one year at 4.6 K, and three years at 4.5 K. Therefore, if system operation requires an age of three years, the circuit should be operated at or below 4.5 K.

Summarizing, as the frequency increases from 1 Hz to 1.209 GHz, the breakpoint temperature increases, respectively, from 11 K to 300 K, as shown in Fig. 3. Therefore, if the circuit operates below 1.209 GHz at a temperature above 300 K, static logic should be used. Dynamic logic can operate at 1 Hz at temperatures below 11 K and at DC below 4.5 K, as illustrated in Figs. 4 and 6.

## 4. Conclusions

Interest in cloud computing has been growing, demanding greater energy efficiency. Due to the stationary nature of these platforms, cloud computing can support cryogenic operation. This characteristic suggests the use of dynamic logic in cloud computing centers operating at cryogenic temperatures to support high frequencies while dissipating low power. The primary objective of this paper is to clarify at which temperature and frequency dynamic logic is preferable to static logic.

Dynamic logic operating at temperatures ranging from liquid helium to room temperature is considered here. The performance of dynamic circuits operating at the transitional temperature boundary between room temperature and liquid helium temperature is evaluated at several frequencies. At liquid helium temperature, dynamic circuits can operate at DC. Dynamic logic is therefore preferable over static logic at any frequency if operated at LHT. At higher temperatures, the time during which the charge leaks away is exponentially less. Furthermore, if DC operation requires holding the charge for one month or less, the temperature can be increased from LHT to 5.5 K. Dynamic logic is preferable at temperatures below 11 K when operated above 1 Hz. At liquid nitrogen temperature, dynamic logic is preferable when operating above 29.7 MHz. Above 1.209 GHz, dynamic logic can be used at any temperature.

#### CRediT authorship contribution statement

**Nurzhan Zhuldassov:** Conceptualization, Methodology, Software, Validation, Formal analysis, Investigation, Writing – original draft, Writing – review & editing, Visualization. **Eby G. Friedman:** Resources, Writing – review & editing, Supervision, Project administration, Funding acquisition.

#### Declaration of competing interest

The authors declare the following financial interests/personal relationships which may be considered as potential competing interests: Eby G. Friedman reports a relationship with National Science Foundation that includes: funding grants. Eby G. Friedman reports a relationship with Intelligence Advanced Research Projects Activity that includes: funding grants. Eby G. Friedman reports a relationship with QUALCOMM Inc that includes: funding grants.

#### Data availability

No data was used for the research described in the article

#### References

- [1] J.P. Uyemura, CMOS Logic Circuit Design, Springer, 2002.

- [2] A. Akturk, J. Allnutt, Z. Dilli, N. Goldsman, M. Peckerar, Device modeling at cryogenic temperatures: Effects of incomplete ionization, IEEE Trans. Electron Devices 54 (11) (2007) 2984–2990.

- [3] A. Van Der Ziel, Thermal noise in field-effect transistors, Proc. IRE 50 (8) (1962) 1808–1812.

- [4] Y. Feng, X. Meng, S. Whiteley, T. Van Duzer, K. Fujiwara, H. Miyakawa, N. Yoshikawa, Josephson-CMOS hybrid memory with ultra-high-speed interface circuit, IEEE Trans. Appl. Supercond. 13 (2) (2003) 467–470.

- [5] N. Zhuldassov, E.G. Friedman, Cryogenic dynamic logic, in: Proceedings of the IEEE International Symposium on Circuits and Systems, 2020, pp. 1–5.

- [6] L. Wanhammar, DSP Integrated Circuits, Elsevier, 1999.

- [7] H. Homulle, L. Song, E. Charbon, F. Sebastiano, The cryogenic temperature behavior of bipolar, MOS, and DTMOS transistors in standard CMOS, IEEE J. Electr. Dev. Soc. 6 (2018) 263–270.

- [8] A. Jonscher, Semiconductors at cryogenic temperatures, Proc. IEEE 52 (10) (1964) 1092–1104.

- [9] R.W. Keyes, E.P. Harris, K. Konnerth, The role of low temperatures in the operation of logic circuitry, Proc. IEEE 58 (12) (1970) 1914–1932.

- [10] G.B. Craig, S.S. Sesnic, Investigations of Field Effect Transistors at Cryogenic Temperatures, Technical Report, Texas University Austin Electronics Research Center, 1970.

- [11] S. Sesnic, G. Craig, Thermal effects in JFET and MOSFET devices at cryogenic temperatures, IEEE Trans. Electron Devices 19 (8) (1972) 933–942.

- [12] A.R. Tokuda, P. Lauritzen, MOSFET thresholds at 4.2 K induced by cooling bias, IEEE Trans. Electron Devices 21 (9) (1974) 606–607.

- [13] B. Lengeler, Semiconductor devices suitable for use in cryogenic environments, Cryogenics 14 (8) (1974) 439–447.

- [14] R.L. Maddox, P-MOSFET parameters at cryogenic temperatures, IEEE Trans. Electron Devices 23 (1) (1976) 16–21.

- [15] Y. Feng, P. Zhou, H. Liu, J. Sun, T. Jiang, Characterization and modelling of MOSFET operating at cryogenic temperature for hybrid superconductor-CMOS circuits, Semicond. Sci. Technol. 19 (12) (2004) 1381.

- [16] J.C. Whitaker, The Electronics Handbook, CRC Press, 2005.

- [17] R.M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu, F. Sebastiano, Characterization and compact modeling of nanometer CMOS transistors at deep-cryogenic temperatures, IEEE J. Electr. Dev. Soc. 6 (2018) 996–1006.

- [18] S. Garg, T.K. Gupta, Low power domino logic circuits in deep-submicron technology using CMOS, Eng. Sci. Technol., Int. J. 21 (4) (2018) 625–638.

### N. Zhuldassov and E.G. Friedman

- [19] A. Beckers, F. Jazaeri, A. Ruffino, C. Bruschini, A. Baschirotto, C. Enz, Cryogenic characterization of 28 nm bulk CMOS technology for quantum computing, in: Proceedings of the European Solid-State Device Research Conference, 2017, pp. 62–65.

- [20] Z. Chen, H. Wong, Y. Han, S. Dong, B. Yang, Temperature dependences of threshold voltage and drain-induced barrier lowering in 60 nm gate length MOS transistors, Microelectron. Reliab. 54 (6–7) (2014) 1109–1114.

- [21] A. Beckers, F. Jazaeri, C. Enz, Cryogenic MOSFET threshold voltage model, in: Proceedings of the IEEE European Solid-State Device Research Conference, 2019, pp. 94–97.