# Design Methodologies for On-Chip Inductive Interconnect

by

Magdy A. El-Moursy

Submitted in Partial Fulfillment

of the

Requirements for the Degree

Doctor of Philosophy

Supervised by

Professor Eby G. Friedman

Department of Electrical and Computer Engineering

School of Engineering and Applied Sciences

The College

University of Rochester

Rochester, New York

2004

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

---

UMI Microform 3142291

Copyright 2004 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against

unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company

300 North Zeeb Road

P.O. Box 1346

Ann Arbor, MI 48106-1346

# Dedication

This work is dedicated to my parents: Professor Dr. Naima A. Ahmed and Professor Dr. Ali A. El-Moursy.

# Curriculum Vitae

The author was born in Cairo, Egypt in 1974. He attended the school of engineering, Department of Electronics and Communications from 1991 to 1996 where he received the B.S. degree in electronics and communications engineering (with honors) and the Master's degree in computer networks from Cairo University, Cairo, Egypt, in 1996 and 2000, respectively, and the Master's degree in electrical engineering from University of Rochester, Rochester, NY, USA, in 2002. He is a Ph.D. candidate in the area of high-performance VLSI/IC design at the University of Rochester, Rochester, NY, USA. In summer of 2003, he was with STMicroelectronics, Advanced System Technology, San Diego, CA, USA.

His research interest is in interconnect design and related circuit level issues in high performance VLSI circuits, clock distribution network design, and low power design. He is the author of about 20 papers and two book chapters in the fields of high speed and low power CMOS design techniques and high speed interconnect.

# Acknowledgments

I would like to express my deep gratefulness and thanks to my supervisor Professor Eby G. Friedman who gave me a lot of his time, concern, and support both technically and socially. Without him, my research was not going to appear in this professional style and form. His advice was always giving me a light to follow the correct way. I will always remember his help and support, which made my Ph.D. study really an interesting and joyful experience which I will never forget.

My thanks to my colleagues, Dr. Volkan Krusun, Dr. Dimitrios Velenis, and Boris Andreev, with whom I enjoyed my research. Special thanks are dedicated to Dr. Andrey V. Mezhiba for the useful discussions, which helped me a lot. I would also like to thank my brother, Ali A. El-Moursy, who is a graduate student in University of Rochester. Ali shared with me all the good and bad moments in my study and life in Rochester.

I would like also to thank everyone in the Electrical and Computer Engineering Department at University of Rochester the secretary, the admin-

istration, and the professors. My special thanks to Professor David A. Albonesi, Professor Martin Margala, Professor Wendi Heinzelman, and Professor Robert C. Waag from whom I have learned a lot and Professor Sandhya Dwarkadas for serving on my proposal and defense committees.

At the end I would like to thank RuthAnn Williams for her professional help to finish all the paper work very accurately and in time. She adds nice spirit to the lab.

# Abstract

With the decrease in feature size of CMOS integrated circuits, interconnect design has become an important issue in high speed, high complexity integrated circuits (IC). Different design methodologies have been proposed to improve circuit performance. Wire sizing, driver sizing, and wire shaping are common techniques to enhance circuit performance.

With increasing signal frequencies and the corresponding decrease in signal transition times, the interconnect impedance can behave inductively. Different design methodologies under an inductive environment are described in this dissertation. Including line inductance in the design process can enhance both the delay and power as well as improve the accuracy of the overall design process.

Line inductance introduces new tradeoffs in interconnect and driver sizing to decrease the circuit delay. An accurate solution for the optimum line width is described that minimizes the total transient power dissipated by a CMOS circuit. Furthermore, interconnect inductance introduces a shielding

effect which decreases the effective capacitance seen by the driver of a circuit, reducing the gate delay. Ignoring the line inductance overestimates the circuit delay, inefficiently oversizing the circuit driver. Considering line inductance in the design process also saves gate area, reducing the dynamic power dissipation.

An alternative technique to reduce the propagation delay in long interconnects is non-uniform wire sizing or wire shaping. In this dissertation, the optimum wire shape for the minimum signal propagation delay across an *RLC* line is shown to have a general exponential form. The line inductance makes exponential tapering more attractive in *RLC* lines than in *RC* lines. Wire tapering can reduce both the propagation delay and the power dissipation. This technique is used to size the interconnect lines within an H-tree clock distribution network. Exponentially tapered interconnect is shown to reduce the dynamic power dissipation while preserving the signal characteristics within clock distribution networks. Furthermore, the inductive behavior of the interconnects is reduced, decreasing the inductive noise.

On-chip inductance should be included in the design process in high frequency circuits. By including the on-chip inductance, the efficiency of different circuit design techniques such as wire sizing, driver sizing, and line tapering can be greatly enhanced.

# Contents

|                                                                             |             |

|-----------------------------------------------------------------------------|-------------|

| <b>Dedication</b>                                                           | <b>ii</b>   |

| <b>Curriculum Vitae</b>                                                     | <b>iii</b>  |

| <b>Acknowledgments</b>                                                      | <b>iv</b>   |

| <b>Abstract</b>                                                             | <b>vi</b>   |

| <b>List of Tables</b>                                                       | <b>xiii</b> |

| <b>List of Figures</b>                                                      | <b>xv</b>   |

| <b>1 Introduction</b>                                                       | <b>1</b>    |

| 1.1 Interconnect Modeling . . . . .                                         | 4           |

| 1.2 Importance of On-Chip Inductance . . . . .                              | 6           |

| <b>2 Design Methodologies to Drive RC Interconnects</b>                     | <b>15</b>   |

| 2.1 Introduction . . . . .                                                  | 15          |

| 2.2 Wire Sizing . . . . .                                                   | 16          |

| 2.3 Repeater Insertion . . . . .                                            | 17          |

| 2.4 Interconnect Shaping . . . . .                                          | 19          |

| <b>3 Inductance Extraction</b>                                              | <b>21</b>   |

| 3.1 Introduction . . . . .                                                  | 21          |

| 3.2 Shell Technique . . . . .                                               | 24          |

| 3.3 Hierarchical Technique . . . . .                                        | 24          |

| 3.4 Halo Technique . . . . .                                                | 26          |

| 3.5 $K$ Matrix Technique . . . . .                                          | 27          |

| 3.6 Comparison between Different Inductance Extraction Techniques . . . . . | 28          |

|                                                                                               |           |

|-----------------------------------------------------------------------------------------------|-----------|

| <b>4 Resistive Power in CMOS Circuits</b>                                                     | <b>32</b> |

| 4.1 Introduction . . . . .                                                                    | 32        |

| 4.2 Effect of Interconnect Resistance on the Transient Power Dissipation . . . . .            | 33        |

| 4.2.1 Conduction Losses in Resistive Interconnect . . . . .                                   | 34        |

| 4.2.2 Effect of Line Resistance on Short-Circuit Power within the Driver Gate . . . . .       | 39        |

| 4.3 Simulation Results . . . . .                                                              | 41        |

| 4.4 Conclusions . . . . .                                                                     | 44        |

| <b>5 Wire Sizing for Inductive Interconnects</b>                                              | <b>46</b> |

| 5.1 Introduction . . . . .                                                                    | 46        |

| 5.2 Transient Power Characterization . . . . .                                                | 51        |

| 5.2.1 Effect of Wire Sizing on Interconnect Line Impedance Characteristics . . . . .          | 51        |

| 5.2.2 Transient Power of Inductive Lines . . . . .                                            | 55        |

| 5.2.3 Transient Power Optimization Criteria . . . . .                                         | 58        |

| 5.3 Transition Time for a Signal at the Far End of an <i>RLC</i> Interconnect Line . . . . .  | 61        |

| 5.3.1 Analytic Solution for the Transition Time . . . . .                                     | 62        |

| 5.3.2 Dependence of Line Characteristics on Interconnect Width . . . . .                      | 63        |

| 5.4 Signal Transition Time Characteristics . . . . .                                          | 68        |

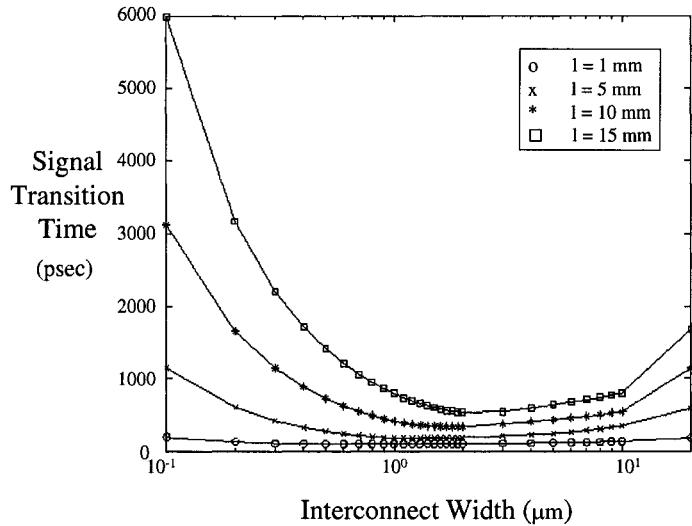

| 5.4.1 Effect of Interconnect Length . . . . .                                                 | 69        |

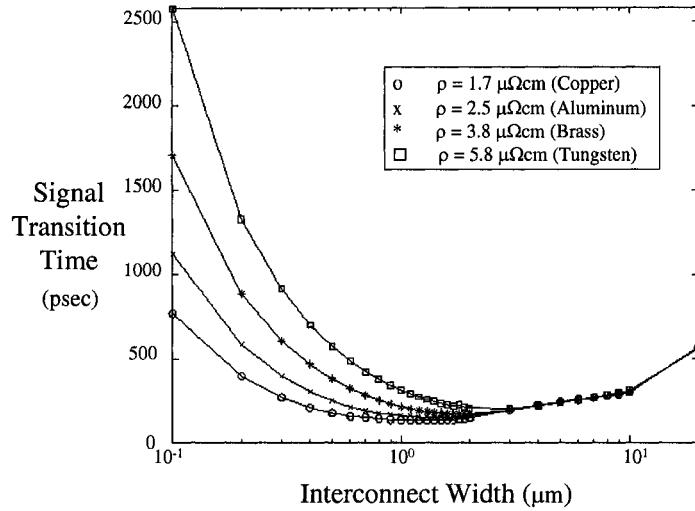

| 5.4.2 Effect of Interconnect Resistivity . . . . .                                            | 69        |

| 5.5 Simulation Results . . . . .                                                              | 71        |

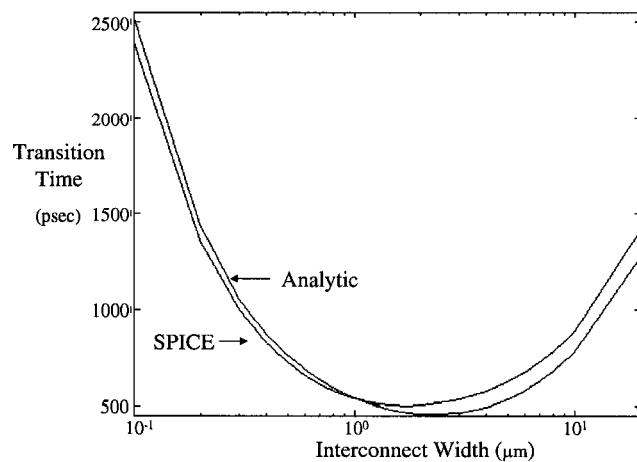

| 5.5.1 Transition Time . . . . .                                                               | 72        |

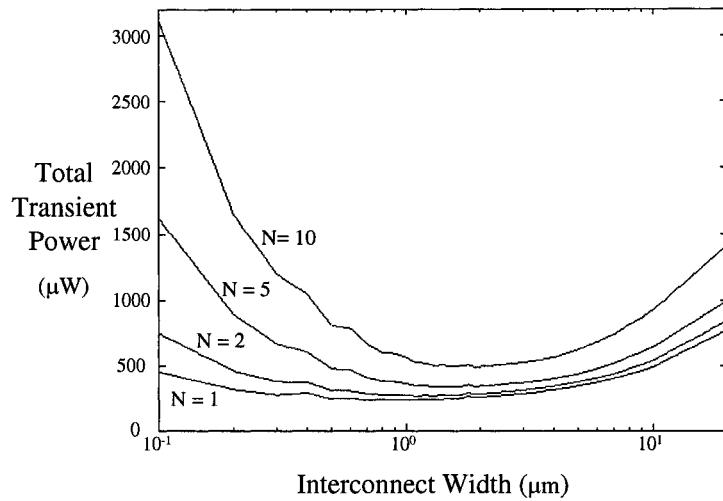

| 5.5.2 Minimizing the Transient Power . . . . .                                                | 74        |

| 5.5.3 Effects of Interconnect Resistivity and Length on Transient Power Dissipation . . . . . | 77        |

| 5.6 Conclusions . . . . .                                                                     | 80        |

| <b>6 Wire Sizing Within a Repeater System</b>                                                 | <b>83</b> |

| 6.1 Introduction . . . . .                                                                    | 83        |

| 6.2 Overview of the Repeater Insertion Process . . . . .                                      | 87        |

| 6.3 Propagation Delay . . . . .                                                               | 89        |

| 6.4 Power Dissipation . . . . .                                                               | 95        |

| 6.4.1 Short-Circuit Power Dissipation . . . . .                                               | 96        |

| 6.4.2 Dynamic Power Dissipation . . . . .                                                     | 97        |

| 6.4.3 Total Power Dissipation . . . . .                                                       | 98        |

|          |                                                                                        |            |

|----------|----------------------------------------------------------------------------------------|------------|

| 6.5      | Area of the Repeater System . . . . .                                                  | 101        |

| 6.6      | Design Criteria for Interconnect Within a Repeater System . .                          | 105        |

| 6.6.1    | Constrained Systems . . . . .                                                          | 105        |

| 6.6.2    | Unconstrained Systems . . . . .                                                        | 106        |

| 6.7      | Application of Interconnect Design Methodology . . . . .                               | 109        |

| 6.8      | Conclusions . . . . .                                                                  | 112        |

| <b>7</b> | <b>Shielding Effect of On-Chip Interconnect Inductance</b>                             | <b>117</b> |

| 7.1      | Introduction . . . . .                                                                 | 117        |

| 7.2      | Effective Capacitance of <i>RLC</i> Interconnect . . . . .                             | 121        |

| 7.3      | Effect of Line Inductance on the Delay Model . . . . .                                 | 124        |

| 7.4      | Inductive Shielding versus Resistive Shielding . . . . .                               | 128        |

| 7.5      | Propagation Delay of CMOS Inverter Driving an Inductive Load . . . . .                 | 131        |

| 7.6      | Simulation Results . . . . .                                                           | 133        |

| 7.7      | Conclusions . . . . .                                                                  | 135        |

| <b>8</b> | <b>Optimum Wire Shape of an <i>RLC</i> Interconnect</b>                                | <b>140</b> |

| 8.1      | Introduction . . . . .                                                                 | 140        |

| 8.2      | Optimum Wire Shape for Minimum Propagation Delay . . .                                 | 144        |

| 8.3      | Constraints on Optimum Tapering for <i>RLC</i> Lines . . . .                           | 148        |

| 8.4      | Tapering versus Uniform Wire Sizing in <i>RC</i> and <i>RLC</i> Lines                  | 149        |

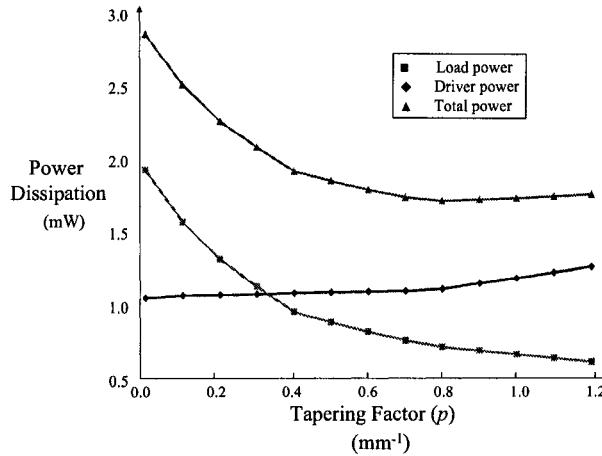

| 8.5      | Interconnect Tapering for Minimum Power Dissipation . . .                              | 153        |

| 8.6      | Interconnect Tapering versus Repeater Insertion . . . . .                              | 155        |

| 8.7      | Signal Integrity in Tapered <i>RLC</i> Interconnects . . . . .                         | 156        |

| 8.8      | Simulation Results . . . . .                                                           | 158        |

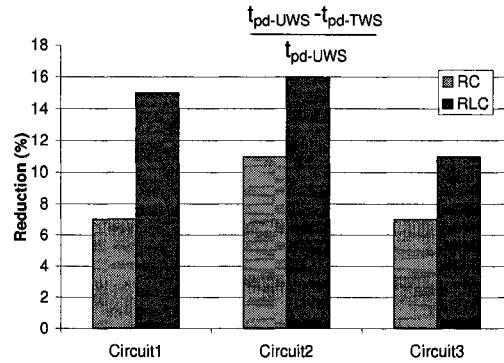

| 8.8.1    | Tapering versus Uniform Wire Sizing . . . . .                                          | 158        |

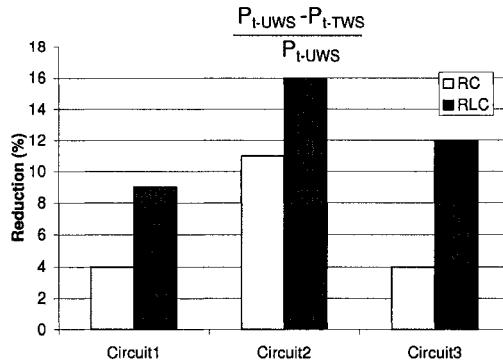

| 8.8.2    | Tapering for Minimum Power Dissipation . . . . .                                       | 161        |

| 8.8.3    | Tapering versus Repeater Insertion . . . . .                                           | 163        |

| 8.8.4    | Signal Integrity Characteristics in an Example Clock Distribution Network . . . . .    | 165        |

| 8.9      | Conclusions . . . . .                                                                  | 166        |

| <b>9</b> | <b>Optimum Wire Tapering for Minimum Power Dissipation of <i>RLC</i> Interconnects</b> | <b>174</b> |

| 9.1      | Introduction . . . . .                                                                 | 174        |

| 9.2      | Interconnect Tapering for Minimum Power Dissipation . .                                | 176        |

| 9.3      | Optimization Criterion for a Tapered Line . . . . .                                    | 179        |

| 9.4      | Tapering versus Uniform Wire Sizing for Minimum Power Dissipation . . . . .            | 182        |

|                     |                                                                                                    |            |

|---------------------|----------------------------------------------------------------------------------------------------|------------|

| 9.5                 | Simulation Results . . . . .                                                                       | 183        |

| 9.5.1               | Tapering for Minimum Power Dissipation . . . . .                                                   | 184        |

| 9.5.2               | Tapering versus Uniform Wire Sizing . . . . .                                                      | 185        |

| 9.6                 | Conclusions . . . . .                                                                              | 187        |

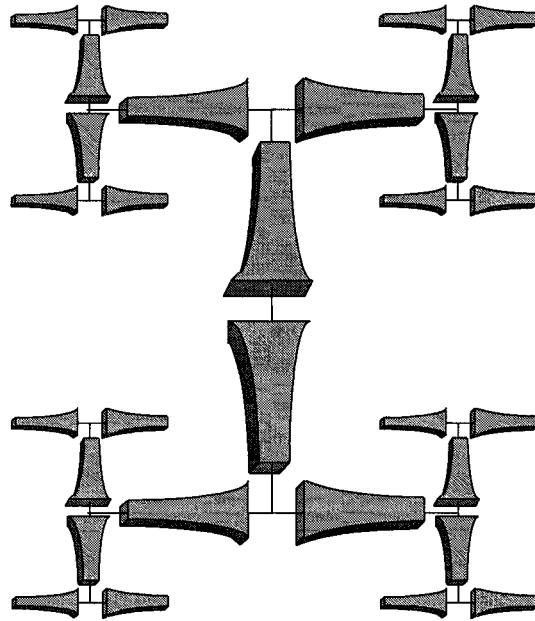

| <b>10</b>           | <b>Exponentially Tapered H-Tree Clock Distribution Networks</b>                                    | <b>191</b> |

| 10.1                | Introduction . . . . .                                                                             | 191        |

| 10.2                | Tapering an H-Tree for Low Power . . . . .                                                         | 194        |

| 10.2.1              | Tapering using First Order Moment Approximation .                                                  | 195        |

| 10.2.2              | Tapering using Second Order Moment Approximation .                                                 | 197        |

| 10.3                | Design Issues in Exponentially Tapered H-Trees . . . . .                                           | 201        |

| 10.3.1              | Signal Integrity . . . . .                                                                         | 201        |

| 10.3.2              | Routing Area . . . . .                                                                             | 204        |

| 10.3.3              | Clock Skew . . . . .                                                                               | 207        |

| 10.4                | Simulation Results . . . . .                                                                       | 208        |

| 10.4.1              | First Order Approximation . . . . .                                                                | 209        |

| 10.4.2              | Second Order Approximation . . . . .                                                               | 212        |

| 10.5                | Conclusions . . . . .                                                                              | 215        |

| <b>11</b>           | <b>Conclusions</b>                                                                                 | <b>221</b> |

| <b>12</b>           | <b>Future Work</b>                                                                                 | <b>227</b> |

| 12.1                | Reduced Order Model for Tapered <i>RLC</i> Interconnect . . . . .                                  | 228        |

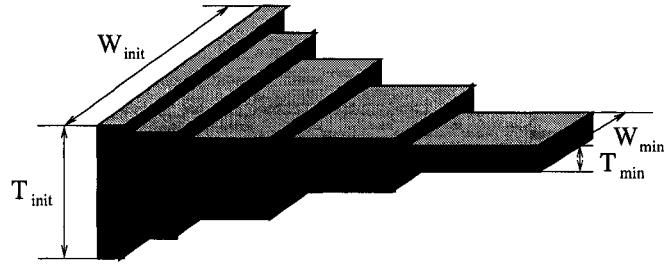

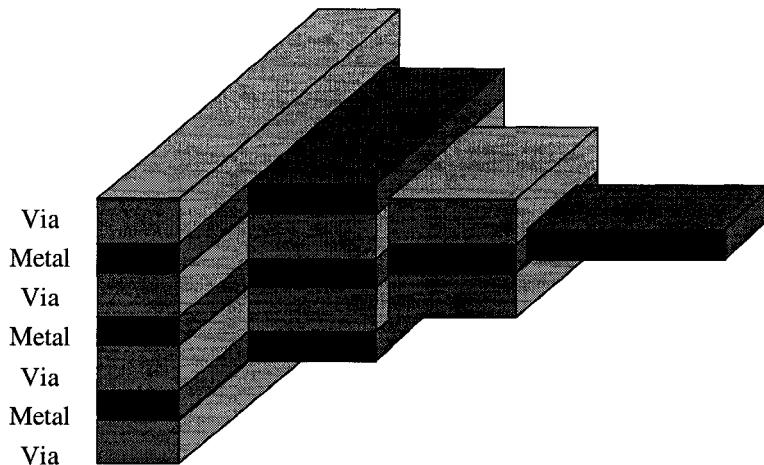

| 12.2                | Interconnect Tapering in Three Dimensions . . . . .                                                | 229        |

| 12.3                | Techniques to Drive Long Interconnects . . . . .                                                   | 232        |

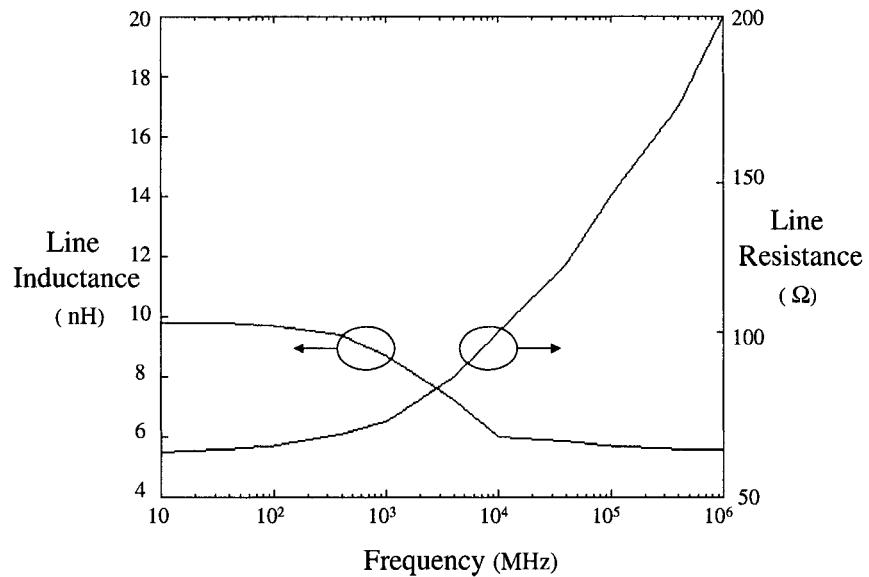

| 12.4                | Design Methodologies for Frequency Dependent Interconnect Impedances . . . . .                     | 234        |

| 12.5                | Summary . . . . .                                                                                  | 236        |

| <b>Bibliography</b> |                                                                                                    | <b>238</b> |

| <b>Appendices</b>   |                                                                                                    | <b>267</b> |

| <b>A</b>            | <b>Transition Time for a Signal at the Far End of an Inductive Interconnect</b>                    | <b>268</b> |

| <b>B</b>            | <b>Expressions for line impedance parameters of an interconnect shielded with two ground lines</b> | <b>275</b> |

| <b>C</b>            | <b>Effective Capacitance of an <i>RLC</i> Load</b>                                                 | <b>277</b> |

|                                                                                                     |            |

|-----------------------------------------------------------------------------------------------------|------------|

| <b>D Dependence of Delay on Line Inductance</b>                                                     | <b>281</b> |

| <b>E Propagation Delay based on <math>\pi_{21}</math> Reduced Order Model</b>                       | <b>283</b> |

| <b>F Impedance Parameters of Tapered <i>RLC</i> Interconnect</b>                                    | <b>290</b> |

| <b>G Practical Implementation of Exponential Tapering</b>                                           | <b>293</b> |

| <b>H Pseudocode for the C Program of the Optimum Tapered Lines using First Order Approximation</b>  | <b>295</b> |

| <b>I Pseudocode for the C Program of the Optimum Tapered Lines using Second Order Approximation</b> | <b>297</b> |

| <b>Publications</b>                                                                                 | <b>299</b> |

# List of Tables

|     |                                                                                                                                |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Number of nonzero elements in the inductance matrix . . . . .                                                                  | 29  |

| 3.2 | CPU time and memory usage for different inductance extraction methods . . . . .                                                | 30  |

| 4.1 | Power components for resistive-capacitive line . . . . .                                                                       | 42  |

| 4.2 | Power components for lossy transmission line . . . . .                                                                         | 44  |

| 5.1 | Simulation and analytic transition times of a signal at the far end of an inductive interconnect line . . . . .                | 73  |

| 5.2 | Simulation and analytic results of the optimum width with different loads . . . . .                                            | 76  |

| 5.3 | Power reduction for different line parameters . . . . .                                                                        | 79  |

| 6.1 | Uniform repeater system for different optimization criteria . .                                                                | 114 |

| 6.2 | Uniform repeater system for different optimization criteria for $l = 5$ mm . . . . .                                           | 115 |

| 6.3 | Uniform repeater system for different optimization criteria for $l = 15$ mm . . . . .                                          | 116 |

| 7.1 | Propagation delay with different models for different line inductance for $C_{line} = 400$ fF . . . . .                        | 137 |

| 7.2 | Propagation delay with different models for different line inductance for $C_{line} = 1$ pF . . . . .                          | 138 |

| 7.3 | Reduction in area and power dissipation when considering line inductance for different dielectric and line materials . . . . . | 139 |

| 8.1 | Circuit parameters of example circuits . . . . .                                                                               | 159 |

| 8.2 | Optimum tapering for minimum power dissipation . . . . .                                                                       | 162 |

| 8.3 | Total power dissipation using different sizing techniques . .                                                                  | 169 |

| 8.4 | Propagation delay for a long interconnect (5 mm) with $q = 1.0$ $\mu\text{m}$ . . . . .                                        | 170 |

|      |                                                                                                                                                                                                                                                       |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.5  | Propagation delay for a long interconnect (5 mm) with $q = 0.5$<br>$\mu\text{m}$ . . . . .                                                                                                                                                            | 171 |

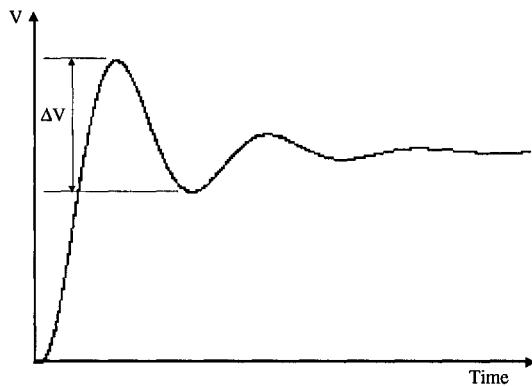

| 8.6  | Propagation delay and $\Delta V_{\text{over-under}}$ for different interconnect<br>sizing techniques . . . . .                                                                                                                                        | 173 |

| 9.1  | Optimum sizing for minimum power dissipation . . . . .                                                                                                                                                                                                | 186 |

| 9.2  | Optimum tapering for minimum power dissipation . . . . .                                                                                                                                                                                              | 189 |

| 10.1 | H-tree design techniques using a first moment approximation                                                                                                                                                                                           | 210 |

| 10.2 | Signal characteristics and power dissipation of different H-tree<br>clock distribution structures . . . . .                                                                                                                                           | 217 |

| 10.3 | H-tree design techniques using second moment approximation                                                                                                                                                                                            | 218 |

| 10.4 | Signal characteristics and power dissipation of different H-tree<br>clock distribution structures . . . . .                                                                                                                                           | 219 |

| 10.5 | Signal characteristics and power dissipation of different H-tree<br>clock distribution structures . . . . .                                                                                                                                           | 220 |

| A.1  | Different regions of operation for a CMOS inverter with a ramp<br>input signal for comparable input and output signal transi-<br>tions after the input signal exceeds the threshold voltage of<br>the NMOS transistor ( $V_{in} > V_{tn}$ ) . . . . . | 270 |

# List of Figures

|     |                                                                                                                                                |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|----|

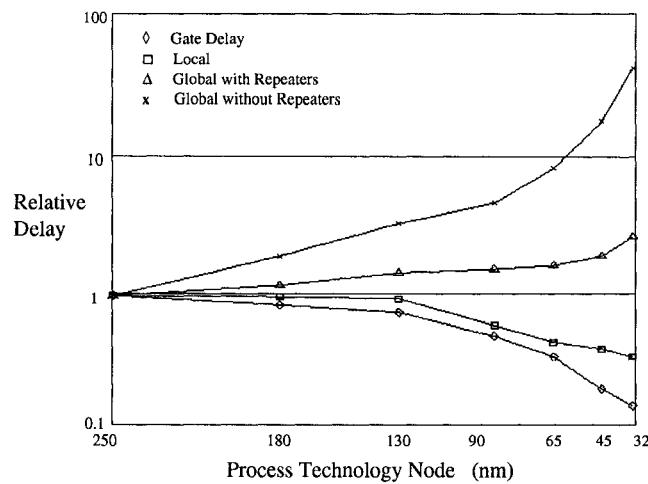

| 1.1 | Relative delay for local and global wiring versus feature size [4] . . . . .                                                                   | 3  |

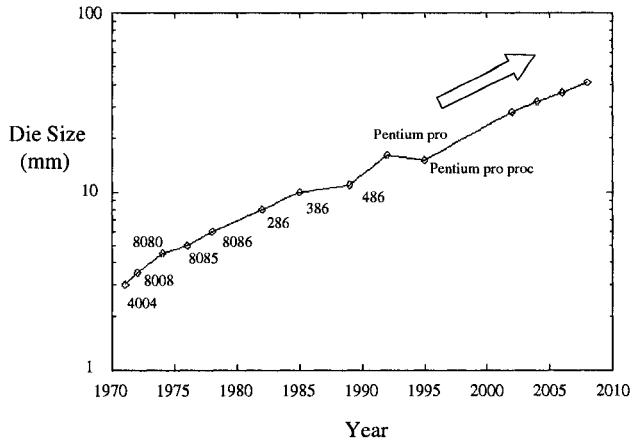

| 1.2 | Die size for different generations of Intel microprocessors [5] . . . . .                                                                      | 4  |

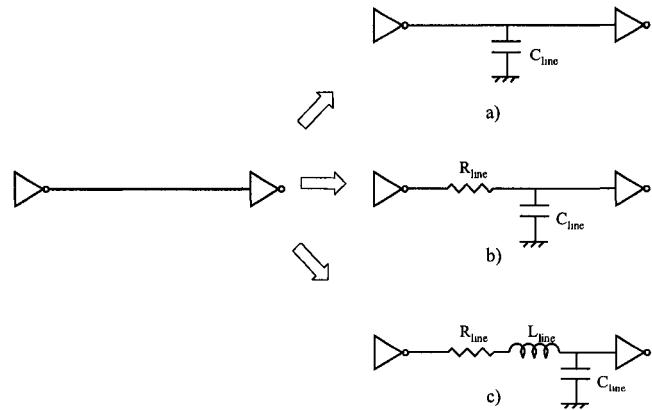

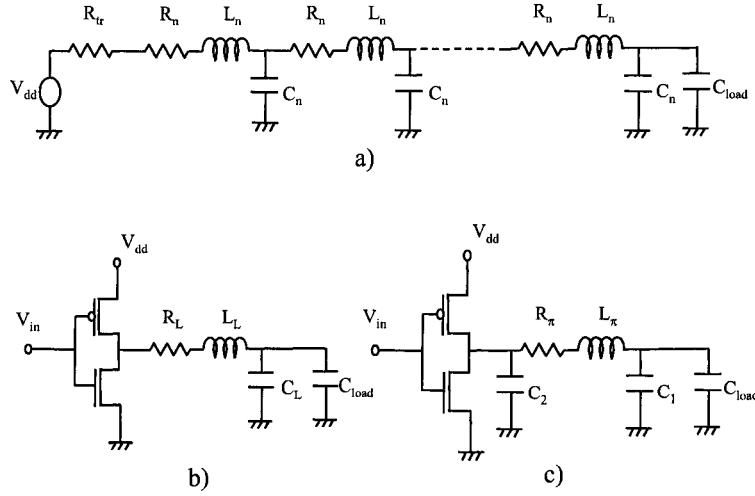

| 1.3 | Different lumped interconnect models a) $C$ model b) $RC$ model c)<br>$RLC$ model . . . . .                                                    | 6  |

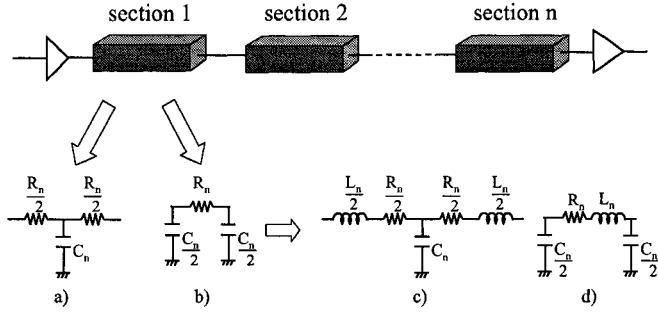

| 1.4 | Distributed model for an interconnect a) $RC$ T model b) $RC$ $\Pi$<br>model c) $RLC$ T model d) $RLC$ $\Pi$ model . . . . .                   | 7  |

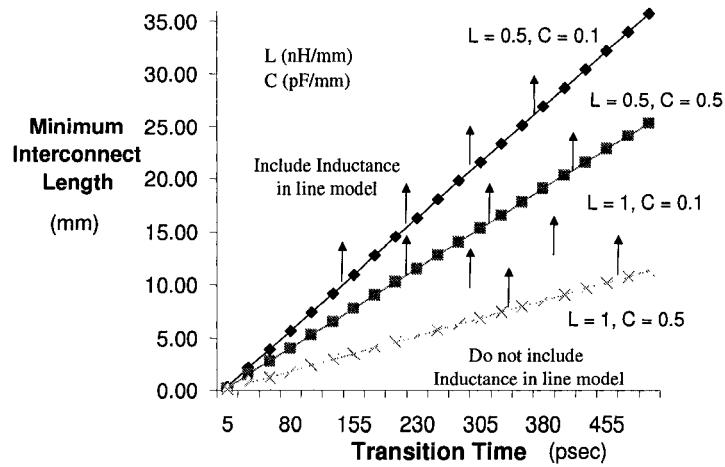

| 1.5 | Lower limit of interconnect length above which the inductance<br>should be considered in the line model . . . . .                              | 8  |

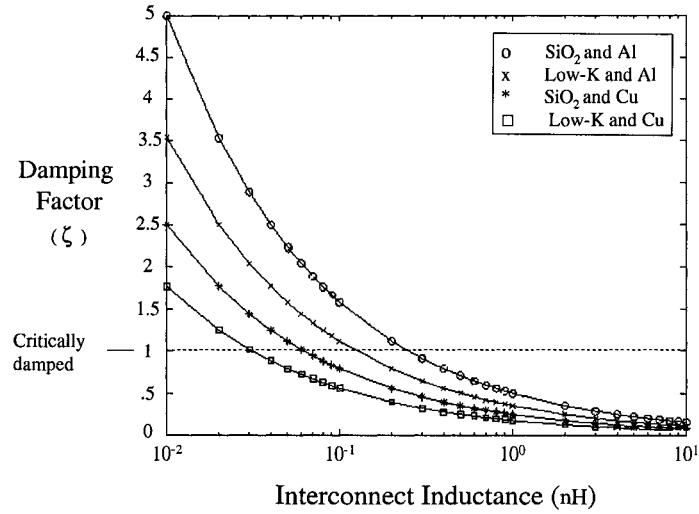

| 1.6 | Damping factor as a function of the line inductance for different<br>dielectric and metal materials . . . . .                                  | 9  |

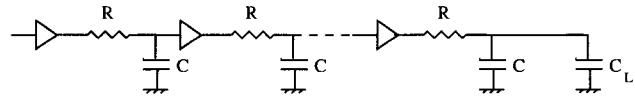

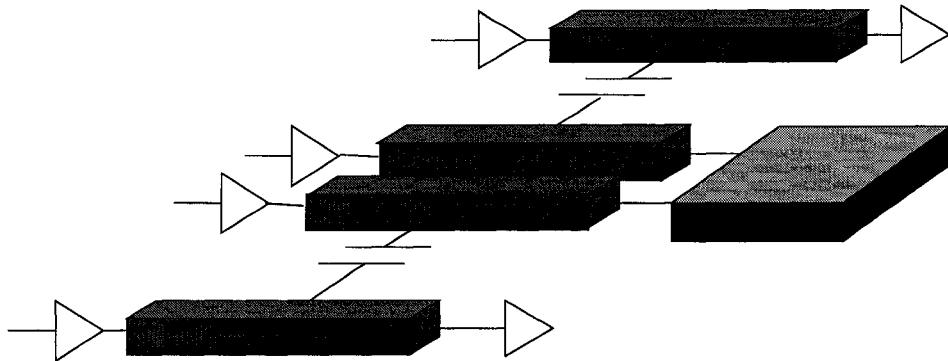

| 2.1 | Uniform repeater system driving a distributed $RC$ interconnect . . . . .                                                                      | 18 |

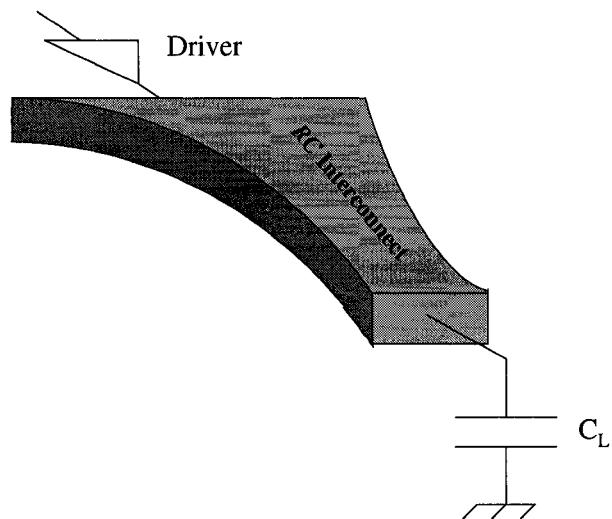

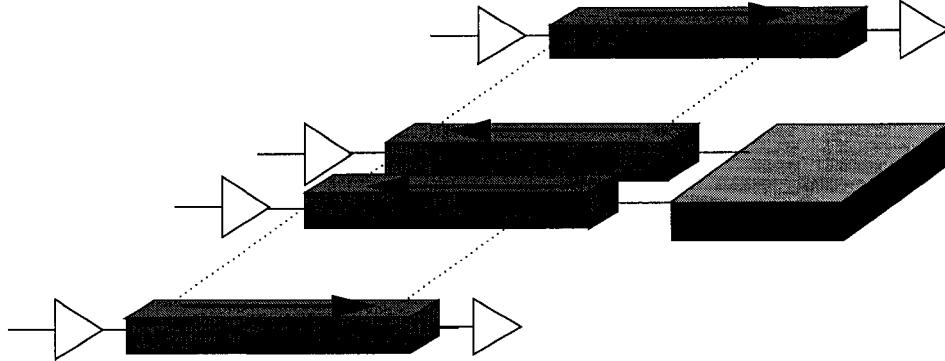

| 2.2 | Tapered $RC$ interconnect . . . . .                                                                                                            | 19 |

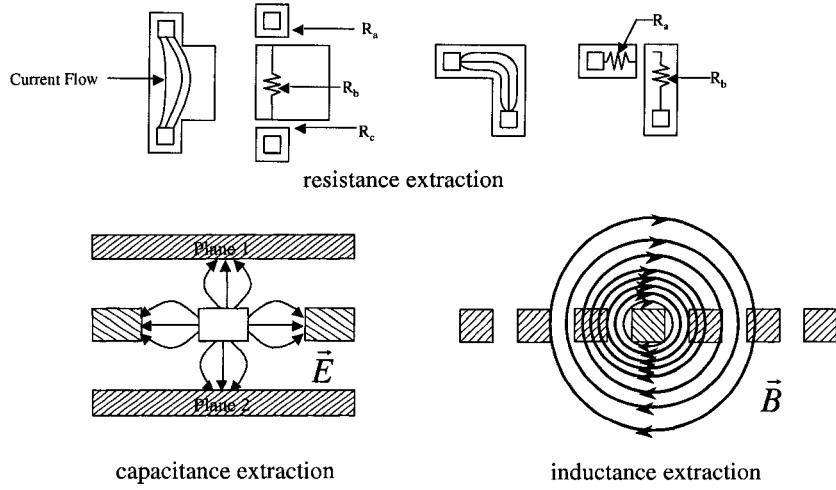

| 3.1 | Example of electric and magnetic field lines to illustrate the differ-<br>ence among resistive, capacitive, and inductive extraction . . . . . | 23 |

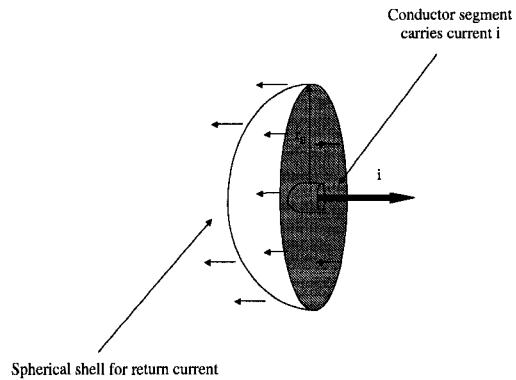

| 3.2 | Spherical shell of return current $i$ at a radius $r_0$ [89] . . . . .                                                                         | 25 |

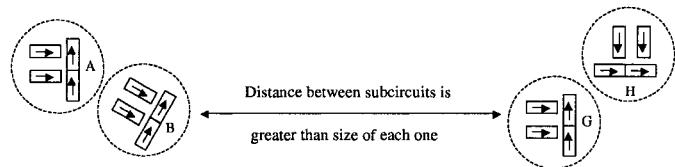

| 3.3 | Example system: A,B- aggressor groups; G,H- victim groups<br>[91] . . . . .                                                                    | 25 |

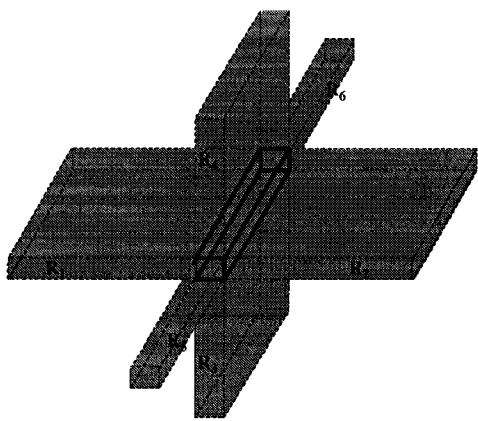

| 3.4 | The halo of a target segment consisting of six semi-infinite<br>regions [88] . . . . .                                                         | 27 |

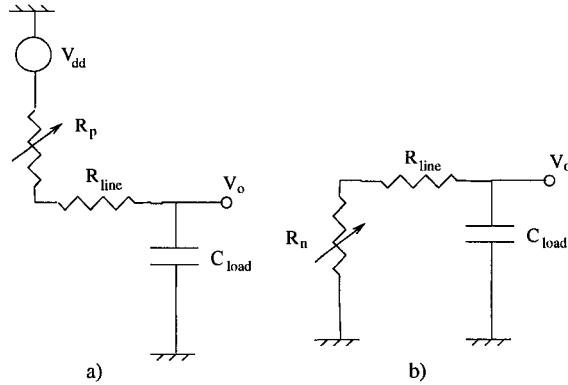

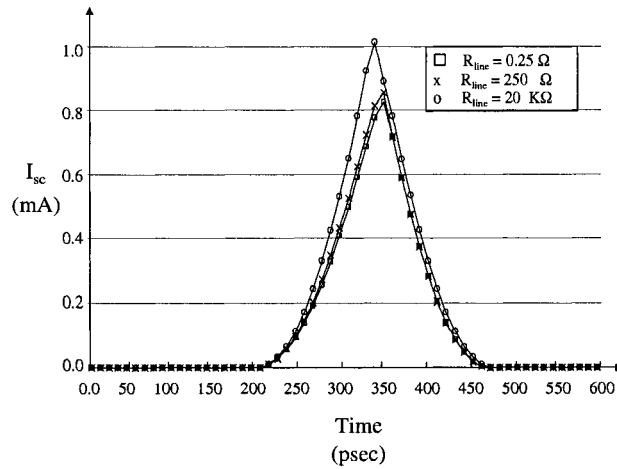

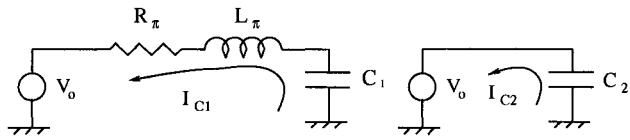

| 4.1 | Equivalent circuit model including line resistance during a)<br>charging, b) discharging . . . . .                                             | 37 |

| 4.2 | Equivalent circuit including short-circuit current for an input<br>signal transitioning from high-to-low . . . . .                             | 40 |

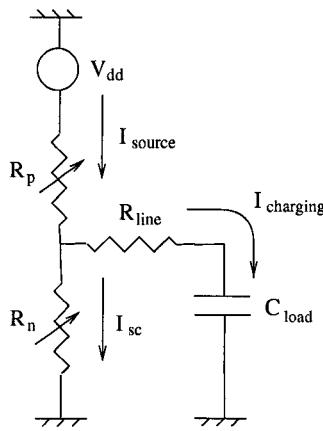

| 4.3 | Short-circuit current waveform for different load resistances of<br>a resistive-capacitive load . . . . .                                      | 43 |

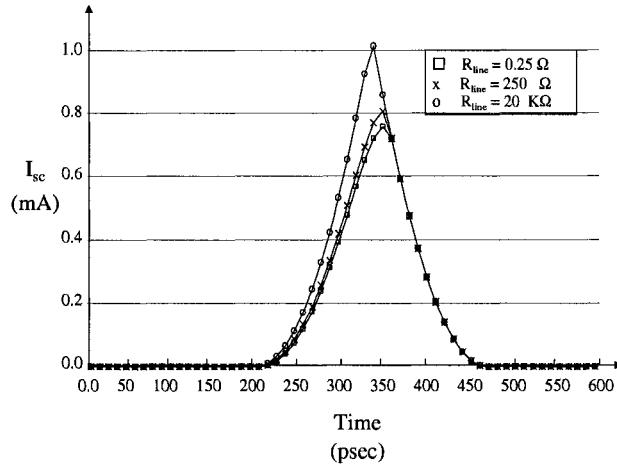

| 4.4 | Short-circuit current waveform for different load resistances of<br>a lossy transmission line . . . . .                                        | 45 |

|      |                                                                                                                                                                                                                                             |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

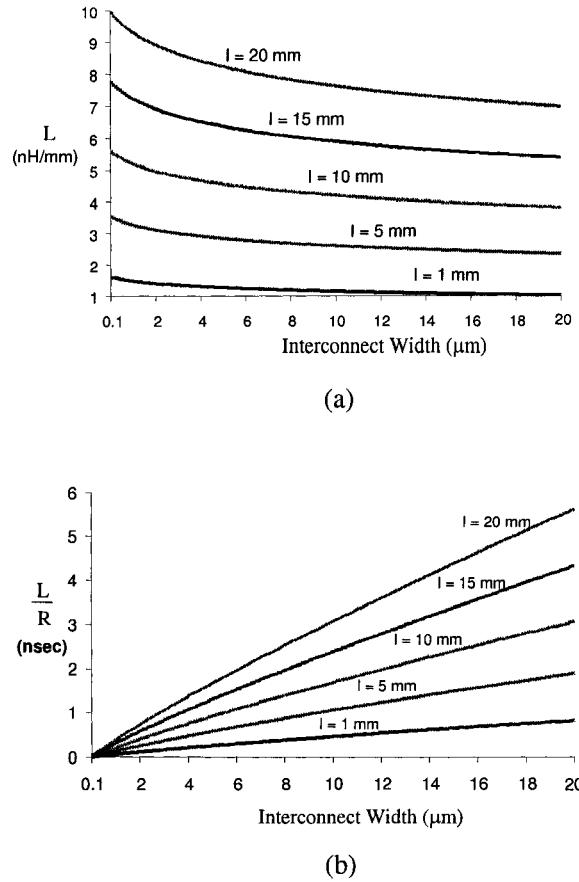

| 5.1  | Inductive interconnect characteristics versus width for different lengths (a) self-inductance, (b) inductive time constant . . . . .                                                                                                        | 53 |

| 5.2  | Lower limit on the interconnect length above which the line inductance should be considered . . . . .                                                                                                                                       | 54 |

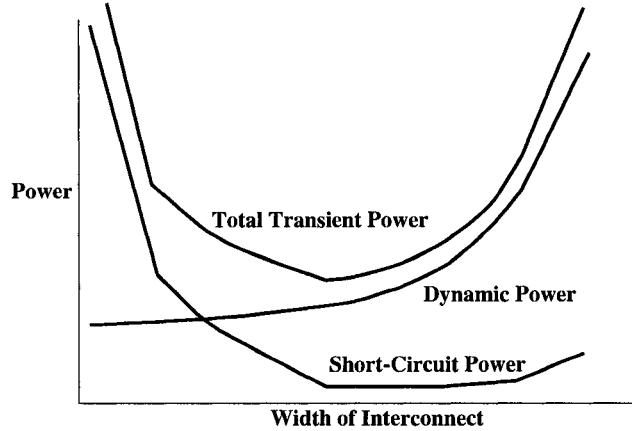

| 5.3  | Dynamic, short-circuit, and total transient power as a function of the interconnect line width . . . . .                                                                                                                                    | 56 |

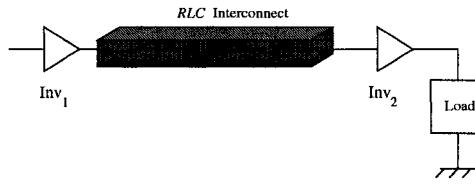

| 5.4  | CMOS gates connected by an <i>RLC</i> interconnect line . . . . .                                                                                                                                                                           | 57 |

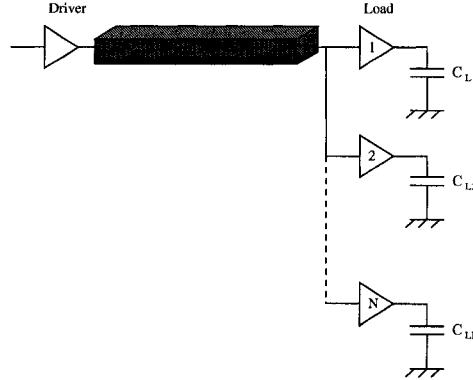

| 5.5  | Inverter driving N logic gates . . . . .                                                                                                                                                                                                    | 59 |

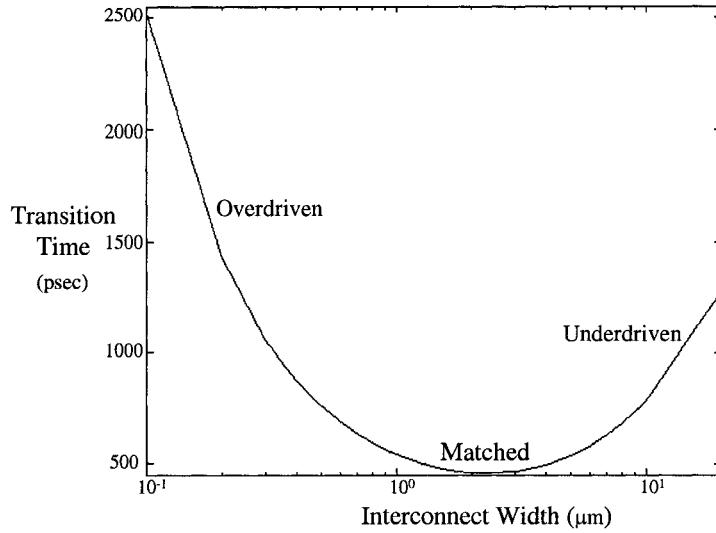

| 5.6  | Transition time as a function of interconnect width for different impedance matching conditions. Note the minimum transition time at the ideally matched condition. . . . .                                                                 | 64 |

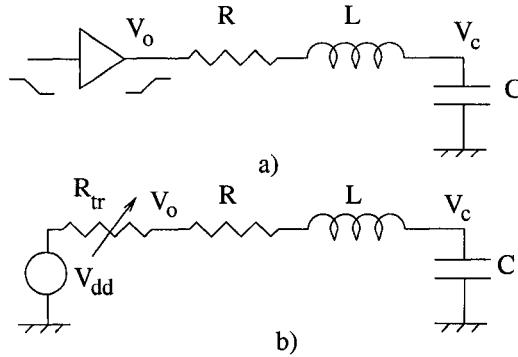

| 5.7  | An inverter driving an <i>RLC</i> interconnect line (a) circuit diagram (b) equivalent circuit of inverter at the end of the high-to-low input transition . . . . .                                                                         | 65 |

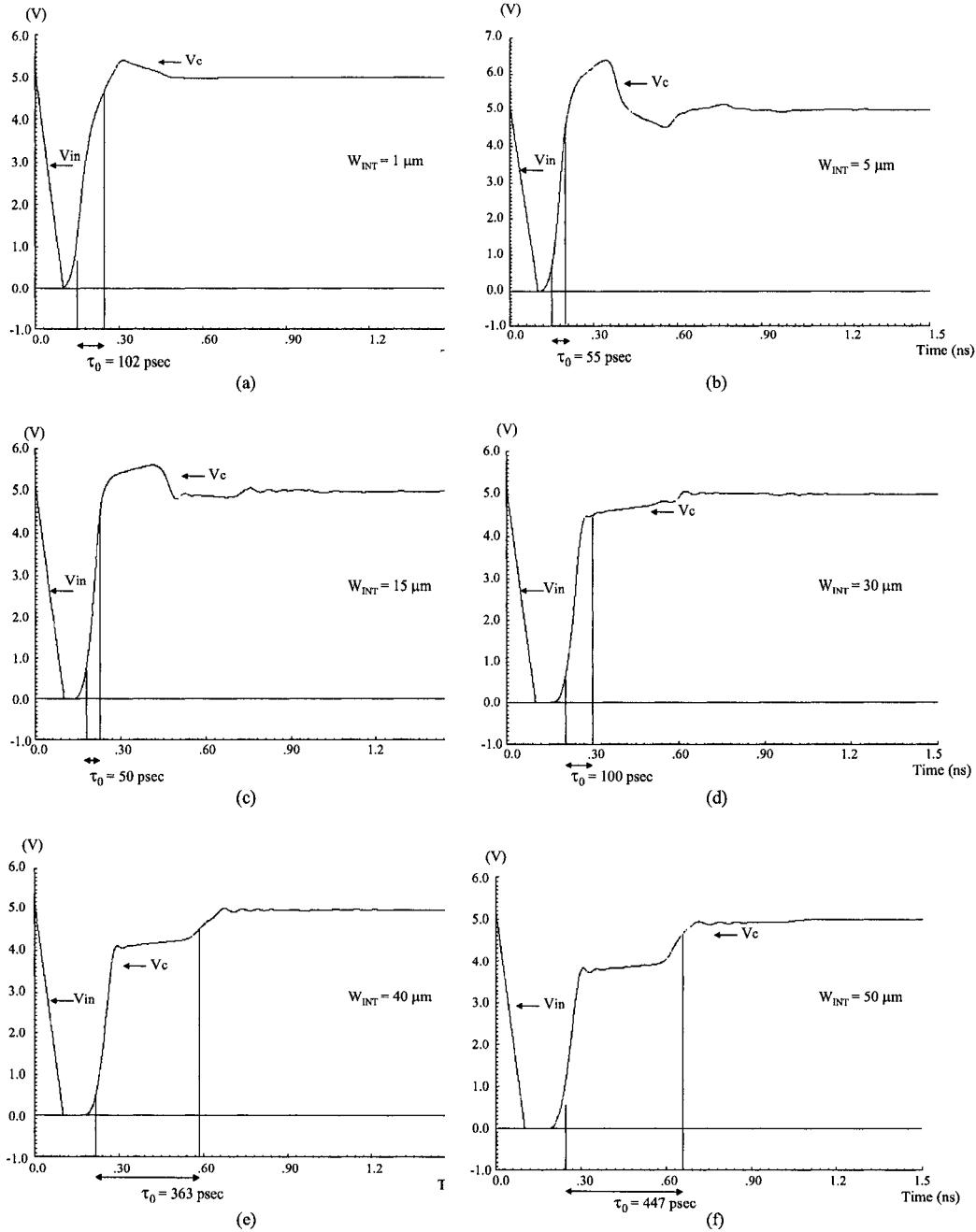

| 5.8  | Output waveform at the far end of a long interconnect line driven by an inverter with different line widths (a) Resistive, (b) Overdriven (inductive), (c) Matched, (d) Underdriven (inductive), (e) Underdriven, (f) Underdriven . . . . . | 66 |

| 5.9  | Signal transition time versus interconnect width for different line lengths . . . . .                                                                                                                                                       | 70 |

| 5.10 | Signal transition time versus interconnect width for different materials ( <i>i.e.</i> , resistivities) . . . . .                                                                                                                           | 71 |

| 5.11 | Analytic solution of the transition time as compared with SPICE for different line widths . . . . .                                                                                                                                         | 72 |

| 5.12 | Total transient power dissipation for an inverter driving N logic gates as determined by SPICE . . . . .                                                                                                                                    | 75 |

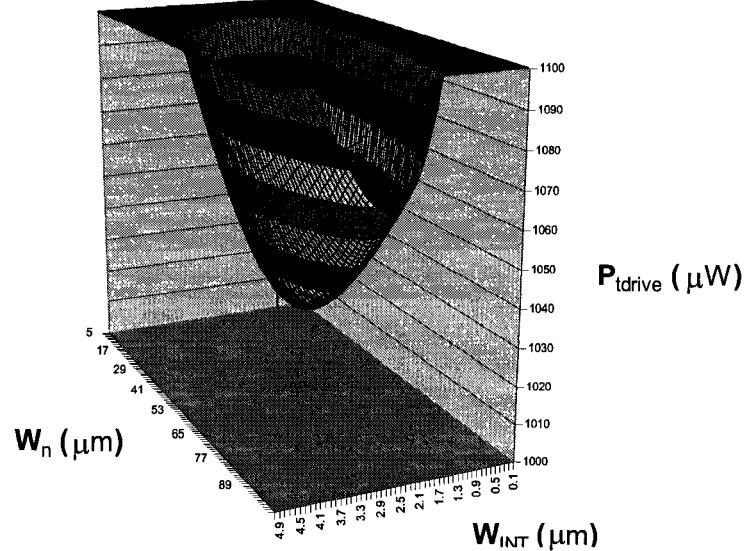

| 5.13 | Total power dissipation with different wire and driver sizes. The number of load gates N is 10. Note that the minimum power occurs at $W_n = 57 \mu m$ and $W_{INT} = 2.8 \mu m$ . . . . .                                                  | 77 |

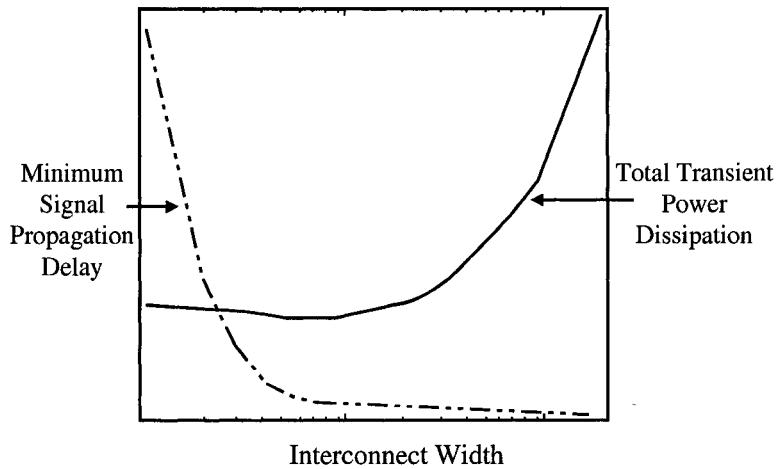

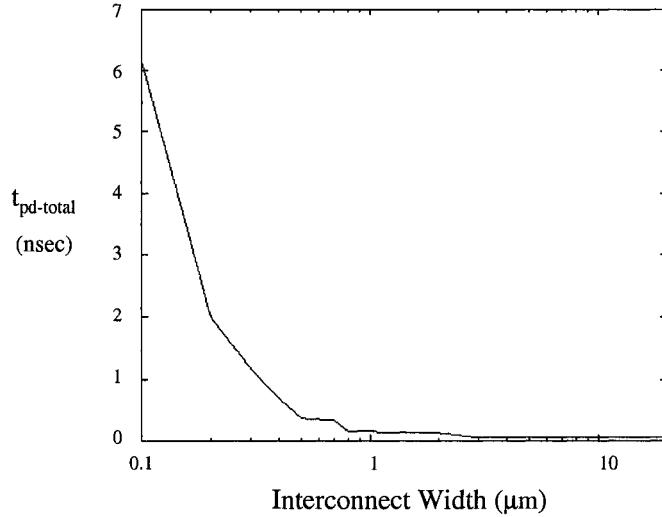

| 6.1  | Minimum signal propagation delay and transient power dissipation as a function of line width for a repeater system . . . . .                                                                                                                | 86 |

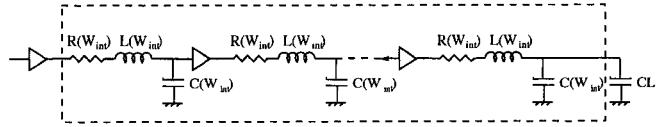

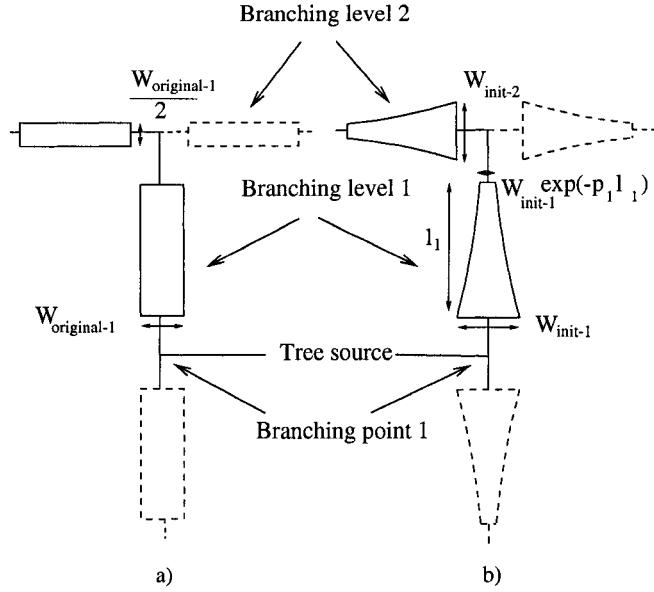

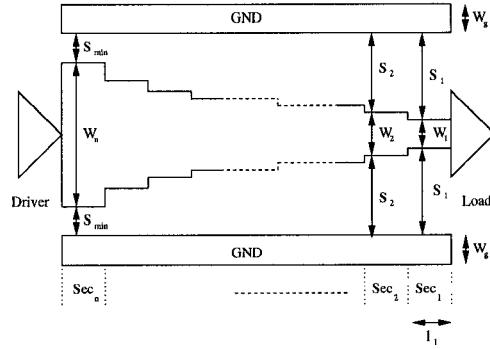

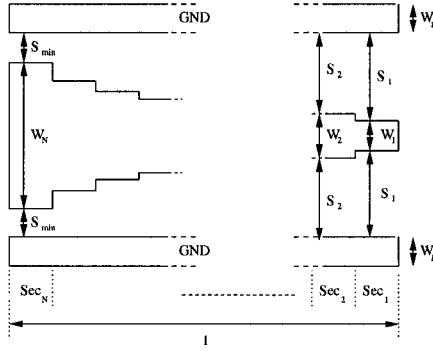

| 6.2  | Uniform repeater system driving a distributed <i>RLC</i> interconnect .                                                                                                                                                                     | 88 |

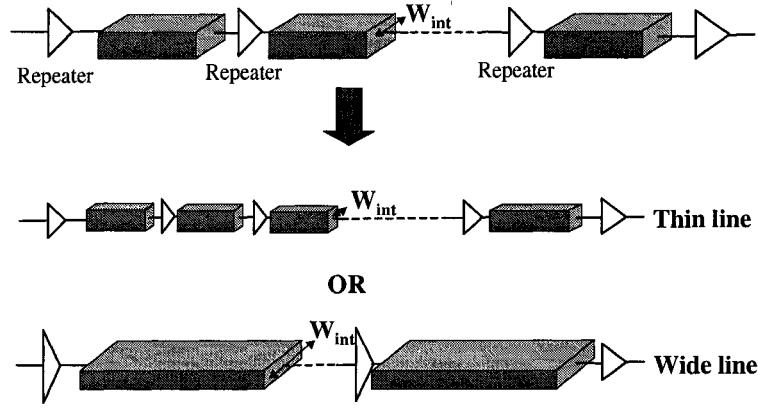

| 6.3  | Wire sizing in a repeater insertion system . . . . .                                                                                                                                                                                        | 89 |

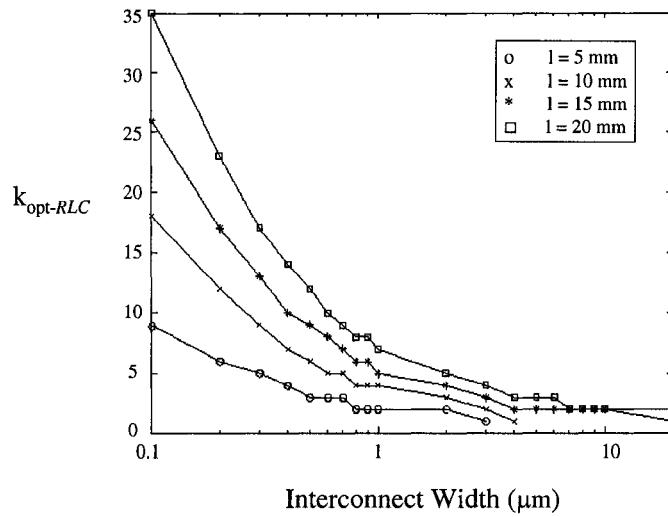

| 6.4  | Optimum number of repeaters for minimum propagation delay for different line widths . . . . .                                                                                                                                               | 91 |

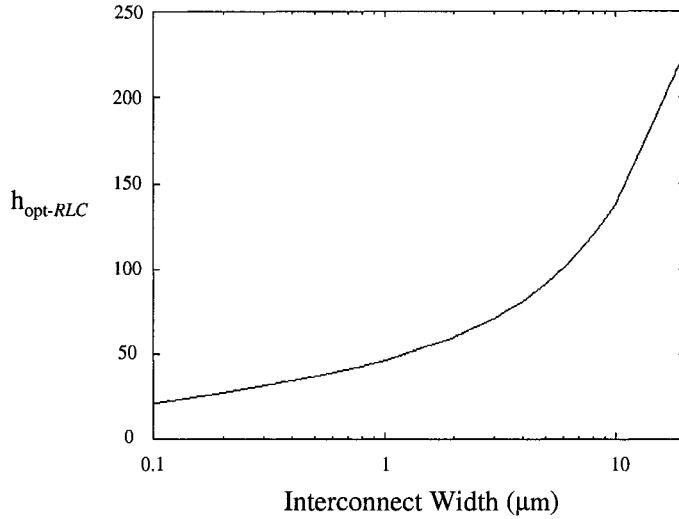

| 6.5  | Optimum repeater size for minimum propagation delay for different line widths . . . . .                                                                                                                                                     | 92 |

| 6.6  | Minimum signal propagation delay as a function of interconnect width ( $l = 5 \text{ mm}$ ) . . . . .                                                                                                                                       | 94 |

|      |                                                                                                                                                                                            |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

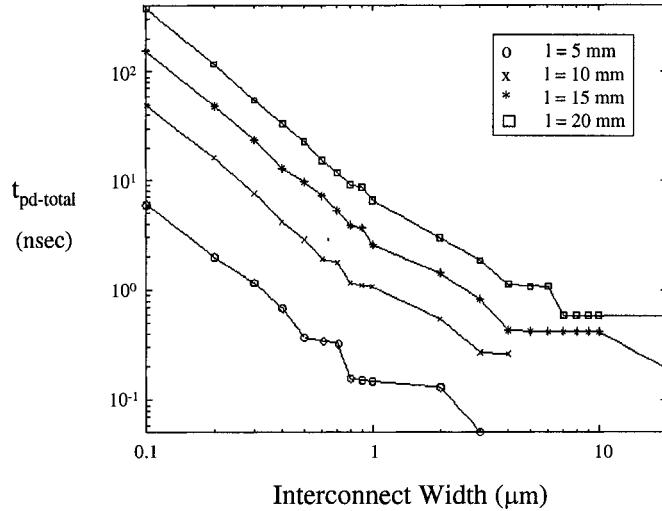

| 6.7  | Minimum signal delay as a function of interconnect width for different line lengths . . . . .                                                                                              | 95  |

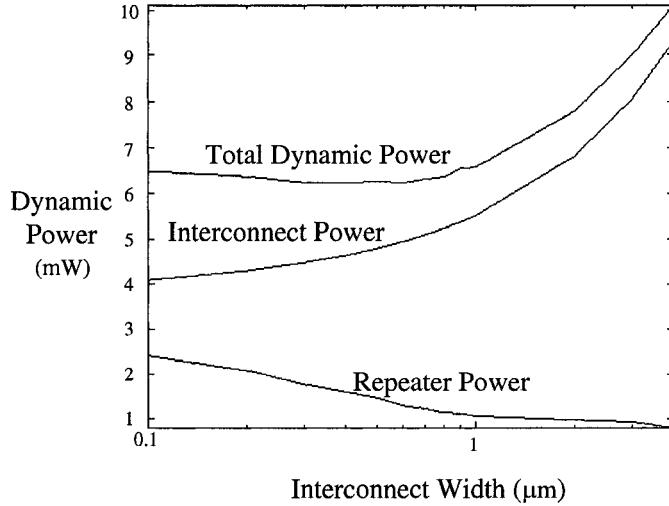

| 6.8  | Dynamic power dissipation as a function of interconnect width for $l = 20$ mm . . . . .                                                                                                    | 99  |

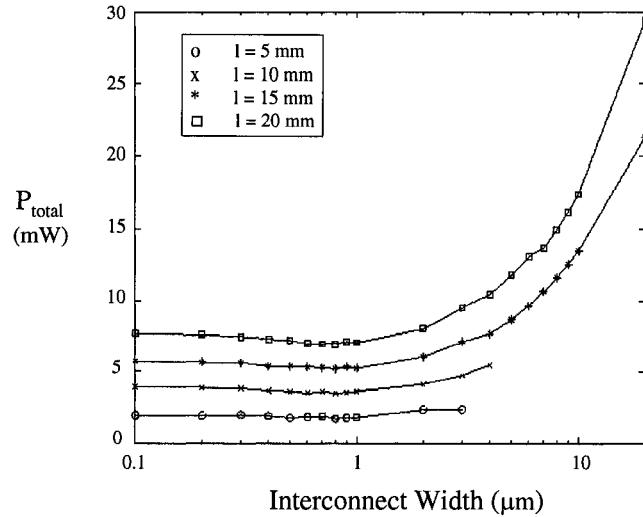

| 6.9  | Total transient power dissipation as a function of interconnect width 100 . . . . .                                                                                                        | 100 |

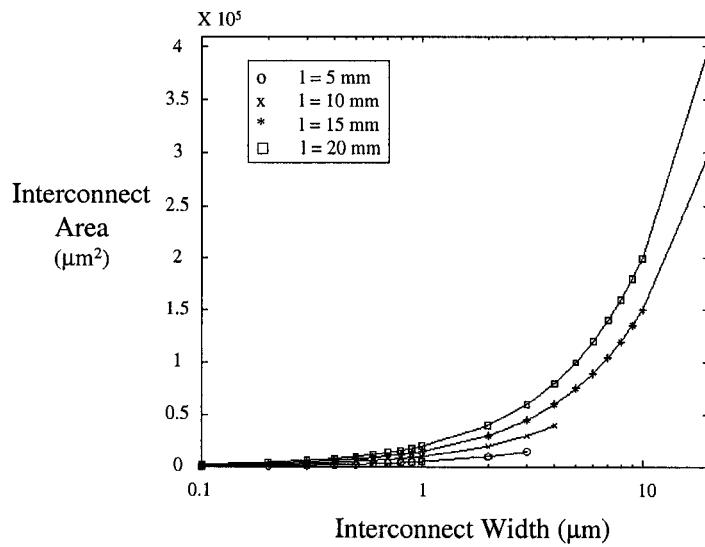

| 6.10 | Interconnect area as a function of interconnect width for different line lengths . . . . .                                                                                                 | 102 |

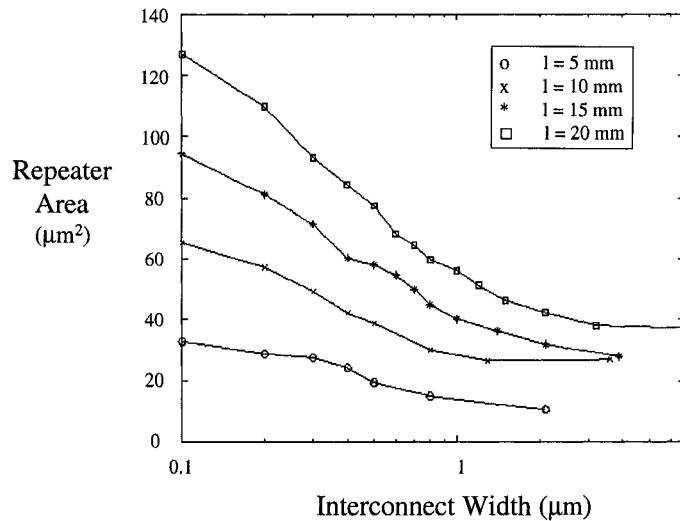

| 6.11 | Total area of the repeaters as a function of the interconnect width for different line lengths . . . . .                                                                                   | 103 |

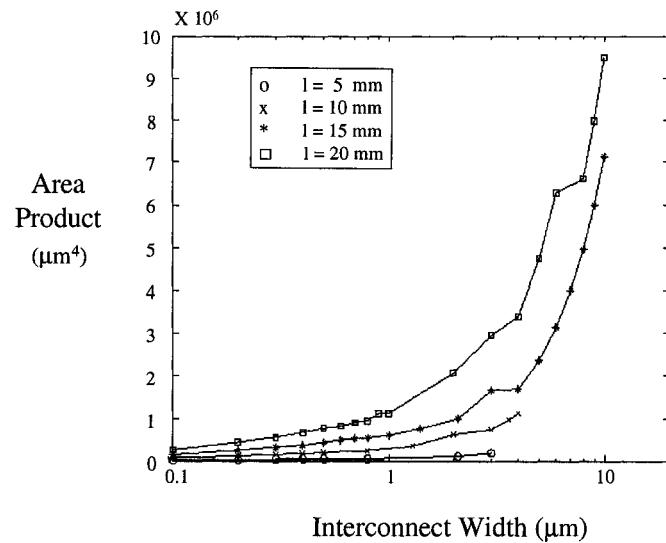

| 6.12 | Product of interconnect and silicon area as a function of the interconnect width for different line lengths . . . . .                                                                      | 104 |

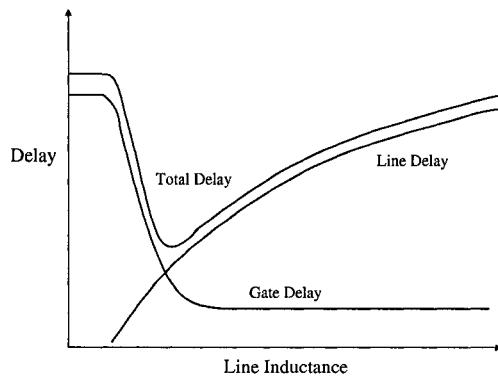

| 7.1  | Propagation delay as a function of the line inductance . . . . .                                                                                                                           | 120 |

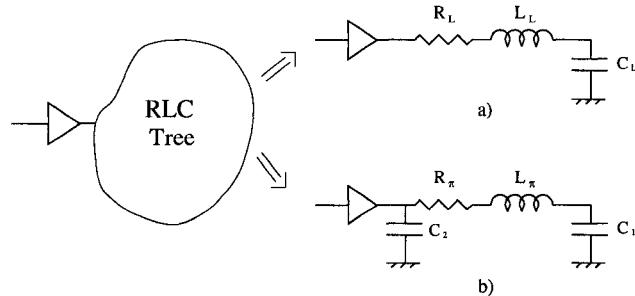

| 7.2  | Reduced order model for a general <i>RLC</i> tree a) Lumped model<br>b) $\pi_{21}$ model . . . . .                                                                                         | 121 |

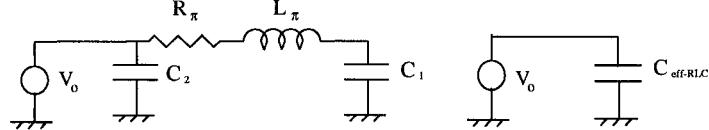

| 7.3  | Effective capacitance of $\pi_{21}$ <i>RLC</i> model . . . . .                                                                                                                             | 122 |

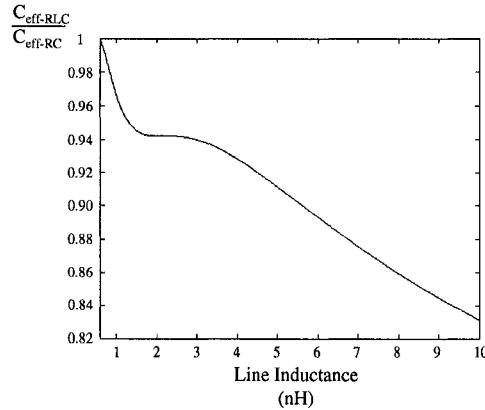

| 7.4  | Ratio between the effective capacitance of an <i>RLC</i> and <i>RC</i> load . . . . .                                                                                                      | 123 |

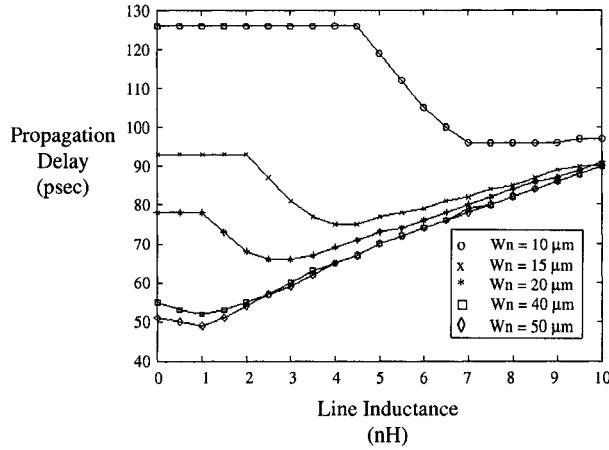

| 7.5  | Total delay for different values of line inductance and driver size of a distributed <i>RLC</i> interconnect as determined by the Cadence circuit simulator . . . . .                      | 126 |

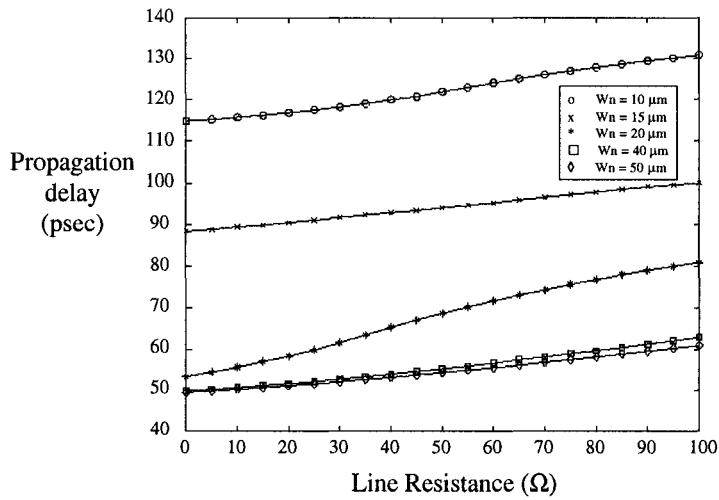

| 7.6  | Total delay for different values of line resistance and driver size for a distributed <i>RLC</i> interconnect (Cadence circuit simulator) . . . . .                                        | 129 |

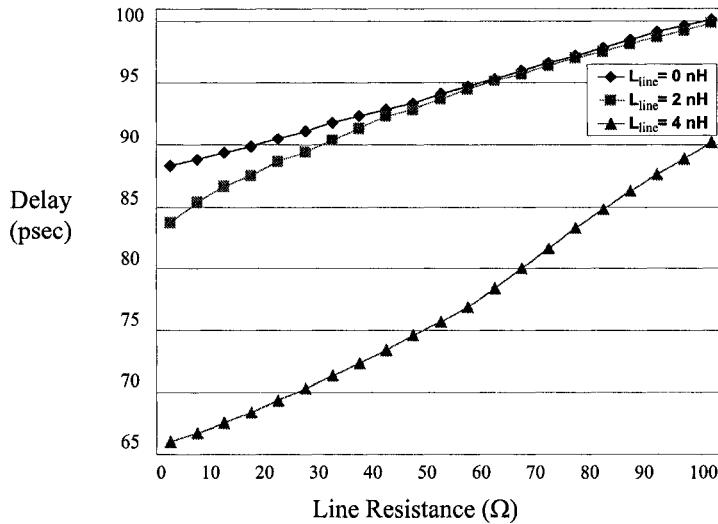

| 7.7  | Total delay for different values of line resistance and inductance of a distributed <i>RLC</i> interconnect (Cadence circuit simulator) . . . . .                                          | 131 |

| 7.8  | Interconnect and driver models a) distributed with constant source resistance [61] b) lumped with nonlinear transistor model [125] c) $\pi_{21}$ with nonlinear transistor model . . . . . | 132 |

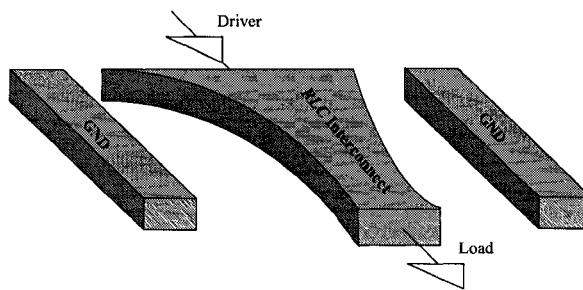

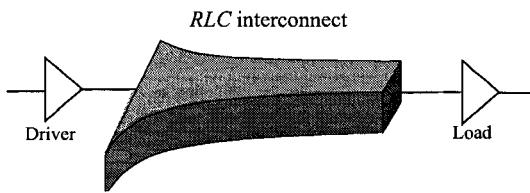

| 8.1  | Coplanar tapered <i>RLC</i> interconnect . . . . .                                                                                                                                         | 141 |

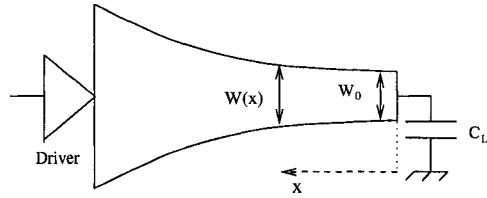

| 8.2  | <i>RLC</i> line tapered by a general width tapering function $W(x)$ . . . . .                                                                                                              | 145 |

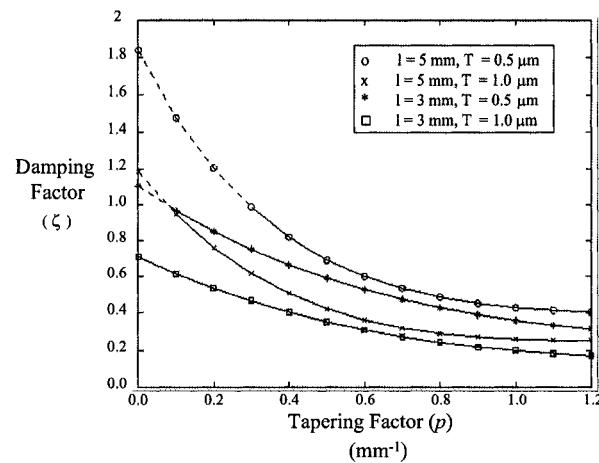

| 8.3  | Interconnect damping factor as a function of the tapering factor for different line parameters . . . . .                                                                                   | 151 |

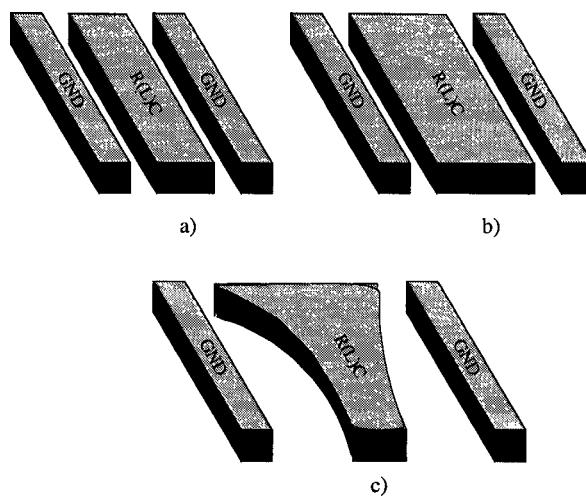

| 8.4  | Coplanar interconnect a) minimum width b) uniform sizing c) exponential tapering . . . . .                                                                                                 | 151 |

| 8.5  | Power dissipation in a load driven by a long tapered interconnect line . . . . .                                                                                                           | 154 |

| 8.6  | Reduction in propagation delay. UWS stands for Uniform Wire Sizing and TWS stands for Tapered Wire Sizing. . . . .                                                                         | 160 |

| 8.7  | Reduction in total power dissipation . . . . .                                                                                                                                             | 161 |

|      |                                                                                                                                                                                                                                      |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

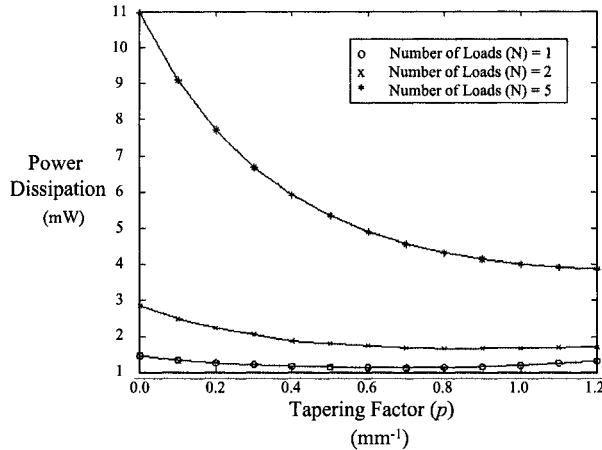

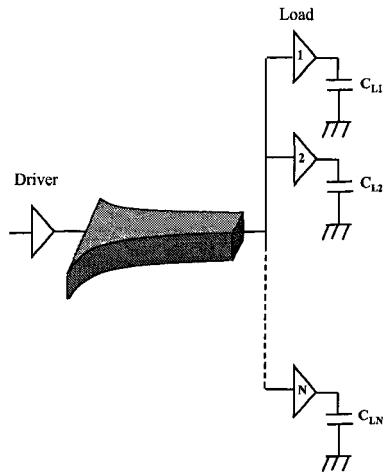

| 8.8  | Power dissipation for different number of loads driven by a long tapered interconnect line . . . . .                                                                                                                                 | 163 |

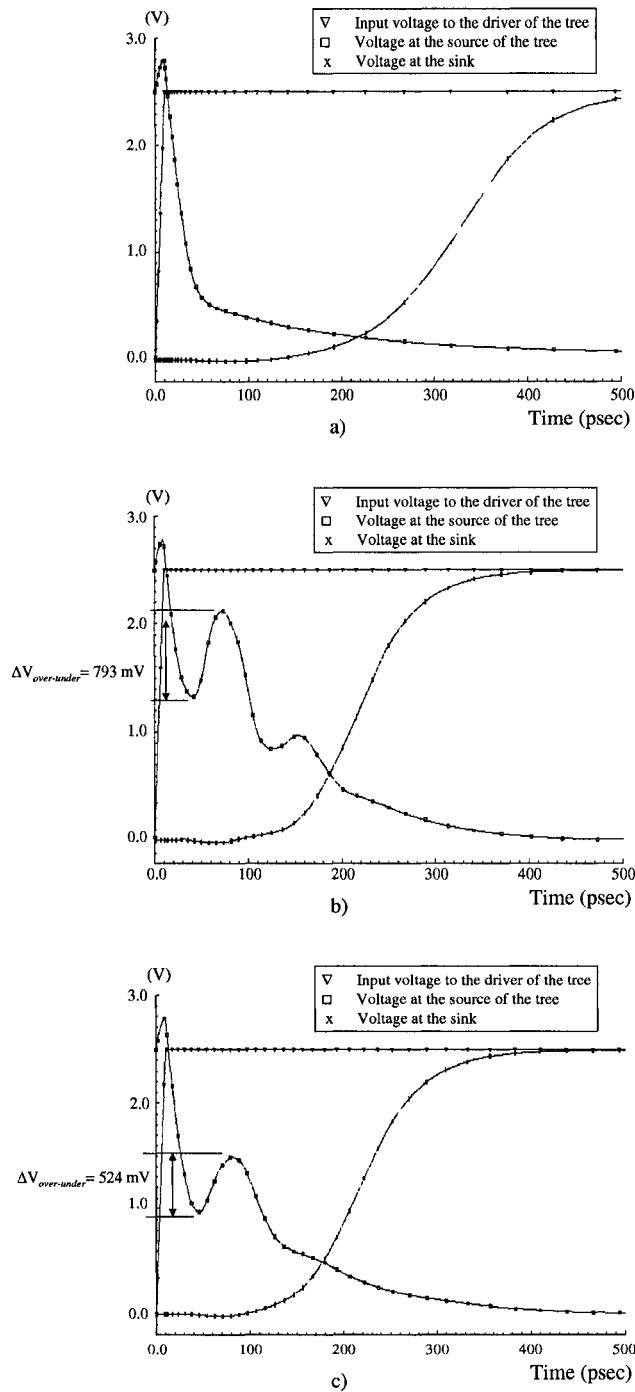

| 8.9  | Waveforms at different nodes within the tree using a) minimum width lines b) uniformly sized lines c) tapered lines . . . . .                                                                                                        | 172 |

| 9.1  | Coplanar tapered <i>RLC</i> interconnect . . . . .                                                                                                                                                                                   | 175 |

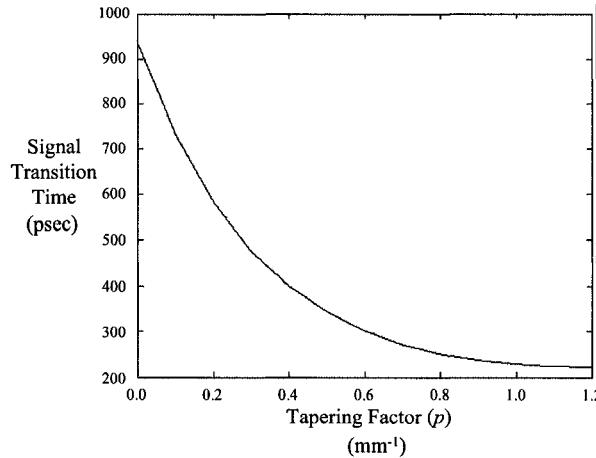

| 9.2  | Signal transition time at the input of a load driven by a long tapered interconnect line . . . . .                                                                                                                                   | 177 |

| 9.3  | Power dissipation in a load driven by a long tapered <i>RLC</i> interconnect line . . . . .                                                                                                                                          | 179 |

| 9.4  | Coplanar tapered <i>RLC</i> interconnect . . . . .                                                                                                                                                                                   | 180 |

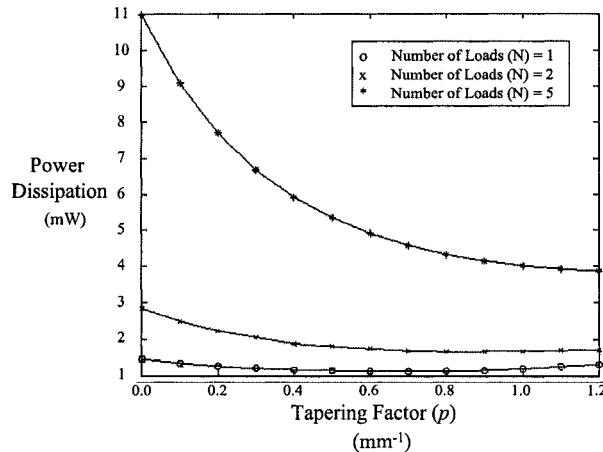

| 9.5  | Power dissipation for different number of loads driven by a long tapered interconnect line . . . . .                                                                                                                                 | 185 |

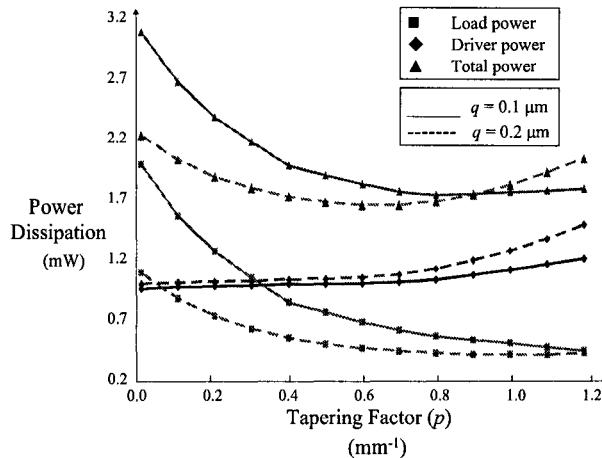

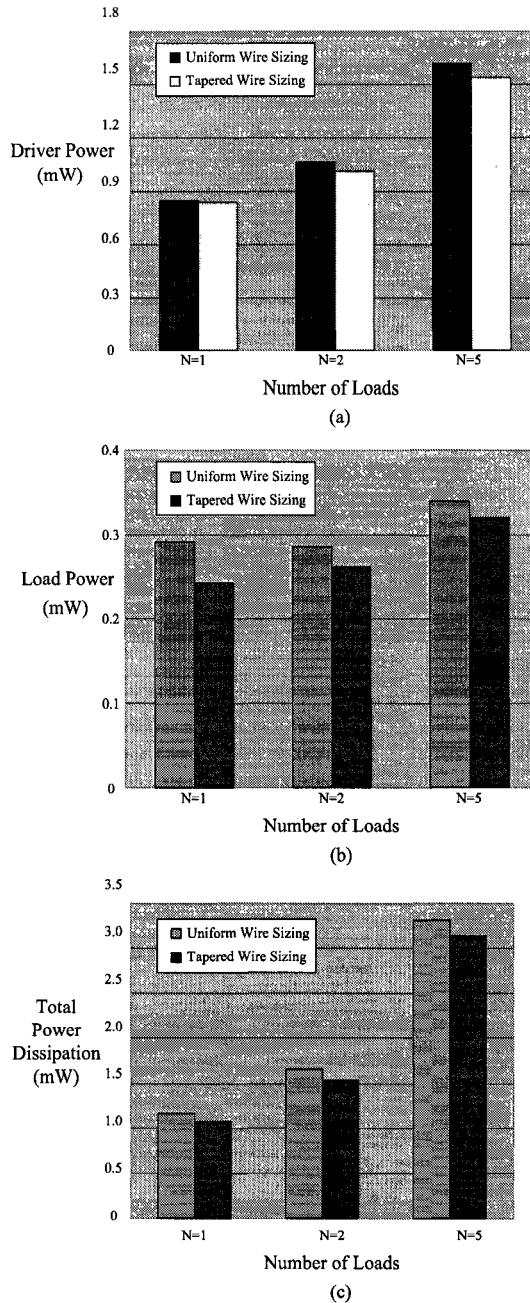

| 9.6  | Power components for different number of loads using optimum tapered and uniform wire sizing a) driver power b) load power c) total power . . . . .                                                                                  | 190 |

| 10.1 | Exponentially tapered H-tree interconnect structure . . . . .                                                                                                                                                                        | 193 |

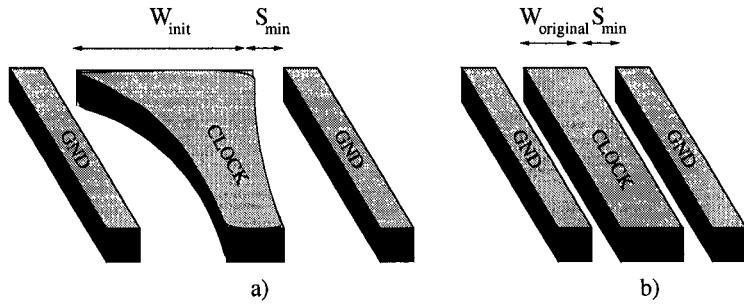

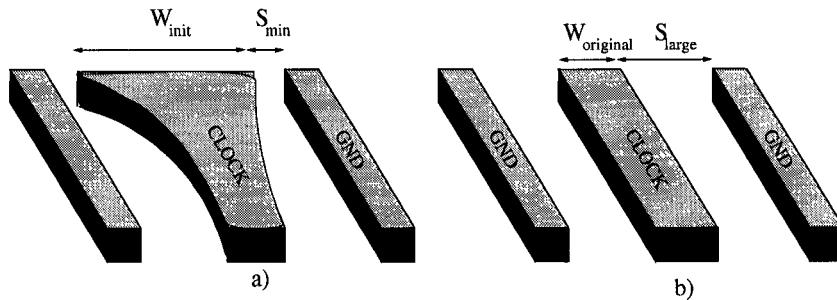

| 10.2 | Coplanar clock line a) exponential tapering b) uniform (no tapering) . . . . .                                                                                                                                                       | 195 |

| 10.3 | Interconnect in an H-tree a) uniform tapering b) exponential tapering . . . . .                                                                                                                                                      | 202 |

| 10.4 | Difference between first overshoot and undershoot for an inductive interconnect . . . . .                                                                                                                                            | 204 |

| 10.5 | Coplanar clock line a) exponential tapering b) uniform line with wider spacing . . . . .                                                                                                                                             | 206 |

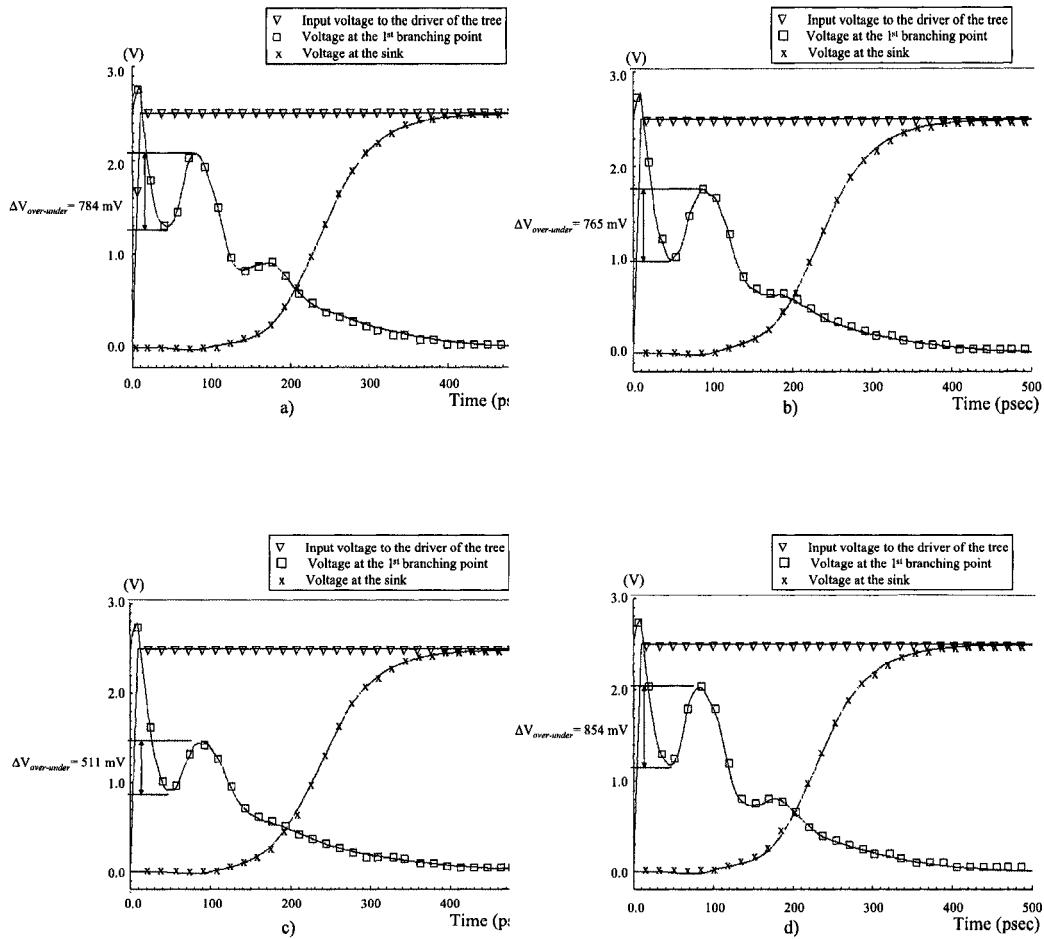

| 10.6 | Waveforms at different nodes within the tree a) uniform tapering b) exponential tapering using first order approximation c) exponential tapering using second order approximation d) uniform tapering (with large spacing) . . . . . | 214 |

| 12.1 | Tapered interconnect line in three dimensions . . . . .                                                                                                                                                                              | 229 |

| 12.2 | 3-D tapered interconnect using sections with different widths and thicknesses . . . . .                                                                                                                                              | 230 |

| 12.3 | 3-D tapered interconnect using long vias . . . . .                                                                                                                                                                                   | 231 |

| 12.4 | Capacitive coupling in current sensing technique . . . . .                                                                                                                                                                           | 233 |

| 12.5 | Inductive coupling in current sensing technique . . . . .                                                                                                                                                                            | 234 |

| 12.6 | Interconnect resistance and inductance with frequency . . . . .                                                                                                                                                                      | 235 |

| C.1  | Discharge currents for the $\pi_{21}$ <i>RLC</i> model . . . . .                                                                                                                                                                     | 278 |

|     |                                                                 |     |

|-----|-----------------------------------------------------------------|-----|

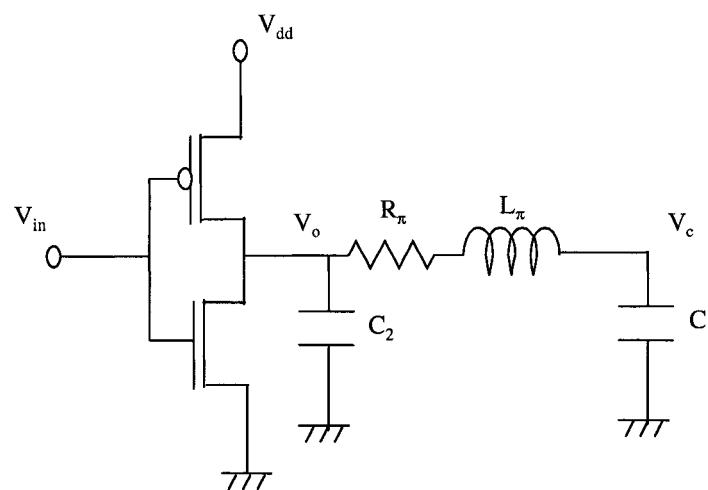

| E.1 | CMOS inverter driving a $\pi_{21}$ interconnect model . . . . . | 283 |

| F.1 | Coplanar tapered line . . . . .                                 | 291 |

| G.1 | Coplanar exponentially tapered interconnect . . . . .           | 294 |

# Chapter 1

## Introduction

On-chip interconnects are now the primary bottleneck in the flow of signals through high complexity, high speed integrated circuits (ICs). Operating an IC at high frequency while dissipating low power is the primary objective for many modern circuit applications. The frequency at which ICs operate increases each year. In order to satisfy these performance objectives, the feature size of CMOS circuits is decreased for each advanced generation of technology. The reduction in feature size reduces the delay of the active devices. The effect on the delay due to the passive interconnects, however, has increased rapidly as described in the National Technology Roadmap [1].

Low power dissipation is another increasingly important design objective in current (and future) ICs. With shrinking feature size, the number of wires grows exponentially [1, 2]. The interconnect capacitance often dominates the total gate load [3]. On-chip interconnects therefore dissipate a large portion of

the total power dissipation. Long interconnects that distribute clock signals and power can dissipate up to 40% to 50% of the total power of an IC [4]. Additional interconnect layers may enhance circuit speed while increasing the power dissipation. Interconnect design has, therefore, become a dominant issue in high speed ICs. Some insight into the complexity of modeling multilayer interconnects at high frequencies is presented in this chapter.

Interconnect wires can be classified into two categories, local wires and global wires. Local wires are those interconnects within logic units that connect the active devices. The delay of the local wires decreases with feature size since the distances among the devices decreases. Global wires are those interconnects that connect different logic units (*e.g.*, busses) or distribute signals across the die (*e.g.*, clock distribution networks). As shown in Fig. 1.1, the delay of local wires decreases while the delay of global wires increases with advancing technology nodes [4]. Despite the reduction in feature size, the die size has tended to increase. The die size has historically doubled every ten years, as shown in Fig. 1.2. The length of the global wires does not scale with technology, while the cross section decreases. The reduction in cross section increases the line resistance and, consequently, the delay required for a signal to propagate along a line. The increase in die size further increases the length of the global lines [6, 7] which further increases the delay. Special

attention should therefore be placed on the global lines, since these lines can limit the overall speed of a circuit [6]-[15].

In order to cope with these trends in advanced technologies, different design methodologies have been developed to decrease the time required for a signal to propagate through a long line. In section 1.1, different models for on-chip interconnect are described. The increasing importance of considering line inductance in the interconnect model is discussed in section 1.2.

Figure 1.1: Relative delay for local and global wiring versus feature size [4]

Figure 1.2: Die size for different generations of Intel microprocessors [5]

## 1.1 Interconnect Modeling

Modeling on-chip interconnect is important to determine the signal characteristics of a line. Accurate modeling enhances both the design and analysis processes. Local lines can often be modeled as a single lumped capacitor, as shown in Fig. 1.3a. If the line capacitance is much smaller than the load capacitance, local lines can be neglected in the delay analysis. Modeling local interconnect by a capacitive load becomes more important as the line capacitance becomes comparable to the load capacitance. Signal propagation through these lines is negligible as compared to the gate delay [16]. Since these lines are short, the resistance is typically negligible. The contribution of the line resistance to the degradation in the signal propagation characteristics is

therefore not significant.

The line resistance impedes the signal propagation in long lines. The delay through these lines can be comparable to or greater than the gate delay. Modeling a global line as a lumped capacitor is often highly inaccurate. Different models have been proposed to model  $RC$  lines. The simplest model is a lumped  $RC$  model as shown in Fig. 1.3b. In order to capture the distributed nature of the line impedance,  $RC$  lines are often divided into sections of distributed impedances [17]-[19]. Each section is modeled as an equivalent  $RC$  circuit. The T and  $\Pi$  circuits, shown in Figs. 1.4a and 1.4b, respectively, are widely used in modeling long interconnects. The accuracy of the model depends upon the number of sections used to model the interconnect. An  $RC$  model is adequate at low to medium frequencies (up to a few hundred MHz). However, at high frequencies (on the order of a GHz), the  $RC$  model is inadequate to accurately characterize the signal. An  $RLC$  model is necessary to accurately characterize these interconnects.

Global lines are usually wide, exhibiting low resistance. With the reduction in line resistance and the increase in clock frequencies, the line inductance has begun to affect the signal propagation characteristics [20]. The inductance should therefore also be considered in the interconnect model. A first order approximation of an inductive interconnect is shown in Fig. 1.3c. The T and

$\Pi$  equivalent distributed models for an  $RLC$  line are shown in Figs. 1.4c and 1.4d, respectively [21, 22].

Figure 1.3: Different lumped interconnect models a)  $C$  model b)  $RC$  model c)  $RLC$  model

## 1.2 Importance of On-Chip Inductance

Many studies have been made to determine the conditions at which the line inductance should be considered in an interconnect model [23]-[25]. The work described in [20] determines the limits on the line length and transition time at which the line inductance should be considered. As the equivalent output resistance of the gate that drives the interconnect decreases, the limits presented in [20] become more accurate. The lower limit on the line length

Figure 1.4: Distributed model for an interconnect a)  $RC$  T model b)  $RC$  II model

c)  $RLC$  T model d)  $RLC$  II model

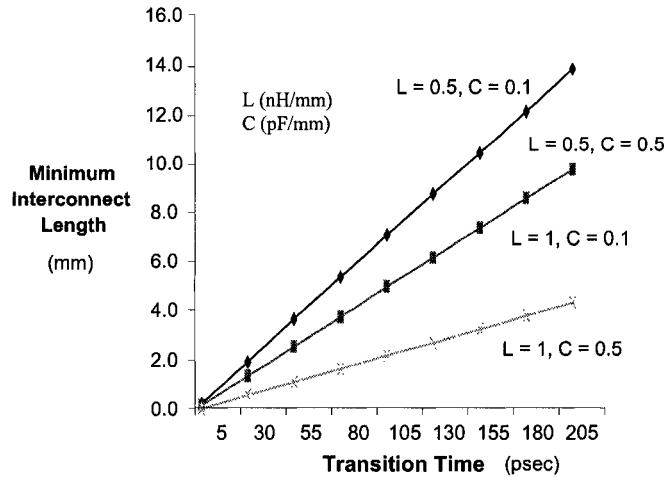

beyond which the line inductance should be considered is shown in Fig. 1.5 for different line impedance parameters ( $L$  is the inductance and  $C$  is the capacitance per unit length, respectively). Increasing signal frequencies typically require faster signal transition times. As the signal transition time decreases, the lower limit on the line length also decreases, making shorter on-chip interconnects behave inductively. Medium length lines which do not behave inductively at low frequency, behave inductively as the frequency increases.

Alternatively, the number of long interconnects has increased rapidly [26]. For example, an IC today may have only 10,000 to 20,000 global nets. This

number, however, is expected to grow to more than 100,000 [27]. Considering the line inductance is, therefore, becoming more crucial in high speed, high complexity integrated circuits [28]-[40].

Figure 1.5: Lower limit of interconnect length above which the inductance should be considered in the line model

Another factor which increases the importance of line inductance is the introduction of new materials. New metal and dielectric materials have been introduced to reduce interconnect delay. Low-k dielectrics can decrease the line capacitance to half the capacitance of  $\text{SiO}_2$ . Furthermore, replacing aluminum lines with copper can also reduce the line resistance by a factor of two to three. These new materials increase the importance of considering the

line inductance. As described in [20], the damping factor  $\zeta$  can be used to characterize the significance of the inductance. For  $\zeta < 1$ , the line is under-damped, causing ringing in the signal. As shown in Fig. 1.6, when advanced materials are used, the damping factor decreases, increasing the importance of considering the line inductance.

Figure 1.6: Damping factor as a function of the line inductance for different dielectric and metal materials

Different techniques to drive long interconnects are reviewed in Chapter 2. In order to drive global interconnects, many design methodologies have been proposed. Different design techniques have been developed to reduce the propagation delay along long resistive line. These techniques ignore the line

inductance, which may lead to area and/or power inefficient circuits. In this chapter, efficient techniques to drive global *RC* interconnects are reviewed.

In Chapter 3, different aspects regarding the complexity of extracting circuit parameters at high frequencies are discussed. On-chip inductance extraction and analysis are becoming more critical at higher frequencies and smaller feature sizes. Extracting on-chip inductance in large circuits is a complicated process. An overview of inductance extraction importance and difficulties is presented in this chapter. Furthermore, the most widely used techniques to simplify the extraction process are also summarized. A comparison between the most efficient techniques is provided.

Resistive power dissipation in CMOS circuits is characterized for both *RC* and *RLC* lines in Chapter 4. Interconnect resistance dissipates a portion of the total transient power in CMOS circuits. Conduction losses increase with larger interconnect resistance. It is shown in this chapter that these losses do not add to the total power dissipation of a CMOS circuit through  $I^2R$  losses. Interconnect resistance can, however, increase the short-circuit power of both the driver and load gates. The effects of interconnect line resistance on the primary components of the transient power dissipation are described in both *RC* and *RLC* lines.

In Chapter 5, power characteristics of an inductive interconnect are de-

scribed. The width of an interconnect line affects the total power consumed by a circuit. The effect of wire sizing on the power characteristics of an inductive interconnect line is presented in this chapter. The matching condition between the driver and the load affects the power consumption since the short-circuit power dissipation may decrease and the dynamic power will increase with wider lines. A tradeoff therefore exists between short-circuit and dynamic power in inductive interconnects. The power characteristics of inductive interconnects therefore may have a great influence on wire sizing optimization techniques. An analytic solution of the transition time of a signal propagating along an inductive interconnect is presented. The solution is useful in wire sizing synthesis techniques to decrease the overall power dissipation. The optimum line width that minimizes the total transient power dissipation is determined. An analytic solution for the optimum width is presented. Considering the driver size in the design process, the optimum wire and driver size that minimizes the total transient power is also determined.

For long lines, repeaters are usually used to drive the interconnect. Power and delay characteristics of a long inductive interconnect driven by a repeater system are presented in Chapter 6. Repeaters are often used to drive high impedance interconnects. These lines have become highly inductive and can affect signal behavior in long interconnects. The line inductance should

therefore be considered in determining the optimum number and size of the repeaters driving a line. The optimum repeater system uses uniform repeater insertion in order to achieve the minimum propagation delay. A tradeoff exists, however, between the transient power dissipation and the minimum propagation delay in sizing long interconnects driven by the optimum repeater system. Optimizing the line width to achieve the minimum power delay product, however, can satisfy current high speed, low power design objectives. The Power-Delay-Area-Product criterion is introduced as an efficient technique to size the interconnect within a repeater system.

In Chapter 7, the shielding effect of line inductance is introduced. Interconnect inductance introduces a shielding effect which decreases the effective capacitance seen by the driver of a circuit, reducing the gate delay. A model of the effective capacitance of an *RLC* load driven by a CMOS inverter is presented. The interconnect inductance decreases the gate delay and increases the time required for the signal to propagate across an interconnect, reducing the overall delay to drive an *RLC* load. Ignoring the line inductance overestimates the circuit delay, inefficiently oversizing the circuit driver. Considering line inductance in the design process saves gate area, reducing dynamic power dissipation. An accurate model for a CMOS inverter and an *RLC* load is used to characterize the propagation delay.

The optimum interconnect shape that minimizes the signal propagation delay along *RLC* lines is determined in Chapter 8. The optimum wire shape to produce the minimum signal propagation delay across an *RLC* line is shown to have a general exponential form. The line inductance makes exponential tapering more attractive for *RLC* lines than for *RC* lines. For *RLC* lines, optimum wire tapering achieves a greater reduction in the signal propagation delay as compared to uniform wire sizing. Wire tapering can reduce both the propagation delay and power dissipation. For *RLC* lines, exponential tapering outperforms uniform repeater insertion. As technology advances, wire tapering becomes more effective than repeater insertion, since a greater reduction in the propagation delay is achieved. Wire tapering can also improve signal integrity by reducing the inductive noise of the interconnect lines. Wire tapering reduces the effect of impedance mismatch in digital circuits.

In Chapter 9, the optimum tapered structure for an *RLC* interconnect to minimize transient power dissipation of a circuit is determined. An analytic solution to determine the optimum tapered structure is provided in this chapter. Wire tapering can reduce the power dissipation of a circuit. Wire tapering is more efficient than uniform wire sizing in reducing the transient power dissipation. Optimum wire tapering can reduce the power dissipation

as compared to uniform wire sizing.

In Chapter 10, a practical implementation for the optimum interconnect shaping is applied to the H-tree clock distribution networks. Exponentially tapered interconnects can reduce the dynamic power dissipation of clock distribution networks. A criterion for sizing H-tree clock networks is proposed. The technique reduces the power dissipated for an example clock network while preserving the signal transition times and propagation delays. Furthermore, the inductive behavior of the interconnects is reduced, decreasing the inductive noise. Exponentially tapered interconnects decrease the difference between the overshoots in the signal at the input of a tree. As compared to a uniform tree with the same area overhead, overshoots in the signal waveform at the source of the tree are reduced.

The dissertation is concluded in Chapter 11. In Chapter 12, other aspects which should be considered when developing design methodologies in the future are discussed.

# Chapter 2

## Design Methodologies to Drive RC Interconnects

### 2.1 Introduction

As interconnect has become a dominant issue in high speed ICs, different design methodologies have been developed to improve the performance of long interconnects. These methodologies have historically concentrated on the distributed resistance of a long line. The most effective techniques used to drive long *RC* interconnect are discussed in the following sections. In section 2.2, wire sizing is presented as an effective technique to increase circuit speed. Uniform repeater insertion is another effective technique as described in section 2.3. In section 2.4, optimum wire shaping for minimum signal propagation delay is discussed.

## 2.2 Wire Sizing

Interconnect widening decreases the interconnect resistance while increasing the capacitance. Many algorithms have been proposed to determine the optimum wire size that minimizes a target cost function. Some of these algorithms address reliability issues by reducing clock skew. Most of the previous work concentrate on minimizing delay [41]-[46]. The results described in [47]-[51] consider simultaneous driver and wire sizing based on the Elmore delay model with simple capacitance, resistance, and power models. As the inductance becomes important, specific algorithms have been enhanced that consider *RLC* impedance models [52]-[55].

Previous studies in wire and driver sizing have not considered changes in the signal characteristics accompanied with changes in the characteristics of the line impedance. The interconnect impedance characteristics are more sensitive to the wire size in long, inductive interconnects. The work described in [48, 51] considers power dissipation while ignoring the inductive behavior of the interconnect and, therefore, the effect of line inductance on the power characteristics. In Chapter 5, the power characteristics of an inductive interconnect are described. Changes in the matching characteristics are discussed in terms of sizing the inductive interconnect for minimum power and delay.

## 2.3 Repeater Insertion

Uniform repeater insertion is an effective technique for driving long interconnects. The objective of a uniform repeater insertion system is to minimize the time for a signal to propagate through a long interconnect. Based on a distributed  $RC$  interconnect model, a repeater insertion technique to minimize signal propagation delay is introduced in [56]. Uniform repeater insertion techniques divide the interconnect into equal sections, employing equal size repeaters to drive each section as shown in Fig. 2.1. Bakoglu and Meindl developed closed form expressions for the optimum number and size of the repeaters to achieve the minimum signal propagation delay in an  $RC$  interconnect [56]. A uniform repeater structure decreases the total delay as compared to a tapered buffer structure when driving long resistive interconnects while buffer tapering is more efficient for driving large capacitive loads [57]. Adler and Friedman developed a timing model of a CMOS inverter driving an  $RC$  load [58, 59]. The authors used this model to enhance the repeater insertion process for  $RC$  interconnects. Alpert considered the interconnect width as a design parameter [60]. He showed that, for  $RC$  lines, repeater insertion outperforms wire sizing. As shown in Chapter 6, this behavior is not the case for an  $RLC$  line. The minimum signal propagation delay always decreases with line width for  $RLC$  lines if a repeater system is used.

Figure 2.1: Uniform repeater system driving a distributed  $RC$  interconnect

The delay can be greatly affected by the line inductance, particularly for low resistance materials and fast signal transitions. Ismail and Friedman extended previous research in repeater insertion by considering the line inductance [61]. The authors showed that on-chip inductance can minimize the speed, area, and power of the repeater insertion process as compared to an  $RC$  line model. Banerjee and Mehrotra developed an analytic delay model and methodology for inserting repeaters into distributed  $RLC$  interconnect which demonstrated the importance of including line inductance as technologies advance [62]-[65].

With increasing demands for low power ICs, different strategies have been developed to minimize power in optimizing the repeater insertion process. Power dissipation and area have been considered in previous work. The line inductance, however, has yet to be considered in the optimization process of sizing a wire driven by a repeater system. Tradeoffs in repeater systems driving inductive interconnect are described in Chapter 6.

## 2.4 Interconnect Shaping

Another technique to reduce the signal propagation delay is to shape the interconnect line. Interconnect shaping changes the interconnect width from the driver to the load as shown in Fig. 2.2. As described in [66, 67], the optimum interconnect shape which minimizes the signal propagation delay in an *RC* interconnect is an exponential function. Different extensions to this work have been applied to consider other circuit parameters such as fringing capacitance [68]-[83].

Figure 2.2: Tapered *RC* interconnect

The research described in [60] shows that wire tapering improves the speed by only 3.5% as compared to uniform wire sizing if an optimum repeater system is used to minimize the propagation delay of an *RC* line. The inductance,

however, has not been considered in the line model described in [60]. The inserted repeaters increase the dynamic power due to the additional input capacitance of the repeaters. In Chapter 8, the optimum shape of an *RLC* line that minimizes the delay is determined.

# Chapter 3

## Inductance Extraction

### 3.1 Introduction

In order to consider line inductance in the design process, an accurate estimate of the line inductance needs to be determined. Determining the inductance of an interconnect surrounded by a complicated metal structure is not an easy process. Inductance extraction is the process of computing the complex frequency-dependent impedance matrix of a multi-terminal conductor, such as an electrical interconnect, under the magneto-quasistatic approximation [84].

Inductance extraction is significantly more difficult than either resistance and capacitance extraction. If skin and proximity effects are neglected, the

line resistance is independent of the geometric structure of the surrounding interconnects [85]. The resistance depends only on how current flows through the interconnect line. As shown in Fig. 3.1, the interconnect capacitance is typically highly localized. The line capacitance depends on the geometric structure of the interconnect line and the adjacent lines. The electric field lines terminate at the nearest metal surface, binding the capacitive coupling to the adjacent metal structure.

Unlike electric field lines, magnetic field lines extend to infinity, making the mutual inductive coupling with distant lines significant and potentially important in determining the line inductance. Inductance calculations require determining the current return path which is difficult in non-systematic and complicated structures [86].

At high frequencies, non-uniform current distribution flows through the interconnect cross section, causing a change in the conductor inductance due to proximity and skin effects [87]. Also, increasing circuit size requires considerable time to analyze and determine the inductance of each conductor in a circuit.

Different techniques have been developed to simplify the extraction process [88]-[113]. Most of these techniques are based on the partial element equivalent circuit (PEEC) to create an inductance matrix for a target net-

Figure 3.1: Example of electric and magnetic field lines to illustrate the difference among resistive, capacitive, and inductive extraction

work. This matrix is usually dense which requires sparsification to accelerate the extraction process. The most efficient sparsification approaches can be partitioned into four techniques; shell technique, hierarchical technique, halo technique, and K Matrix technique. Each of these techniques are briefly summarized in the following sections.

## 3.2 Shell Technique

This technique was first proposed by Krauter and Pileggi [89]. The authors assume that all of the current return paths are at a finite and constant radius  $r_0$  from the origin as shown in Fig. 3.2. No inductive coupling is assumed outside of this radius. The inductance values of the segments within the radius are shifted to account for those entries that have been dropped as a result of truncation. This shift-truncate method can guarantee that positive definite sparse approximations of the original matrix are always produced. An extension of this technique is an ellipsoid shell, which is more suitable for conductor filament structures [90]. The primary difficulty with this technique is determining the appropriate radius  $r_0$ .

## 3.3 Hierarchical Technique

The hierarchical technique was first proposed by Beattie *et al.* [91]. Two auxiliary nodes are introduced to model the coupling between two groups of conductors by a single value. The new global circuit node variables represent the averaged source and potential values over an entire group of conductors

Figure 3.2: Spherical shell of return current  $i$  at a radius  $r_0$  [89]

as shown in Fig. 3.3

Figure 3.3: Example system: A,B- aggressor groups; G,H- victim groups [91]

As an example, groups A and B are considered the aggressor groups and G and H are the victim groups. To calculate the flux induced on a specific conductor in group G, (3.1) and (3.2) are used. Without calculating the flux

induced from each conductor element in A and B, the flux can be calculated in a hierarchical fashion. This approach avoids calculating the flux induced from each conductor in the system, but adds an overhead to the simulation runtime and memory.

$$\phi_{GH,A} = \sum_{i \in A} [\bigcup_{j \in GH} L_{ji}] * I_{Ai}, \quad (3.1)$$

$$\phi_{Gj,AB} = \phi_{Gj,AB} * \left[ \sum_{i \in AB} L_{ji} / \sum_{i \in AB} [\bigcup_{j \in G} L_{ji}] * I_{Ai} \right]. \quad (3.2)$$

### 3.4 Halo Technique

Another approach for limiting the inductive interaction was proposed by Shepared and Tian [88]. This approach introduces return-limited inductances for sparsification and the use of "halos" to limit the number of mutual inductances. The technique separately performs inductance modeling of the signal and power/ground lines. The technique assumes a halo region surrounds the ground lines as shown in Fig. 3.4.

No mutual inductance should be considered between two conductors separated by a halo region. This approach exploits the power and ground distri-

Figure 3.4: The halo of a target segment consisting of six semi-infinite regions [88]

bution networks to localize the inductive coupling.

### 3.5 $K$ Matrix Technique

The authors in [92] noticed the relation between the inductance and capacitance of a transmission line represented by

$$[L_{Loop}] = \mu_0 \epsilon_0 [C_0]^{-1}. \quad (3.3)$$

For a sparse capacitance matrix, Devgan, Ji, and Dai expected that if the inductance matrix is dense, the inverse matrix should be sparse. They proposed a new circuit matrix,

$$[K] = [L]^{-1}, \quad (3.4)$$

where  $K$  is the inverse of the partial inductance matrix. The  $K$  matrix has locality and sparsity normally associated with a capacitance matrix. A simulator called KSim has also been developed [93]. The simulator is used to directly analyze the  $RKC$  circuit rather than the  $RLC$  equivalent circuit by inserting the transient model of  $K$  into SPICE. This technique requires the partial inductance matrix to be inverted and a special simulator to analyze the circuit.

### 3.6 Comparison between Different Inductance Extraction Techniques

In this subsection, some observations and comments are provided that describe the strengths and weaknesses of each technique. The primary difficulty with the shell technique is determining the radius of the shell [95]. If the radius is too large, the solution may be inefficient as the inductance matrix will

be quite large. Alternatively, if the radius is too small, the solution may be inaccurate because some important elements may have been neglected. The shell technique includes any inductance within a certain geometric distance from the origin whether the included inductance is significant or not. Many mutual inductances may be included which have no significant effect on the signal behavior.

The halo technique is more efficient. By assuming the current return path is in the nearest ground lines, the technique exploits the shielding effect of the power and ground traces. This technique can be highly inaccurate and strongly depends on the nature of the geometric structures. Three circuits are used to compare the two techniques. The number of nonzero elements in the inductance matrix is listed in Table 3.1.

Table 3.1: Number of nonzero elements in the inductance matrix

| Circuit | Shell radius |            |            | Halo Technique |

|---------|--------------|------------|------------|----------------|

|         | 50 $\mu m$   | 25 $\mu m$ | 10 $\mu m$ |                |

| 1       | 3297         | 1297       | 465        | 132            |

| 2       | 3075         | 1427       | 859        | 178            |

| 3       | 6103         | 2513       | 681        | 597            |

The accuracy of the shell technique does not achieve that of the halo technique until the shell radius reaches  $50 \mu m$ , which greatly increases the number of elements included in the matrix, thereby requiring larger memory and CPU time.

One of the most promising techniques is the  $K$  matrix method. Since the  $K$  matrix is sparse, no additional steps are required to determine which inductance should be considered. To compare the  $K$  matrix with the shell technique, the CPU time and memory required for both techniques are listed in Table 3.2. If the special simulator, which considers the  $K$  element rather than the  $L$  element, becomes more popular, this technique has significant potential.

Table 3.2: CPU time and memory usage for different inductance extraction methods

| Method            | CPU time (s) | Memory (MB) |

|-------------------|--------------|-------------|

| Full $L$ Matrix   | 734          | 20          |

| Shell method      | 144          | 6           |

| $K$ matrix method | 17           | 3           |

The work described in [94] is a table based inductance extraction method which considers the common structure of the  $N$  conductors in the metal layers

of an IC. Techniques such as hierarchical and table based techniques are not widely used. The hierarchical technique requires significant overhead in both CPU time and memory, and is therefore unacceptable in large circuits. Table based techniques are not applicable to any structure. Only symmetric structures can be evaluated, making these approaches not generally useful.

Different design methodologies to drive long, inductive interconnect are discussed in following chapters. At high frequencies, long interconnects should be treated as lossy transmission lines. Transmission line properties affect the signal characteristics and change the nature of the circuit design methodologies. In the following chapters, different design methodologies are reevaluated assuming an inductive environment.

## Chapter 4

# Resistive Power in CMOS Circuits

### 4.1 Introduction