# A system for critical path analysis based on back annotation and distributed interconnect impedance models

G.Y. Yacoub, H. Pham, M. Ma and E.G. Friedman Hughes Aircraft Company, Carlsbad, CA, USA

This paper describes a VLSI CAD system that automatically selects optimal interconnect impedance models and embeds them into circuit simulation files each identified as a critical worst case timing path. The CAD system initially identifies pre-layout critical timing paths and back annotates these paths with post-layout interconnect impedances. Accurate post-layout resistive and capacitive interconnect impedances are automatically extracted, their magnitudes are compared to the path specific device dependent RC loads of each cell-to-cell node, and an appropriate RC lumped model is selected to optimally model the distributed nature of the RC interconnect impedance of that particular cell-to-cell node. These interconnect RC impedance models are then back annotated into a SPICE formatted circuit simulation file for the precise determination of the timing behaviour of these critical paths. Therefore, timing accuracy and CPU efficiency are optimised on a node by node basis. This analysis system is tailored to support high performance circuits while maintaining automated layout database independence and maximal design flexibility.

# 1. Introduction

Comprehensive detailed circuit analysis has traditionally been an important bottleneck in VLSI circuit design for two main reasons. The first is the large amount of time required for manually identifying all possible critical signal paths from among thousands of total paths that can exist in a VLSI circuit. The second is the tedious construction of a circuit simulation file and the use of manually operated iterative optimisation techniques for accurately analysing these critical signal paths. Many papers have been published which individually discuss timing analysis 1 4, interconnect parasitic extraction 5 6, distributed interconnect parasitic impedances<sup>7</sup>, and back annotation<sup>8</sup>. Other papers on VLSI design systems and their methodologies<sup>9</sup> 12 discuss the relative importance and utility of these capabilities. However, minimal work has been performed to automatically embed optimal circuit netlist models into detailed circuit simulation files based on back annotation of accurately modeled interconnect impedances. This paper presents a CAD system which identifies prelayout critical timing paths, annotates these paths with post-layout interconnect impedances which are modeled in an optimally accurate fashion, and inserts these RC impedances into circuit simulation files developed for each critical path. This system has been specifically tailored to support high performance VLSI complexity circuits while maintaining automated layout database independence and maximal design flexibility.

### 2. System overview

This integrated timing analysis system is composed of two tools that work in concert with each other to generate multiple circuit simulation files accurately representing a circuit's

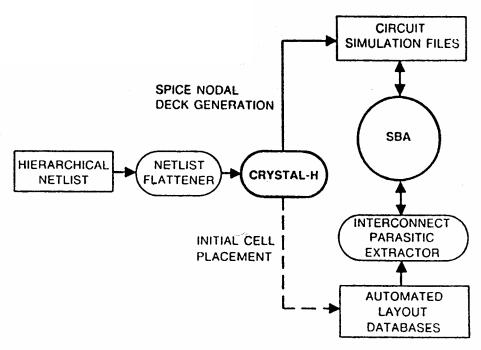

Fig. 1 Iterative performance optimisation environment based on back annotation of interconnect impedances

critical timing paths. This CAD system utilises a unified data structure, thereby making it compatible with virtually any existing automated layout systems. Fig. 1 illustrates the use of the system in a VLSI circuit design and analysis environment.

### 2.1 Generation of a critical path's circuit simulation file

In order to determine which paths in a VLSI circuit are constrained by their timing behaviour, a timing analyser is used to identify critical paths. The timing analyser used is Crystal-H, a modified version of the University of California at Berkeley's timing analyser program<sup>13</sup>, Crystal-2. It performs CMOS transistor level pre-layout worst case path selection based on user defined inputs. The critical signal paths identified by Crystal-H are formatted into nodal decks in SPICE format, each containing a worst case critical timing path. All unused input pins of branch cells along the critical circuit path are automatically grounded while all output pins not belonging to the circuit path are tied to predefined load capacitors.

# 2.2 Automatic back annotation of interconnect parasitic impedances

In order to analyse accurately the effect of interconnect impedances on circuit performance, a CAD system for automatically extracting parasitic interconnect impedances and embedding them into a circuit simulation file predefined by Crystal-H has been developed. This tool is our Simulation Back Annotation (SBA) program. SBA accepts multiple nodal decks formatted by Crystal-H and invokes an in-house developed Parasitic Extraction program<sup>5</sup> to determine accurate parasitic resistive and capacitive interconnect impedances for each intercellular net. The Parasitic Extractor program references an automated layout database to determine the specific technology dependent interconnect parasitic impedances for the specific nets along the critical path. These lumped interconnect parasitic

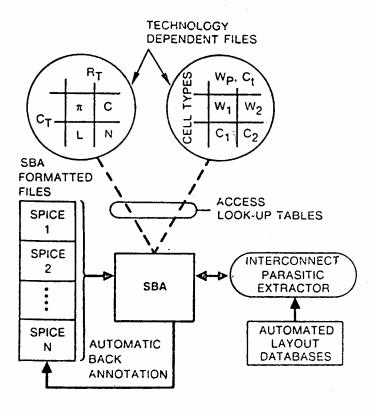

Fig. 2 Automatic back annotation based on optimal selection of lumped interconnect models

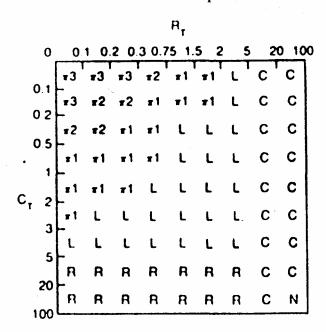

impedances, Rw and Cw, are used to compute the ratios,  $R_T = \frac{r_t}{Rw}$  and  $C_T = \frac{C_t}{Cw}$ , after accessing

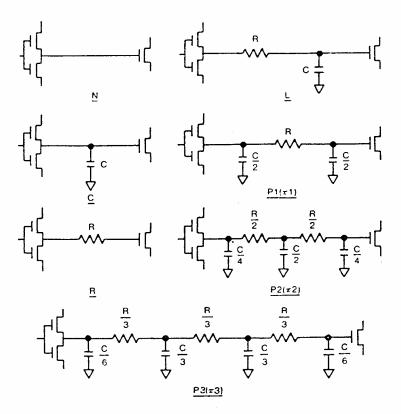

one of two technology specific look-up tables, as shown in Fig. 2.  $r_1$  and  $C_1$  represent the device dependent output resistance and load capacitance and are defined below. These ratios are used to select one of seven different lumped interconnect impedance networks,  $\pi 3$ ,  $\pi 2$ ,  $\pi 1$ , L, R, C, or N (see Fig. 3) for each RC load from the second technology specific look-up table, as depicted in Fig. 2. Once the impedance network is optimally selected, SBA automatically back annotates the SPICE nodal decks with the appropriate interconnect impedance network configuration. Distributed impedance model selection and back annotation can be iteratively changed as the layout's routing is optimised. Fig. 2 illustrates the total SBA environment.

## 3. Circuit analysis

It is common practice within the industry to use a lumped one-section ladder network to model distributed RC transistor interconnect load impedances. This lumped network guarantees an upper bound (i.e., worst case) time delay for critical path timing analysis and a minimum number of nodes for CPU computational efficiency. However, this upper bound can lead to appreciable circuit over-design which increases with the relative magnitude of the interconnect delay between register elements in a data path. Thus, a more accurate representation of the interconnect delay will permit the design of higher performance circuits. Therefore, the design technique described within this paper is directly oriented to high speed and high precision VLSI circuit design.

Fig. 3 Lumped circuit models used to approximate distributed RC interconnect impedance

# 3.1 Definition of symbols

W<sub>P</sub> : PMOS transistor width (micrometres)

Rw : Lumped wire resistance (ohms)

Cw : Lumped wire capacitance (femtofarads)

: Lower bound transistor output impedance, (max drain conductance)

C: Lumped transistor input capacitance (femtofarads)

V<sub>in</sub> : MOS transistor input voltage (volts)

$V_{tp}$ : PMOS transistor threshold voltage, negative for enhancement devices

(volts)

V<sub>dsp</sub>, V<sub>dsn</sub> : PMOS and NMOS transistor source-drain voltages, respectively (volts)

V<sub>DD</sub> : Power supply voltage (volts)

$\infty$ : Relative Modulation Factor between  $r_t$  and  $W_p$  (dimensionless)

$\beta_P$ : PMOS transistor gain factor  $\left(\frac{\text{farads}}{\text{volt-second}}\right)$

$C_T = \frac{C_t}{C_w}$ , ratio of the transistor input capacitance to the lumped wire capacitance

$R_T = \frac{r_t}{R_w}$ , ratio of the transistor output resistance to the lumped wire resistance

# 3.2 Calculation of CMOS output impedance

The output impedance of a driver is a complex relationship among several factors such as a device's process parameters, the shape of the input transient waveform, the output resistive and capacitive loading, the circuit environmental conditions, and the layout design style. Lower r bounds are used in this design technique since they are more sensitive to capacitive interconnect impedances and thereby require greater accuracy of the distributed interconnect impedance models.

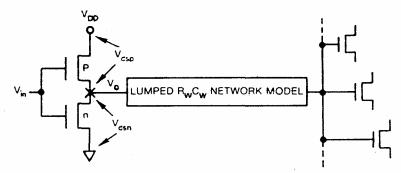

Fig. 4 CMOS ratioed buffer driving interconnect and device loads

The drain current equations of a typical ratioed buffer represented in Fig. 4 which correspond to a minimum PMOS output impedance are defined below<sup>15</sup>:

It that the threshold to a minimum PMOS output impedance are defined below 15:

$$I_{dsp} = -\beta_p \left[ (V_{in} - V_{DD} - V_{tp}) (V_{dsp}) - \frac{1}{2} V_{dsp}^2 \right]$$

$$V_o \leqslant V_{in} - V_{tp}$$

$$0 \leqslant V_{in} \leqslant V_{tn}$$

$$V_{tp} \leqslant V_o \leqslant V_{DD}$$

(2)

where,

$$\beta_{\rm p} = \frac{W_{\rm p}}{L_{\rm p}} \mu_{\rm p} C_{\rm ox} \tag{3}$$

The above equations define the drain current of a PMOS transistor when operating in the linear mode and the drain current of a NMOS transistor when operating in the cutoff mode. Since the PMOS and NMOS devices are assumed to be geometrically ratioed, the drain-tosource current is equivalent for both devices when operating in the same I-V region. As the input voltage V<sub>in</sub> and the drain voltage V<sub>dsp</sub> approach zero, the PMOS lower bound output impedance will approach  $r_1$  as described in equations (4) and (5) below.

$$(r_i)^{-1} = \lim_{V_{in}, V_{dSp} \to 0} \frac{dI_{dsp}}{dV_{dsp}} = \beta_p (V_{DD} + V_{tp})$$

(4)

Therefore,

$$\mathbf{r}_{t} = \frac{1}{\beta_{p} \left( \mathbf{V}_{DD} + \mathbf{V}_{tp} \right)} \tag{5}$$

The transconductance of a device,  $(r_1)^{-1}$ , is linearly dependent upon its width as described by equations (3) and (5). The larger the device width, the greater its transconductance. This relationship between device output impedance and geometric width is shown in equation (6). Thus, for a given value of  $\alpha$ , process parameters, and bias conditions,  $r_1$  can be determined directly from  $W_p$ .

$$r_{t} = \frac{1}{\beta_{P} (V_{DD} + V_{tp})} = \alpha \frac{1}{\beta_{P} V_{DD}} = \alpha \frac{1}{W_{P}} \frac{L_{P}}{\mu_{P} Cox} \frac{1}{V_{DD}}$$

(6)

where,

$$\propto = \frac{V_{DD}}{V_{DD} + V_{tp}} \text{ and } \beta_{p} V_{DD} \text{ is described in reference 16.}$$

(7)

$\alpha$  is always larger than one for a typical enhancement PMOS device since  $V_{\pi}$  is negative. Thus, one can determine the device output impedance directly from a given device geometric width under a given set of environmental conditions.

The Relative Modulation Factor  $\alpha$  is sensitive to the circuit environment as depicted in Table 1 since both  $V_{DD}$  and  $V_{\Phi}$  can change.  $V_{\Phi}$  is depicted in Table 1 as an implicit function of temperature and process parameters. This table has been calibrated for an in-house CMOS technology. The dependence of  $V_{\Phi}$  on  $\alpha$  and  $V_{DD}$  can be explicitly described and this relationship is defined in equation (8) below.

$$V_{p} = V_{DD} \left( \frac{1-\alpha}{\alpha} \right) \tag{8}$$

Thus, precharacterised data from Table 1 provide a precise measure of the effect of various environmental conditions on the magnitude of the P-channel threshold voltage. Values of r have been determined by Sakurai<sup>7</sup> with the added sophistication of considering the effect of varying circuit environmental conditions on the value of  $\alpha$ . Thus, for a given value of  $\alpha$ , an estimate of the output resistance of a ratioed buffer can be made and this value can be used to optimally model that output node's interconnect impedance.

TABLE I Values of the relative modultation factor  $\alpha$  as a function of circuit environmental conditions

| V <sub>DD</sub> (V) | TEMP (°C) | PROCESS<br>PARAMETERS | α    |

|---------------------|-----------|-----------------------|------|

| 4.5                 | 27        | BEST                  | 1.50 |

| 4.5                 | 85        | NOMINAL               | 2.23 |

| 4.5                 | 125       | WORST                 | 2.92 |

| 5.0                 | 27        | BEST                  | 1.34 |

| 5.0                 | 85        | NOMINAL               | 2.01 |

| 5.0                 | 125       | WORST                 | 2.61 |

| 5.5                 | 27        | BEST                  | 1.22 |

| 5.5                 | 85        | NOMINAL               | 1.83 |

| 5.5                 | 125       | WORST                 | 2.37 |

# 3.3 Determination of optimal interconnect impedance network

For each cell type in a given cell library, the input capacitive load and the output drive resistance described in terms of P-channel device width is defined in a look-up table, exemplified by Table 2. From these values of  $r_t$  and  $C_T$ , each node's interconnect impedances ( $R_W$  and  $C_W$ ), and a user defined value for  $\alpha$ , SBA computes the ratios  $R_T$  and  $C_T$ . These ratios represent the relative magnitude of the transistor impedance,  $r_t$  and  $C_t$ , to its interconnect impedance,  $R_W$  and  $C_W$ , as described in equations (9) and (10) below.

$$\mathbf{R}_{\mathrm{T}} = \frac{\mathbf{r}_{\mathrm{t}}}{\mathbf{R}_{\mathrm{w}}} \tag{9}$$

$$C_{T} = \frac{C_{t}}{C_{w}} \tag{10}$$

TABLE II Lumped interconnect circuit models used by SBA to model distributed RC interconnect impedance

After computing  $R_T$  and  $C_T$ , SBA accesses a second look-up table, as described in Table 2, to select an optimum lumped network model for each net under study. Table 2 was constructed based on the relative error of the signal transition time between a one-section ladder network and a one-section  $\pi$  network<sup>17</sup> for various values of  $R_T$  and  $C_T$ . Table 2 assumes that an L network is chosen over a one-section network when the relative signal transistion error is less than 10%. When the relative error is between 10% and 35%, a two-section  $\pi$  network is chosen while a three-section network is chosen for larger errors. Thus, a favourable compromise position between circuit accuracy and computational efficiency is maintained.

The choice of error breakpoint is both technology and design style dependent and can be

TABLE III SBA VAX 11/750 CPU time benchmarks which include parasitic database read-in time. Each delay stage requires a lumped RC network annotation

| NUMBER OF CRITICAL PATHS | NUMBER OF DELAY<br>STAGES | CPU TIME<br>(MINUTES) |

|--------------------------|---------------------------|-----------------------|

| 5                        | 74                        | 02:25                 |

| 10                       | 130                       | 03:39                 |

| 25                       | 273                       | 06:32                 |

| 50                       | 649                       | 12:38                 |

varied for different design constraints. The relative error describes the percentage improvement in accuracy that one can achieve when using a more accurate interconnect impedance model. A  $\pi$  network is used instead of a T network since it utilises fewer nodes and is therefore more computationally efficient since the computational efficiency of SPICE is directly dependent upon the size of its nodal matrix. For values of  $R_T$  and  $C_T$  greater than 5, relative errors between L, R, C, and N networks less than 10% dictate the selection of a simple R, C, or N network model. For large values of  $R_T$ , the interconnect resistance is of negligible consequence and the interconnect model can be represented as a simple capacitor. For large values of  $C_T$ , the interconnect model can be represented as a simple resistor. For large values of both  $R_T$  and  $C_T$ , no RC interconnect impedance model is necessary and this is symbolically represented as an N network model. Thus, the user defined factor combined with the two technology dependent look-up tables, Tables 2 and 3, define an appropriate RC network for modelling a wire's distributed interconnect impedance which accurately represents the distributed RC load for specific  $R_T$  and  $C_T$  ratios.

### 4. Illustration of results

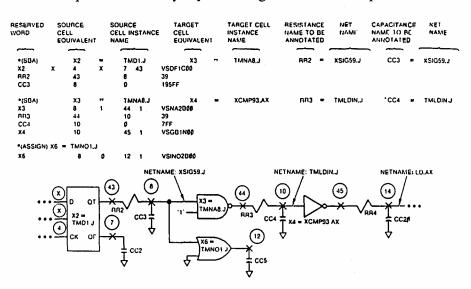

This system has been used to interface to two automated layout databases, an in-house developed system, HAL (Hughes Automated Layout) and a commercially developed system, SDA (Silicon Design Automation). The input to Crystal-H is a netlist in TDL (TEGAS Design Language) format. The outputs are SPICE files formatted by SBA where each file contains a critical path identified by Crystal-H. Fig. 5 shows an example of an SBA format-

Fig. 5 An SBA formatted SPICE file and its schematic circuit diagram

ted SPICE file and its corresponding schematic circuit. These-files also contain cross reference tables to associate the SPICE nodal numbers with their TDL netlist. Each file contains an ordered printout of the critical path instance names and cell types along with all of the branches of the paths to assist the designer during circuit analysis. Crystal-H also performs instance name assignments to assure correct syntax of the generated SPICE files.

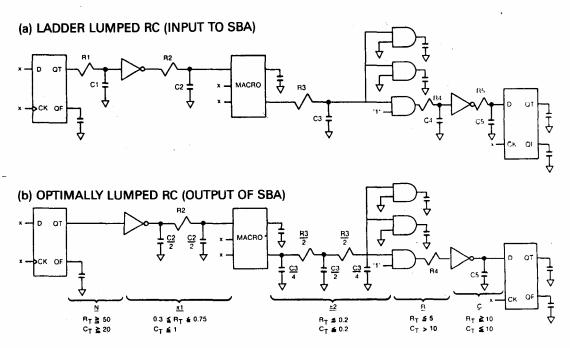

SBA accepts automatically generated SPICE files, identifies a path's source-target-net instance names, invokes the parasitic extractor, accesses the two look-up tables, selects the optimal distributed impedance network, and performs back annotation into the predefined SPICE files. Fig. 6 shows a schematic of a typical circuit with  $\pi 2$ ,  $\pi 1$ , L, R, N, and C lumped interconnect networks chosen in a locally optimal fashion. In Fig. 6(a), dummy RC variables are placed on each cell-to-cell node and are consequently redefined by SBA as shown in Fig. 6(b). The nodes marked 'x' are defined by the circuit designer based on the path's specific functionality. Table 3 depicts SBA benchmarks run on a VAX 11/750.

Fig. 6 Typical circuit input to SBA: (a) Input to SBA, (b) Output of SBA

### 5. Conclusions

A tool for accurately and automatically analysing critical worst case paths in large VLSI circuits has been described. Accurate post-layout resistive and capacitive interconnect impedances are automatically extracted, modeled in a technology dependent optimal fashion, and back annotated into a SPICE formatted circuit simulation file for the precise determination of the timing behaviour of each critical path. An algorithm for 1) determining a device's output impedance from a technology circuit environment and 2) choosing an optimal RC network which accurately models a wire's interconnect impedance based on technology specific look-up tables has been described. These algorithms have been integrated with existing in-house and commercial CAD tools and merges the accuracy required to design high performance VLSI circuits with the automation necessary in today's competitive digital marketplace.

## 6. Acknowledgements

The authors would like to acknowledge Mr. Takayasu Sakurai for the creative spark which triggered this work<sup>7</sup> and to thank Dr. W.R. Smith for his valuable comments.

### 7. References

- [1] Hitchcock, R.B. Sr., "Timing verification and timing analysis program," Proceedings of ACM IEEE 19th Design Automation Conference, pp. 594-604, 1982.

- [2] Jouppi, N.P., "Timing analysis for nMOS VLSI," Proceedings of ACM IEEE 20th Design Automation Conference, pp. 411-418, June 1983.

- [3] Muraoka, M. et al., "ACTAS: an accurate timing analysis system for VLSI," Proceedings of ACM IEEE 22nd Design Automation Conference, pp. 152-158, 1985.

- [4] Rubinstein, J., Penfield, P. Jr. and Horowitz, M.A., "Signal delay in RC tree networks," IEEE Transactions on Computer-Aided Design, Vol. CAD-2, No. 3, pp. 202-211, July 1983.

- [5] Powell, S., Smith, W.R. and Persky, G., "A parasitic extraction program for closely-spaced VLSI interconnects," Proceedings of International Conference on Computer-Aided Design, pp. 193-195, 1985.

- [6] Yuan, C.P. and Trick, T.N., "Extraction of interconnect parameters in VLSI circuits," Proceedings of international conference on computer-aided design, pp. 1229-1232, 1983.

- [7] Sakurai, T., "Approximation of wiring delay in MOSFET LSI," IEEE Journal of Solid State Circuits, Vol. SC-18, No. 4, pp. 418-426, August 1983.

- State Circuits, Vol. SC-18, No. 4, pp. 418-426, August 1983.

Wei, Y-P., Lyons, C. and Hailey, S., "Timing analysis of MOS VLSI circuits," VLSI Systems Design, pp. 52-58, August 1987.

- [9] Friedman, E.G., Yacoub, G.Y. and Powell, S., "A CMOS/SOS VLSI design system," Journal of Semicustom ICs, Vol. 2, No. 4, pp. 5-11, June 1985.

- [10] Pollack, S., Erickson, B. and Mazor, S., "Silicon compilers ease complex VLSI design," Computer Design, pp. 79-82, September 15, 1986.

- [11] Friedman, E.G. et al., "A signal tracking chip utilising a VHSIC CMOS/SOS structured custom design methodology," Government Microcircuit Applications Conference Digest of Papers, pp. 217-222, 1986.

- [12] Jespers, P.G., Sequin, C.H. and Van de Wiele, F., Design Methodologies for VLSI Circuits. Maryland: Siithoff Et Noordhoff, pp. 357-373, 1982.

- cuits, Maryland: Sijthoff Et Noordhoff, pp. 357-373, 1982.

[13] Ousterhout, J.K., "A switch-level timing verifier for digital MOS VLSI," IEEE Transactions on Computer Aided Design, Vol. CAD-4, No. 3, pp. 336-349, July 1985.

- [14] Yacoub, G.Y. and Friedman, E.G., "An environment sensitive circuit design technique for modelling VLSI interconnect impedances," Government Mirocircuits Application Conference Digest of Papers, October 1987.

- [15] Weste, N. and Eshraghian, K., *Principles of CMOS VLSI Design*, Reading: Addison-Wesley, pp. 46-49, 1985.

- [16] Annaratone, M., Digital CMOS Circuit Design, Boston: Kluwar, pp. 149-151, 1986.

- [17] Antinone, R.J. and Brown, G.W., "The modelling of resistive interconnects for integrated circuits," IEEE Journal of Solid State Circuits, Vol. SC-18, No. 2, pp. 200-203, April 1983.