US010552756B2

## (12) United States Patent Ipek et al.

## (54) SUPERCONDUCTING SYSTEM ARCHITECTURE FOR HIGH-PERFORMANCE ENERGY-EFFICIENT CRYOGENIC COMPUTING

(71) Applicants: Engin Ipek, Rochester, NY (US); Ben Feinberg, Rochester, NY (US); Shibo Wang, Rochester, NY (US); Mahdi N. Bojnordi, Rochester, NY (US); Ravi Patel, Victor, NY (US); Eby G. Friedman, Rochester, NY (US)

(72) Inventors: Engin Ipek, Rochester, NY (US); Ben Feinberg, Rochester, NY (US); Shibo Wang, Rochester, NY (US); Mahdi N. Bojnordi, Rochester, NY (US); Ravi Patel, Victor, NY (US); Eby G. Friedman, Rochester, NY (US)

(73) Assignee: **University of Rochester**, Rochester, NY (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/774,503

(22) PCT Filed: **Nov. 10, 2016**

(86) PCT No.: **PCT/US2016/061292**

§ 371 (c)(1),

(2) Date: **May 8, 2018**

(87) PCT Pub. No.: WO2018/009240PCT Pub. Date: Jan. 11, 2018

#### (65) Prior Publication Data

US 2019/0188596 A1 Jun. 20, 2019

#### Related U.S. Application Data

(60) Provisional application No. 62/254,546, filed on Nov. 12, 2015.

#### (10) Patent No.: US 10,552,756 B2

(45) Date of Patent:

Feb. 4, 2020

(51) Int. Cl.

G06N 10/00 (2019.01)

G06F 7/38 (2006.01)

(Continued)

(58) Field of Classification Search CPC ...... G06N 10/00; H03K 19/195; G11C 19/32; G11C 11/44; G11C 11/1675;

(Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

#### OTHER PUBLICATIONS

Van Duzer, Theodore, et al., "64-kb Hybrid Josephson-CMOS 4 Kelvin RAM with 400 ps Access Time and 12 mW Read Power," 2013, IEEE Transactions on Applied Superconductivity, vol. 23, No. 3, (4 pgs.).

(Continued)

Primary Examiner — Don P Le (74) Attorney, Agent, or Firm — Harris Beach PLLC

#### (57) ABSTRACT

An energy efficient rapid single flux quantum (ERSFQ) logic register wheel includes a circular shift register having a plurality of destructive read out (DRO) cells. Each entry of the circular shift register includes a data block, a tag, and a valid bit. A compare and control logic is coupled to the circular shift register to compare a source specifier or a destination register specifier against a register tag stored in the wheel following each cycle of the register wheel. At least one or more read ports and at least one or more write ports (Continued)

are coupled to the circular shift register to write to or to read from a different entry each in the register wheel following each cycle of the register wheel. A RSFQ clearable FIFO with flushing and a crosspoint memory topology for integrating MRAM devices with ERSFQ circuits are also described.

#### 12 Claims, 25 Drawing Sheets

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

|      | H01L 39/22  | (2006.01) |

|      | G06F 9/30   | (2018.01) |

|      | G11C 11/16  | (2006.01) |

|      | G11C 11/44  | (2006.01) |

|      | G11C 19/32  | (2006.01) |

|      | H03K 19/195 | (2006.01) |

|      | H01L 27/18  | (2006.01) |

|      | H01L 27/22  | (2006.01) |

|      | H01L 43/02  | (2006.01) |

|      |             |           |

#### (52) U.S. Cl.

CPC ...... *G06F 9/3016* (2013.01); *G06F 9/30105* (2013.01); G11C 11/161 (2013.01); G11C 11/1673 (2013.01); G11C 11/1675 (2013.01); G11C 11/44 (2013.01); G11C 19/32 (2013.01); H01L 39/223 (2013.01); H03K 19/195 (2013.01); H01L 27/18 (2013.01); H01L 27/222 (2013.01); H01L 43/02 (2013.01)

#### (58) Field of Classification Search

CPC . G11C 11/1673; G11C 11/161; G06F 9/3016; G06F 9/30105; G06F 9/3004; G06F 7/381; G06F 1/16; H01L 39/223; H01L 43/02; H01L 27/222; H01L 27/18

See application file for complete search history.

(56)

#### References Cited

| 2009/0322374 | A1*           | 12/2009 | Przybysz G06N 10/00 |

|--------------|---------------|---------|---------------------|

|              |               |         | 326/5               |

| 2012/0184445 | $\mathbf{A}1$ | 7/2012  | Mukhanov et al.     |

| 2015/0146805 | A1*           | 5/2015  | Terry H04L 25/0204  |

375/260

U.S. PATENT DOCUMENTS

#### OTHER PUBLICATIONS

Vernik, Igor V., et al., "Magnetic Josephson Junctions with Superconducting Interlayer for Cryogenic Memory," 2013, IEEE Transactions on Applied Superconductivity, vol. 23, No. 3. (8 pgs.). Wilton, Steven J.E., et al., "CACTI: An Enhanced Cache Access and Cycle Time Model," 1996, IEEE Journal of Solid-State Circuits, vol. 31, No. 5, (pp. 677-688).

Woo, Steven Cameron, et al., "The SPLASH-2 Programs: Characterization and Methodological Considerations," 1995, In Computer Architecture 1995. Proceedings., 22nd Annual International Symposium (pp. 24-36).

Yamada, Tatsuji, et al., "Quantitative Evaluation of the Single-Flux-Quantum Cross/Bar Switch," 2005 IEEE Transactions on Applied Superconductivity, vol. 15, No. 2, (4 pgs.).

Yamanashi, Y., et al., "Design and Implementation of a Pipelined Bit-Serial SFQ Microprocessor, CORE1 β," 2007, IEEE Transactions on Applied Superconductivity, vol. 17, No. 2., (pp. 474-477). Yoo, Richard M., et al., "Phoenix Rebirth: Scalable MapReduce on a Large-Scale Shared-Memory System," 2009, In Workload Characterization 2009. IISWC 2009. IEEE International Symposium (pp. 198-207).

Yorozu, S., et al., "Progress of Single Flux Quantum Packet Switch Technology," 2005, IEEE Transactions on Applied Superconductivity, vol. 15, No. 2, (pp. 411-414). Yorozu, Shinichi, et al., "A Single Flux Quantum (SFQ) Packet

Switch Unit towards Scalable Non-blocking Router," 2002, IEICE Transactions on Electronics, vol. E85-C, No. 3, (pp. 617-620).

Yorozu, S., et al., "A 40GHz clock 160Gb/s 4x4 switch circuit using single flux quantum technology for high-speed packet switching systems," 2004, In High Performance Switching and Routing, 2004. HPSR. 2004 Workshop (pp. 20-23).

Yorozu, S., et al., "Single Flux quantum circuit technology innovation for backbone router applications," 2003, Physica C: Superconductivity, (pp. 392-396, Part 2(0): 1478-1484). Zhao, Wei, et al., "New Generation of Predictive Technology Model

for Sub-45nm Design Exploration," 2006, IEEE Transactions on Electron Devices, vol. 53, No. 11, (6 pages).

Zimmerman, J.E., "Space applications of superconductivity: low frequency superconducting sensors," 1980, Cryogenics, vol. 20, No. 1, (pp. 3-10).

Zinoviev, Dmitry Y., et al., "Feasibility Study of RSFQ-based Self-Routing Nonblocking Digital Switches," 1997, IEEE Transactions on Applied Superconductivity, vol. 7, No. 2., (pp. 3155-3163). Zotev, Vadim S., et al., "Multi-Channel SQUID System for MEG and Ultra-Low-Field MRI," 2007, IEEE Transactions on Applied Superconductivity, vol. 17, No. 2, (pp. 839-842).

Zotev, Vadim S., et al., "SQUID-based instrumentation for ultralowfield MRI," 2007, Superconductor Science and Technology, vol. 20, No. 11, (pp. S367-S373).

Zotev, Vadim S., et al., "Microtesla MRI of the human brain combined with MEG," 2008, Journal of Magnetic Resonance, vol. 194, No. 1, (14 pgs.).

Gaj, Kris, et al., "Tools for the Computer-Aided Design of Multigigahertz Superconducting Digital Circuits," 1999, IEEE Transactions on Applied Superconductivity, vol. 9, No. 1, (pp. 18-38).

Gaj, Krzysztof, et al., "A Clock Distribution Scheme for Large RSFQ Circuits," 1995, IEEE Transactions on Applied Superconductivity, vol. 5, No. 2., (pp. 3320-3324).

Silver, Arnold H., "Superconductor Technology for High-End Computing System Issues and Technology Roadmap," 2005, Proceedings of the ACM/IEEE SC/05 Conference, (4 pages).

Engel, B.N., et al., "A 4-Mb Toggle MRAM Based on a Novel Bit and Switching Method," 2005, IEEE Transactions on Magnetics, vol. 41, No. 1, (pp. 132-136).

Hosomi, M., et al., "A Novel Nonvolatile Memory with Spin Torque Transfer Magnetization Switching: Spin-RAM," 2005, IEDM Technical Digest, (4 pages).

Kishi, T., et al., "Lower-current and Fast switching of A Perpendicular TMR for High Speed and High density Spin-Transfer-Torque MRAM," 2008, Proceedings of the IEEE International Electron Devices Meeting, (4 pages). Kawahara, Takayuki, et al., "2 Mb SPRAM (SPin-Transfer Torque

RAM) With Bit-by-Bit Bi-Directional Current Write and Parallelizing-Direction Current Read," 2008, IEEE Journal of Solid-State Circuits, vol. 43, No. 1, (pp. 109-120). Liang, Jiale, et al., "Effect of Wordline/Bitline Scaling on the

Performance, Energy Consumption, and Reliability of Cross-Point Memory Array," 2013, ACM Journal on Emerging Technologies in Computing Systems, vol. 9, No. 1, Article 9, (14 pages)

Ayala, Christopher Lawrence, "Energy-Efficient Wide Datapath Integer Arithmetic Logic Units Using Superconductor Logic," 2012, PhD Thesis, Stony Brook University (173 pgs.).

Bailey, D.H., et al., "The NAS Parallel Benchmarks-Summary and Preliminary Results," 1991, Supercomputing '91. Proceedings of the 1991 ACM/IEEE Conference (pp. 158-165).

Bakolo, Rodwell S., "Design and Implementation of RSFQ Superconductive Digital Electronics Cell Library," 2011, PhD Thesis, University of Stellenbosch (150 pgs).

Bienia, Christian, et al., "The PARSEC Benchmark Suite: Characterization and Architectural Implications," 2008, In Proceedings of the 17th International Conference on Parallel Architectures and Compilation Techniques (8 pgs.).

Brock, Darren K., et al., "Superconductor ICs: the 100-GHz second generation," 2000, IEEE Spectrum (12 pgs.).

#### (56) References Cited

#### OTHER PUBLICATIONS

Bronk, Christopher, et al., "Innovation for Sustainability in Information and Communication Technologies (ICT)," 2010, James A. Baker III Inst. Public Policy, Rice Univ., Houston, TX (7 pgs.). Bunyk, Paul, et al., "FLUX-1 RSFQ Microprocessor: Physical Design and Test Results," 2003, IEEE Transactions on Applied Superconductivity, vol. 13, No. 2 (pp. 433-436).

Caufield, H. John, et al., "Why future supercomputing requires optics," 2010, Nature Photonics, vol. 4 (pp. 261-263).

Chen, W., et al., "Rapid Single Flux Quantum T-Flip Flop Operating up to 770 GHz," 1999, IEEE Transactions on Applied Superconductivity, vol. 9 (pp. 3212-3215).

Dagum, Leonardo, et al., "OpenMP: An Industry-Standard API for Shared-Memory Programming," 1998, IEEE Computational Science & Engineering (pp. 46-55).

Dorojevets, Mikhail, et al., "Data-Flow Microarchitecture for Wide Datapath RSFQ Processors: Design Study," 2011, IEEE Transactions on Applied Superconductivity, vol. 21, No. 3 (pp. 787-791). Dorojevets, Mikhail, et al., "8-Bit Asynchronous Sparse-Tree Superconductor RSFQ Arithmetic-Logic Unit With a Rich Set of Operations," 2013, IEEE Transactions on Applied Superconductivity, vol. 23, No. 3 (4 pgs.).

Dorojevets, Mikhail, et al., "COOL-0: Design of an RSFQ Subsystem for Petaflops Computing," 1999, IEEE Transactions on Applied Superconductivity, vol. 9, No. 2 (pp. 3606-3614).

Dorojevets, Mikhail, et al., "Architectural and Implementation Challenges in Designing High-Performance RSFQ Processors: A FLUX-1 Microprocessor and Beyond," 2003, IEEE Transactions on Applied Superconductivity, vol. 13, No. 2 (pp. 446-449).

Dorojevets, Mikhail, et al., "20-GHz 8x8 Parallel Carry-Save Pipelined RSFQ Multiplier," 2013, IEEE Transactions on Applied Superconductivity, vol. 23, No. 3 (4 pgs).

Dorojevets, M., "A 20-GHz FLUX-1 superconductor RSFQ microprocessor," 2002, J. Phys. IV France, vol. 12 (pp. 157-160).

Dubash, Noshir B., et al., "SFQ Data Communication Switch," 1997, IEEE Transactions on Applied Superconductivity, vol. 7, No. 2 (pp. 2681-2684).

Espy, M.A., et al., "Ultra-low-field MRI for the detection of liquid explosives," 2010, Superconductor Science and Technology, vol. 23 (10 pgs.).

Hamilton, Clark A., "Josephson voltage standards," 2000, Review of Scientific Instruments, vol. 71 (pp. 3611-3623).

Haverkamp, Imke, et al., "Linearity of a Digital SQUID Magnetometer," 2011, IEEE Transactions on Applied Superconductivity, vol. 21, No. 3 (pp. 705-708).

Herr, Quentin P., et al., "Implementation and Application of First-In First-Out Buffers," 2003, IEEE Transactions on Applied Superconductivity, vol. 13., No. 2 (pp. 563-566).

Kameda, Yoshio, et al., "Design and Demonstration of a 4×4 SFQ Network Switch Prototype System and 10-Gbps Bit-Error-Rate Measurement," 2008, IEICE Trans. Electron., vol. E91-C, No. 3 (pp. 333-341).

Lawrence, R.D., et al., "A Scalable Parallel Algorithm for Self-Organizing Maps with Applications to Sparse Data Mining Problems," 1999, Data Mining and Knowledge Discovery, vol. 3 (pp. 171-195).

Lenz, James, et al., "Magnetic Sensors and Their Applications," 2006, IEEE Sensors Journal, vol. 6, No. 3 (pp. 631-649).

Likharev, K.K, et al., "RSFQ Logic/Memory Family: A New Josephson-Junction Technology for Sub-Terahertz-Clock-Frequency Digital Systems," 1991, IEEE Transactions on Applied Superconductivity, vol. 1, No. 1 (pp. 3-28).

Lin, J.C., et al., "Design of SFQ-Counting Analog-to-Digital Converter," 1995, IEEE Transactions on Applied Superconductivity, vol. 5, No. 2 (pp. 2252-2259).

Liu, Qingguo, "Josephson-CMOS hybrid memories," 2007, PhD Thesis, University of California, Berkeley (198 pgs.).

Li, Sheng, et al., "McPAT: An Integrated Power, Area, and Timing Modeling Framework for Multicore and Manycore Architectures," 2009, In Microarchitecture, MICRO-42, 42nd Annual IEEE/ACM International Symposium (pp. 469-480).

Matula, R.A., Electrical Resistivity of Copper, Gold, Palladium, and Silver, 1979, J. Phys. Chem. Ref. Data, vol. 8, No. 4 (pp. 1147-1298).

McCambridge, James D., et al., "Multilayer HTS SFQ Analog-to-Digital Converters," 1997, IEEE Transactions on Applied Superconductivity, vol. 7, No. 2 (pp. 3622-3625).

Moody, M.V., et al., "Superconducting gravity gradiometer for space and terrestrial applications," 1986, Journal of Applied Physics, vol. 60, No. 12, (pp. 4308-4315).

MOSIS, "MOSIS Packaging and Assembly: Packaging Options," 2013, http://www.mosis.com/pages/products/assembly/index. (7 pgs.).

Mukhanov, Oleg A., et al., "Superconductor Analog-to-Digital Converters," 2004, Proceedings of the IEEE, vol. 92, No. 10, (pp. 1564-1584).

Mukhanov, Oleg A., "Energy-Efficient Single Flux Quantum Technology", 2011, IEEE Transactions on Applied Superconductivity, vol. 21, No. 3, (pp. 760-769).

Muralimanohar, Naveen, et al., "CACTI 6.0: A Tool to Model Large Caches," 2009, HP Laboratories (25 pgs.).

Nakagawa, Takahiro, et. al., "Large-Scale SFQ Switches Using Miniaturized 2×2 Switch Cell", 2008, IEEE Transactions on Applied Superconductivity, vol. 18, No. 4., (pp. 1790-1796).

Nisenoff, M., "Space Applications of Superconductivity," 1992, Principles and applications of superconducting quantum interference devices, (69 pgs.).

Numata, H., et al., "A Vortex Transitional Memory Cell for 1-Mbit/cm2 Density Josephson RAMs," 1997, IEEE Transactions on Applied Superconductivity, vol. 7, No. 2., (pp. 2282-2287).

Ortlepp, T., et al., "Design guidelines for Suzuki stacks as reliable high-speed Josephson voltage drivers," 2013, Superconductor Science and Technology, vol. 26 (13 pgs.).

Polonsky, S.V., "New SFQ/DC converter for RSFQ logic/memory family," 1991, Superconductor Science and Technology, vol. 4 (pp. 442-444).

Reich, Torsten., et al., "Digital SQUID Sensor Based on SFQ Technique," 2005, IEEE Transactions on Applied Superconductivity, vol. 15, No. 2, (pp. 304-307).

Renau, Jose, et al., "SESC: cycle accurate architectural simulator," 2005, http://sesc.sourceforge.net.

Rupp, Karl, et al., "The Economic Limit to Moore's Law," 2010, Proceedings of the IEEE, vol. 98, No. 3, (pp. 351-353).

Ryazanov' Valery V., et al., "Magnetic Josephson junction technology for digital and memory applications," 2012, Physics Procedia, vol. 36, (pp. 35-41).

Sasaki, H., et al., "RSFQ-Based D/A Converter for AC Voltage Standard," 1999, IEEE Transactions on Applied Superconductivity, vol. 9, No. 2, (pp. 3561-3564).

Semenov, V.K., et al., "DC Voltage Multipliers: A Novel Application of Synchronization in Josephson Junction Arrays," 1989, IEEE Transactions on Magnetics, vol. 25, No. 2, (pp. 1432-1435).

Snyder, Wilson, et al., "Introduction to Verilator," Verilator Wiki. http://www.veripool.org/wiki/verilator.

Suzuki, M., et al., "An Interface Circuit for a Josephson-CMOS Hybrid Digital System," 1999, IEEE Transactions on Applied Superconductivity, vol. 9, No. 2, (pp. 3314-3317).

Thompson, Scott E., "Power, Cost and Circuit IP Reuse: The Real Limiter to Moore's Law Over the Next 10 Years," 2010, VLSI Technology Systems and Applications, (pp. 88-89).

Tsuga, Yuto., et al., "Asynchronous Digital SQUID Magnetometer With an On-Chip Magnetic Feedback for Improvement of Magnetic Resolution," 2013, IEEE Transactions on Applied Superconductivity, vol. 23, No. 3, (5 pgs.).

#### \* cited by examiner

FIG. 2

FIG. 5

Feb. 4, 2020

Read signal NDRO J Flush signal Flush bit FIFO DRO **Output** data Data FIFO

FIG. 6A

FIG. 6B

FIG. 7

FIG. 8

FIG. 9

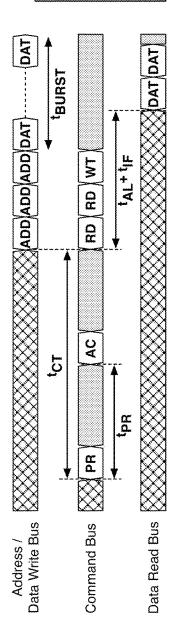

t<sub>CT</sub>: cycle time for accessing a new block t<sub>PR</sub>: bit-line precharge latency t<sub>AL</sub>: bank access latency (roundtrip) t<sub>IF</sub>: SFQ and CMOS interfacing latency ADD: address DAT: data RD: read WT: write PR: precharge AC: activate

FIG. 10

| Processor Parameters            |                          |  |

|---------------------------------|--------------------------|--|

| Fequency                        | 20 GHz (80 GHz wheels)   |  |

| Number of cores                 | 1                        |  |

| Number of SMT contexts          | 16 per core              |  |

| Pipeline organization           | Single-issue, in-order   |  |

| L1 Caches                       |                          |  |

| IL1/DL1 size                    | 32KB/32KB                |  |

| IL1/DL1 block size              | 32B/32B                  |  |

| IL1/DL1 round-trip latency      | 1/1 cycles (uncontended) |  |

| IL1/DL1 associativity           | 4/4                      |  |

| Shared L2 Cache and Main Memory |                          |  |

| Shared L2 Cache                 | 4MB, 64B block, 16-way   |  |

| L2 round-trip latency           | 8 cycles (uncontended)   |  |

| DRAM subsystem                  | Section 5.3              |  |

| Memory controllers              | 1                        |  |

FIG. 11

**Table 1: Parameters of the proposed architecture.**

| Processor Parameters            |                          |  |

|---------------------------------|--------------------------|--|

| Fequency                        | 4 GHz                    |  |

| Number of cores                 | 8                        |  |

| Number of SMT contexts          | 8 per core               |  |

| Pipeline organization           | Single-issue, in-order   |  |

| L1 Caches                       |                          |  |

| IL1/DL1 size                    | 32KB/32KB                |  |

| IL1/DL1 block size              | 32B/32B                  |  |

| IL1/DL1 round-trip latency      | 2/2 cycles (uncontended) |  |

| IL1/DL1 associativity           | 4/4                      |  |

| Coherence protocol              | MESI                     |  |

| Shared L2 Cache and Main Memory |                          |  |

| Shared L2 Cache                 | 4MB, 64B block, 16-way   |  |

| L2 round-trip latency           | 10 cycles (uncontended)  |  |

| DRAM subsystem                  | DDR3-1600 SDRAM [57]     |  |

| Memory controllers              | 4                        |  |

FIG. 12

Table 2: Parameters of baseline.

US 10,552,756 B2

| Benchmark         | Problem size                     |  |  |  |

|-------------------|----------------------------------|--|--|--|

| Data Mining       |                                  |  |  |  |

| Bsom              | 2,048 rec., 100 epochs           |  |  |  |

| Phoenix           |                                  |  |  |  |

| Linear regression | 50MB points                      |  |  |  |

| Histogram         | 34,843,392 pixels (104MB)        |  |  |  |

| SPLASH-2          |                                  |  |  |  |

| Barnes            | 16K Particles                    |  |  |  |

| FFT               | 1M points                        |  |  |  |

| FMM               | 16K particles                    |  |  |  |

| LU                | 512×512 matrix, 16×16 blocks     |  |  |  |

| Ocean             | 514×514 ocean                    |  |  |  |

| Radix             | 2M integers                      |  |  |  |

| Water-NSquared    | 512 molecules                    |  |  |  |

| SPEC OpenMP       |                                  |  |  |  |

| Equake-Omp        | MinneSpec-Large                  |  |  |  |

| NAS OpenMP        |                                  |  |  |  |

| MG                | Class A                          |  |  |  |

| PARSEC            |                                  |  |  |  |

| Blackscholes      | 4,096 options                    |  |  |  |

| Swaptions         | 64 swaptions, 10,000 simulations |  |  |  |

Table 3: Simulated applications and data sets.

FIG. 21

FIG. 22

FIG. 25

FIG. 26

FIG. 29A

Write Line

FIG. 29B

# SUPERCONDUCTING SYSTEM ARCHITECTURE FOR HIGH-PERFORMANCE ENERGY-EFFICIENT CRYOGENIC COMPUTING

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a national stage application under 35 U.S.C. § 371 of PCT Application No. PCT/US16/61292, filed Nov. 10, 2016, SUPERCONDUCTING SYSTEM ARCHITECTURE FOR HIGH-PERFORMANCE ENERGY-EFFICIENT CRYOGENIC COMPUTING, and published as WO/2018/009240, which claims priority to and the benefit of U.S. provisional patent application Ser. No. 62/254,546, SUPERCONDUCTING SYSTEM ARCHITECTURE FOR HIGH-PERFORMANCE ENERGY-EFFICIENT CRYOGENIC COMPUTING, filed Nov. 12, 2015, which applications are incorporated herein by reference in their entirety.

### STATEMENT REGARDING FEDERALLY FUNDED RESEARCH OR DEVELOPMENT

This invention was made with Government Support under <sup>25</sup> Contract Nos. CCF1054179 and CCF1329374 awarded by the National Science Foundation. The Government has certain rights in the invention.

#### FIELD OF THE APPLICATION

The application relates to superconducting systems architecture for high-performance energy-efficient cryogenic computing, and particularly to rapid single flux quantum (RSFQ) and energy efficient rapid single flux quantum <sup>35</sup> (ERSFQ) based components thereof.

#### BACKGROUND

In the background, other than the bolded paragraph numbers, non-bolded square brackets ("[]") refer to the citations listed hereinbelow.

Data centers and high performance computing have relied on Moore's law scaling to achieve petaflop scale compute capability within feasible power budgets. However, semiconductor scaling, abated by increasingly stringent power constraints, growing manufacturing variability, and ultimately restricted by fundamental physical limits, is predicted to end soon [8, 48, 54]. Moreover, modern data center power consumption is predicted to increase by a factor of 50 three to 661 TWh within the same time frame [6].

Niobium (Nb) based superconductor electronics, an existing and mature technology, enables fundamentally different tradeoffs in performance and power. Conventional superconductor electronics, however, have been limited to small 55 applications such as high frequency analog to digital conversion [28, 33, 37], low latency network switches [17, 23, 60, 63, 64], and embedded space applications [35, 42, 68]. Small scale digital electronics have been demonstrated, but with limited applicability to general computer applications.

#### **SUMMARY**

According to one aspect, an energy efficient rapid single flux quantum (ERSFQ) logic register wheel includes a 65 circular shift register having a plurality of destructive read out (DRO) cells. Each entry of the circular shift register

2

includes a data block, a tag, and a valid bit which advance by one entry every cycle of the register wheel. A compare and control logic is coupled to the circular shift register to compare a source specifier or a destination register specifier against a register tag stored in the wheel following each cycle of the register wheel. At least one or more read ports and at least one or more write ports are coupled to the circular shift register to write to or to read from a different entry each in the register wheel following each cycle of the register wheel. The logic wheel includes a Josephson junction (JJ) based ERSFQ logic disposed in a cryostat which maintains cryogenic temperatures.

In one embodiment, the ERSFQ logic wheel progresses through the circular register at a frequency of more than twice a core clock frequency of an associated processor to reduce average access latency.

In another embodiment, the ERSFQ logic register wheel further includes at least one or more additional read port 20 including a single JJ junction.

In yet another embodiment, the ERSFQ logic register wheel further includes at least one or more additional write port including three JJ junctions.

In yet another embodiment, the ERSFQ logic register wheel implements a random access memory (RAM) or a content addressed memory (CAM).

In yet another embodiment, the ERSFQ logic register wheel implements a ERSFQ logic store wheel wherein each entry of the circular shift register further includes an additional bit flag and the ERSFQ logic register wheel further includes at least one or more search ports.

In yet another embodiment, the ERSFQ logic store wheel implements an ERSFQ logic miss store holding register (MSHR) wheel.

In yet another embodiment, the MSHR wheel includes a CAM wheel with an address field for comparison and two fields for secondary misses.

In yet another embodiment, at least one or more of the ERSFQ logic register wheels provide a register file access component of a processor which is coupled to a decode component by asynchronous FIFOs and where the register file access component provides instructions to an execution component via asynchronous FIFOs such that each of the decode component, the register file access component, and the execution component can run at different clock rates.

In yet another embodiment, the ERSFQ logic register wheel further includes a multiported store queue as a write buffer

In yet another embodiment, at least one or more ERSFQ logic register wheels provide a load queue to support recovery from branch mispredictions.

In yet another embodiment, a first load wheel holds load instructions that have not yet been issued to a memory or searched by a store wheel and a second wheel holds loads after they are issued to a memory subsystem until they are committed.

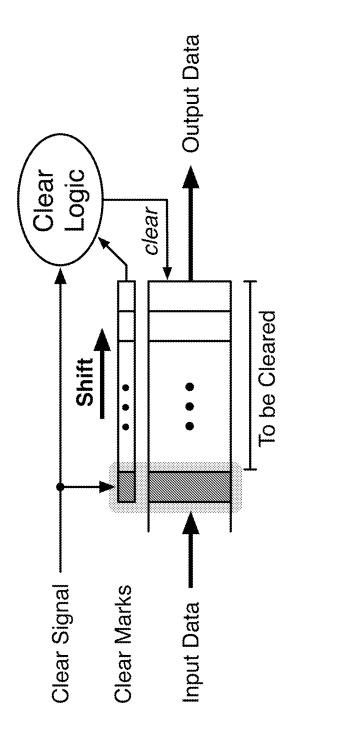

According to another aspect, a rapid single flux quantum (RSFQ) clearable FIFO with flushing includes a data FIFO including a plurality of data entries. A flush bit FIFO includes a flush bit corresponding to each data entry. A flush signal input terminal is coupled to a nondestructive read out (NDRO) register. A Muller C-gate is coupled to and enabled by an inverted output of the NDRO register, and a FIFO output data terminal. When the FIFO receives a flush signal, the NDRO register is set to 1, and a 1 is inserted at a tail of the FIFO, and as an invalid data progresses through the FIFO, the data is set to zero at the FIFO output data terminal,

and when the flush bit reaches a head of the FIFO, a stored 1 resets the NDRO register causing the RSFQ FIFO to return to a normal operation.

In one embodiment, at least one or more of the RSFQ clearable FIFOs connect pipelined stages of a processor core 5 operating at different clock rates.

In another embodiment, the pipelined stages are selected from the group consisting of fetch, decode, register read, execute, memory, and write back.

In yet another embodiment, the core includes a globally 10 asynchronous locally synchronous (GALS) operation having clock distribution and synchronization to provide locally controlling clock signals and to optimize delays across branching logic paths.

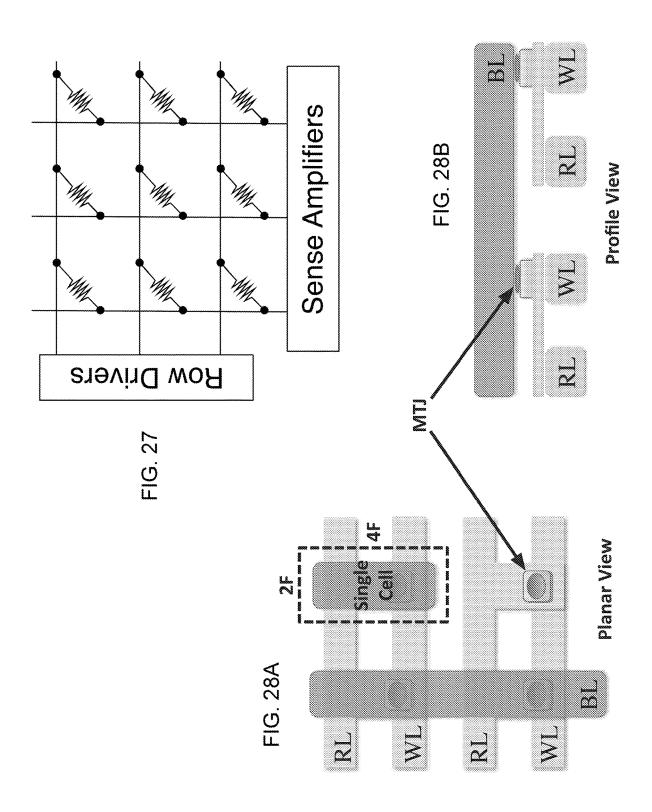

According to yet another aspect, a crosspoint memory 15 topology for integrating MRAM devices with ERSFQ circuits includes an array of magnetic tunnel junction (MTJ) devices disposed in a crosspoint array structure, each row oriented in an opposite direction to cancel off-state currents. A row write line is disposed on a first side of each MTJ 20 device. A column line write is disposed on a second side of each MTJ device. A column read line is disposed adjacent to the row write line. To read a device state, a pulse is applied to the device while the rest of the array is biased low. To write the device state, a current will pass through both of the 25 off-chip cache and main memory as an exemplary embodirow line and the column line to switch the device.

In one embodiment, the MTJ devices are configured as T Flip-Flop Josephson junction (JJ) circuits.

In another embodiment, a forward circulating current adjusts an effective magnitude of the current passing through 30 the line and individual MTJ devices are selected within the array by a ratio of high and low circulating currents.

In yet another embodiment, during a read, the pulse is applied by a SFQ-to-DC converter.

The foregoing and other aspects, features, and advantages 35 of the application will become more apparent from the following description and from the claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The features of the application can be better understood with reference to the drawings described below, and the claims. The drawings are not necessarily to scale, emphasis instead generally being placed upon illustrating the principles described herein. In the drawings, like numerals are 45 used to indicate like parts throughout the various views.

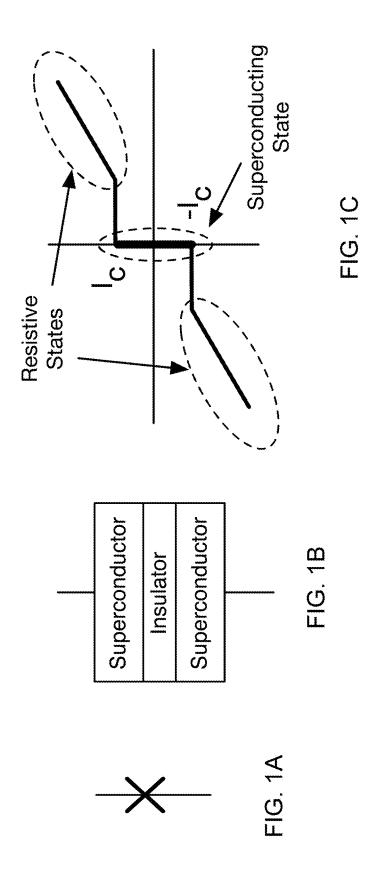

- FIG. 1A shows a drawing of the circuit symbol for a Josephson junction (JJ);

- FIG. 1B is a drawing that shows how a JJ is formed from a superconductor-insulator-superconductor (SIS) trilayer 50 called the SIS junction;

- FIG. 1C is a graph that shows the I-V curve of a JJ;

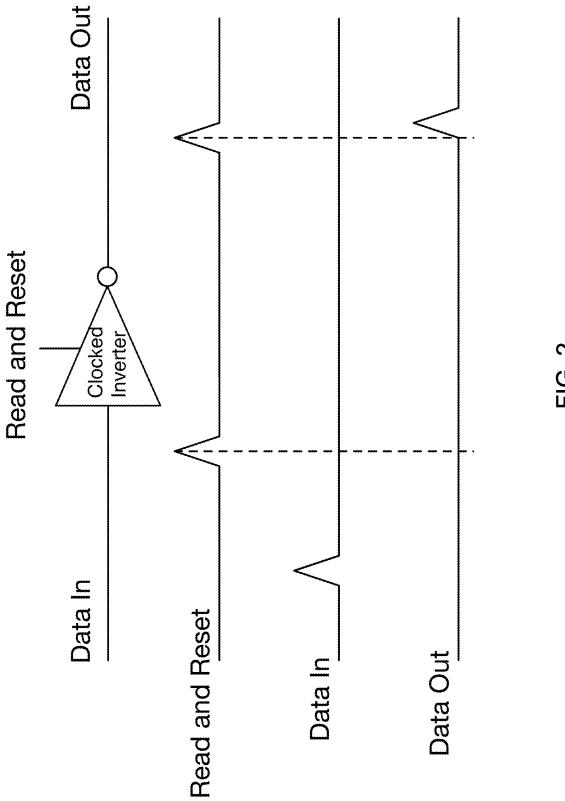

- FIG. 2 shows a timing diagram for an exemplary clocked RSFQ inverter;

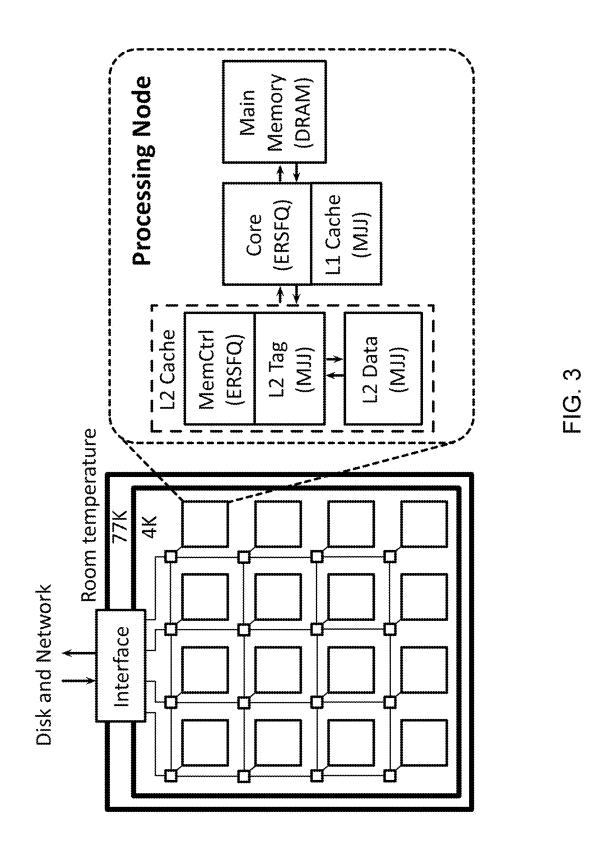

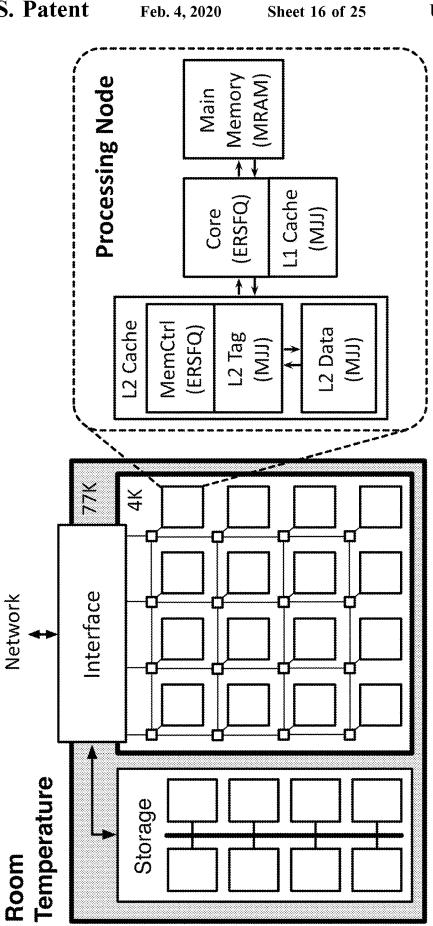

- FIG. 3 is block diagram which shows how different 55 components of the proposed system can be partitioned between room temperature and cryogenic environments;

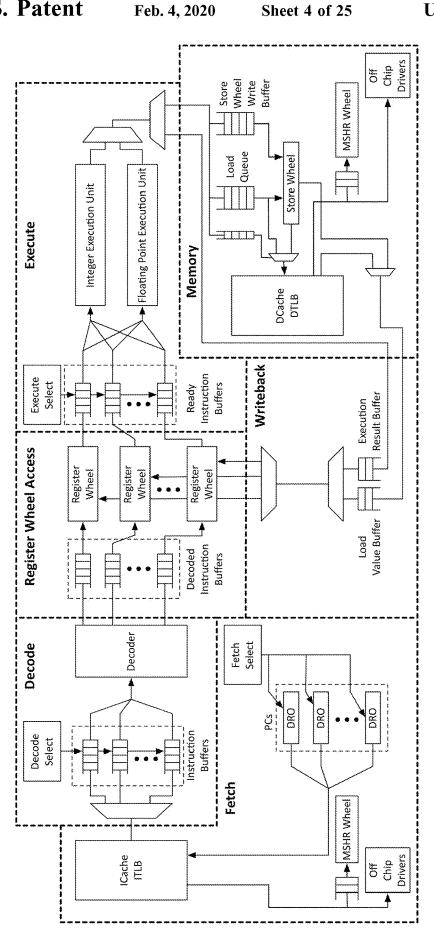

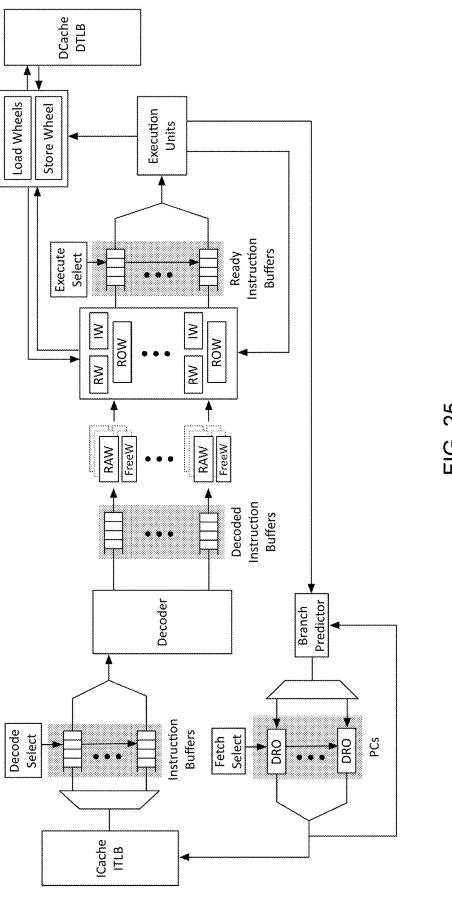

- FIG. 4 shows a block diagram of one exemplary embodiment of a processor based on RSFQ logic;

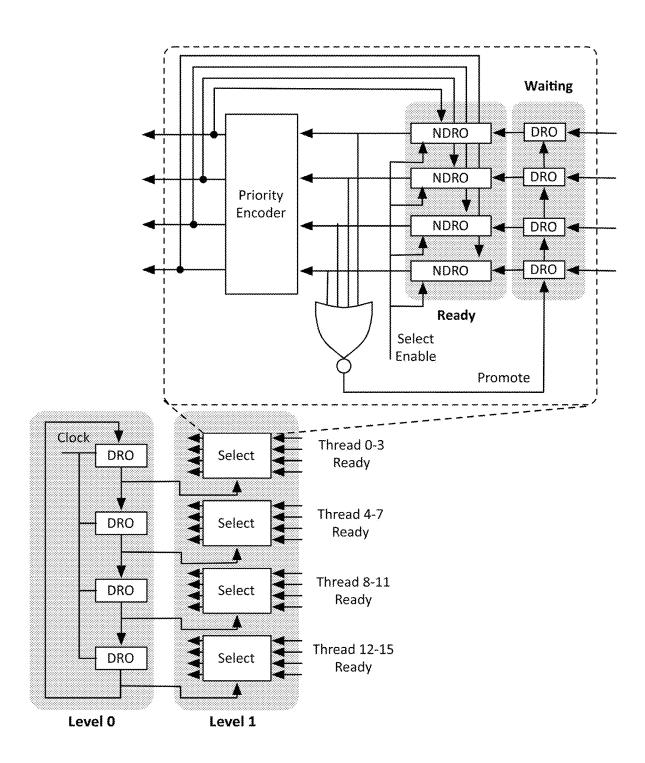

- FIG. 5 shows a schematic diagram of an exemplary 60 pseudo round-robin scheme which implements a two-level selection mechanism;

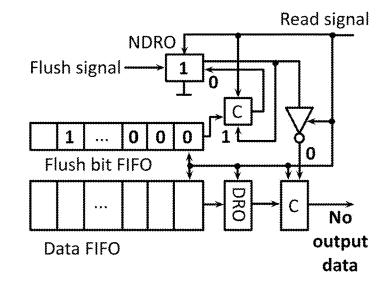

- FIG. 6A is a schematic diagram showing a normal operation of an exemplary RSFQ FIFO that can support a flushing

FIG. 6B shows a flush contents operation of the RSFQ FIFO of FIG. 6A;

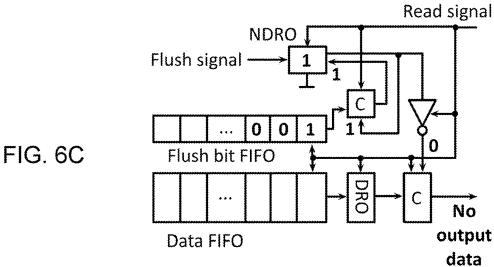

FIG. 6C shows a clear flushing signal operation of the RSFQ FIFO of FIG. 6A;

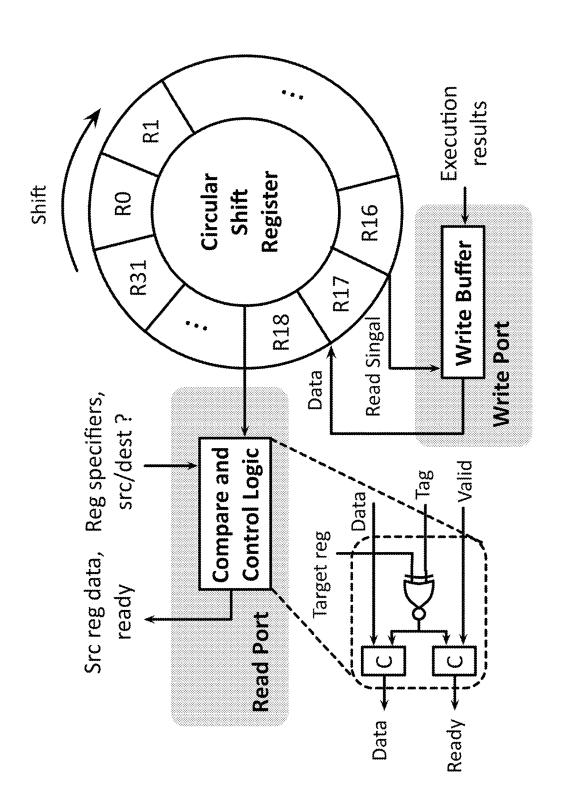

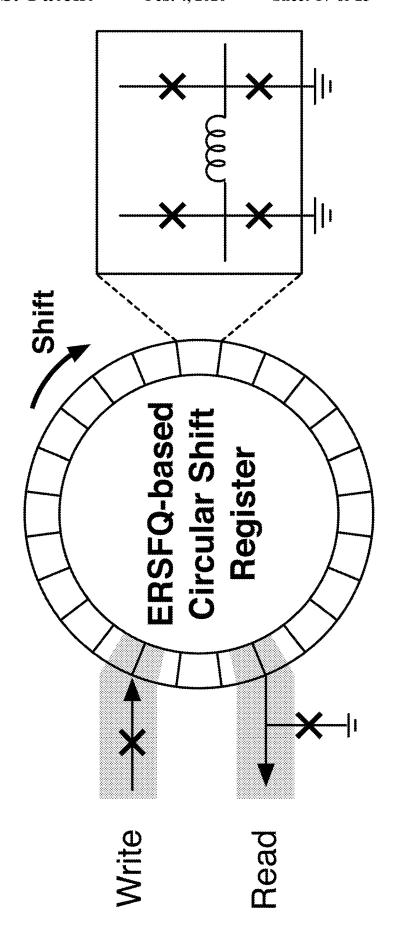

FIG. 7 shows a schematic diagram of an exemplary register wheel:

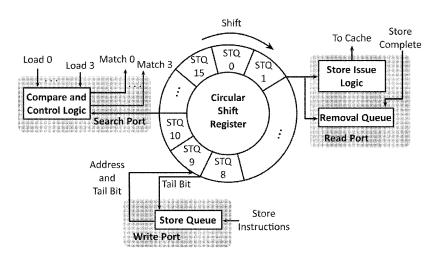

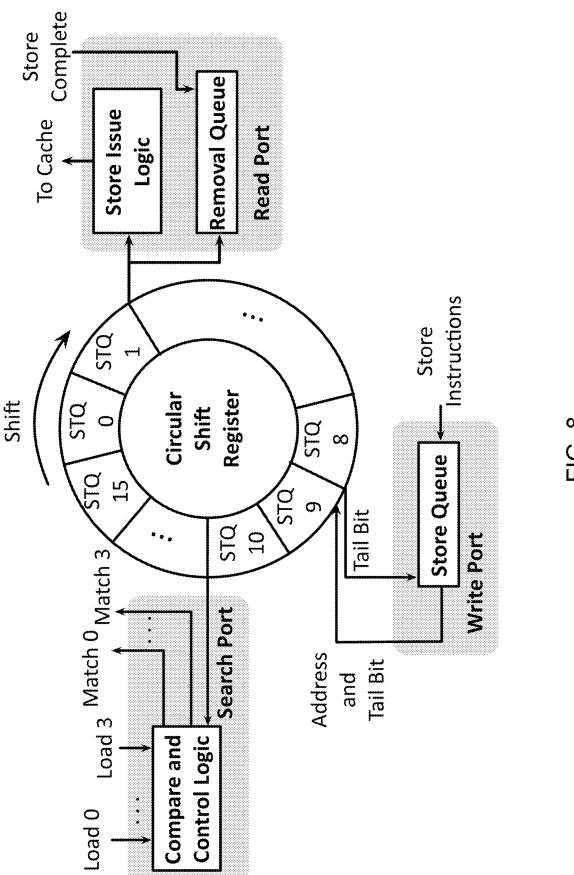

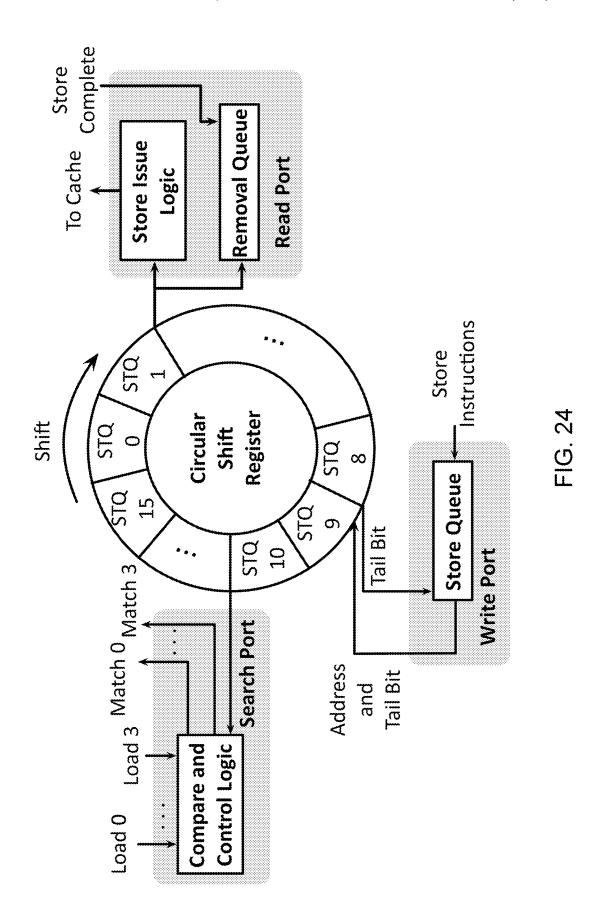

FIG. 8 shows a schematic diagram of an exemplary store

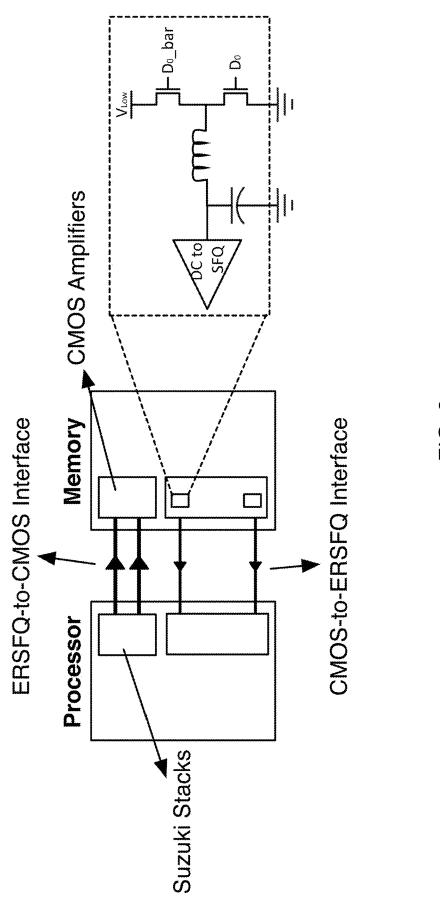

FIG. 9 shows a schematic diagram of one exemplary circuit suitable for interfacing RSFQ voltage pulses and CMOS voltage levels;

FIG. 10 shows an exemplary DRAM timing diagram;

FIG. 11 shows a table 1 of exemplary architecture param-

FIG. 12 shows a table 2 of exemplary architecture parameters of a baseline core and shared memory subsystem;

FIG. 13 shows a table 3 of simulated applications and

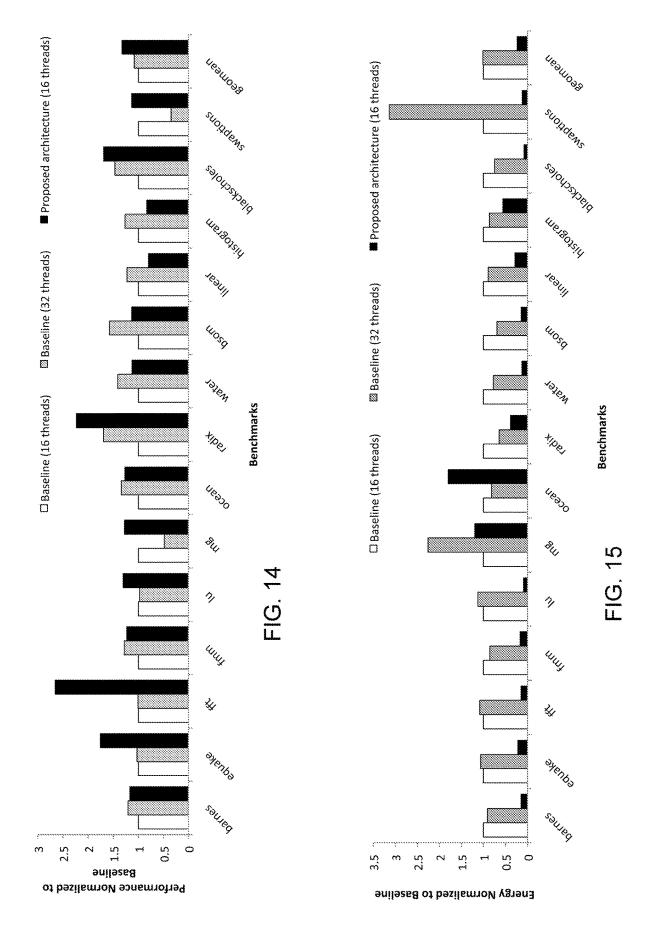

FIG. 14 is a bar graph showing exemplary performance normalized to baseline for various benchmarks;

FIG. 15 is a bar graph showing exemplary energy normalized to baseline for various benchmarks;

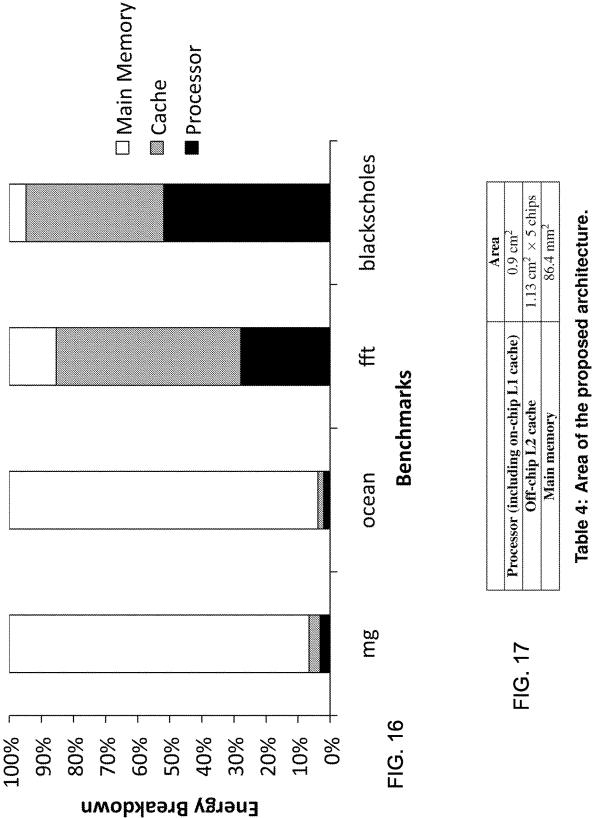

FIG. 16 is a bar graph showing an exemplary energy breakdown for various benchmarks;

FIG. 17 is a table 4 showing areas of an processor, ment of the new architecture;

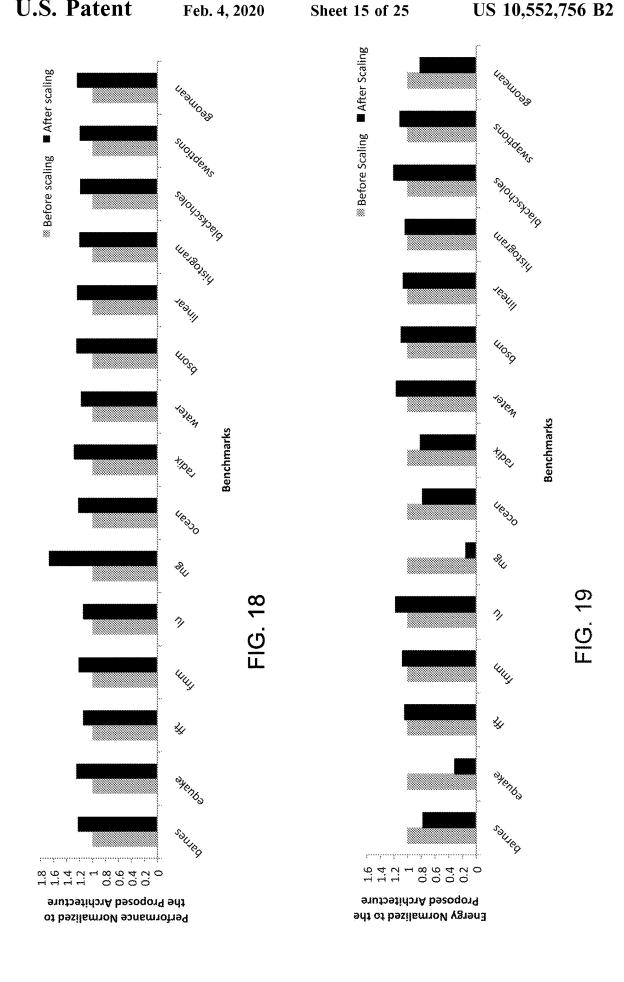

FIG. 18 is a bar graph showing performance normalized to the new architecture for various benchmarks;

FIG. 19 is a bar graph showing energy normalized to the new architecture for various benchmarks;

FIG. 20 is a block diagram showing an exemplary system overview:

FIG. 21 is a diagram of an exemplary wheel architecture;

FIG. 22 is a diagram of an exemplary clearable FIFO;

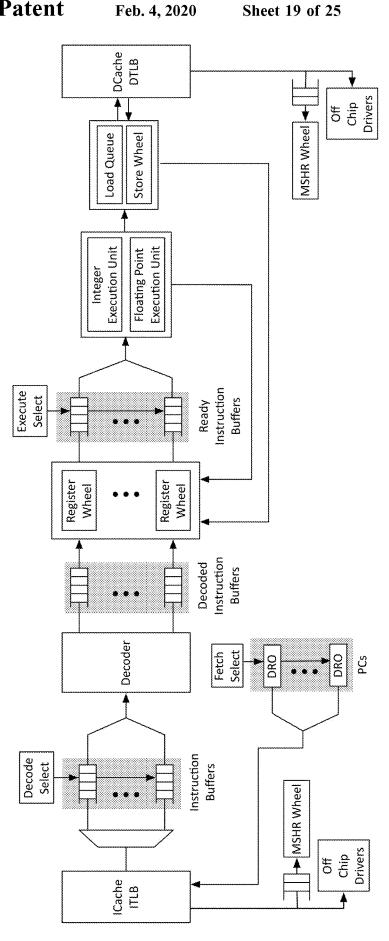

FIG. 23 is a block diagram of an exemplary ERSFQ based in-order processor core:

FIG. 24 is a diagram of an exemplary store wheel;

FIG. 25 is a block diagram of an exemplary out-of-order 40 ERSFQ based processor;

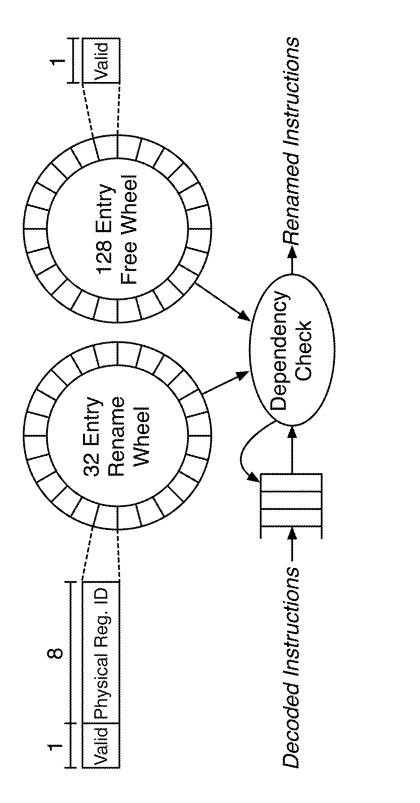

FIG. **26** is a diagram of an exemplary rename architecture: FIG. 27 is a schematic diagram of an exemplary crosspoint circuit;

FIG. 28A shows a planar view of an exemplary crosspoint circuit:

FIG. 28B shows a profile view of the crosspoint circuit of FIG. 28A;

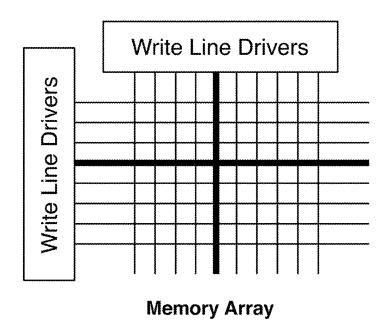

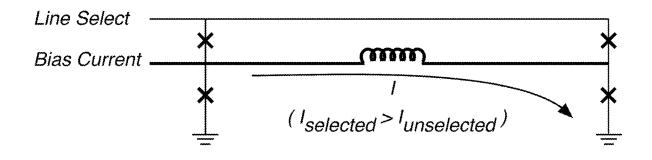

FIG. 29A shows a diagram of an exemplary field based MRAM write circuit;

FIG. 29B shows a schematic representation of a write line of the field based MRAM write circuit of FIG. 29A; and

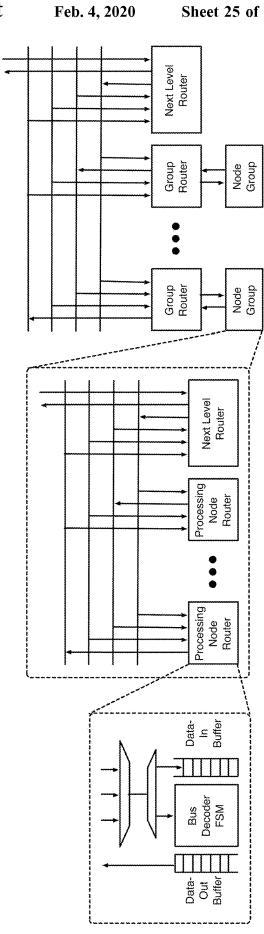

FIG. 30 is a block diagram showing an exemplary interconnection network.

#### DETAILED DESCRIPTION

In the description, other than the bolded paragraph numbers, non-bolded square brackets ("[ ]") refer to the citations listed hereinbelow.

1 Introduction

As described hereinabove, data centers and high performance computing have relied on Moore's law scaling to achieve petaflop scale compute capability within feasible power budgets. However, semiconductor scaling, abated by increasingly stringent power constraints, growing manufacturing variability, and ultimately restricted by fundamental physical limits, is predicted to end soon [8, 48, 54]. More-

over, modern data center power consumption is predicted to increase by a factor of three to 661 TWh within the same time frame [6].

5

Niobium (Nb) based superconductor electronics, an existing and mature technology, enables fundamentally different 5 tradeoffs in performance and power. This class of electronics, based on superconductivity, enables ultra high frequency operation at voltage levels on the order of hundreds of microvolts, three orders of magnitude smaller than standard CMOS, resulting in microprocessors that can consume milliwatts of power with comparable performance to modern CMOS-based systems.

Typical circuits in single flux quantum (SFQ) circuits operate in excess of 20 GHz, while individual logic gates have been demonstrated that operate in excess of 770 GHz 15 [5, 9]. Cryogenic environments provide a near-zero thermal noise environment and quantized signal output, yielding reliable circuits at very small voltage signals. While SFQ circuits require cooling, such as, for example, a large cryocooler, many compute nodes can be placed within a housing 20 to amortize the cost, thereby enabling datacenter scale systems.

Conventional superconductor electronics, however, have been limited to small applications such as high frequency analog to digital conversion [28, 33, 37], low latency net- 25 work switches [17, 23, 60, 63, 64], and embedded space applications [35, 42, 68]. Small scale digital electronics have been demonstrated, but with limited applicability to general computer applications.

This application describes a new microprocessor and 30 memory system architecture based on energy efficient rapid single flux quantum (ERSFQ) technology. Unlike traditional CMOS which uses static voltage levels to represent logic states, ERSFQ signaling is based on propagating voltage pulses. Most ERSFQ gates are also self latching. However, 35 ERSFQ lacks a pass gate, which prevents isolation between different circuits on a common line, such as a bus or a decoder tree. These characteristics lead to a different design approach from traditional CMOS logic.

A new wheel structure is described hereinbelow which 40 enables search and multi-porting capabilities. The wheel structure, used to implement the register file, the store queue, and the miss status holding registers (MSHRs), significantly reduces the area overhead required to access and control CMOS-based DRAM at cryogenic temperatures is also described. An asymmetric memory bus with a simplified DRAM command scheme is presented to deliver sufficient bandwidth under a constrained power budget. The microprocessor and memory system architecture described here- 50 inbelow produces a 1.2 performance improvement over a conventional CMOS multicore system, while operating under a 30 mW power budget achieves a 4.3 times improvement in overall energy consumption.

#### 2 Superconducting Electronics

A superconductor is a material that exhibits zero DC resistance below a critical temperature. As a result, current circulating a superconducting loop flows indefinitely. Superconducting electronic circuits have found commercial application in numerous areas, including magnetic sensors [21, 60 25, 46, 55], MRI machines [19, 70-72], high-speed A/D converters [28, 33, 37], and reference voltage generators [20, 50, 51]. Their application to computer systems has been limited.

FIG. 1A is a drawing that shows the circuit symbol for the 65 switching element used in superconducting electronics, the Josephson junction (JJ). FIG. 1B is a drawing that shows

how a JJ is formed from a superconductor-insulator-superconductor (SIS) trilayer called the SIS junction. In large scale superconducting electronics fabrication, Niobium (Nb) or Niobium Nitrate is typically used as the superconductor, and Aluminum Dioxide or Silicon Dioxide is used as the insulator.

FIG. 1C is a graph that shows the I-V curve of a JJ. A JJ has two states: a superconducting state and a resistive state. In the superconducting state, the JJ behaves as a superconductor with zero DC resistance; in the resistive state, the JJ behaves as a resistor with finite resistance. The JJ transitions from the superconducting state to the resistive state when the current through the JJ exceeds a critical current, I<sub>c</sub>. When the junction is in the superconducting state, the current through the junction can take on any value between -I<sub>c</sub> and I<sub>c</sub>. Every time a JJ switches to the resistive state, a voltage pulse develops across its two terminals. In Rapid Single Flux Quantum (RSFQ) logic, this voltage pulse is used as the physical basis for logic operations.

JJ devices, and thus circuits based on JJ devices, can scale to deep sub-micron technology nodes. Modern JJ technologies exhibit physical feature sizes on the order of 1 µM, a scale significantly less dense (and more mature) than CMOS lithographic techniques can achieve. This implies that much of the technological development used for silicon can be repurposed for Nb processes. Physical scaling facilitates increases in the critical current density, J<sub>C</sub>, which is a physical parameter that describes the current required switch to a JJ from the superconducting state to the resistive state. This parameter is exponentially dependent on the tunnel barrier thickness.

JJ circuits also depend on large passive components to stabilize their operation. Each JJ must exhibit sufficient resistive damping to prevent unstable oscillatory behavior. These passive components often consume a majority of the circuit area. As J<sub>C</sub> increases beyond 100 A/cm2, the intrinsic resistance of the tunnel barrier becomes sufficient to damp the device. Hence, 100 A/cm<sup>2</sup> represents an inflection point in the scaling behavior of JJs, beyond which self-shunted JJs enable a significant density advantage over present Nb JJ technologies.

#### 2.1 Superconducting Logic Families

A number of logic families based on RSFQ logic have been proposed. These families aim at improving on RSFQ in typical CPU blocks. A memory subsystem that leverages 45 a number of ways, typically by reducing static power consumption.

#### 2.1.1 Rapid Single Flux Quantum (RSFQ) Logic

RSFQ logic uses the switching property of JJs to transmit and store the short voltage pulses that are generated when a JJ transitions to the resistive state. RSFQ logic is promising because it provides fast switching (1 ps) and low energy per switching event  $(10^{-19} \text{ J})$  [26].

Unlike CMOS logic gates which represent high and low logic values with different voltage levels, RSFQ logic gates 55 represent logic values by the presence or absence of voltage pulses within a pre-determined timing interval. FIG. 2 shows a timing diagram for an exemplary clocked RSFQ inverter. In addition to the data input and output terminals, the inverter has a read and reset terminal connected to the clock. Before the arrival of the first reset signal, a voltage pulse appears at the input terminal (logic 1). This voltage pulse causes the inverter to store a logic 0, so that no output voltage pulse is generated the next time the read and reset input is pulsed. Conversely, between the first and second reset signals, there is no input pulse (logic 0), and as a result, the second reset causes an output voltage pulse (logic 1). This exemplary clocked RSFQ inverter demonstrates

another important property of RSFQ gates: many of the combinational CMOS logic gates are state holding in RSFQ. Conceptually, an RSFQ gate can be considered a conventional combinational logic gate in series with an output latch.

These differences in bit representation and gate design 5 create a number of important distinctions between RSFQ logic and traditional CMOS logic. One important RSFQ gate is a Muller-C gate, or "CFF". A Muller-C gate has three inputs—two data and one reset. If a pulse arrives at both data inputs without an intervening reset signal, then an output 10 pulse is generated. In RSFQ, a Muller-C gate can often serve a purpose similar to a pass gate in CMOS design. Another important RSFQ gate is the destructive read out (DRO) register, which provides a high density (4 JJs per bit) storage but suffers from destructive reads. In contrast, a nondestruc- 15 tive read out (NDRO) register provides an input and output port for non-destructive reads but uses 9 JJs. Note that neither a NDRO nor a DRO register can have a stored 1 overwritten by a 0 without an intervening reset. For fan-in, a special RSFQ gate known as a "merger" is used. A merger 20 serves as an asynchronous OR gate, and can be combined with a DRO or inverter to create synchronous OR and NOR gates, respectively. Fan-out uses a special RSFQ gate known as a splitter, which splits a voltage pulse along two paths, and restores the voltage pulse to full height. For large fan-in 25 or fan-out, a merger or splitter tree is typically used. Most gates that are used in CMOS are also available in RSFQ; however, the cost of these gates is quite different. For example, multiplexers, demultiplexers, XOR gates, and DRO.

#### 2.1.2 ERSFQ

Although the dynamic power dissipation of standard RSFQ circuits is low, the total power consumption is dominated by the static power caused by Joule heating in current 35 biasing resistors. This limits the use of standard RSFQ for VLSI circuits [38]. ERSFQ logic is one of the energyefficient SFQ logic families that can eliminate the static power dissipation by using inductors to generate DC bias currents. ERSFQ employs a combination of additional junc- 40 tions and inductors that increase the junction count and area by about 40 times over standard RSFQ, and approximately doubles the dynamic power dissipation. However, compared to the standard RSFQ logic, ERSFQ is much more energy efficient because it virtually eliminates static power con- 45 sumption.

#### 2.2 Magnetic Josephson Junction

A Magnetic Josephson Junction (MJJ) is a Josephson spintronic device with a ferromagnetic layer, which can change and retain the critical current value based on the 50 ferromagnetic layer magnetization. MJJs are compatible with the traditional JJs used for standard RSFQ or ERSFQ logic, and they can be integrated on the same chip with JJs in a single fabrication process [57]. Therefore, a simple hybrid decision-making pair (dc biasing and serially con- 55 necting a MJJ with a standard JJ) can be used as a memory cell to build a fast, energy-efficient, nonvolatile and relatively dense cryogenic cache [39, 49, 57]. For a MJJ based memory array, the write operation is performed by sending multiple SFQ pulses, generated by an SFQ-to-DC converter 60 [18, 45], to the desired memory cell. The critical current of the MJJ in the target memory cell is modified such that it is either above or below the critical current of the JJ in the cell. The read operation is performed by sending an SFQ pulse along a wordline. This SFQ pulse triggers either the MJJ (generating a pulse on the bit line) or the standard JJ (generating no pulse) depending on which JJ has a lower

critical current. The absence or presence of this pulse is detected to read out a line [39, 49, 57].

Although the capacity and density of MJJ based memory is lower than cryogenic hybrid JJ-CMOS RAM [29, 56], it has the capability to operate with a clock rate and energy consumption similar to ERSFQ circuits. In addition, compared to other native SFQ technologies, MJJs can have a higher density because the storage element is a ferromagnetic layer rather than a large inductor.

#### 2.3 Cryostats

The cryogenic environment is an important difference between RSFQ and CMOS that imposes a number of limitations. For example, in some embodiments, 4 Kelvin cryostats typically use a two stage design with an initial cooling stage that uses liquid nitrogen and a cold-head or cold box that is cooled to 4K. A cryostat has a cooling efficiency, typically reported in watts per watt, which indicates how many watts of power it takes to dissipate one watt within the cryostat. This value varies from several thousand watts per watt to several hundred watts per watt depending on a number of factors, including the size of the cryostat (the larger the better). Cryostats also have a finite cooling capacity, which limits the maximum power that can be dissipated within the cryostat. Interfacing between the cryostat and room temperature allows heat leak into the system within the interface; this heat leak grows with the number and crosssectional area of the wires.

#### 3 Overview

An energy efficient, superconducting computer system XNOR gates are several times more expensive than a basic 30 can be designed by partitioning hardware components between cryogenic and room temperature environments based on latency and power considerations. On the one hand, communicating with components outside the cryostat involves traversing wires longer than one meter, which results in long latencies. On the other hand, the cryostat has a limited power budget, and draws multiple hundreds of watts from the power supply for every watt consumed inside the cryostat. The limited cooling capacity of the cryostat makes it impractical to cool high-power devices to cryogenic temperatures. Once the system has been partitioned between cryogenic and room temperature domains, the electrical interface between these different temperature regimes should be architected to minimize the number and size of the wires, as wires allow heat to leak into the cryostat and cut into the cooling and power budgets.

FIG. 3 is block diagram which shows how in one exemplary embodiment different components are partitioned between room temperature and cryogenic environments. Inside the cryostat, a mesh architecture connects processing nodes, each comprising a multithreaded ERSFQ processor, off-chip L2 cache implemented with MJJs, and main memory implemented with 1T-DRAM. External storage, a network interface, and power supplies are located outside the cryostat at room temperature, as the power consumption of these modules far exceeds the power budget of the cryostat. To minimize heat leakage, the cryogenic environment connects to room temperature through an intermediate cooling stage at 77 Kelvin, which uses liquid nitrogen. Only the performance of a single node is considered as described in more detail hereinbelow. RSFQ network routers suitable to enable message passing among multiple nodes have been designed and studied in prior work [41, 65, 66, 69].

#### 4 Processor

The proposed processor comprises six major pipeline stages: fetch, decode, register file access, execute, memory, and write back. These stages are connected through asynchronous FIFOs [22] to allow different stages to operate at

different clock rates. FIG. 4 shows a block diagram of an exemplary embodiment of a processor based on RSFQ logic. This globally asynchronous, locally synchronous (GALS) hardware organization simplifies the clock distribution network, and provides the opportunity to improve performance 5 and energy efficiency. Because RSFQ logic gates can switch fast and hold state, most of the major stages are further partitioned into minor pipeline stages. Thus, the ERSFQ processor is deeply pipelined without incurring the overhead of extra pipeline registers that would be needed in a deeply pipelined CMOS processor. To keep the pipeline busy, the proposed processor uses fine grained multithreading with sixteen thread contexts.

#### 4.1 Front-End

In one exemplary embodiment, the fetch unit includes a 15 thread selector, a PC for each thread context, and an adder to compute the next PC, and control logic. Because of the low JJ density at the current RSFQ technology node, the thread selection logic implements a simple, pseudo-roundrobin policy that minimizes JJ count. This reduction in JJ 20 count is achieved by using gates that are simple to implement in RSFQ, such as a destructive readout register and a merger, instead of complex gates such as multiplexers or XNOR gates.

FIG. 5 shows a schematic diagram of an exemplary 25 pseudo round-robin scheme which implements a two-level selection mechanism. In the first level, it divides the sixteen threads into four groups, and uses a four-bit shifter to select one of the groups in round-robin order. Within the selected group, one of the ready threads (i.e., the threads that are not 30 stalled due to a full instruction buffer or an instruction cache miss) is selected using a priority encoder. To avoid starvation, two bit-vectors are used within each group: (1) a ready bit-vector, which records the request signals to the priority encoder and resets the entry for a ready thread to zero as 35 soon as that thread is scheduled; and (2) a waiting bit-vector, which records newly available threads that become ready while the scheduler works on the threads in the ready bit-vector. Once all of the threads whose bits are set in the ready bit-vector are scheduled, the waiting bit-vector is 40 copied to the ready bit-vector, and is reset to zeroes. Although it is possible for the selected group to have no threads that are ready to fetch, this situation is rare in practice, and the pseudo round-robin scheme provides performance comparable to a true round robin policy with much 45 lower hardware cost. Because the processor is deeply pipelined and a branch instruction takes multiple clock cycles to resolve, the fetch engine uses a simple static branch prediction scheme (always not taken). Every clock cycle, the PC of the selected thread is sent to the instruction cache.

Because content addressable memory (CAM) is expensive in the RSFO logic family, the buffers that connect the decode stage to the fetch and register wheel access stages are implemented with a FIFO structure that supports flushes to efficiently recover from branch mispredictions.

FIG. 6A is a schematic diagram showing a normal operation of an exemplary RSFQ FIFO that can support a flushing scheme. This FIFO structure includes multiple data entries, and a flush bit per entry. These flush bits, as well as the When the next stage tries to read data from the FIFO, the Muller-C gate is enabled by the inverted NDRO output, which allows valid data to pass through the Muller-C gate and reach the next stage.

FIG. 6B shows a flush contents operation of the RSFQ 65 FIFO of FIG. 6A. If the FIFO receives a flush signal, the state of the NDRO register is set to 1, and a 1 is inserted at

10

the tail of the FIFO. As a result, the inverted NDRO output becomes 0, which prevents the data from passing through the Muller-C gate. As the invalid data progresses through the FIFO, the data is set to zero on readout by the Muller-C gate.

FIG. 6C shows a clear flushing signal operation of the RSFQ FIFO of FIG. 6A. When the flush bit reaches the head of the FIFO, the stored 1 resets the NDRO flush flag and the system returns to normal operation as shown in FIG. 6C.

The proposed pseudo round-robin selection logic can also be used in the instruction decoder to select an instruction to be decoded from one of the sixteen instruction buffers. The decoder uses a combination of shifters and Muller-C gates (instead of expensive multiplexers) to steer the decoded instruction to the buffer for the corresponding thread. In one exemplary embodiment, the decoder is divided into four minor stages, and is designed to maintain a high clock frequency. The jump address is computed in parallel with the decoding, and is sent to the fetch engine at the end of the decode stage.

#### 4.2 Register File Access

Conventional register files are inefficient to implement in RSFQ due to the large number of JJs necessary to implement each register with non-destructive readout. FIG. 7 shows a schematic diagram of a new hardware structure called a "register wheel" which solves this problem. The proposed register wheel implements a circular buffer using efficient DRO registers. Each entry of the register wheel stores one architectural register and a valid bit. Every register wheel cycle, the register wheel conceptually rotates by one entry, and a different register becomes accessible through its read port. Thus, the contents of any register can be observed by waiting in the register wheel access stage until the register appears at the read port, as conceptually shown in FIG. 7.

When an instruction arrives at the register wheel access stage, the source and destination register specifiers are sent to a compare and control logic. Because the architectural registers rotate constantly, the compare and control logic can compare the source and destination register specifiers against a new register tag stored in the wheel every cycle. If the current register is valid and its tag matches one of the source register specifiers, the register value is latched and sent to the next stage for execution. At the end of this clock period, the wheel rotates by one element and the next stored register becomes accessible via the read port. However, if the stored register tag matches the destination register specifier, before moving to the next shifter in the circle, the tag, the value, and the valid bit should all be reset to guarantee correct operation for the writeback stage. (Resetting the tag and value fields is done because a DRO register does not allow overwriting a 1 with a 0; instead, it provides a global reset functionality for all of the bits in the register.)

As the register wheel is built on top of the simple and fast DRO gate, it can rotate at a frequency that is several times higher than the core clock frequency of the processor, which 55 is four times faster in the proposed design. This higher clock rate reduces the worst case register file access latency by a factor of four.

#### 4.3 Execute

After accessing the register wheel, the instruction is sent nondestructive read out (NDRO) register, are initialized to 0. 60 to a ready instruction buffer shared by a group of threads, and is selected for execution using the pseudo round-robin scheme described hereinabove in Section 4.1. Both the ALU and the FPU are deeply pipelined to maintain a high clock frequency. The integer ALU and multiplier are designed based on existing work [1, 12, 15]. An RSFQ barrel shifter is implemented to handle the shift instructions, and completes execution in four cycles using a small number of JJs.

Since most of the existing RSFQ floating point adders and multipliers are bit-serial, a new, 32-bit deeply pipelined RSFQ floating point adder and multiplier are designed.

The branch condition is resolved in the execute stage; if the condition indicates a taken branch, the branch address and the branch signal are sent to the front-end for fetching. The branch signal is also sent to the decode and register wheel stages for recovery. After execution, the result is stored in the load/store queue as an effective address if the instruction is a load or a store; otherwise, it is placed in an ALU result buffer with its register tag and thread ID, where it awaits writeback.

#### 4.4 Memory Access

After effective address computation, loads and stores are respectively placed in FIFO load and store queues. In addition, a single bit flag indicating if the operation is a load or a store is written to a shared bookkeeping queue to preserve ordering. A store instruction blocks this queue until it can be written to the store wheel. To preserve in order 20 writeback and to avoid coherence issues, only one load and one store from each thread can be in flight simultaneously. The store queue and the MSHRs present a challenge for RSFQ logic due to the lack of an efficient CAM circuit. In some embodiments, a CAM wheel structure similar to the 25 register wheel described in Section 4.2 is used to implement the store queue (i.e. the store wheel) and the MSHRs. One important difference between the store wheel and register wheels (previously discussed) is the need for ordering information in the store queue. A store cannot be written into 30 an arbitrary entry on the wheel, instead head and tail bits should be stored in every wheel entry to track the location of the store queue head and tail. An additional bit flag is stored in the wheel to track whether the corresponding store instruction has issued to memory. After this bit passes the 35 read port of the store wheel, the oldest store in the queue that has not been sent to memory is issued. If the store hits in the cache, it is removed from the wheel; if it misses in the cache, it is allocated an MSHR entry.

When a load instruction reaches the head of the load 40 queue, the load speculatively accesses the cache and begins searching the store wheel, which in some embodiments, can take from one to four cycles depending on the current state of the wheel. To prevent the load queue search from becoming a performance bottleneck, the store wheel has multiple 45 search ports. A search operation can start at any point on the store wheel and looks for the head or tail bits. If the head bit is found first, all of the matches found between the beginning of the search and the tail bit must have been seen from the oldest to the youngest. Hence, if the tail bit is found first, 50 any matches found so far are known to be younger than any other matches to be found in the queue. If a match is found in the wheel, the corresponding value is forwarded to the load. If no matches are found in the cache or in the store wheel, the load is placed in an MSHR buffer to be written 55 into the MSHR wheel.

The MSHR wheel is a CAM wheel with an address field for comparison and two fields for secondary misses. Returning memory accesses search the MSHR wheel and add the instructions in the matching wheel entry back into the load 60 or store queues to be replayed.

#### 4.5 Writeback

Each clock cycle, a register value and its identifier are read from either an execution result buffer or a load value buffer in round-robin fashion. The register value is sent to 65 the write buffer inside the register wheel along with the thread ID.

12

As shown in FIG. 7, the write buffer is a FIFO, each entry of which stores the write back register value with its register tag. Every time a register in the wheel passes through the write port, its valid bit is inverted, and acts as the read signal of the write buffer. If the write buffer is not empty, both the value and the tag will enter the register wheel for future accesses. The write port can be placed next to the read port to reduce the latency between data dependent instructions.

#### 5 Memory Subsystem

To achieve a sufficiently large and fast memory subsystem, the architecture described herein can use two different memory technologies. MJJs can be used for caches; as a native RSFQ technology, where MJJs can be interfaced readily with ERSFQ circuits. The main memory can be implemented, for example, using 1T-DRAM to achieve high capacity.

#### 5.1 On-Chip L1 Caches and TLBs

The L1 instruction cache, the L1 data cache, and the TLBs can be implemented using magnetic Josephson junctions (MJJs), which are high-speed storage devices native to ERSFQ technology. The relatively low density of MJJs places substantial limits on the size of the L1 caches. The L1 data cache is shared among all of the threads to avoid the need for a coherence protocol. MJJs, similar to other MRAM technologies, suffer from long write latencies. To prevent writes from frequently blocking reads, in some embodiments, the cache is heavily banked. MJJ arrays use a well known SFQ-to-DC converter to convert an SFQ pulse into a pseudo-DC signal comprising multiple SFQ pulses spaced closely in time. In some embodiments, these SFQto-DC converters are used to implement the line and column drivers for the MJJ arrays. For tag comparisons, XNOR gate based comparators can be used instead of a CAM wheel, since (1) a tag comparison is a one time comparison, which allows destructive readout (rather than non-destructive readout) cells to be used, and (2) for tag comparison, the values cannot easily be loaded into a wheel in advance, since they must first be read from the array. Using XNOR gates limits the associativity of the L1 caches and the TLBs because of the relative inefficiency of XNOR gates compared to wheel based structures.

#### 5.2 Off-Chip L2 Cache

Density and integration scale limitations can prevent the L2 cache from being placed on chip. Therefore, in some embodiments, the L2 cache is split between five separate ICs within a multi-chip module (MCM), one containing the tag array and the control logic, and four containing 1 MB data arrays. Since the L2 is off chip, the strict JJ budget imposed on the L1 caches do not apply, which allows for greater associativity using XNOR based tag comparison. The L2 MSHRs are still implemented using a CAM wheel structure. To maximize the available bandwidth for the L2 cache, each L2 cache IC has a direct bus to the processor.

#### 5.3 Main Memory

High density main memory poses a significant challenge to ERSFQ systems. While MJJs provide sufficient density for caches, at present, the density of MJJs and other native RSFQ memories is not sufficient for main memory. Previous efforts have operated SRAM and DRAM at cryogenic temperatures to implement large scale RSFQ memories [29, 56]. In some exemplary embodiments, main memory is implemented with 1T-DRAM. In a cryogenic environment, 1T-DRAM gains a number of performance advantages over room temperature, mainly due to reduced line resistances and a high retention time that makes refresh operations unnecessary. Interfacing between SFQ voltage pulses and CMOS voltage levels consumes a substantial amount of

power. In some embodiments, to achieve sufficient amplification, a two-stage scheme can be employed (FIG. 9). A Suzuki Stack (SS) [44, 53], which is a well known latching JJ based amplifier, can be used on the ERSFQ processor, and communicates to a second stage CMOS amplifier on the memory chip. The power consumption of this interface is proportional to the number of parallel wires. To limit this power, a 34-bit bus carries the required information from the processor to memory. The bus is used for both read and write operations. On a write operation, the address (32 bits) and control signals (2 bits) are placed on the interface first. Next, the data block (512 bits) starts bursting on the 32 wires of the interface. As a result, a memory write operation requires 17 cycles to complete.

Similar to the write operation, a read operation transfers the address and control signals through the ERSFQ-to-CMOS interface. The data block, however, is transferred on a dedicated read bus, which relies on CMOS-to-ERSFQ interfacing techniques. As shown in FIG. 9, interfacing 20 CMOS with ERSFQ for reads can be accomplished by voltage matching with the ERSFQ circuits. In some embodiments, an NMOS-based interface is employed to drive off-chip connections to the ERSFQ microprocessor. The interface uses a reduced supply voltage (Vdd<sub>low</sub>) to drive the 25 interconnect line. A signaled data bit forms a resistive divider with the ERSFQ circuit to generate a low DC level on the output line. A DC-to-SFQ converter transforms this DC level into an SFQ pulse on the microprocessor. The interface from memory back to ERSFQ consumes substan- 30 tially lower power than the interface from the processor to memory, allowing for a wide bus to be used to increase read bandwidth.

The asymmetric latency and bandwidth characteristics of the memory bus uses a DRAM command protocol optimized 35 for the proposed computer system. An exemplary timing diagram for this command protocol is shown in FIG. 10. Note that the address and data write signals are transferred using the same interfacing wires in hardware. Because the command protocol is custom designed, it provides only the 40 functionality required for the proposed computer system. On a read, an address is sent along the shared address and data buses, and after  $t_{AL}$ + $t_{IF}$  cycles, it is returned along the wide read bus in a single cycle. On a write, the address is first sent on the shared address and data buses, followed by a burst of 45 data, one byte per cycle.

FIG. 10 shows the timing constraints used for three memory requests (two reads followed by a write to the same DRAM row). The first read access opens a new row, which uses precharge (PR) and activate (AC) operations and for a 50 multi-cycle latency ( $t_{CT}$ ) between the precharge and read (RD) operations. The row activation starts after the precharge completes ( $t_{FR}$ ). For each read operation, both address and command bits are transferred to the memory in one cycle. Because the read operations are to the same 55 DRAM row and the data read bus is sufficiently wide, the reads can be issued back to back. After  $t_{AL}$ + $t_{IF}$  cycles, the corresponding data blocks return from main memory in the same order the read commands were sent. After the reads, the memory controller issues the address and command bits 60 for the write operation.

#### 6 Experimental Setup (Example)

To evaluate the performance, energy, and area of the proposed architecture, both circuit and architecture level simulations were conducted. The tools, parameters, applications, and assumptions made in the evaluation are described in this section.

14

6.1 Circuits and RTL Design

To simulate CMOS at cryogenic temperatures, the 22 nm PTM model of a transistor was modified [67]. Key transistor performance parameters, such as the threshold voltage and mobility, were scaled from the transistor modeling data presented in [30]. Notably, operating at cryogenic temperatures results in a large transistor threshold that is comparable to the supply voltage of the technology. A forward body bias was applied to model a CMOS technology that has been optimized for cryogenic operation wherein the threshold and supply voltages have both been reduced. Circuit simulation was used to generate transistor performance parameters for the peripheral circuitry and cell transistors used in CACTI 6.5 [40]. Parasitic interconnect resistances were reduced in a cryogenic environment because bulk copper resistivity falls by approximately a factor of two thousand [32]. Offchip parasitics were modeled with an effective length of 1.5 centimeters, which is typical for System-In-Package interconnects. The parasitics were approximated by standard wire bond impedances available for MOSIS fabrication[36]. For power and delay estimation, a Verilog model of the processor was constructed and simulated using the Verilator toolkit [52]. Each pipeline stage was modeled individually to determine the critical path delay, and the activity factor per instruction. The critical path delay, the JJ count, and the area of the design were estimated using the Hypress and Bakolo[3] standard cell libraries scaled to a 10 kA/cm2 fabrication process.

#### 6.2 Architecture

The SESC [47] simulator was modified to model both the proposed architecture (parameters are shown in Table 1 of FIG. 11) and a Niagara-like in-order CMT baseline. Table 2 of FIG. 12 lists the architecture parameters of the baseline core and the shared memory subsystem. The energy and the area of the baseline processor were evaluated using McPAT [31].

To evaluate the energy of the proposed ERSFQ processor, the dynamic energy of a conventional RSFQ implementation of the processor is derived based on the JJ counts and the switching activity factor obtained from RTL simulation. Then, the ERSFQ energy is obtained according to the dynamic energy scaling factor from standard RSFQ to ERSFQ (the static power is zero for an ERSFQ circuit) [38]. The energy consumption of the cryostat is calculated based on the power consumption of commercially available cryostats [27]. A modified version of CACTI 6.5 [58] is used to derive latency, access energy, static power, and area for main memory at cryogenic temperatures, based on parameters obtained from circuit simulation.

#### 6.3 Applications

The evaluated benchmarks represent a wide range of parallel applications from Data mining [24], Phoenix [62], SPLASH-2 [59], SPEC OpenMP [10], NAS [2], and PAR-SEC [4] suites. FIG. 13 shows table 3 which lists these applications and their input sets.

#### 7 Evaluation

This section evaluates the performance, energy, and area characteristics of the new architectures described herein.

#### 7.1 Performance

FIG. 14 compares the performance of the proposed architecture to a baseline CMOS processor. The ERSFQ processor runs the applications with 16 threads, whereas the baseline processor is evaluated with both 16 and 32 threads. On average, the ERSFQ processor achieves 32.5% higher performance than CMOS with 16 threads. For two benchmarks, linear regression and histogram, the proposed architecture performs worse than the baseline. Compared to other benchmarks, these applications execute a higher proportion

of store instructions, and the store wheel writing delay causes the performance degradation. The best baseline performance is achieved at 32 threads (8 cores, 4 threads per core). On average, a 22.4% speedup is obtained over this baseline run with 32 threads

#### 7.2 Energy

FIG. 15 shows an energy comparison between the proposed architecture and two configurations of the baseline system: one with eight cores and two threads per core (which is the most energy-efficient baseline configuration), and another with eight cores and four threads per core. The proposed architecture reduces the energy consumption by 4.3× on average. However, for benchmarks mg and ocean, the energy consumption of the proposed architecture is 15 worse than the baseline. The reason as shown in FIG. 16 is that the main memory dominates the energy consumption of these two benchmarks. Since DRAM based cryogenic memory is not as energy-efficient as ERSFQ (or MJJs), the energy saved on the processor is not sufficient to compensate 20 for the energy consumed by the refrigeration system. It is contemplated that energy consumption can be further reduced by introducing RSFQ compatible energy-efficient main memory.

#### 7.3 Area

The area evaluation of the proposed architecture is shown in Table 4 of FIG. 17. At the current RSFQ technology node, the area of the processor and the off-chip L2 cache is much larger than similar components designed in CMOS technology. However, given the volume of the cold boxes in existing cryostats (e.g., 2.0 m×1.6 m×2.6 m [27]), the area is not a limiting constraint: the scale of the computer system that can be housed in a cryostat is primarily determined by power and cooling budgets rather than area.

#### 7.4 Scaling to Future Technology Nodes

To examine the potential of the proposed architecture under technology scaling, we study how the system scales under two different sets of assumptions. First, the system is scaled based on the increased JJ density that allows the size of the L1 and L2 caches to be doubled, and the L2 tag array and the MSHRs to be placed on chip. Second, we consider scaling the clock frequency based on the increased critical current density. Specifically, a core clock speed of 25 GHz and a wheel clock frequency of 75 GHz are evaluated. The 45 performance and energy improvements of the proposed architecture after scaling are shown in FIG. 18 and FIG. 19, respectively

The performance improvement of the scaled architecture is application dependent. For memory intensive applications 50 (mg, equake, ocean, and radix) whose working sets fit in the enlarged cache subsystem, the increased cache capacity dramatically reduces the number of main memory accesses, and improves performance. For bsom, the performance improvement is mainly due to the on-chip L2 tag array and 55 MSHRS after scaling. Other benchmarks benefit from the increased clock frequency, but the performance improvements are limited by the wheel latency. On average, the scaled architecture outperforms the unscaled one by 23.1%.

For the applications that have many L2 cache misses in 60 the unscaled configuration of the proposed architecture, most of the energy is expended on inefficient DRAM based main memory. As the capacity of the L2 cache increases, these applications achieve lower energy. For other benchmarks, the energy consumption does not change significantly because of the peripheral circuitry overhead of the large cache

16

8 Related Work

Given the theoretical advantages of RSFQ over CMOS, a number of efforts to use RSFQ as a possible alternative technology have been made. One important aspect of making RSFQ a viable alternative to CMOS is the development of fast, wide ALUs. There have been a number of fast ALU designs utilizing Kogge-Stone and sparse tree designs with various functionalities [1, 12, 15]. Another focus of research in this area is the search for an appropriate memory technology. Early work focused on using native SFQ based memories such as NEC's vortex transitional [43] memory, but these approaches suffered from limited density. Other work on RSFQ memories has attempted to use CMOS memories, both SRAM and DRAM, in a cryogenic environment. There have also been a number of proposed RSFQ microarchitectures. The Flux-1 [7, 14, 16] was an eight-bit, dual issue LIW processor where operations could only occur between adjacent registers to minimize wire lengths. The Corel [61] was another eight-bit microprocessor that used a more traditional four stage pipeline design with two substages per pipeline stage. The COOL-0 [13] was an RSFQ processor proposed for the Hybrid Technology Multithreaded (HTMT) architecture project. COOL-0 used a multithreading architecture to hide latencies with multiple thread groups that shared functional units. The Frontier architecture [11] was a 32-bit processor that organized the register file four eight-bit. In contrast to the prior work the proposed design represents a complete computer system, with a novel wheel concept that makes high capacity register files, store queues and MSHRs possible.

#### 9 Summary

We described hereinabove new superconducting architectures for parallel applications using ERSFQ. To exploit the unique properties of RSFQ gates with natural latching behavior and high switching speed, a deeply pipelined architecture uses fine grained multithreading of ERSFQ gates. A novel wheel structure uses a free running circular shift register to provide a register file and searchable queue functionality. In some exemplary embodiments, the proposed memory subsystem uses MJJs for the cache and 1T-DRAM for the main memory. Overall, the architecture achieves a 1.2× performance improvement over a baseline system with a 4.3× lower system energy.

Using new such new architectures as described hereinabove, ERSFQ holds significant potential for data center applications, and offers a number of potential avenues for future research. This includes a memory subsystem better designed for cryogenic operation, and increased single thread performance made possible through out-of-order execution.

#### 10 Example Datacenter in a Cryostat

The exemplary datacenter in a cryostat includes a system of compute nodes, each with processors and a supporting memory hierarchy, interconnected by a networking fabric to primary storage (FIG. 20). Each subsystem will be designed to exploit the speed and functionality of ERSFQ circuits to realize performance superior to existing datacenters.

#### 10.1 Fundamental Building Blocks

A computer system using JJ technologies uses architectural and circuit solutions to amortize the high cost of memory components. Implementing conventional register files, on-die random access memories (RAMs), and content addressable memories (CAMs) with ERSFQ logic is inefficient. Two new building blocks introduced hereinabove reduce the cost of memory components in ERSFQ-based processors: a storage wheel and a clearable FIFO. DRO

buffers, capable of high-speed and low-power pulse propagation are employed to perform fast read, write, and search

10.1.1 Implementing Efficient RAM and CAM Circuits with Storage Wheels