# **Supply and Threshold Voltage Scaling Techniques in CMOS Circuits**

by

#### Volkan Kursun

Submitted in Partial Fulfillment

of the

Requirements for the Degree

Doctor of Philosophy

Supervised by Professor Eby G. Friedman

Department of Electrical and Computer Engineering School of Engineering and Applied Sciences The College

> University of Rochester Rochester, New York 2004

UMI Number: 3122245

#### **INFORMATION TO USERS**

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

#### UMI Microform 3122245

Copyright 2004 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346  $\mathcal{MELIORA}$

# **Dedication**

This work is dedicated to my mother Nazan and my sister Pınar.

### **Curriculum Vitae**

The author was born in Ankara, Turkey on June 5, 1974. He attended the Middle East Technical University from 1995 to 1999 and graduated with a Bachelor of Science degree in Electrical and Electronics Engineering in 1999. He received a Master of Science degree in Electrical and Computer Engineering from the University of Rochester in 2001. Since 1999 he has been working toward a Ph.D. degree in Electrical and Computer Engineering at the University of Rochester.

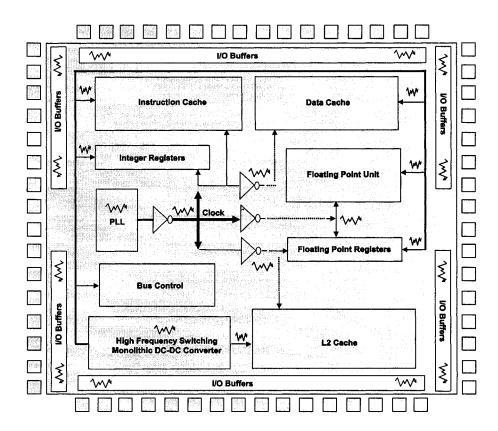

He performed research on high speed voltage interface circuits with Xerox Corporation, Webster, New York in 2000. During summers 2001 and 2002, he was with Intel Microprocessor Research Laboratories, Hillsboro, Oregon, responsible for the modeling and design of high frequency monolithic DC-DC converters. His current research interests include low voltage, low power, and high performance integrated circuit design, modeling of semiconductor devices, and emerging integrated circuit technologies.

## Acknowledgments

I would like to thank Professor Eby G. Friedman for his dedication and excellence as a supervisor. His technical skills as a researcher combined with his immense experience in management, human psychology, and life in general constitutes a rich source that I have been sampling since we have met. His guidance to his students goes well beyond the regular duty of a Ph.D. supervisor. He spent an ample amount of time on helping me to develop the necessary skills for becoming a successfull researcher in the field of Electrical and Computer Engineering. His continuous encouragement and support throughout my Ph.D. studies are deeply appreciated.

I would like to thank Doctor Siva G. Narendra of Intel Corporation, Hillsboro, Oregon for sharing his experience and enthusiasm with me during summers 2001 and 2002. I would also like to thank him for taking the time from his busy schedule to participate in my Ph.D final oral examination committee.

I would like to thank Professor David Albonesi for his leading role in the Complexity Adaptive Processing Project which initiated my interest in the areas of low power CMOS circuit design and monolithic DC-DC converters. I would also like to thank him for his support throughout my graduate studies and his service in my Ph.D. qualifying and final oral examination committees.

I would like to thank the colleagues at Intel Microprocessor Research Laboratories for the wonderful time we had during summers 2001 and 2002 in Hillsboro, Oregon. I continue to be inspired by their hard work and innovative thinking. My special thanks go to Shekhar Borkar, the Director of Circuit Research Labs, for managing a work environment that fully supports collaboration and creativity.

I would like to thank Professor Sandhya Dwarkadas and Professor Martin Margala for their support and service in my Ph.D. qualifying and final oral examination committees.

#### **Abstract**

The generation, distribution, and dissipation of power are at the forefront of problems faced in the development of high performance integrated circuits. Several techniques for designing low power and high speed integrated circuits are presented in this dissertation. Supply and threshold voltage scaling techniques, targeting lower power consumption and enhanced device reliability without degrading circuit speed, are described.

Systems with multiple supply voltages can significantly reduce power consumption without degrading speed by selectively lowering the supply voltages along non-critical delay paths. High frequency monolithic DC-DC conversion techniques applicable to multiple supply voltage CMOS circuits are presented in order to provide additional voltage levels with low energy and area overhead. Full integration of a high efficiency buck converter on the same die as a dual supply voltage microprocessor is demonstrated to be feasible. A low swing DC-DC conversion technique is presented that enhances the energy efficiency of a monolithic DC-DC converter. Device reliability issues in monolithic DC-DC converters operating at high input voltages are discussed. A cascode bridge circuit that guarantees the reliable operation of deep submicrometer MOSFETs without exposure to high voltage stress while operating at high input and output voltages is introduced.

An important technique for reducing the impact of supply voltage scaling on circuit performance is scaling threshold voltages. Exponentially increasing subthreshold leakage currents and worsening short-channel effects at reduced threshold voltages are discussed. Increasing performance degradation caused by dieto-die and within-die parameter variations at reduced gate lengths and threshold voltages is described. Dynamic threshold voltage scaling techniques reduce the deleterious effects of static threshold voltage scaling. A novel variable threshold voltage CMOS circuit technique for simultaneously enhancing the speed and power

characteristics of dynamic circuits is presented. Both reverse and forward body bias techniques are applied to domino logic circuits for enhanced robustness against onchip noise. Multiple threshold voltage CMOS circuits offer decreased subthreshold leakage currents and enhanced performance by selectively lowering the threshold voltages along the speed critical paths. A sleep switch dual threshold voltage domino logic circuit technique providing significant savings in subthreshold leakage energy is described.

## **Contents**

| De  | dicati  | on        |                                                       |                                         | iii  |

|-----|---------|-----------|-------------------------------------------------------|-----------------------------------------|------|

| Cu  | rricul  | um Vitae  |                                                       |                                         | iv   |

| Ac  | know    | ledgmen   | ts                                                    |                                         | v    |

| Αb  | stract  |           |                                                       |                                         | vi   |

| Lis | st of T | ables     |                                                       |                                         | xv   |

| Lis | st of F | igures    |                                                       |                                         | xvii |

| 1   | Intro   | duction   |                                                       |                                         | 1    |

|     | 1.1     | Evoluti   | on of Integrated Circuits                             |                                         | 4    |

|     | 1.2     | Outline   | of the Dissertation                                   | •••••                                   | 15   |

| 2   | Sour    | ces of P  | ower Consumption in CMOS Integrated Circuits          | •••••                                   | 22   |

|     | 2.1     | Dynam     | ic Switching Power                                    |                                         | 23   |

|     | 2.2     | Leakag    | e Power                                               | · • • • • • • • • • • • • • • • • • • • | 27   |

|     |         | 2.2.1     | Subthreshold Leakage Current                          |                                         | 27   |

|     |         |           | 2.2.1.1 Short-Channel Effects                         |                                         | 29   |

|     |         |           | 2.2.1.2 Drain-Induced Barrier Lowering                |                                         | 31   |

|     |         |           | 2.2.1.3 Characterization of Subthreshold Leakage Curr | rent                                    | 31   |

|     |         | 2.2.2     | Gate Oxide Leakage Current                            | · • • • • • • • • • • • • • • • • • • • | 37   |

|     | 2.3     | Short-C   | Circuit Power                                         | • • • • • • • • • • • • • • • • • • • • | 45   |

|     | 2.4     | Static I  | OC Power                                              | • • • • • • • • • • • • • • • • • • • • | 46   |

| 3   | Supr    | olv and T | hreshold Voltage Scaling Techniques                   |                                         | 48   |

|   | 3.1   | Dynam    | ic Supply  | Voltage Scaling                                    | 53  |

|---|-------|----------|------------|----------------------------------------------------|-----|

|   | 3.2   | Multipl  | le Supply  | Voltage CMOS                                       | 57  |

|   | 3.3   | Thresh   | old Voltag | e Scaling                                          | 61  |

|   |       | 3.3.1    | Body Bia   | as Techniques                                      | 67  |

|   |       |          | 3.3.1.1    | Reverse Body Bias                                  | 67  |

|   |       |          | 3.3.1.2    | Forward Body Bias                                  | 76  |

|   |       |          | 3.3.1.3    | Bidirectional Body Bias                            | 83  |

|   |       | 3.3.2    | Multiple   | Threshold Voltage CMOS                             | 88  |

|   | 3.4   | Multipl  | le Supply  | and Threshold Voltage CMOS                         | 93  |

|   | 3.5   | Dynam    | ic Supply  | and Threshold Voltage Scaling                      | 97  |

|   | 3.6   | Chapte   | r Summar   | y                                                  | 100 |

| 4 | Low   | Voltage  | Power Su   | pplies                                             | 102 |

|   | 4.1   | Linear   | DC-DC C    | onverters                                          | 106 |

|   | 4.2   | Switch   | ed-Capaci  | tor DC-DC Converters                               | 110 |

|   | 4.3   | Switch   | ing DC-D   | C Converters                                       | 112 |

|   |       | 4.3.1    | Operation  | n of a Buck Converter                              | 113 |

|   |       | 4.3.2    | Power Ro   | eduction Techniques for Switching DC-DC Converters | 117 |

|   | 4.4   | Chapte   | r Summar   | y                                                  | 118 |

| 5 | Anal  | ysis of  | Buck Con   | verters for On-Chip Integration with a Dual Supply |     |

|   | Volta | age Mici | roprocesso | r                                                  | 122 |

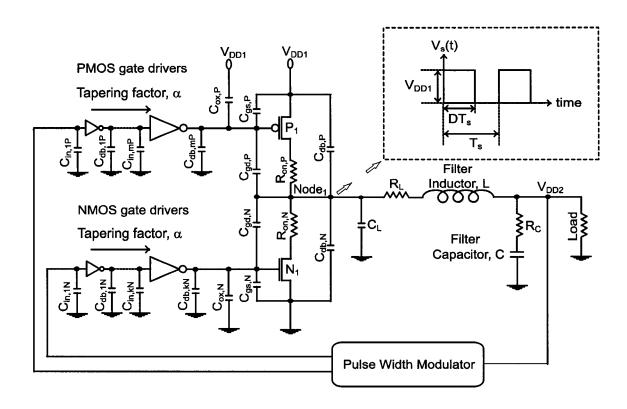

|   | 5.1   | Circuit  | Model of   | a Buck Converter                                   | 125 |

|   |       | 5.1.1    | MOSFET     | Γ Related Power Losses                             | 126 |

|   |       | 5.1.2    | Filter Inc | luctor Related Power Losses                        | 128 |

|   |       | 5.1.3    | Filter Capacitor Related Power Losses                       | 129 |

|---|-------|----------|-------------------------------------------------------------|-----|

|   |       | 5.1.4    | Total Power Consumption of a Buck Converter                 | 129 |

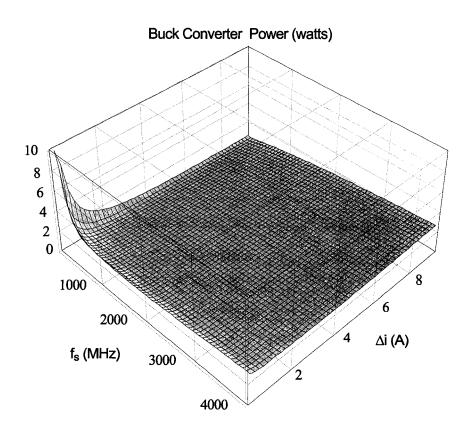

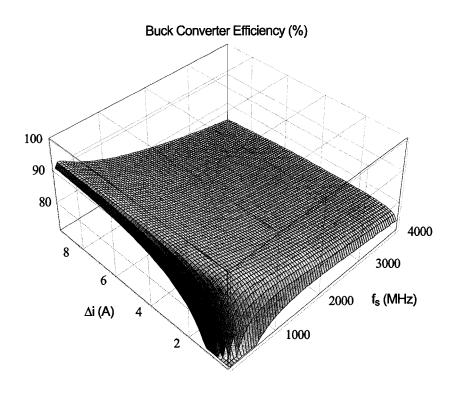

|   | 5.2   | Efficien | ncy Analysis of a Buck Converter                            | 130 |

|   |       | 5.2.1    | Circuit Analysis for Global Maximum Efficiency              | 132 |

|   |       | 5.2.2    | Circuit Analysis with Limited Filter Capacitance            | 136 |

|   |       | 5.2.3    | Output Voltage Ripple Constraint                            | 137 |

|   | 5.3   | Simula   | tion Results                                                | 140 |

|   | 5.4   | Chapte   | r Summary                                                   | 142 |

| 6 | Low   | Voltage  | Swing Monolithic DC-DC Conversion                           | 144 |

|   | 6.1   | Circuit  | Model of a Low Voltage Swing Buck Converter                 | 146 |

|   |       | 6.1.1    | MOSFET Power Dissipation                                    | 147 |

|   |       | 6.1.2    | MOSFET Model                                                | 150 |

|   |       | 6.1.3    | Filter Inductor Power Dissipation                           | 151 |

|   | 6.2   | Low V    | oltage Swing Buck Converter Analysis                        | 152 |

|   |       | 6.2.1    | Full Swing Circuit Analysis for Global Maximum Efficiency   | 153 |

|   |       | 6.2.2    | Low Swing Circuit Analysis for Global Maximum Efficiency    | 155 |

|   | 6.3   | Chapte   | r Summary                                                   | 159 |

| 7 | High  | Input V  | Voltage Step-Down DC-DC Converters for Integration in a Low |     |

|   | Volta | age CM(  | OS Process                                                  | 162 |

|   | 7.1   | Cascod   | le Bridge Circuit                                           | 165 |

|   | 7.2   | Large S  | Step-Down Non-Isolated Switching DC-DC Converter            | 166 |

|   |       | 7.2.1    | Operation of the Cascode DC-DC Converter                    | 166 |

|   |       | 7.2.2    | Efficiency Characteristics                                  | 168 |

|   |      | 7.2.3    | Charge Recycling Mechanism                                                      | 70  |

|---|------|----------|---------------------------------------------------------------------------------|-----|

|   | 7.3  | Chapte   | r Summary 1                                                                     | 71  |

| 8 | Sign | al Trans | fer in Integrated Circuits with Multiple Supply Voltages 1                      | 72  |

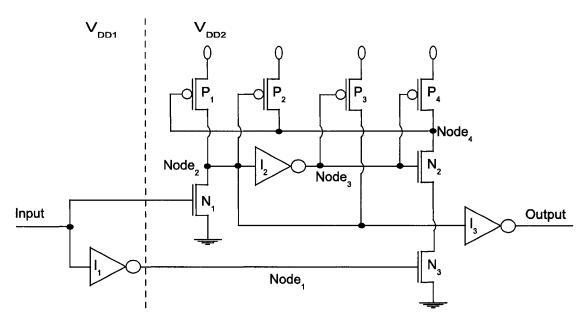

|   | 8.1  | A High   | Speed and Low Power Voltage Interface Circuit                                   | 74  |

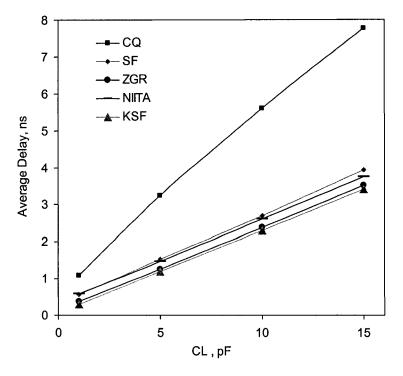

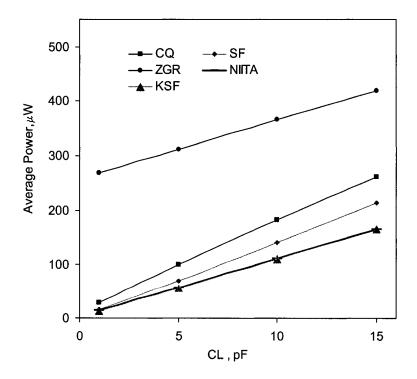

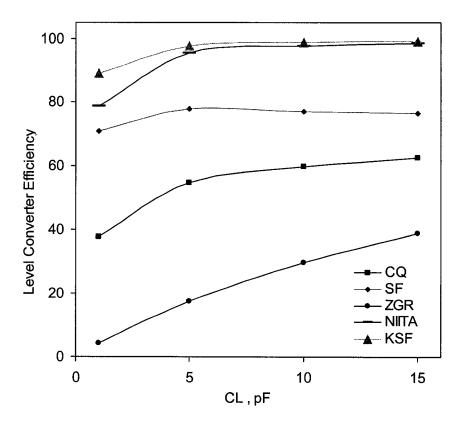

|   | 8.2  | Voltage  | e Interface Circuit Simulation Results                                          | 75  |

|   | 8.3  | Experi   | mental Results                                                                  | 80  |

|   | 8.4  | Chapte   | r Summary 1                                                                     | 82  |

| 9 | Dom  | ino Log  | ic with Variable Threshold Voltage Keeper 1                                     | 83  |

|   | 9.1  | Standa   | rd Domino Logic Circuits                                                        | 85  |

|   |      | 9.1.1    | Operation of Standard Domino Logic Circuits 1                                   | 85  |

|   |      | 9.1.2    | Noise Immunity, Delay, and Energy Tradeoffs in Domino                           |     |

|   |      |          | Logic Circuits                                                                  | 87  |

|   | 9.2  | Domin    | o Logic with Variable Threshold Voltage Keeper 1                                | 92  |

|   |      | 9.2.1    | Variable Threshold Voltage Keeper 1                                             | 92  |

|   |      | 9.2.2    | Dynamic Body Bias Generator 1                                                   | 94  |

|   | 9.3  | Simula   | tion Results 1                                                                  | 95  |

|   |      | 9.3.1    | Multiple Output Domino Carry Generator with Variable Threshold Voltage Keeper   | .96 |

|   |      |          | 9.3.1.1 Improved Delay and Power Characteristics with Comparable Noise Immunity | .99 |

|   |      |          | 9.3.1.2 Improved Noise Immunity with Comparable Delay or Power Characteristics  | 202 |

|   |      | 9.3.2    | Clock-Delayed Domino Logic with Variable Threshold  Voltage Keeper              | 204 |

|    |       | 9.3.3    | Impact of Gate Size on the Energy Overhead of the Dynamic                                                         |     |

|----|-------|----------|-------------------------------------------------------------------------------------------------------------------|-----|

|    |       |          | Body Bias Generator                                                                                               | 208 |

|    | 9.4   | Domino   | Logic with Forward and Reverse Body Biased Keeper                                                                 | 210 |

|    |       | 9.4.1    | Clock-Delayed Domino Logic with Forward and Reverse Body Biased Keeper                                            | 210 |

|    |       | 9.4.2    | Technology Scaling Characteristics of the Reverse and Forward Body Bias Techniques Applied to a Keeper Transistor | 215 |

|    | 9.5   | Chapter  | r Summary                                                                                                         | 217 |

| 10 | Subtl | nreshold | Leakage Current Characteristics of Dynamic Circuits                                                               | 219 |

|    | 10.1  | State D  | ependent Subthreshold Leakage Current Characteristics                                                             | 221 |

|    | 10.2  | Noise I  | mmunity                                                                                                           | 227 |

|    | 10.3  | Power a  | and Delay Characteristics During the Active Mode                                                                  | 232 |

|    | 10.4  | Dual T   | hreshold Voltage CMOS Technology                                                                                  | 234 |

|    | 10.5  | Chapte   | r Summary                                                                                                         | 239 |

| 11 | -     |          | Dual Threshold Voltage Domino Logic with Reduced Standby rent                                                     | 241 |

|    | 11.1  | Previou  | usly Published Sleep Mode Circuit Techniques                                                                      | 242 |

|    | 11.2  | Dual T   | hreshold Voltage Domino Logic Employing Sleep Switches                                                            | 246 |

|    | 11.3  | Simula   | tion Results                                                                                                      | 247 |

|    |       | 11.3.1   | Subthreshold Leakage Energy Reduction                                                                             | 249 |

|    |       | 11.3.2   | Stack Effect in Domino Logic Circuits                                                                             | 251 |

|    |       | 11.3.3   | Delay and Power Reduction in the Active Mode                                                                      | 254 |

|    |       | 11.3.4   | Sleep/Wake-up Delay and Energy Overhead                                                                           | 255 |

|    | 11.4  | Noise I  | mmunity Compensation                                                                                              | 260 |

|     | 11.5    | Chapter | Summary                                              | 265 |

|-----|---------|---------|------------------------------------------------------|-----|

| 12  | Low     | Swing D | Oomino Logic                                         | 268 |

|     | 12.1    | Power I | Reduction Techniques in Domino Logic Circuits        | 269 |

|     | 12.2    | Low Sv  | ving Domino Logic                                    | 272 |

|     |         | 12.2.1  | Low Swing Domino Logic with Fully Driven Keeper      | 273 |

|     |         | 12.2.2  | Low Swing Domino Logic with Weakly Driven Keeper     | 273 |

|     | 12.3    | Simulat | tion Results                                         | 274 |

|     | 12.4    | Dual Tl | nreshold Voltage Low Swing Domino Logic              | 279 |

|     | 12.5    | Chapter | r Summary                                            | 283 |

| 13  | Conc    | lusions |                                                      | 284 |

| 14  | Futur   | e Resea | rch                                                  | 293 |

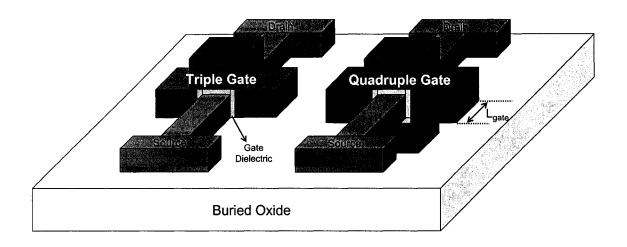

|     | 14.1    | Nanom   | eter Devices                                         | 293 |

|     | 14.2    | Energy  | Efficiency in CMOS Circuits                          | 294 |

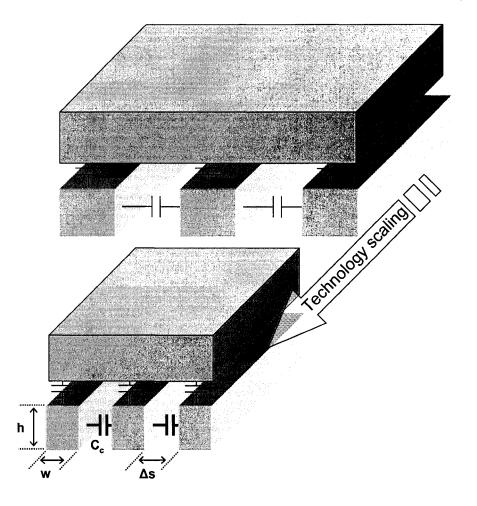

|     |         | 14.2.1  | Multiple Supply Voltage CMOS Circuits                | 295 |

|     |         | 14.2.2  | Dynamic Supply Voltage and Frequency Scaling         | 296 |

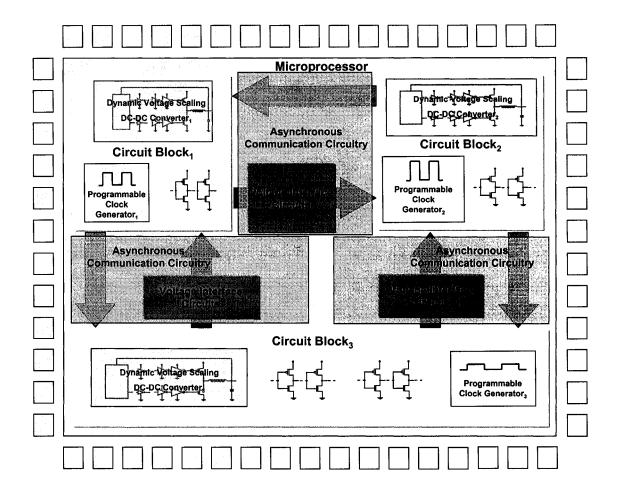

|     |         | 14.2.3  | Circuits with Multiple Voltage and Clock Domains     | 297 |

|     |         | 14.2.4  | Leakage Current Reduction Techniques                 | 299 |

|     | 14.3    | Reliabi | lity in CMOS Circuits                                | 300 |

|     |         | 14.3.1  | On-Chip Noise and Immunity Issues in CMOS Integrated |     |

|     |         |         | Circuits                                             | 300 |

|     |         | 14.3.2  | Parameter Variations                                 | 304 |

|     |         | 14.3.3  | On-Chip Clock Generation                             | 304 |

| Bih | oliogra | phy     |                                                      | 306 |

|                         | xiv |

|-------------------------|-----|

| Appendix A Patents      | 326 |

| Appendix B Publications | 327 |

## **List of Tables**

| 1.1 | Technological trends of high performance microprocessors                                                                                                                                                       | 7   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | A comparison of the subthreshold slope (S) and leakage current ( $I_{OFF}$ ) of                                                                                                                                |     |

|     | NMOS transistors fabricated at different technologies (T = 25°C)                                                                                                                                               | 36  |

| 2.2 | Semiconductor device scaling trends                                                                                                                                                                            | 38  |

| 2.3 | The dominant mechanisms of gate oxide tunneling current for different regions of operation of a MOSFET                                                                                                         | 42  |

| 4.1 | A comparison of the electrical characteristics and typical applications of the linear, switched-capacitor, and switching DC-DC converters                                                                      | 119 |

| 5.1 | Maximum efficiency circuit configurations of a buck converter with different filter capacitances                                                                                                               | 136 |

| 6.1 | Efficiency ( $\eta$ ) characteristics of the full swing (FS) and low swing (LS) DC-DC converter circuits obtained from the power model and simulation ( $V_{DD1} = 1.8 \text{ volts}$ and $C = 3 \text{ nF}$ ) | 150 |

|     | $(VDD) = 1.8 \text{ Voits and } C = 3 \text{ in}^3$                                                                                                                                                            | 159 |

| 7.1 | Circuit Characteristics of the Maximum Efficiency DC-DC Converters                                                                                                                                             | 169 |

| 8.1 | Normalized area, MFSO, and average internal power consumption of each voltage interface circuit ( $C_L = 1 \text{ pF}$ )                                                                                       | 179 |

| 8.2 | Experimentally measured test results                                                                                                                                                                           | 181 |

| 9.1 | A comparison of the evaluation delay, power dissipation, power-delay product (PDP), and NML (for maximum reverse body biased keeper) of                                                                        |     |

|     | SD and DVTVK circuit techniques for KPR = 2.2                                                                                                                                                                  | 201 |

| 9.2  | Achievable improvement in NML with the DVTVK circuit technique as compared to SD while maintaining equal delay, power dissipation, or PDP                                                                                                       |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | (KPR of DVTVK is 2.2)                                                                                                                                                                                                                           | 203 |

| 9.3  | Delay, power, and PDP savings of COR-DVTVK as compared to COR-SD with different keeper sizes                                                                                                                                                    | 206 |

| 9.4  | Achievable improvement in NML with the DVTVK circuit technique as compared to SD while maintaining equal delay, power dissipation, or PDP (KPR of DVTVK is 2.2)                                                                                 | 207 |

| 9.5  | Delay, power, power-delay product (PDP), and NML savings of COR-DVTVK as compared to COR-SD (with a forward body bias voltage of 0.6 volts)                                                                                                     | 214 |

| 11.1 | Input vectors applied to an adder                                                                                                                                                                                                               | 248 |

| 11.2 | Degradation in noise immunity of standard dual- $V_t$ and sleep switch adders as compared to the low- $V_t$ adder with same size transistors                                                                                                    | 261 |

| 11.3 | A comparison of normalized subthreshold leakage energy of low- $V_t$ , standard dual- $V_t$ , and sleep switch adders under similar and degraded noise immunity conditions                                                                      | 263 |

| 11.4 | Minimum duration of the idle mode required for the sleep switch circuit technique to provide a net savings in standby energy as compared to the standard low- $V_t$ and dual- $V_t$ adders under similar and degraded noise immunity conditions | 266 |

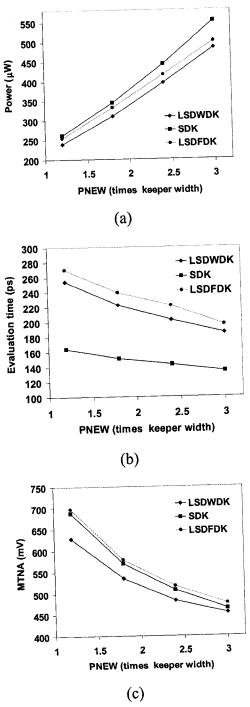

| 12.1 | Normalized dynamic power, evaluation delay, and MTNA (PNEW = 3)                                                                                                                                                                                 | 278 |

| 12.2 | Standby mode leakage power and active mode total power for different threshold voltage distributions                                                                                                                                            | 282 |

| 12.3 | Evaluation delay and MTNA for different threshold voltage distributions                                                                                                                                                                         | 282 |

# **List of Figures**

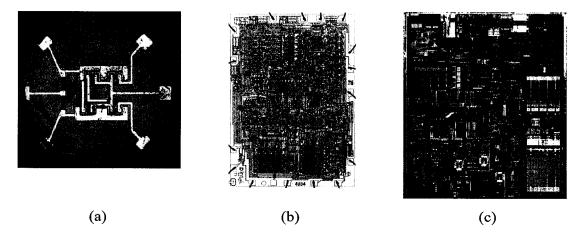

| 1.1 | Microphotographs of three landmark ICs from the evolution of the            |    |

|-----|-----------------------------------------------------------------------------|----|

|     | integrated circuit technology (the sizes of the dies are not to scale). (a) |    |

|     | The first monolithic integrated circuit, Fairchild Semiconductor (1959).    |    |

|     | (b) The first microprocessor, Intel 4004 (1971). (c) The latest Intel       |    |

|     | Pentium 4 microprocessor (2002)                                             | 1  |

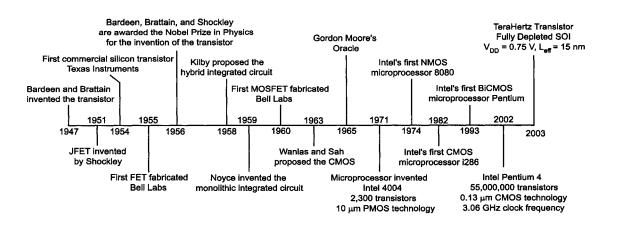

| 1.2 | A timeline of some of the key events during the evolution of                |    |

|     | semiconductor technologies                                                  | 5  |

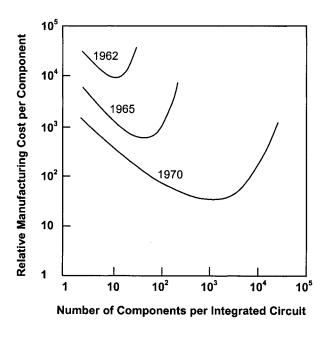

| 1.3 | The general form of Moore's law                                             | 6  |

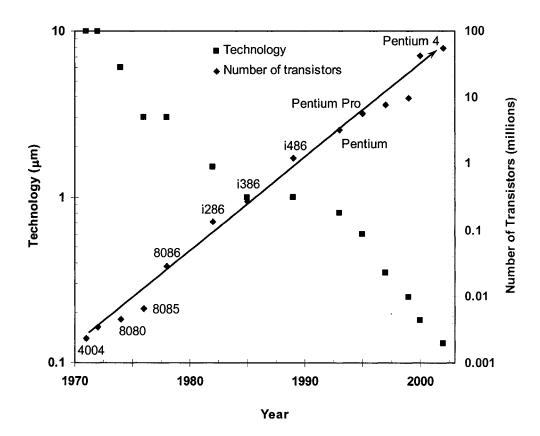

| 1.4 | Scaling of the minimum feature size and the increasing total number of      |    |

|     | transistors within each lead Intel microprocessor                           | 8  |

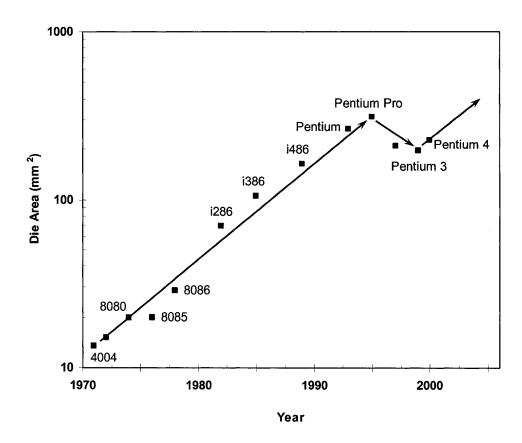

| 1.5 | Die area of lead Intel microprocessors                                      | 9  |

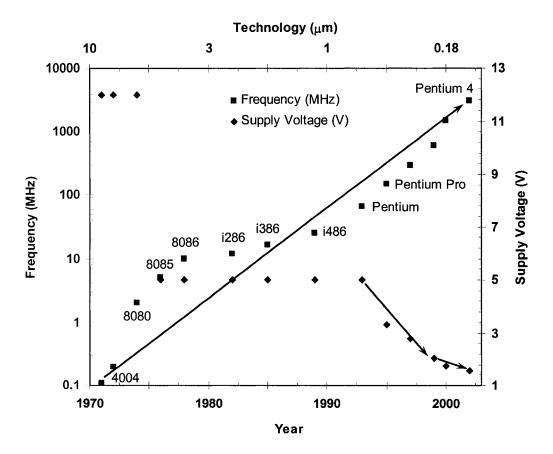

| 1.6 | Operating frequency and supply voltage of lead Intel microprocessors        | 11 |

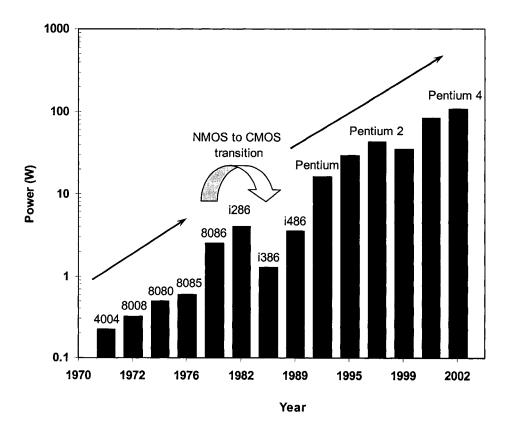

| 1.7 | Maximum power consumption of lead Intel microprocessors                     | 12 |

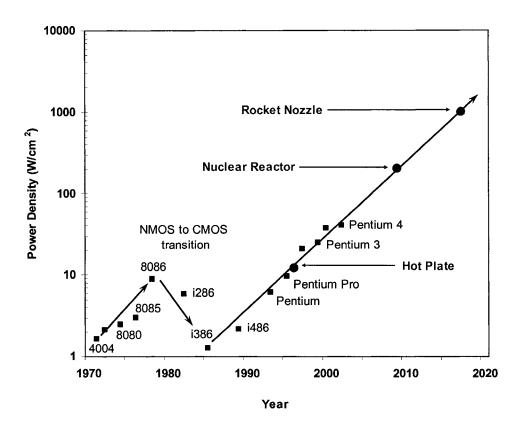

| 1.8 | Power density trends of lead Intel microprocessors                          | 13 |

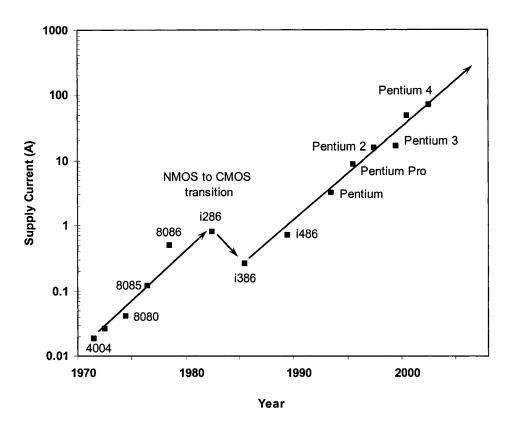

| 1.9 | Increasing current demand of lead Intel microprocessors                     | 14 |

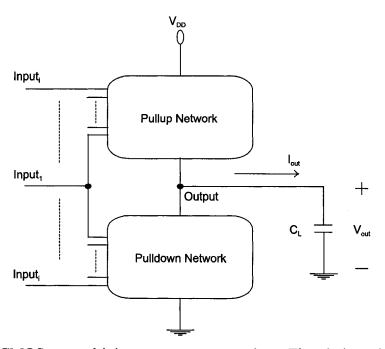

| 2.1 | A CMOS gate driving an output capacitor. The drain-to-body junction         |    |

|     | capacitances of the driver gate, the equivalent capacitance of the          |    |

|     | interconnect, and the gate oxide capacitance of the load transistors are    |    |

|     | lumped into a single equivalent capacitance. C <sub>1</sub>                 | 23 |

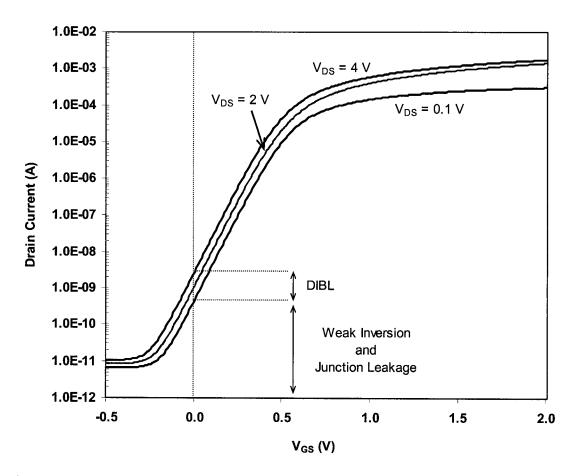

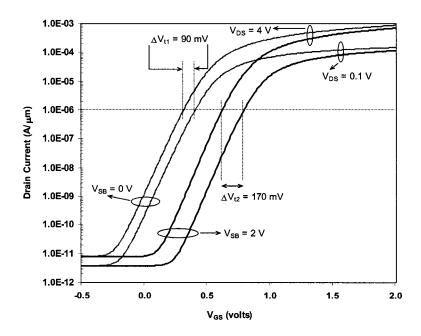

| 2.2  | The drain current of a short-channel n-type MOSFET as a function of the                                               |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

|      | gate-to-source voltage $(V_{\text{GS}})$ for three different drain-to-source voltages                                 |    |

|      | $\left(V_{DS}\right)$ . The DIBL, weak inversion, and p-n junction diode leakage                                      |    |

|      | components of the drain subthreshold leakage current are indicated (0.18                                              |    |

|      | $\mu m$ CMOS technology, W = 10 * W <sub>min</sub> , and L = L <sub>min</sub> )                                       | 28 |

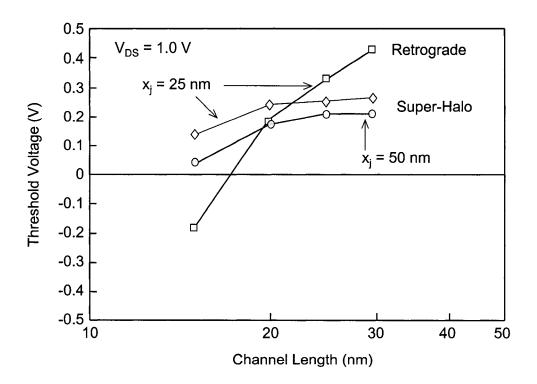

| 2.3  | Short-channel MOSFET threshold voltage roll-off for super-halo (both                                                  |    |

|      | vertically and laterally non-uniform) and retrograde (vertically non-                                                 |    |

|      | uniform) doping profiles                                                                                              | 30 |

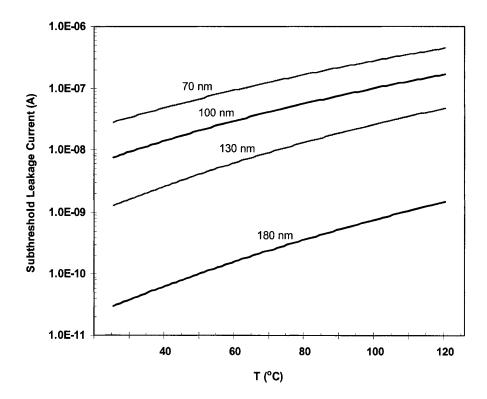

| 2.4  | Variation of the subthreshold leakage current with junction temperature                                               |    |

|      | for four different CMOS technology generations (W = 10 * $W_{min}$ and L =                                            |    |

|      | L <sub>min</sub> )                                                                                                    | 33 |

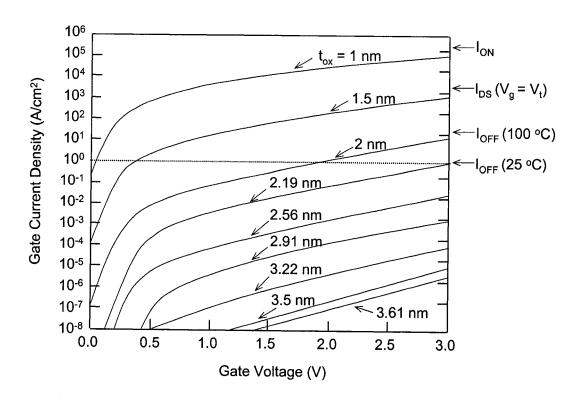

| 2.5  | Gate oxide tunneling current density as a function of the gate voltage for                                            |    |

|      | various gate oxide (SiO <sub>2</sub> ) thicknesses assuming a 100 nm CMOS                                             |    |

|      | technology                                                                                                            | 39 |

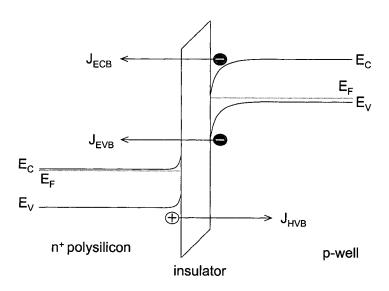

| 2.6  | The three mechanisms of gate dielectric tunneling current in an NMOS                                                  |    |

|      | transistor                                                                                                            | 40 |

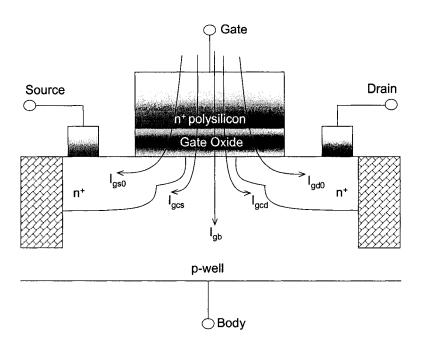

| 2.7  | Different components of gate dielectric tunneling current in a MOSFET                                                 | 41 |

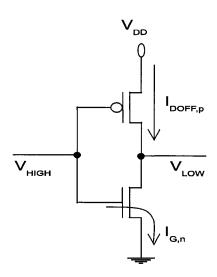

| 2.8  | Standby power dissipation current paths in a CMOS circuit                                                             | 42 |

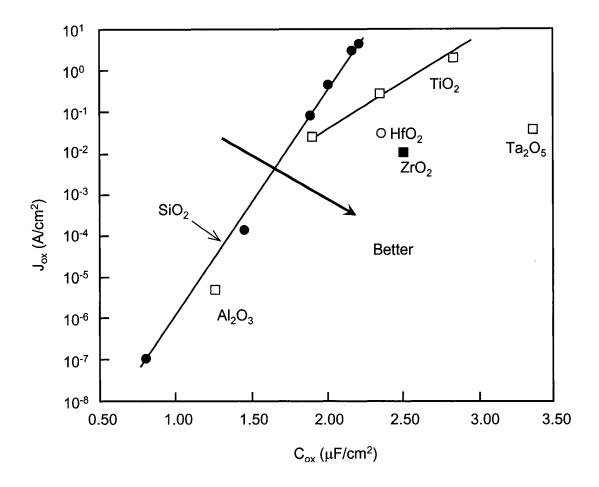

| 2.9  | Comparison of the gate oxide capacitance per unit area versus the gate                                                |    |

|      | oxide leakage current density of various insulators for Aluminum Oxide                                                |    |

|      | (Al <sub>2</sub> O <sub>3</sub> ), Hafnium Dioxide (HfO <sub>2</sub> ), Silicon Dioxide (SiO <sub>2</sub> ), Tantalum |    |

|      | Pentoxide (Ta <sub>2</sub> O <sub>5</sub> ), Titanium Dioxide (TiO <sub>2</sub> ), and Zirconium Dioxide              |    |

|      | (ZrO <sub>2</sub> )                                                                                                   | 44 |

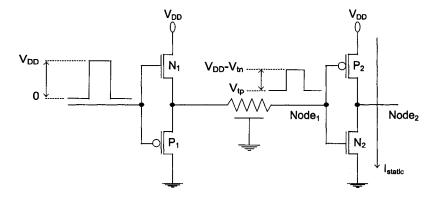

| 2.10 | Static DC current in a full voltage rail CMOS inverter driven by a low                                                |    |

|      | voltage swing signal                                                                                                  | 46 |

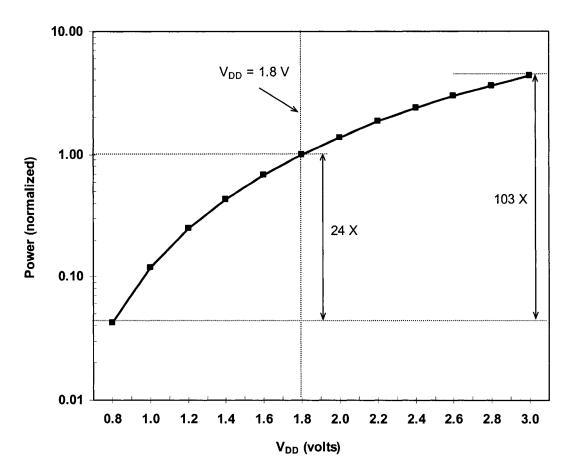

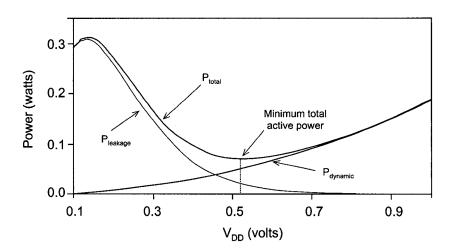

| 3.1  | Normalized power consumption versus supply voltage (V <sub>DD</sub> ) of a 19               |            |

|------|---------------------------------------------------------------------------------------------|------------|

|      | stage ring oscillator assuming a 0.18 µm CMOS technology                                    | 49         |

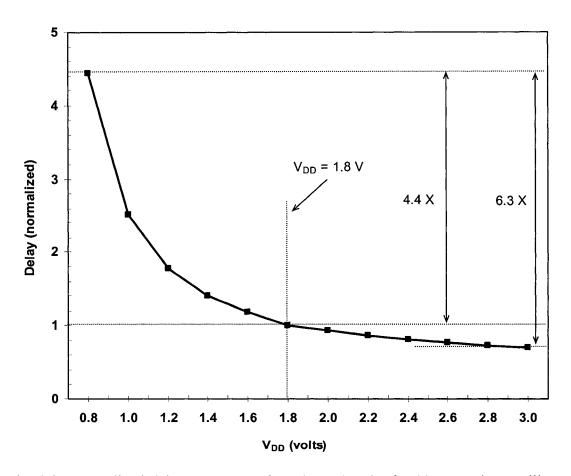

| 3.2  | Normalized delay versus supply voltage (V <sub>DD</sub> ) of a 19 stage ring                |            |

|      | oscillator for a 0.18 μm CMOS technology                                                    | 51         |

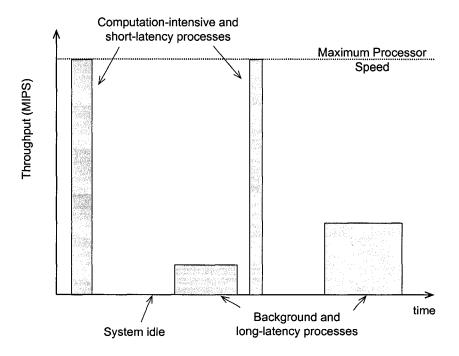

| 3.3  | Variation of the throughput required to execute certain tasks in a typical                  |            |

|      | microprocessor system                                                                       | 54         |

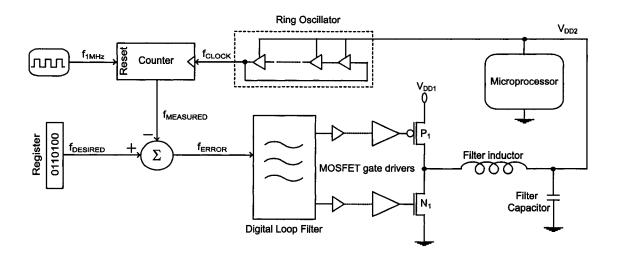

| 3.4  | Feedback loop architecture for a dynamic voltage scaling circuit                            | 56         |

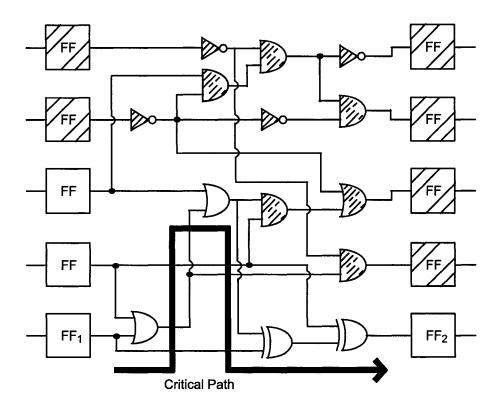

| 3.5  | A single supply voltage circuit                                                             | 58         |

| 3.6  | A dual supply voltage circuit. The gates that operate at a lower supply                     |            |

|      | voltage are shaded                                                                          | 59         |

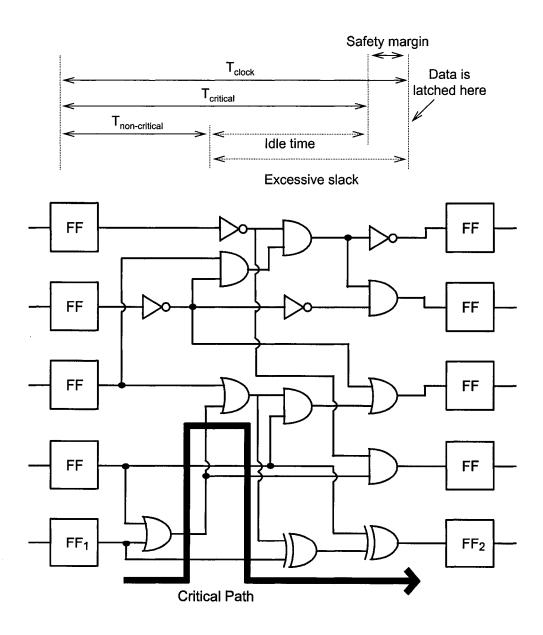

| 3.7  | A dual supply voltage circuit with the clustered voltage scaling                            |            |

|      | technique. The circuits operating at a lower supply voltage are shaded.                     |            |

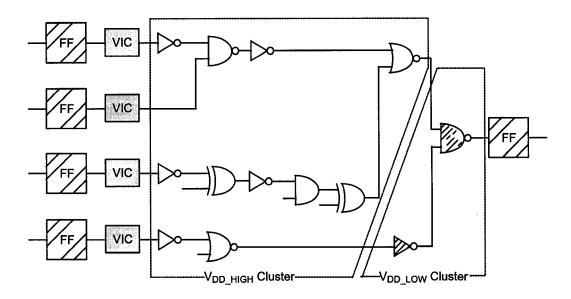

|      | VIC: voltage interface circuit                                                              | 61         |

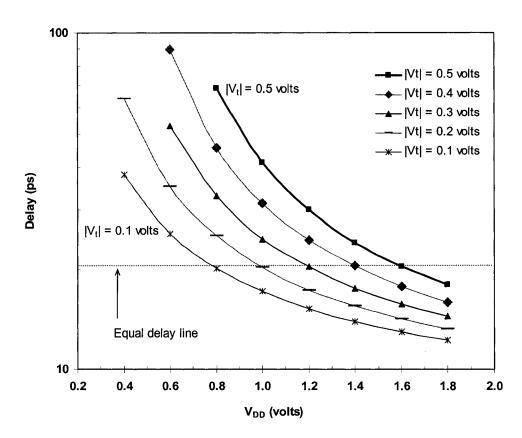

| 3.8  | Variation of the delay of a CMOS inverter with supply voltage for                           |            |

|      | different MOSFET threshold voltages assuming a 0.18 µm CMOS                                 |            |

|      | technology                                                                                  | 62         |

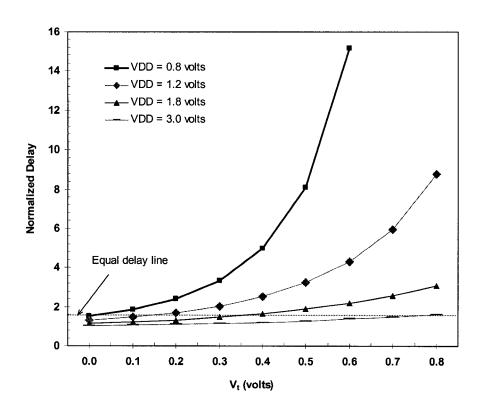

| 3.9  | Effect of threshold voltage scaling on the delay of a 19 stage ring                         |            |

|      | oscillator for four different supply voltages assuming a 0.18 µm CMOS                       |            |

|      | technology                                                                                  | 63         |

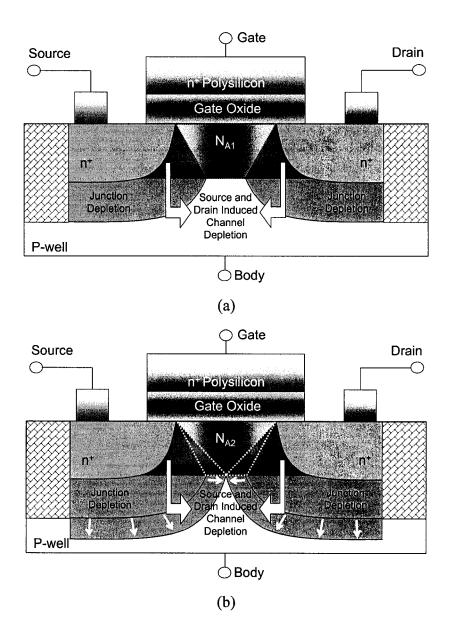

| 3.10 | Effect of threshold voltage scaling on short-channel effects in an NMOS                     |            |

|      | transistor. (a) A high-V <sub>t</sub> short-channel MOSFET. (b) A low-V <sub>t</sub> short- |            |

|      | channel MOSFET. $N_A$ : acceptor concentration in the channel area ( $N_{A2} < N_{A1}$ )    | 65         |

|      |                                                                                             | 65         |

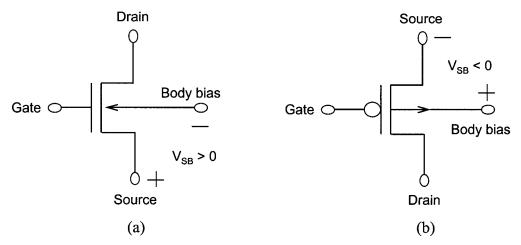

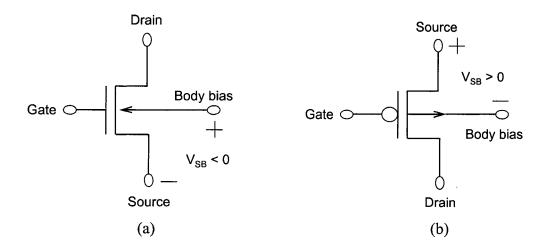

| 3.11 | Reverse body bias circuit technique. (a) A reverse body biased NMOS                         | <b>(</b> 0 |

|      | transistor. (b) A reverse body biased PMOS transistor                                       | 68         |

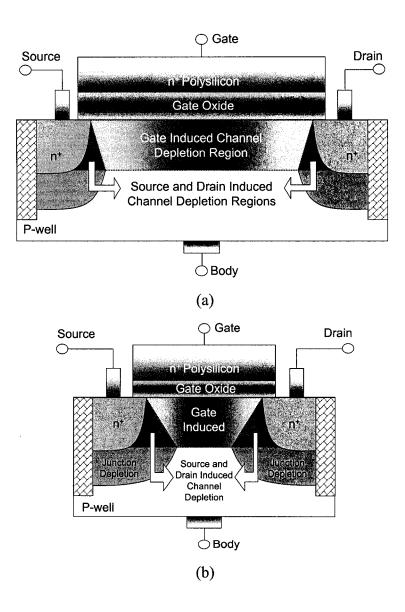

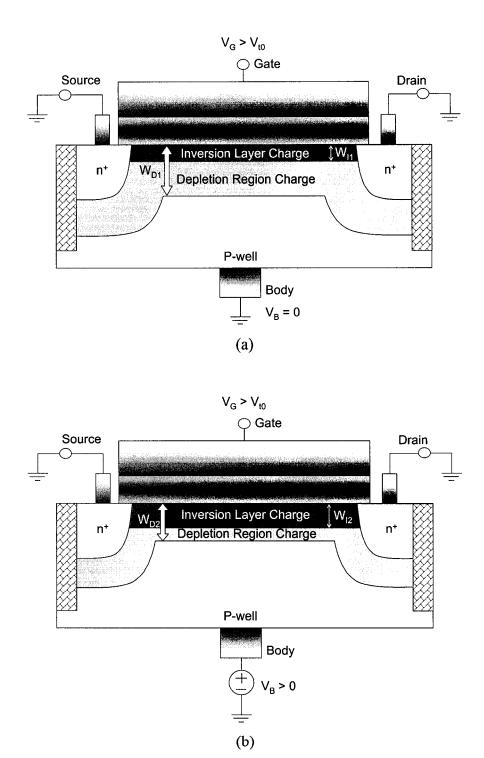

| 3.12 | Effect of reverse body bias on the depletion region and inversion layer charge in a MOSFET. (a) A zero body biased NMOS transistor. (b) A reverse body biased NMOS transistor. $W_{D1} < W_{D2}$ . $W_{I1} > W_{I2}$                                                                                                                                                    | 69 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

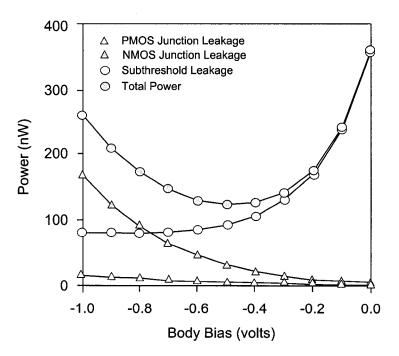

| 3.13 | Variation of the total standby power of a microprocessor test circuit as a function of reverse body bias voltage                                                                                                                                                                                                                                                        | 70 |

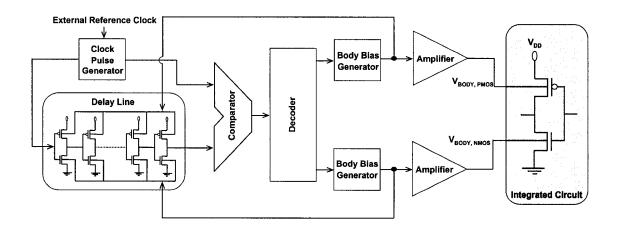

| 3.14 | Block diagram of a speed adaptive body bias circuit                                                                                                                                                                                                                                                                                                                     | 71 |

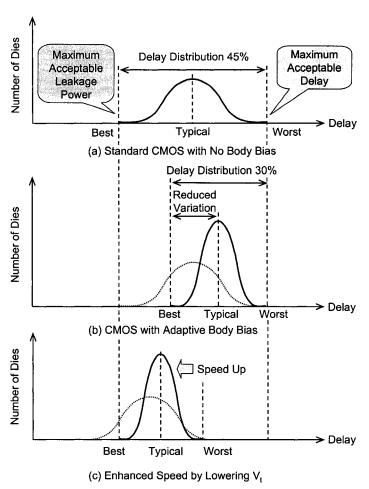

| 3.15 | Reduced die-to-die delay variations by applying the speed adaptive reverse body bias circuit technique to test circuits fabricated in a 0.25 $\mu$ m CMOS technology [73]. (a) Delay distribution of standard CMOS circuits with zero body bias. (b) Reduced delay distribution with adaptive body bias. (c) Enhanced worst case speed by further scaling the threshold |    |

|      | voltages with the adaptive body bias circuit technique                                                                                                                                                                                                                                                                                                                  | 72 |

| 3.16 | Body effect degradation due to channel length scaling. (a) A long channel MOSFET. (b) A short-channel MOSFET                                                                                                                                                                                                                                                            | 73 |

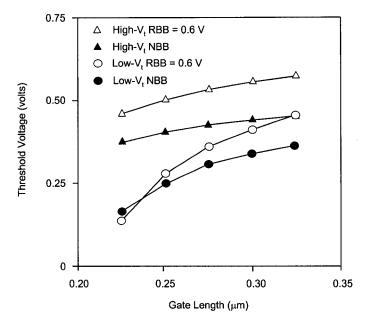

| 3.17 | Increasing short-channel effects and threshold voltage roll-off with reverse body bias (RBB) for low-V $_t$ and high-V $_t$ MOSFETs for a 0.25 $\mu$ m CMOS technology [63]. NBB: no body bias, RBB: reverse body bias                                                                                                                                                  | 75 |

| 3.18 | Effect of the reverse body bias circuit technique on drain-induced barrier lowering ( $\Delta V_t/\Delta V_{DS}$ ) for a 0.18 $\mu m$ CMOS technology. The threshold voltage ( $V_t$ ) is the gate-to-source voltage at which the drain current is equal to 1 $\mu A/\mu m$                                                                                             | 75 |

| 3.19 | Forward body bias circuit technique. (a) A forward body biased NMOS transistor. (b) A forward body biased PMOS transistor                                                                                                                                                                                                                                               | 76 |

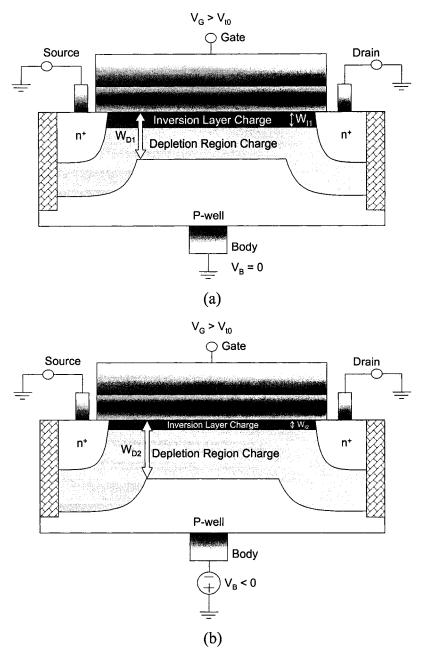

| 3.20 | Effect of forward body bias on the depletion region and inversion layer charge in a MOSFET. (a) A zero body biased NMOS transistor. (b) A                                                                                                                                                                                                                               |    |

|      | forward body biased NMOS transistor. $W_{D1} > W_{D2}$ . $W_{I1} < W_{I2}$                                                                                                                                                                                                                                                                                              | 77 |

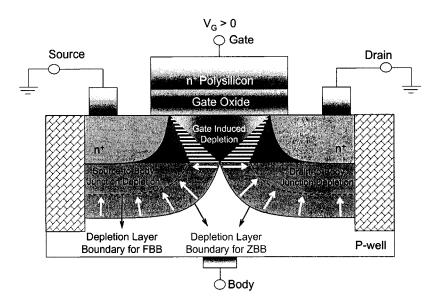

| 3.21 | Effect of forward body bias on short-channel effects in an NMOS transistor. FBB: forward body bias ( $V_{Body} > 0$ ). ZBB: zero body bias ( $V_{Body} = 0$ )                   | 79 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

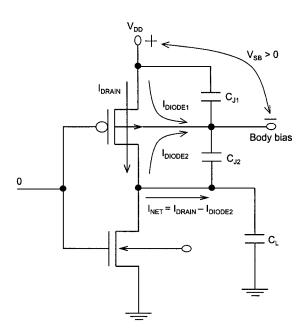

| 3.22 | Schematic representation of a forward body biased CMOS circuit.  IDIODE1: source-to-body junction diode current, IDIODE2: drain-to-body                                         | ,, |

|      | junction diode current, C <sub>J1</sub> : source-to-body junction capacitance, and C <sub>J2</sub> : drain-to-body junction capacitance                                         | 80 |

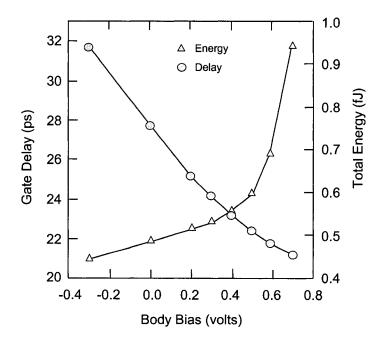

| 3.23 | Variation of the propagation delay and energy consumption of a 101 stage ring oscillator with body bias voltage based on a 0.18 µm CMOS technology                              | 81 |

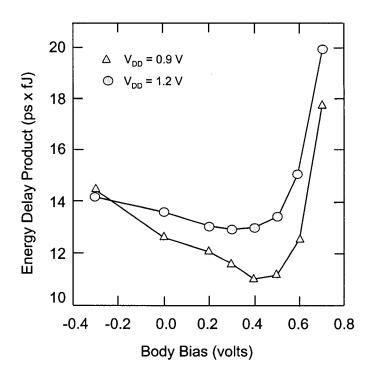

| 3.24 | Variation of the energy-delay product of a 101 stage ring oscillator with body bias voltage based on a 0.18 µm CMOS technology                                                  | 82 |

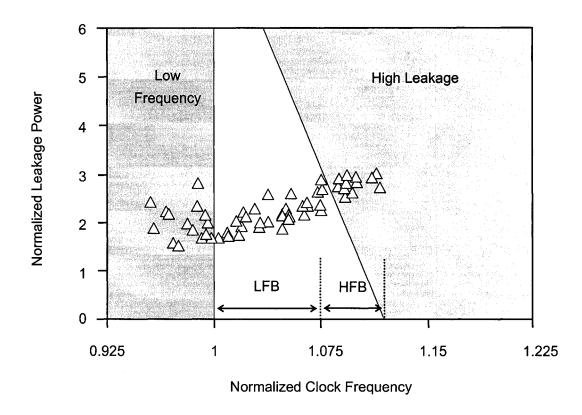

| 3.25 | Leakage power and clock frequency characteristics of microprocessor test circuits fabricated in a 0.15 μm CMOS technology (LFB: lower frequency bin, HFB: higher frequency bin) | 85 |

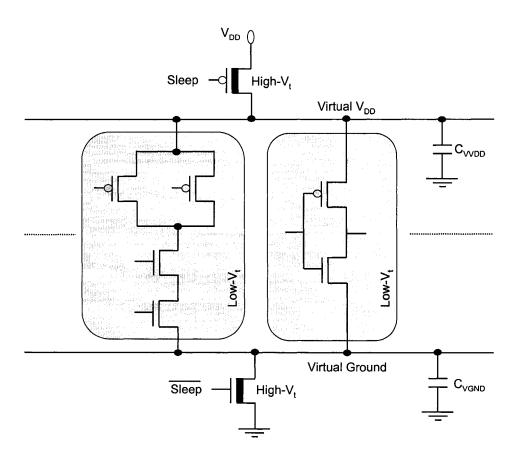

| 3.26 | A multithreshold-voltage CMOS (MTCMOS) circuit. The high threshold voltage transistors are illustrated by a bold line in the channel area                                       | 90 |

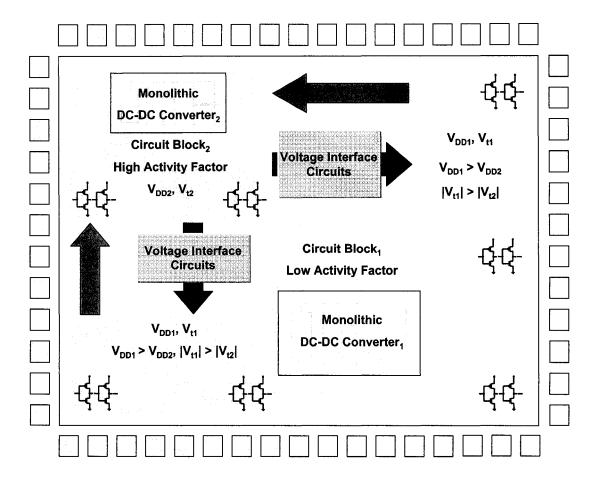

| 3.27 | A multiple supply and threshold voltage integrated circuit with voltage partitioning based on the difference of the activity factors among different circuit blocks             | 94 |

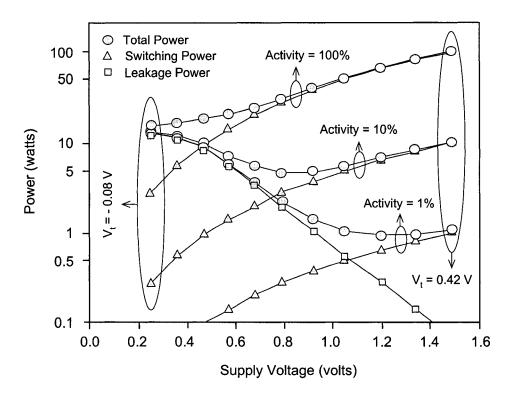

| 3.28 | Power dissipation of a test circuit with varying supply voltage for three different activity factors assuming a 2 GHz clock frequency and a 100 nm CMOS technology              | 95 |

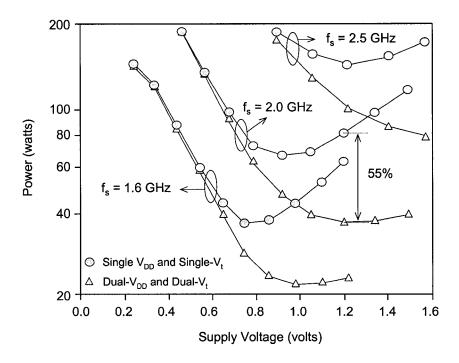

| 3.29 | Power dissipation of dual- $V_{DD}$ /dual- $V_t$ and standard single- $V_{DD}$ /single- $V_t$        |     |

|------|------------------------------------------------------------------------------------------------------|-----|

|      | test circuits with varying supply voltage for three different clock                                  |     |

|      | frequencies, assuming a 100 nm CMOS technology. For a dual- $V_{\text{DD}}$ /dual-                   |     |

|      | $V_t$ circuit, $V_{DD2}$ and $\left V_{t2}\right $ are fixed at 0.5 volts and 0 volts, respectively. |     |

|      | The supply voltage of the low activity circuits $(V_{DD1})$ is varied together                       |     |

|      | with the threshold voltages ( $ V_{t1} $ ) while maintaining a target clock                          |     |

|      | frequency                                                                                            | 96  |

| 3.30 | Active mode power dissipation of a CMOS circuit with varying supply                                  |     |

|      | voltage for a fixed operating frequency. The threshold voltages are                                  |     |

|      | modified together with the supply voltage to maintain a constant                                     |     |

|      | frequency                                                                                            | 98  |

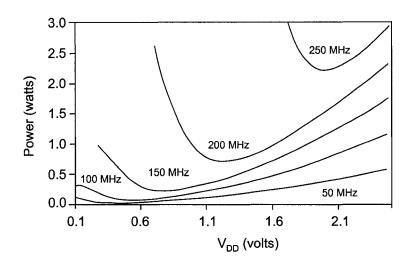

| 3.31 | Active power with varying supply voltage for various clock frequencies.                              |     |

|      | With each curve, the threshold voltages are modified together with the                               |     |

|      | supply voltage to maintain a constant frequency                                                      | 99  |

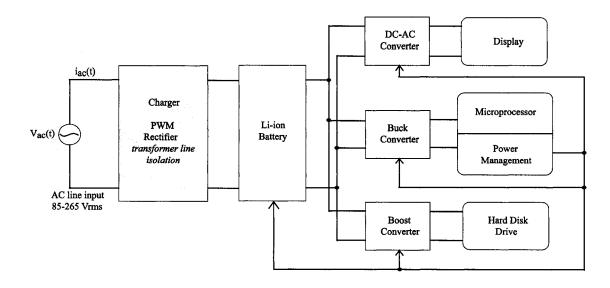

| 4.1  | Power supply system for a laptop computer                                                            | 104 |

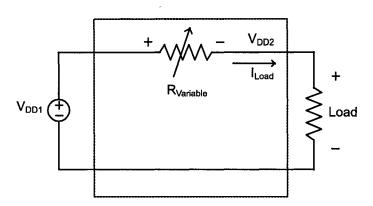

| 4.2  | A simple voltage divider circuit describing the operating principle of a                             |     |

|      | linear DC-DC converter                                                                               | 106 |

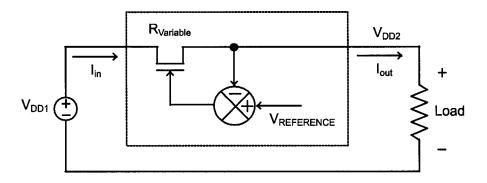

| 4.3  | A linear voltage regulator                                                                           | 107 |

| 4.4  | A high current-efficiency linear regulator                                                           | 109 |

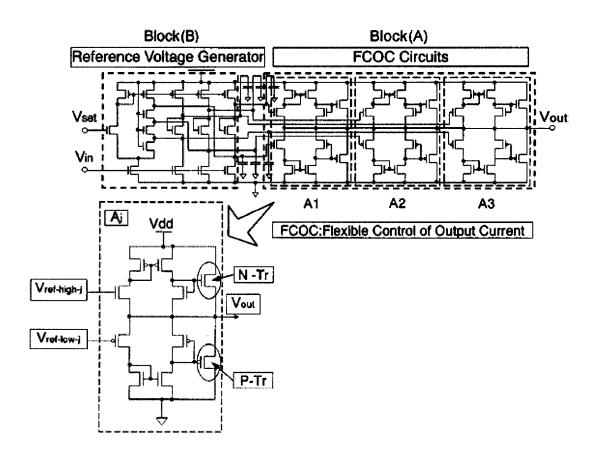

| 4.5  | Diagram representing the operation of the flexible control of the output                             |     |

|      | current (FCOC) technique proposed in [106]                                                           | 110 |

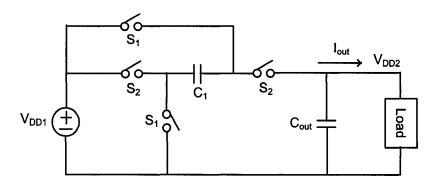

| 4.6  | Schematic representation of a switched-capacitor DC-DC converter                                     | 111 |

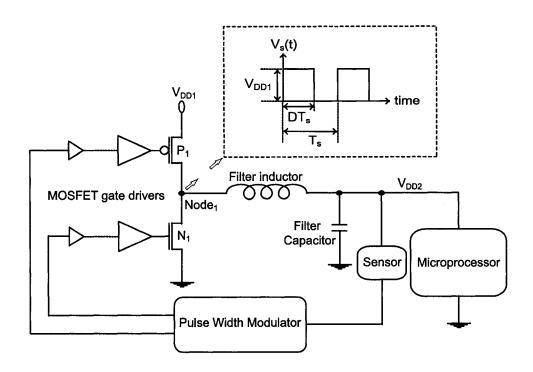

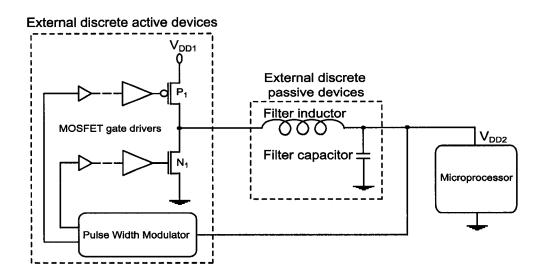

| 4.7  | Buck converter circuit                                                                               | 114 |

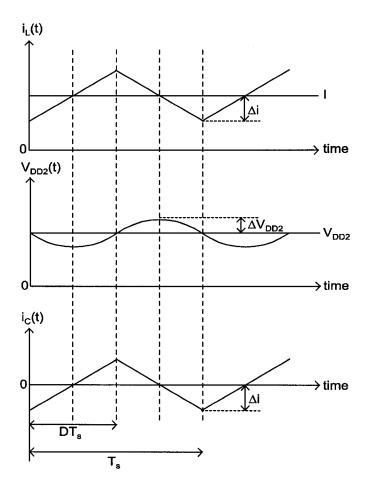

| 4.8  | Inductor current $i_L(t)$ , output voltage $V_{DD2}(t)$ , and capacitor current $i_C(t)$             |     |

|      | waveforms                                                                                            | 116 |

| 5.1  | Circuit model of the parasitic impedances of a buck converter                                        | 125 |

| 5.2 | Total power consumption of a buck converter as a function of $f_s$ and $\Delta i$                                                                                                                                                                                                                                 | 132 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3 | Efficiency of a buck converter as a function of $f_s$ and $\Delta i$                                                                                                                                                                                                                                              | 133 |

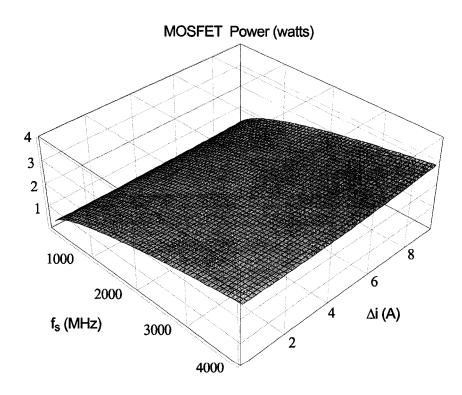

| 5.4 | Variation of the total MOSFET related optimized power (including the power dissipated in the gate driver buffers of the power MOSFETs) with the switching frequency and inductor current ripple                                                                                                                   | 134 |

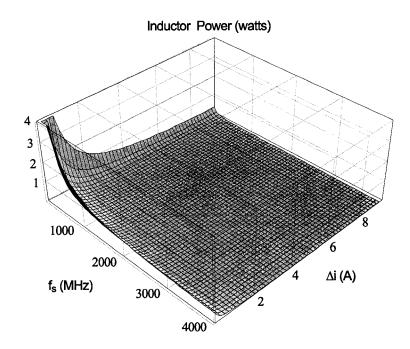

| 5.5 | Variation of the total power dissipated in the filter inductor with the switching frequency and inductor current ripple                                                                                                                                                                                           | 135 |

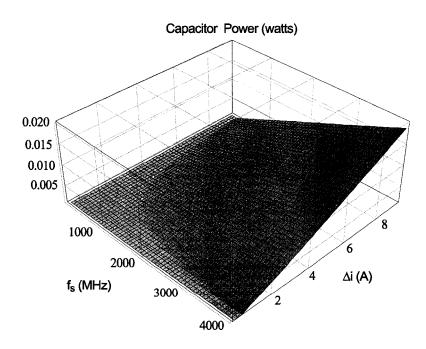

| 5.6 | Variation of the total power dissipated in the filter capacitor with the switching frequency and inductor current ripple                                                                                                                                                                                          | 135 |

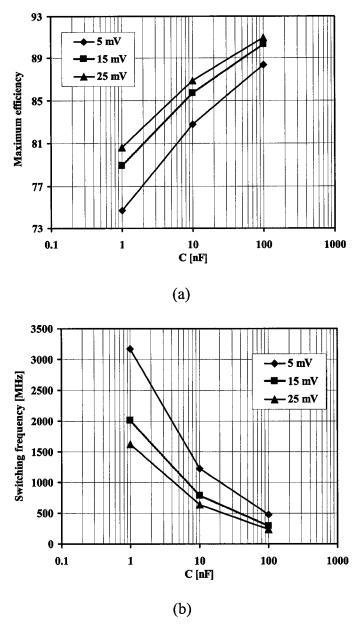

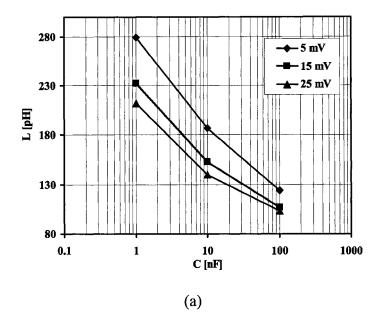

| 5.7 | Variation of maximum efficiency and switching frequency of a buck converter with filter capacitance $C$ (1 nF < $C$ < 100 nF) and output voltage ripple $\Delta V_{DD2}$ (5 mV < $\Delta V_{DD2}$ < 25 mV). (a) Maximum efficiency. (b) Switching frequency                                                       | 138 |

| 5.8 | Variation of filter inductance and MOSFET and inductor related power components of a buck converter with filter capacitance $C$ (1 nF < $C$ < 100 nF) and output voltage ripple $\Delta V_{DD2}$ (5 mV < $\Delta V_{DD2}$ < 25 mV). (a) Filter inductance. (b) Total MOSFET and inductor related power components | 139 |

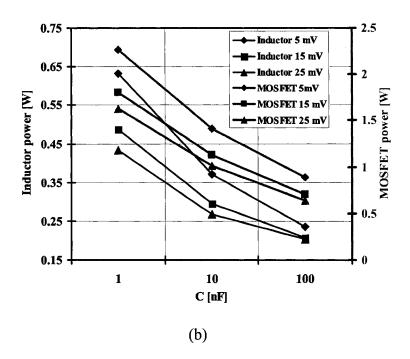

| 5.9 | Simulation waveforms of a buck converter for $C = 100$ nF. (a) Output voltage ripple $V_{ripple}(t)$ . (b) Output response of a buck converter to a change in load current from $I_{min}$ to $I$ . (c) Output response of a buck converter to a step current changing between $I_{min}$ and $I$                   | 141 |

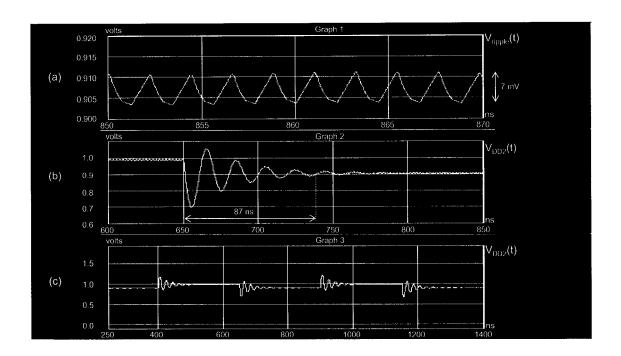

| 6.1 | Parasitic impedances and transistor geometric sizes of a buck converter                                                                                                                                                                                                                                           | 146 |

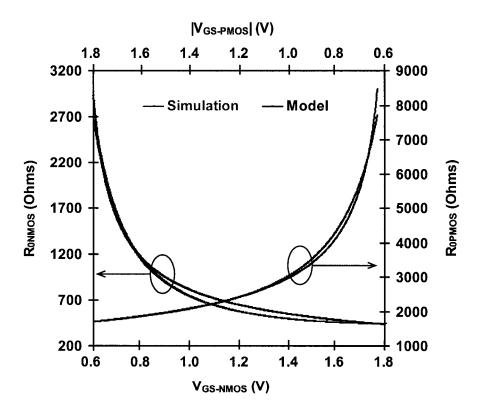

| 6.2 | Variation of the effective series resistance of 1 $\mu m$ wide NMOS and PMOS transistors with gate-to-source voltage, $V_{GS}$ ( $ V_{DS} $ = 0.1 volts)                                                                                                                                                          | 151 |

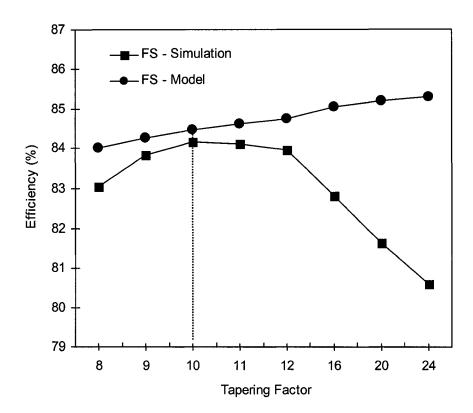

| 6.3 | The maximum efficiency attainable with a full swing (FS) buck converter circuit for different tapering factors                                                                                                                                                                                                    | 154 |

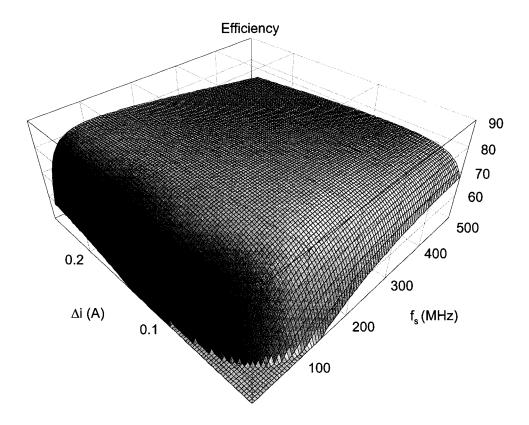

| 6.4 | Efficiency of a full swing buck converter as a function of the switching                           |     |

|-----|----------------------------------------------------------------------------------------------------|-----|

|     | frequency $(f_s)$ and inductor current ripple $(\Delta i)$                                         | 155 |

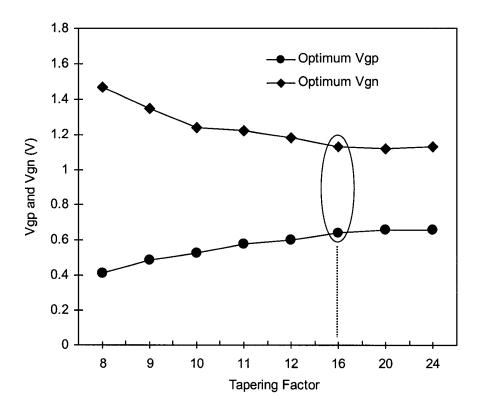

| 6.5 | Optimum power supply voltage of the power NMOS drivers ( $V_{gn}$ ) and                            |     |

|     | optimum ground voltage of the power PMOS drivers $(V_{gp})$ that maximize                          |     |

|     | the efficiency for different tapering factors                                                      | 156 |

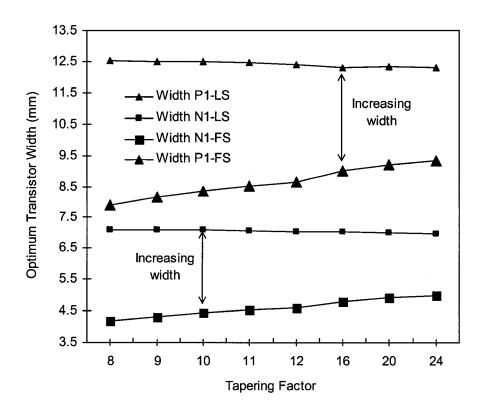

| 6.6 | A comparison of the optimum widths of the power PMOS and NMOS                                      |     |

|     | transistors that maximize the efficiency of the full swing (FS) and the low                        |     |

|     | swing (LS) buck converters for different tapering factors                                          | 157 |

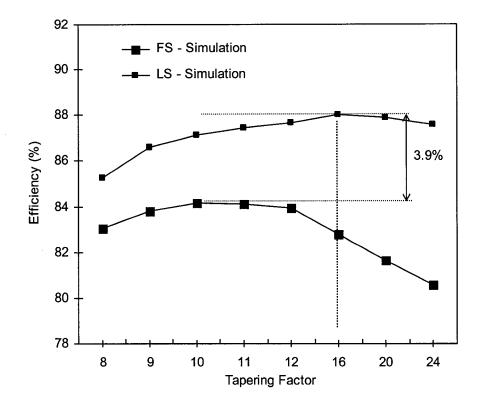

| 6.7 | A comparison of the maximum efficiency attainable with the low swing                               |     |

|     | (LS) and the full swing (FS) buck converter circuits for different tapering                        |     |

|     | factors                                                                                            | 158 |

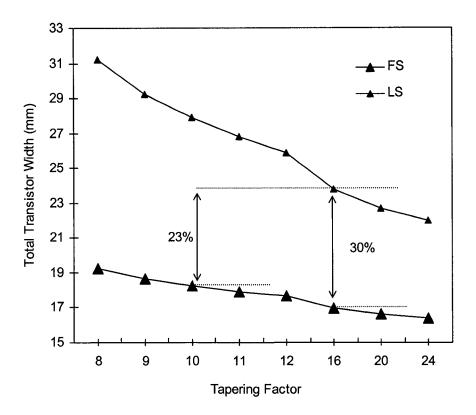

| 6.8 | A comparison of the total transistor width (including the widths of the                            |     |

|     | transistors within the gate drivers) of the low swing (LS) and the full                            |     |

|     | swing (FS) buck converter circuits with the highest efficiency                                     |     |

|     | characteristics for different tapering factors                                                     | 160 |

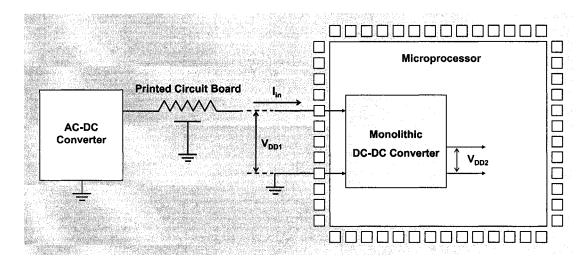

| 7.1 | High voltage off-chip power delivery and on-chip DC-DC conversion                                  | 163 |

| 7.2 | Input voltage constraint in an off-chip buck converter circuit ( $V_{DD1} \le$                     |     |

|     | V <sub>max</sub> )                                                                                 | 164 |

| 7.3 | Cascode bridge circuit operating at an input supply voltage of $V_{DD1}$ =                         |     |

|     | $3V_{max}$ ( $V_{DD3} = 2V_{max}$ and $V_{DD4} = V_{max}$ )                                        | 166 |

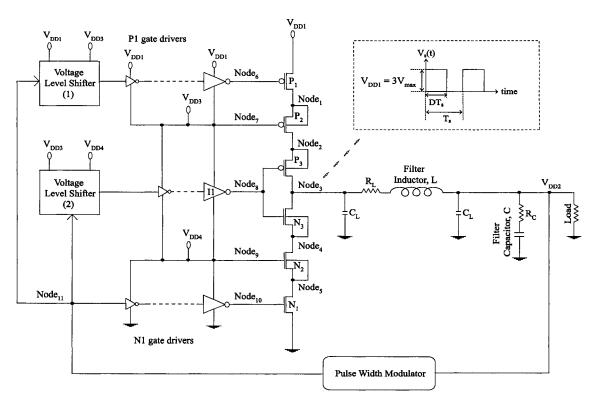

| 7.4 | Proposed DC-DC converter circuit operating at an input supply voltage of                           |     |

|     | $V_{DD1} = 3V_{max} (V_{DD3} = 2V_{max}, V_{DD4} = V_{max}, \text{ and } V_{DD2} < V_{DD1}) \dots$ | 167 |

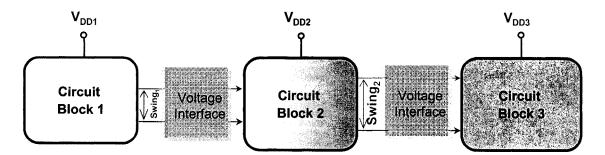

| 8.1 | Signal transfer between circuit blocks in a multiple supply voltage                                |     |

|     | integrated circuit                                                                                 | 172 |

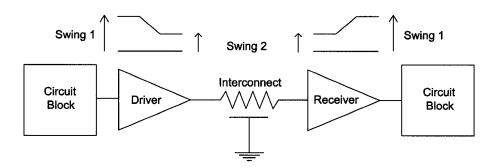

| 8.2 | Circuit architecture for low swing interconnect                                                    | 173 |

| 8.3 | The proposed voltage interface circuit                                                             | 175 |

| 8.4 | Average delay versus load capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 177 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.5 | Average power versus load capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 177 |

| 8.6 | Power efficiency versus load capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 178 |

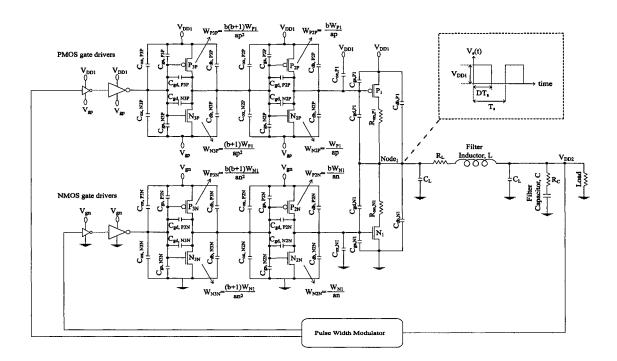

| 8.7 | Microphotograph of the interface circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 180 |

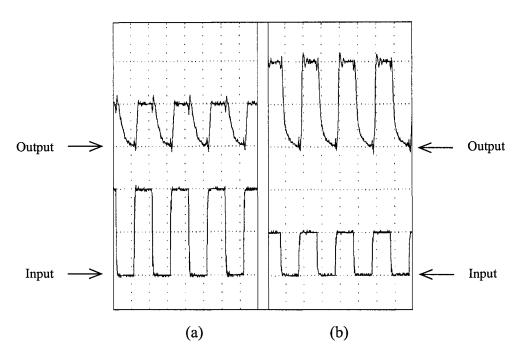

| 8.8 | Experimentally derived input and output voltage waveforms of the proposed voltage interface circuit. (a) 10 V → 5 V interface. (b) 5 V → 10 V interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 181 |

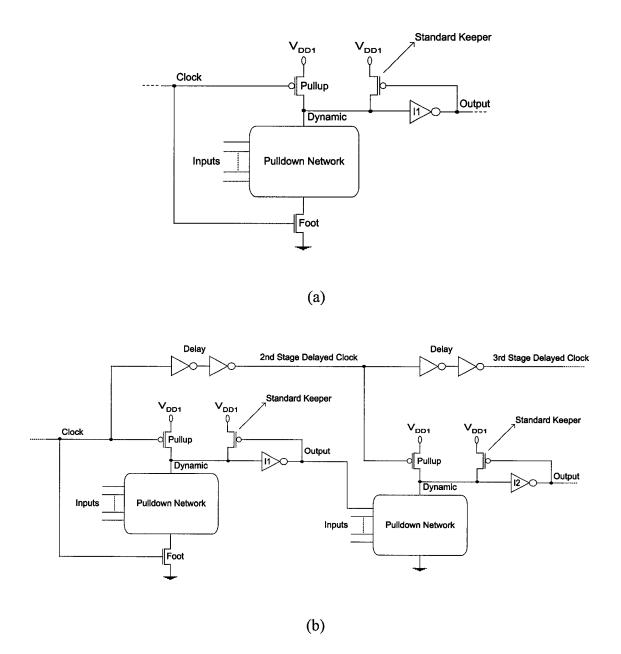

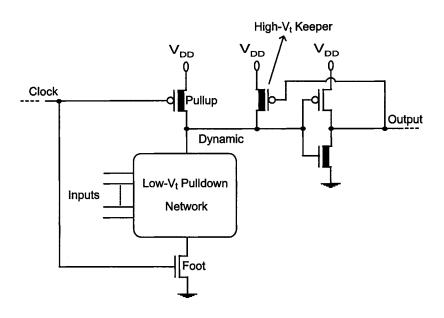

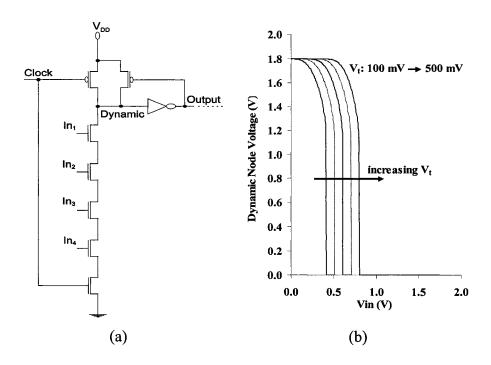

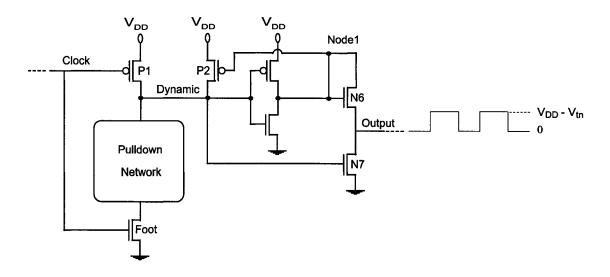

| 9.1 | Domino gates with standard keeper transistors. (a) Standard footed domino gate. (b) Standard clock-delayed footless domino logic circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 186 |

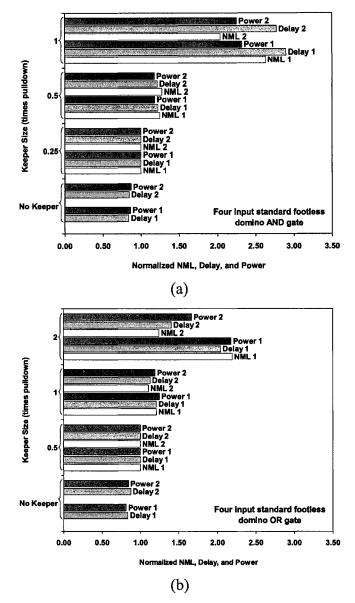

| 9.2 | Comparison of the normalized noise immunity, evaluation delay, and power characteristics of standard footless domino logic circuits with different keeper sizes. (a) Effect of the increased keeper size on the circuit characteristics of a four input domino AND gate. (b) Effect of the increased keeper size on the circuit characteristics of a four input domino OR gate. NML 1, Delay 1, and Power 1: only one input is excited while the other inputs are either grounded (for the OR gates) or connected to $V_{DD}$ (for the AND gates). NML 2, Delay 2, and Power 2: All four inputs are excited with the same input or noise signal | 189 |

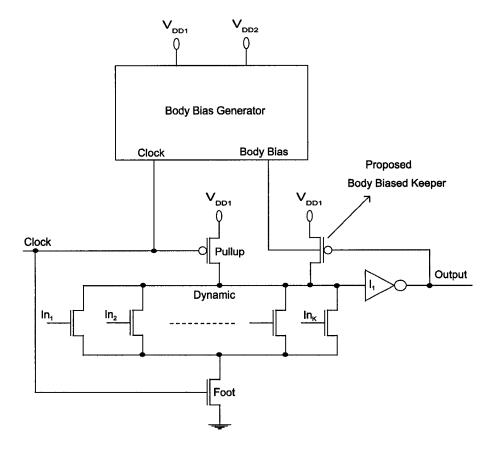

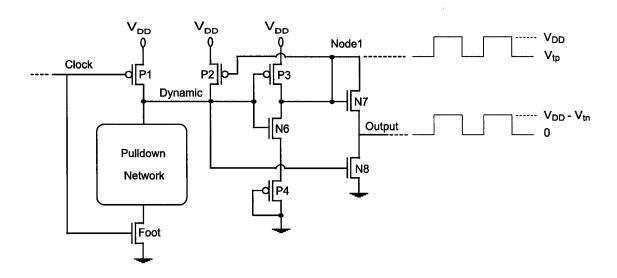

| 9.3 | A k input domino OR gate with a variable threshold voltage keeper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 193 |

| 9.4 | Waveforms that characterize the operation of the variable threshold voltage keeper circuit technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 194 |

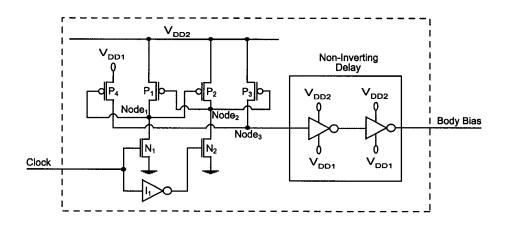

| 9.5 | Body bias generator circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 194 |

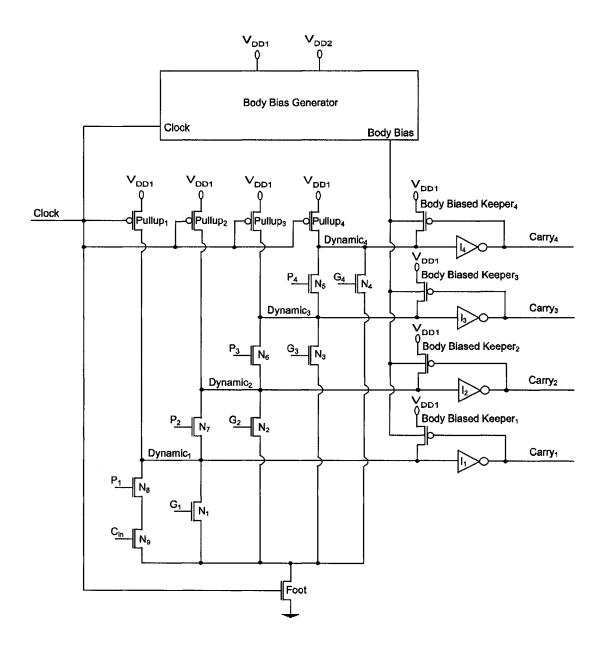

| 9.6 | A four-bit multiple-output domino carry generator of a carry lookahead adder implemented with the variable threshold voltage keeper circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107 |

|     | technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 197 |

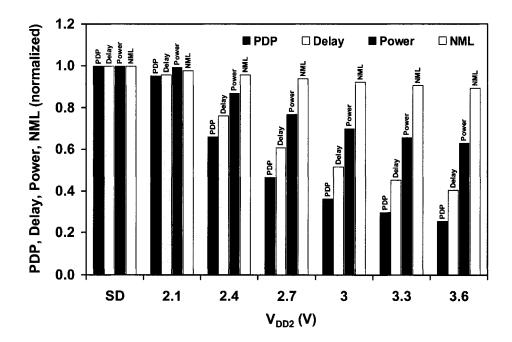

| 9.7  | Variation of the power-delay product (PDP), delay, power, and noise             |     |

|------|---------------------------------------------------------------------------------|-----|

|      | margin low (NML) characteristics of CG-DVTVK with V <sub>DD2</sub> . Values are |     |

|      | normalized to those of a standard domino (SD) carry generator circuit           |     |

|      | with the same size transistors (KPR = 2.2)                                      | 198 |

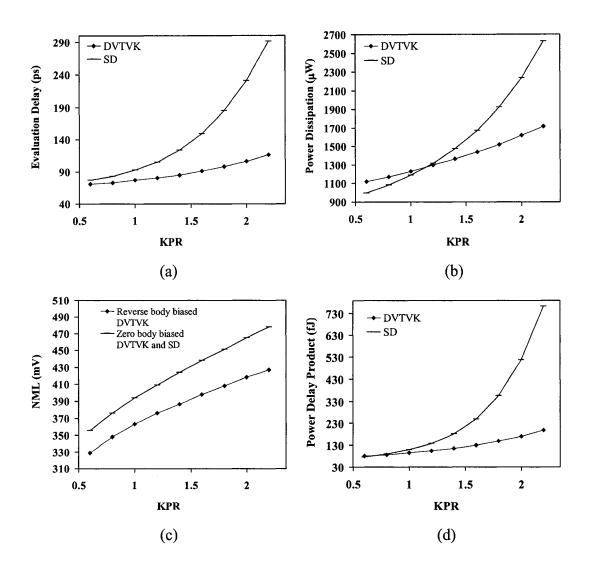

| 9.8  | SD and DVTVK simulation results for different keeper to critical path           |     |

|      | equivalent transistor width ratios (KPR). (a) Evaluation delay versus           |     |

|      | KPR. (b) Power dissipation versus KPR. (c) Noise margin versus KPR.             |     |

|      | (d) Power delay product versus KPR                                              | 200 |

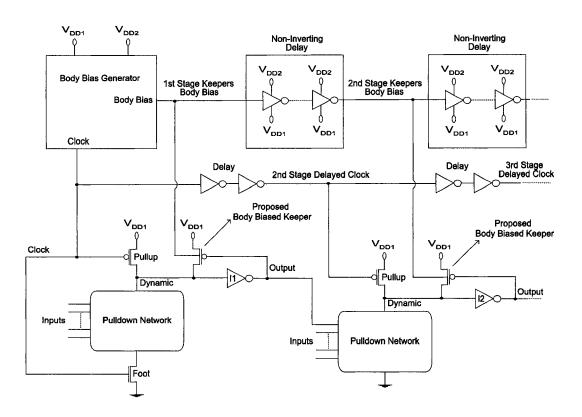

| 9.9  | Clock delayed domino logic with the variable threshold voltage keeper           |     |

|      | circuit technique                                                               | 205 |

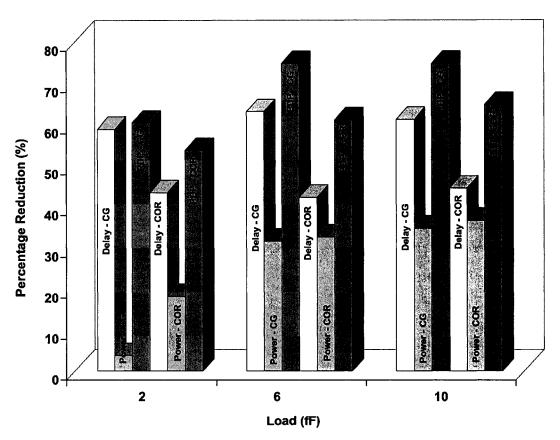

| 9.10 | Variation of the delay, power, and PDP savings of the CG-DVTVK and              |     |

|      | COR-DVTVK circuits with the output load capacitance as compared to              |     |

|      | CG-SD and COR-SD, respectively (KPR = 2.2)                                      | 209 |

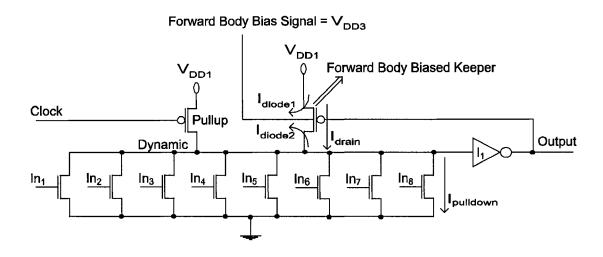

| 9.11 | An eight-input footless domino OR gate with forward body biased keeper          | 211 |

| 9.12 | Variation of COR-DVTVK noise margins with the forward body bias for             |     |

|      | KPR = 1 and $KPR = 2.2$ . The noise margins are normalized to the zero          |     |

|      | body biased keeper condition. NML-ONE: noise couples to one input               |     |

|      | while all of the other inputs are grounded. NML-ALL: noise couples to           |     |

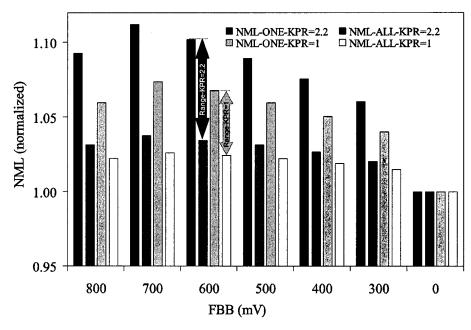

|      | all of the inputs                                                               | 213 |

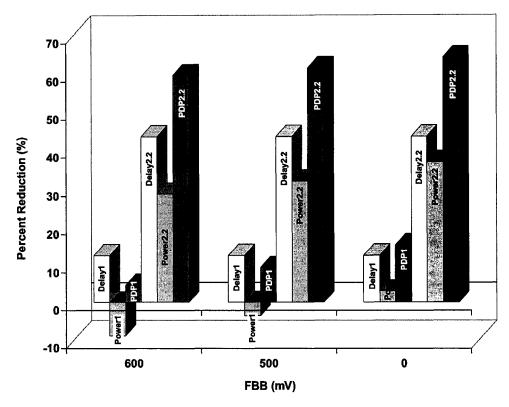

| 9.13 | Variation of the savings in delay, power, and PDP of COR-DVTVK as               |     |

|      | compared to COR-SD with a forward body bias applied to the keeper for           |     |

|      | two different keeper sizes. {Delay1, Power1, PDP1} → KPR = 1.                   |     |

|      | $\{Delay2.2, Power2.2, PDP2.2\} \rightarrow KPR = 2.2 \dots$                    | 214 |

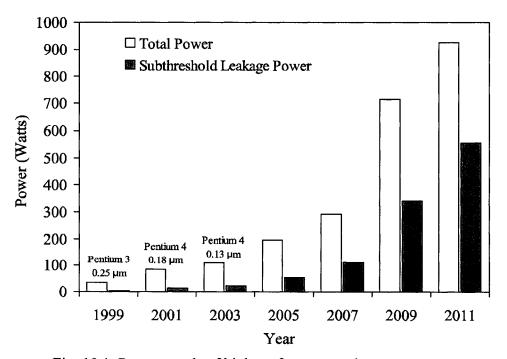

| 10.1 | Power trends of high performance microprocessors                                | 219 |

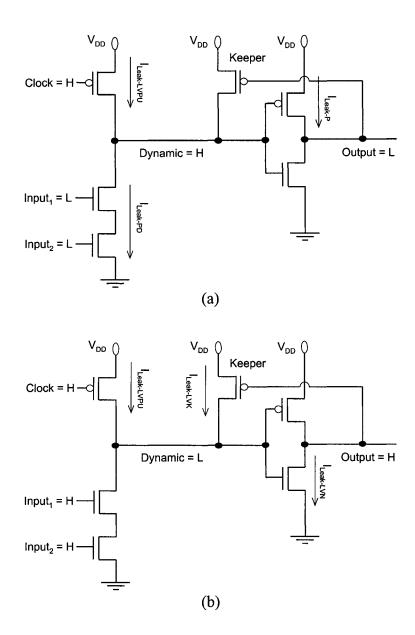

| 10.2 | A dual-V, domino logic circuit                                                  | 222 |

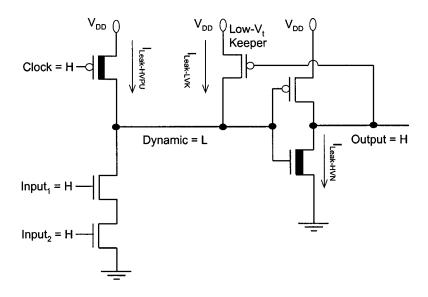

| 10.3 | Variation of the subthreshold leakage current conduction paths with the           |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | state of the dynamic and output nodes in a two input standard low- $V_{t}$        |     |

|      | domino AND gate. (a) High (H) dynamic node voltage state. (b) Low (L)             |     |

|      | dynamic node voltage state. LVK: Low-V <sub>t</sub> keeper transistor. LVPU:      |     |

|      | Low-V <sub>t</sub> pull-up transistor. LVN: Low-V <sub>t</sub> NMOS transistor    | 223 |

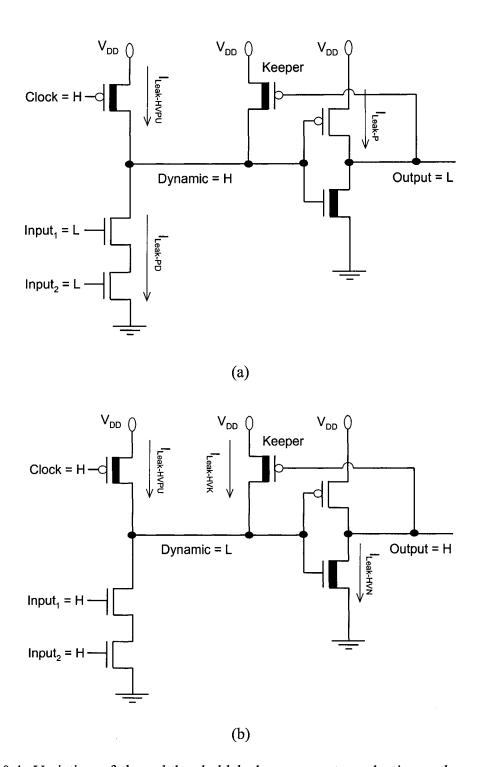

| 10.4 | Variation of the subthreshold leakage current conduction paths with the           |     |

|      | node voltages in a two input dual-V <sub>t</sub> domino AND gate. (a) High (H)    |     |

|      | dynamic node voltage. (b) Low (L) dynamic node voltage. HVK: High-                |     |

|      | $V_t$ keeper transistor. HVPU: High- $V_t$ pull-up transistor. HVN: High- $V_t$   |     |

|      | NMOS transistor                                                                   | 224 |

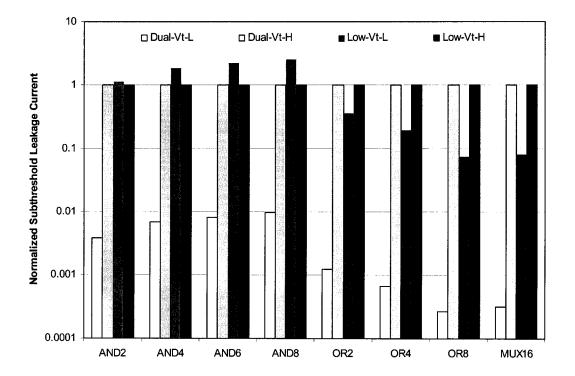

| 10.5 | Comparison of the subthreshold leakage current of low-V $_{t}$ and dual-V $_{t}$  |     |

|      | domino logic circuits for the two states of the dynamic node. The leakage         |     |

|      | current of each gate is normalized to the leakage current of the                  |     |

|      | corresponding low- $V_t$ gate with a high (H) dynamic node voltage. L: low        |     |

|      | dynamic node voltage. AND2, AND4, AND6, and AND8: 2, 4, 6, and 8                  |     |

|      | input, respectively, domino AND gates. OR2, OR4, and OR8: 2, 4, and 8             |     |

|      | input, respectively, domino OR gates. MUX16: 16-bit domino                        |     |

|      | multiplexer                                                                       | 225 |

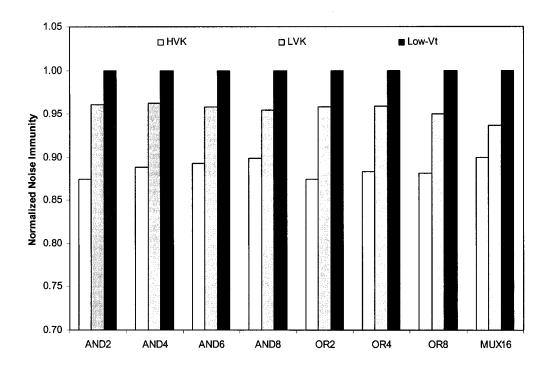

| 10.6 | Comparison of the noise immunity of low- $V_t$ and dual- $V_t$ domino logic       |     |

|      | circuits with the same size transistors. The noise margin of each gate is         |     |

|      | normalized to the noise margin of the corresponding low-V <sub>t</sub> gate. HVK: |     |

|      | high-V <sub>t</sub> keeper. LVK: low-V <sub>t</sub> keeper                        | 229 |

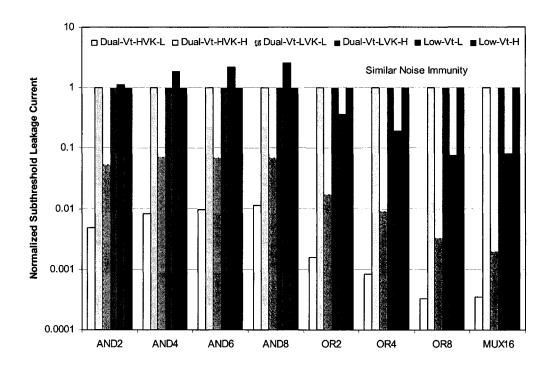

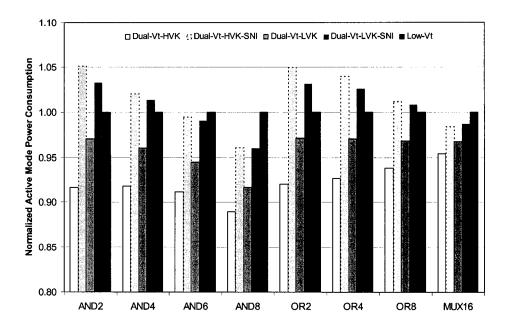

| 10.7  | Comparison of the subthreshold leakage current of low-V <sub>t</sub> and dual-V <sub>t</sub> |     |

|-------|----------------------------------------------------------------------------------------------|-----|

|       | domino logic circuits for the two states of the dynamic node (under                          |     |

|       | similar noise immunity conditions). The leakage current of each gate is                      |     |

|       | normalized to the leakage current of the corresponding low-V $_{t}$ gate with a              |     |

|       | high dynamic node voltage (H). L: low dynamic node voltage. Dual- $V_{t}$ -                  |     |

|       | HVK: dual- $V_t$ domino with high- $V_t$ keeper. Dual- $V_t$ -LVK: dual- $V_t$               |     |

|       | domino with low- $V_t$ keeper. Low- $V_t$ : standard low- $V_t$ domino circuit               | 230 |

| 10.8  | Subthreshold leakage current conduction paths for the low (L) voltage                        |     |

|       | state of the dynamic node in a dual-V $_{t}$ domino AND gate with a low-V $_{t}$             |     |

|       | keeper. LVK: Low- $V_t$ keeper transistor. HVPU: High- $V_t$ pull-up                         |     |

|       | transistor. HVN: High-V <sub>t</sub> NMOS transistor                                         | 231 |

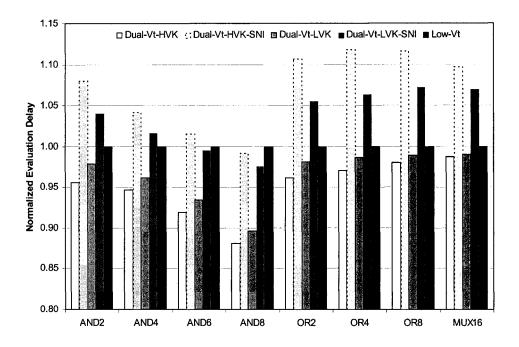

| 10.9  | Comparison of the evaluation delay of domino logic circuits. The                             |     |

|       | evaluation delay of each gate is normalized to the delay of the                              |     |

|       | corresponding low- $V_t$ gate. SNI: same noise immunity                                      | 233 |

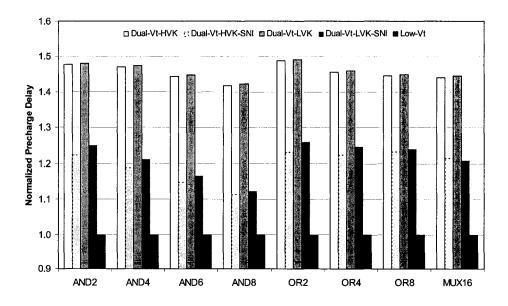

| 10.10 | Comparison of the precharge delay of domino logic circuits. The                              |     |

|       | precharge delay of each gate is normalized to the precharge delay of the                     |     |

|       | corresponding low-V $_t$ gate. SNI: same noise immunity                                      | 233 |

| 10.11 | Comparison of the power consumption of domino logic circuits during                          |     |

|       | the active mode. The power consumed by each gate is normalized to the                        |     |

|       | power consumption of the corresponding low-V <sub>t</sub> gate. SNI: same noise              |     |

|       | immunity                                                                                     | 234 |

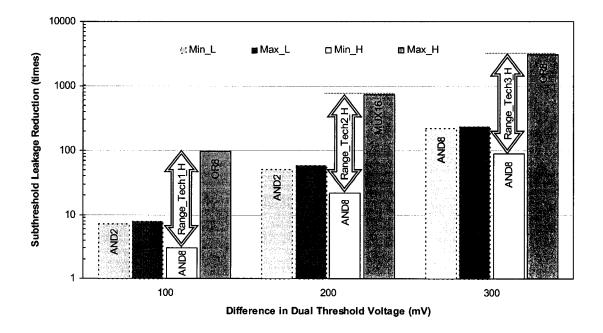

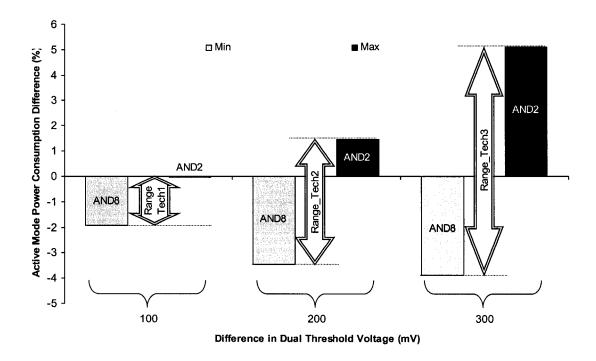

| 10.12 | The range of savings in subthreshold leakage current provided by the                     |     |

|-------|------------------------------------------------------------------------------------------|-----|

|       | dual-V <sub>t</sub> domino logic circuit technique as compared to the standard low-      |     |

|       | V <sub>t</sub> domino logic circuit technique for three different sets of dual threshold |     |

|       | voltages. Min_L and Max_L: minimum and maximum, respectively, of                         |     |

|       | the reduction in subthreshold leakage current as compared to the low- $V_t$              |     |

|       | domino logic circuits at a low dynamic node voltage state. Min_H and                     |     |

|       | Max_H: minimum and maximum, respectively, of the reduction in                            |     |

|       | subthreshold leakage current as compared to the low- $V_t$ domino logic                  |     |

|       | circuits at a high dynamic node voltage state                                            | 236 |

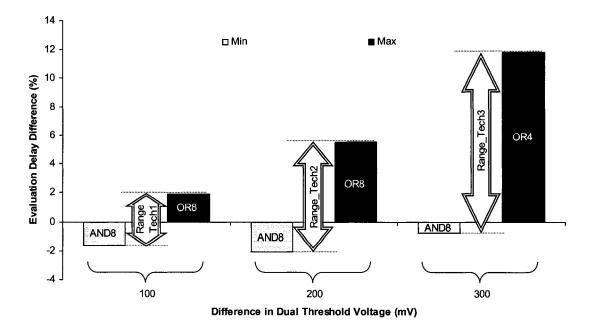

| 10.13 | The range of difference in evaluation delay of the dual-V <sub>t</sub> circuits as       |     |

|       | compared to the low- $V_t$ domino logic circuits for three different sets of             |     |

|       | dual threshold voltages. A negative difference indicates a smaller                       |     |

|       | evaluation delay as compared to a low- $V_t$ circuit. Min: minimum                       |     |

|       | difference in evaluation delay as compared to the low-V $_{t}$ domino logic              |     |

|       | circuits. Max: maximum difference in evaluation delay as compared to                     |     |

|       | the low-V <sub>t</sub> domino logic circuits                                             | 237 |

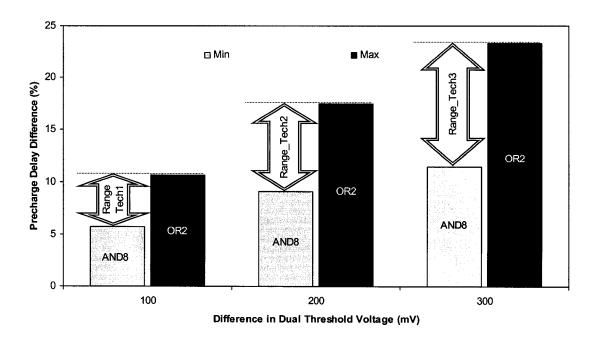

| 10.14 | The range of difference in precharge delay between the dual- $V_t$ and low-              |     |

|       | $V_{t}$ domino logic circuits for three different sets of dual threshold                 |     |

|       | voltages. Min: minimum difference in precharge delay as compared to                      |     |

|       | $low-V_t$ domino logic circuits. Max: maximum difference in precharge                    |     |

|       | delay as compared to low- $V_t$ domino logic circuits                                    | 238 |

| 10.15 | The range of difference in the power consumption (during the active                      |     |

|       | mode) of the dual- $V_t$ and low- $V_t$ domino logic circuits for three different        |     |

|       | sets of dual threshold voltages. A negative difference indicates smaller                 |     |

|       | power consumption as compared to a low-V $_{t}$ circuit. Min: minimum                    |     |

|       | difference in power consumption as compared to low- $V_t$ domino logic                   |     |

|       | circuits. Max: maximum difference in power consumption as compared                       |     |

|       | to low- $V_t$ domino logic circuits                                                      | 239 |

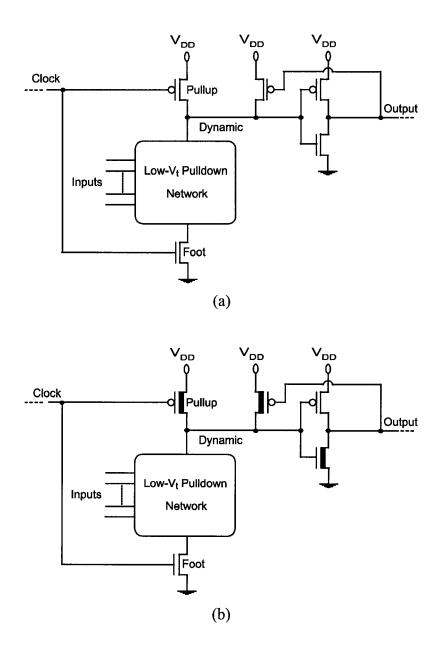

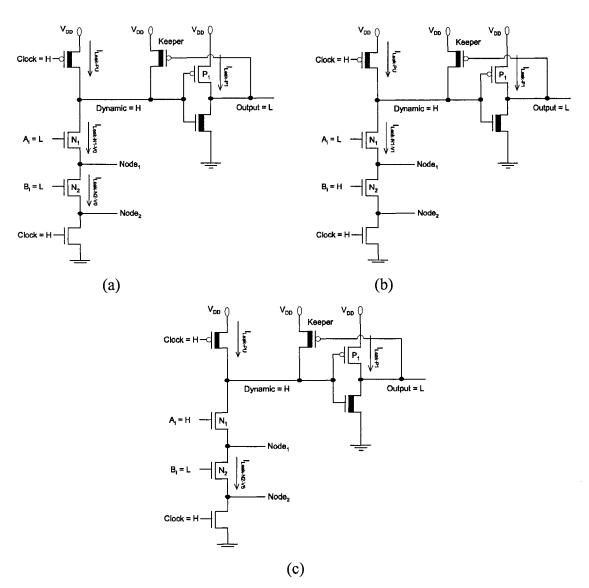

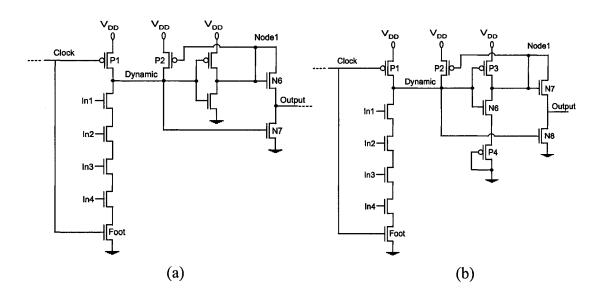

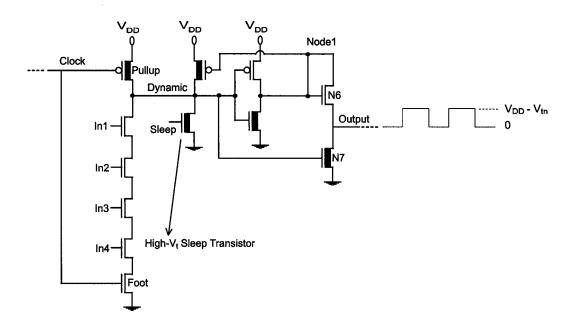

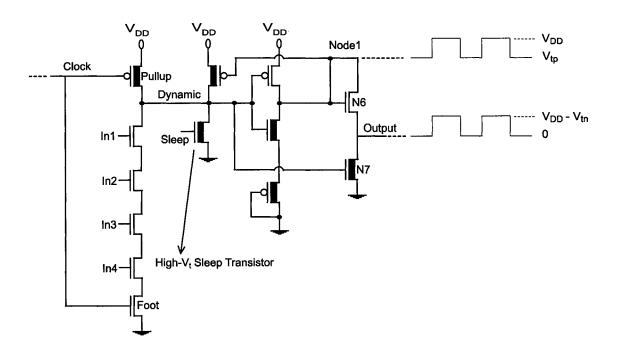

| 11.1 | Standard domino logic circuits. (a) Standard low-V <sub>t</sub> domino logic circuit. (b) Standard dual-V <sub>t</sub> domino logic circuit. High-V <sub>t</sub> transistors are symbolically represented by a thick line in the channel region                                                                                                                                                      | 243 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

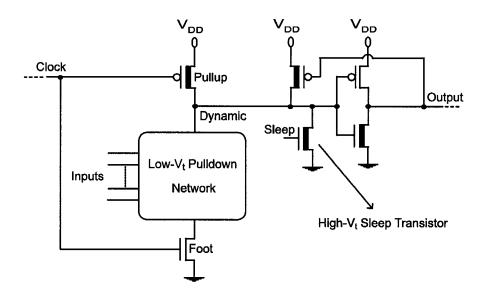

| 11.2 | Sleep switch dual- $V_t$ domino logic circuit technique. High- $V_t$ transistors are symbolically represented by a thick line in the channel region                                                                                                                                                                                                                                                  | 246 |

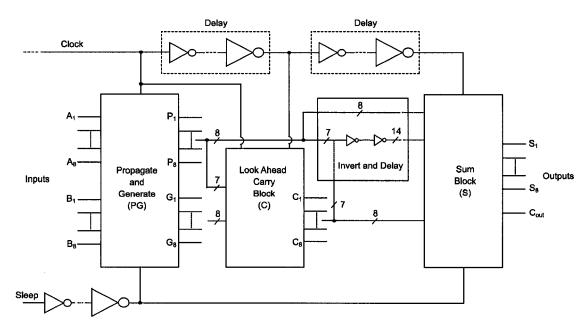

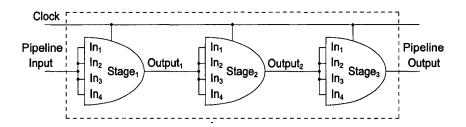

| 11.3 | Block diagram of a clock-delayed domino carry lookahead adder with the sleep switch dual-V <sub>t</sub> circuit technique                                                                                                                                                                                                                                                                            | 248 |

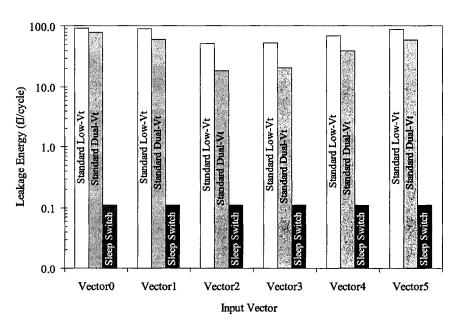

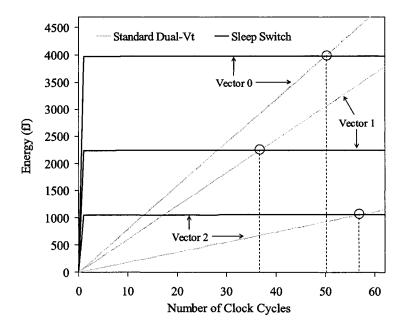

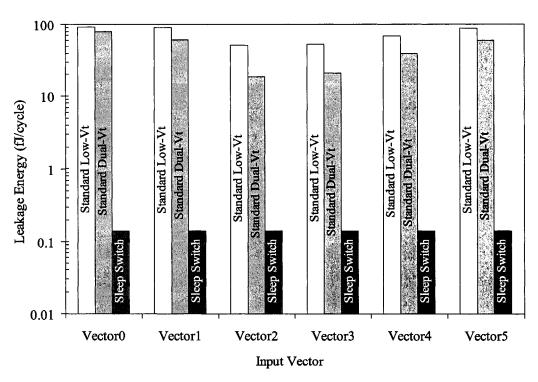

| 11.4 | A comparison of the leakage energy (per clock cycle) of the adder circuits with the low- $V_t$ , standard dual- $V_t$ , and sleep switch circuit techniques for six different input vectors                                                                                                                                                                                                          | 250 |

| 11.5 | Variation of subthreshold leakage current conduction paths with input vector for a high voltage state at the dynamic node in a standard dual-V <sub>t</sub> domino logic circuit. (a) Sources of subthreshold leakage current for V <sub>0</sub> . (b) Sources of subthreshold leakage current for V <sub>1</sub> . (c) Sources of subthreshold leakage current for V <sub>5</sub> . H: high. L: low | 252 |

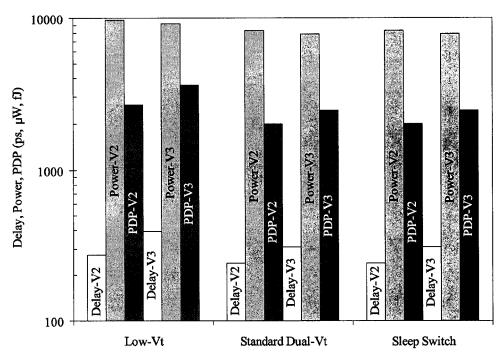

| 11.6 | A comparison of the delay, power, and power delay product (PDP) of adder circuits with low- $V_t$ , standard dual- $V_t$ , and sleep switch circuit techniques for the input vectors $V_2$ and $V_3$                                                                                                                                                                                                 |     |

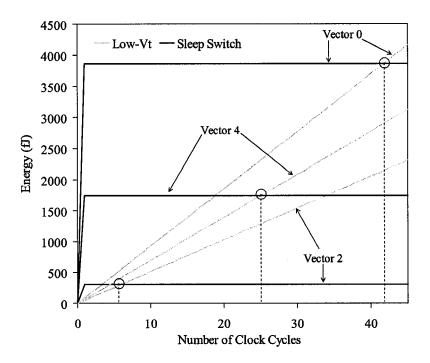

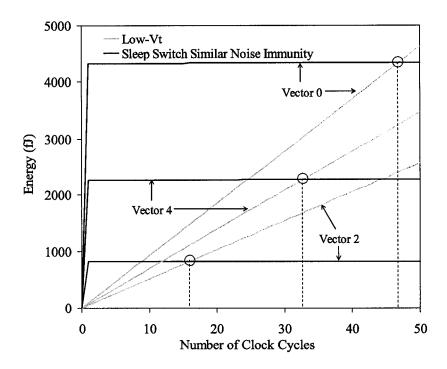

| 11.7 | Cumulative standby energy dissipation of the low-Vt and sleep switch adders for three different input vectors                                                                                                                                                                                                                                                                                        | 258 |

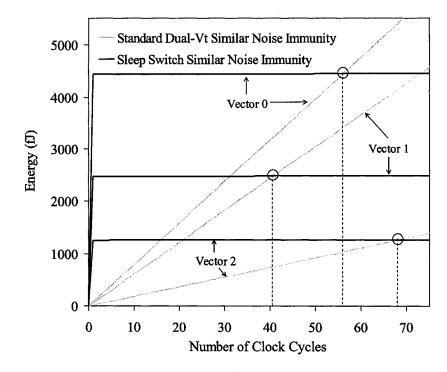

| 11.8 | Cumulative standby energy dissipation of the sleep switch and standard dual- $V_t$ adders for three different input vectors                                                                                                                                                                                                                                                                          | 259 |

| 11.9 | Under similar noise immunity conditions, a comparison of the leakage energy (per clock cycle) of the adder circuits with the low-V <sub>t</sub> , standard dual-V <sub>t</sub> , and sleep switch circuit techniques for six different input vectors                                                                                                                                                 | 262 |

| 11.10 | Under similar noise immunity conditions, cumulative standby energy dissipation of the low-V <sub>t</sub> and sleep switch adders for three different input vectors                                                                                                               | 264 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|