# **NOTE TO USERS**

This reproduction is the best copy available.

**UMI**<sup>®</sup>

# Noise Issues in Mixed-Signal Integrated Circuits

by

Weize Xu

Submitted in Partial Fulfillment

of the

Requirements for the Degree

Doctor of Philosophy

Supervised by

Professor Eby G. Friedman

Department of Electrical and Computer Engineering

School of Engineering and Applied Sciences

The College

University of Rochester

Rochester, New York

2004

## INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

---

UMI Microform 3156839

Copyright 2005 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company

300 North Zeeb Road

P.O. Box 1346

Ann Arbor, MI 48106-1346

## **Dedication**

To my wife Jing Liu, son Barry, and daughter Emily.

## **Curriculum Vitae**

The author was born in Nanjing, China on October 13, 1961. From 1978 to 1982, he studied at the Department of Electrical Engineering, Nanjing Institute of Post and Telecommunications where he received his B.S. degree in Electrical Engineering. After graduation, he worked for four years as an assistant engineer at Nanjing General Semiconductor Device Plant in China on process development and circuit design of NMOS ICs. From 1986 to 1990, he was a research engineer at the Solid-State Device Research Institute, Nanjing, China working in the area of millimeter wave and microwave power transmitters (MMIC). He came to the University of Rhode Island in September 1990, where he received his Masters degree in Electrical Engineering in 1993.

He was with TCI Corporation from 1993 to 1997 in Boston, Massachusetts and Philadelphia, Pennsylvania, working on the design of linear CCD and TFT LCD displays, respectively. He joined the Eastman Kodak Company, Rochester, New York in 1997. He is now a senior IC design engineer at Kodak, working on the design of CMOS mixed-signal integrated circuits.

He is currently completing his Ph.D. degree in the area of substrate coupling noise test and analysis at the University of Rochester.

## Acknowledgments

I would like to express my sincere gratitude towards Professor Eby G. Friedman, my academic advisor. Through his continuous and enthusiastic encouragement, Professor Friedman guided me across the bridge connecting engineering and academic research. He has spent countless hours discussing with me research ideas and teaching me how to improve my presentation skills and academic writing style.

I would like to thank Professors Mark J. Bocko, Christopher M. Brown, and Hui Wu for acting as members of my Ph.D. committee. I would also like to thank RuthAnn Williams for her administrative support.

I would like to express my special thanks to my wife Jing Liu for her incredible support and understanding through the years of my graduate studies at the University of Rochester. I would also like to promise my son Barry and daughter Emily more time together with them.

My appreciation goes to Eastman Kodak for providing me with full support both financially and technically during the years of my part time Ph.D. studies. My research work would have taken much longer time without the support from Kodak

in the area of design tools, chip fabrication, and laboratory testay. Special thanks to my colleagues at the University of Rochester, Andrey Mezhiba, Volkan Kursun, Boris Andreev, Dimitris Velenis, Magdy El-Moursy, Junmou Zhang, Mikhail Popovich, Guoqing Chen, Jonathan Rosenfeld, and Vassilis Pavlidis for their help and discussions. I would also like to thank my colleagues at Eastman Kodak, Mike Mattern, Mike Guidash, Simon Cooper, Bruce Johnson, Ravi Mruthyunjaya, David Madziarz, David Sacktte, Bruce McDermott, Michael Shamberger and all who gave their kind help and support.

## Abstract

Complex high-speed digital circuits are commonly integrated together with high performance analog circuits onto the same substrate. In such mixed-signal systems, fast switching transients produced by digital circuits can couple into sensitive analog components through both the substrate and line-to-line capacitances, thereby limiting the achievable analog precision. Furthermore, performance degradation caused by substrate and capacitive coupling noise is difficult to control and even more difficult to predict. The need for highly accurate noise measurement to identify and manage noise has therefore become increasingly evident.

An analysis of clock feedthrough in CMOS analog transmission gate switches is presented in this dissertation. A clock feedthrough mechanism and a related model of a transmission gate switch are established in the current-voltage domain. Region and zone maps of the transmission gate during switch-off are developed and used to efficiently estimate clock feedthrough noise.

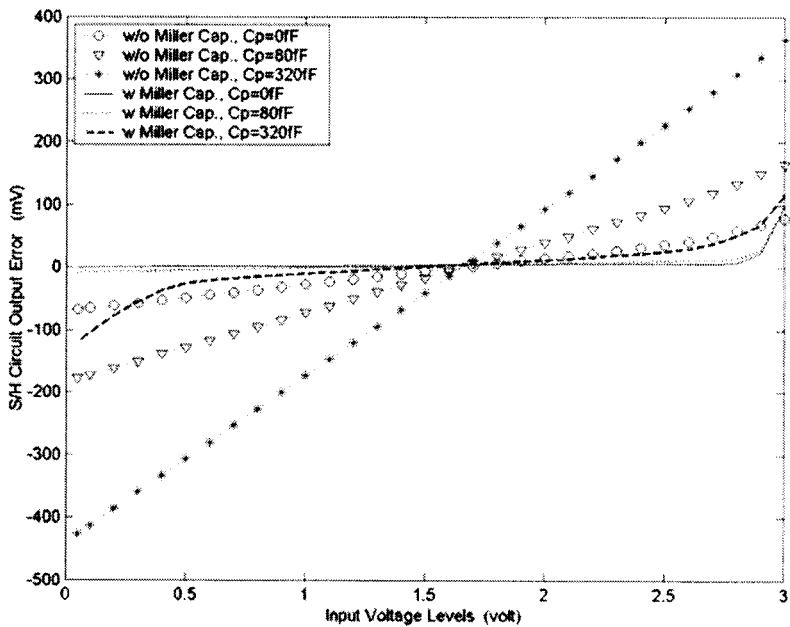

The charge-sharing effect (CSE) in switched-capacitor CMOS circuits is studied and evaluated. A technique using Miller capacitance in a sample-and-hold circuit is introduced to reduce the charge sharing effect caused by the parasitic capacitances and clock feedthrough from a sampling switch. A ten-fold reduction in CSE and clock feedthrough is achieved.

An on-chip circuit has also been developed to directly measure substrate and line-to-line coupling noise voltages and waveforms. This test circuit has been manufactured in a 0.35  $\mu\text{m}$  CMOS process and consists of noise generators and switched-capacitor signal processing circuitry. The experimental data show that on-chip generators ranging in area from 1  $\mu\text{m}^2$  to 6  $\mu\text{m}^2$  produce noise at the receiver, decreasing from 3.14 mV/ $\mu\text{m}$  to 0.73 mV/ $\mu\text{m}$ . The efficiency with which including substrate guard rings reduces substrate noise has also been studied and evaluated in this research effort. Supported by experiment measurement, open loop and closed guard rings reduce the noise by 20% and 85%, respectively. The difference between experimental and analytic models of the line-to-line coupling capacitance ranges from 8.5% to 17.7% for different metal layers.

## Table of Contents

|                                                                                           |     |

|-------------------------------------------------------------------------------------------|-----|

| <b>Dedication .....</b>                                                                   | ii  |

| <b>Curriculum Vitae .....</b>                                                             | iii |

| <b>Acknowledgments .....</b>                                                              | iv  |

| <b>Abstract.....</b>                                                                      | vi  |

| <br>                                                                                      |     |

| <b>Chapter One: Introduction .....</b>                                                    | 1   |

| 1.1. Development of the Integrated Circuit .....                                          | 2   |

| 1.2. IC Generations and Scaling of Semiconductor Processing Technologies .....            | 3   |

| 1.3. Difficulties in Characterizing Analog Circuit Technologies .....                     | 4   |

| 1.3.1. Subthreshold Characteristics of MOSFET's Are Difficult to Model.....               | 5   |

| 1.3.2. Modeling of Output Resistance of Short-Channel MOS Transistors .....               | 5   |

| 1.3.3. Modeling of the Capacitance of the Well-to-Substrate .....                         | 6   |

| 1.3.4. Linearity of Passive Devices.....                                                  | 6   |

| 1.3.5. Modeling of MOSFET Transconductance .....                                          | 6   |

| 1.4. Fabricating Analog and Digital circuits on the Same Substrate: Mixed-Signal ICs..... | 7   |

| 1.5. Analog and Mixed-Signal Circuit Noise Testing.....                                   | 8   |

| 1.6. Topics Presented in This Research Proposal .....                                     | 9   |

| <br>                                                                                      |     |

| <b>Chapter Two: Noise Sources in Mixed-Signal CMOS ICs.....</b>                           | 12  |

| 2.1. Noise in Integrated Circuits and Electronic Devices .....                            | 12  |

| 2.2. Random Noise .....                                                                   | 13  |

| 2.2.1. Noise Bandwidth.....                                                               | 15  |

| 2.2.2. Noise Factor and Noise Figure.....                                                 | 16  |

| 2.3. Major Types of Random Noise in CMOS ICs.....                                         | 16  |

| 2.3.1. Shot (Schottky) Noise .....                                                        | 16  |

| 2.3.2. Thermal (Johnson) Noise .....                                                      | 18  |

| 2.3.3. <i>KTC</i> Noise.....                                                              | 20  |

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| 2.3.4. $1/f$ (Flicker) Noise .....                                     | 21        |

| 2.3.5. Corner Frequency.....                                           | 22        |

| 2.4. Noise Sources in Mixed-Signal ICs from Parasitic Components ..... | 23        |

| 2.4.1. Substrate Coupling Noise.....                                   | 23        |

| 2.4.2. Capacitive Coupling Noise.....                                  | 25        |

| 2.4.3. Clock Feedthrough.....                                          | 26        |

| 2.4.4. Charge Sharing Effect.....                                      | 27        |

| 2.4.5. Power Supply/Ground Noise.....                                  | 27        |

| 2.5. Conclusions.....                                                  | 29        |

| <b>Chapter Three: Non-Ideal Factors in Mixed-Signal CMOS ICs .....</b> | <b>30</b> |

| 3.1. Component Mismatch in CMOS ICs.....                               | 30        |

| 3.2. Matching Properties of a MOS Transistor .....                     | 31        |

| 3.2.1. Variations in MOS Transistor Parameters .....                   | 33        |

| 3.3. Capacitor Mismatch.....                                           | 39        |

| 3.3.1. Variations in Capacitance.....                                  | 40        |

| 3.3.2. Random Error in MOS Capacitors .....                            | 45        |

| 3.4. Conclusions.....                                                  | 47        |

| <b>Chapter Four: Accurate Substrate Noise Testing Technique.....</b>   | <b>49</b> |

| 4.1. Substrate Coupling Noise .....                                    | 51        |

| 4.2. Principle of the Substrate Noise Testing Technique .....          | 54        |

| 4.2.1. Generating and Detecting Substrate Noise.....                   | 55        |

| 4.2.2. Circuit Operation.....                                          | 56        |

| 4.3. Detailed Circuit Characteristics .....                            | 58        |

| 4.3.1. Integration of the Substrate Noise.....                         | 58        |

| 4.3.2. Circuit Calibration.....                                        | 62        |

| 4.4. Accuracy and Error Analysis .....                                 | 63        |

| 4.5. OPAMP and Comparator.....                                         | 64        |

| 4.5.1. OPAMP Circuit Design.....                                       | 65        |

| 4.5.2. Comparator Circuit Design .....                                 | 68        |

| 4.6. Simulation Results .....                                          | 73        |

|                                                                                                             |            |

|-------------------------------------------------------------------------------------------------------------|------------|

| 4.7. Conclusions.....                                                                                       | 75         |

| <b>Chapter Five: A Circuit Technique for Accurately Measuring Coupling Capacitance .....</b>                | <b>76</b>  |

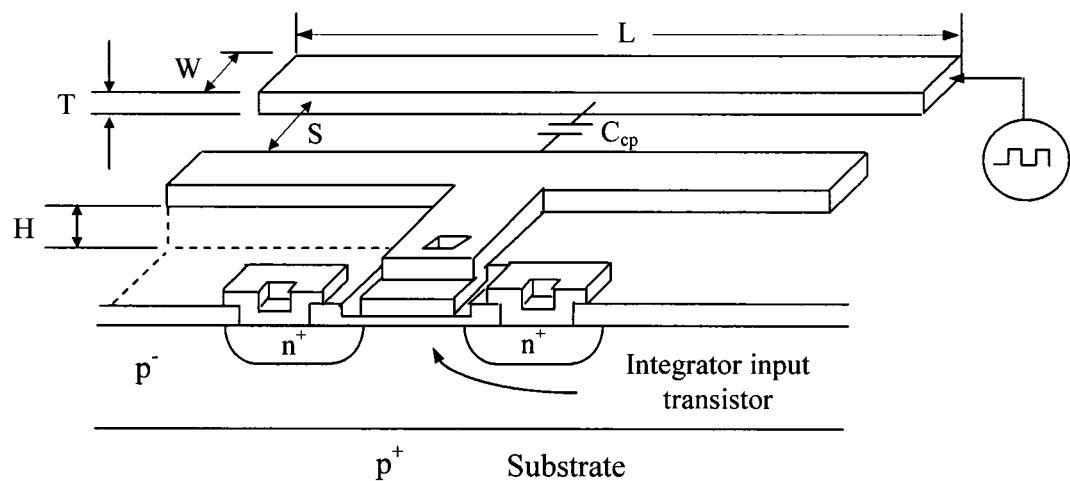

| 5.1. On-Chip Coupling Between Lines.....                                                                    | 78         |

| 5.2. Circuit Principles .....                                                                               | 81         |

| 5.2.1. Operation of the Test Circuit.....                                                                   | 81         |

| 5.3. Detailed Circuit Characteristics .....                                                                 | 83         |

| 5.4.1. Circuit Calibration Process.....                                                                     | 85         |

| 5.4. Accuracy and Error Analysis.....                                                                       | 86         |

| 5.5. Simulation Results .....                                                                               | 87         |

| 5.6. Conclusions.....                                                                                       | 91         |

| <b>Chapter Six: Clock Feedthrough in CMOS Analog Transmission Gate Switches.....</b>                        | <b>92</b>  |

| 6.1. Mechanism of Clock Feedthrough in TG Switches.....                                                     | 94         |

| 6.1.1. Clock Feedthrough in TG Switches .....                                                               | 95         |

| 6.1.2. Modeling Clock Feedthrough in TG Switches.....                                                       | 96         |

| 6.1.3. Region Map.....                                                                                      | 97         |

| 6.2. Clock Feedthrough in the Full Conduction Region .....                                                  | 100        |

| 6.3. Half Conduction.....                                                                                   | 104        |

| 6.4. Subthreshold/Cutoff Region .....                                                                       | 110        |

| 6.5. Simulation Results .....                                                                               | 111        |

| 6.6. Conclusions.....                                                                                       | 113        |

| <b>Chapter Seven: Charge Sharing Effect (CSE) in CMOS Switched Capacitor Sample-and-Hold Circuits .....</b> | <b>115</b> |

| 7.1. Sample-and-Hold Circuit Design.....                                                                    | 116        |

| 7.2. Charge Sharing Effect (CSE).....                                                                       | 119        |

| 7.3. Charge-Sharing Noise in CMOS Switched Capacitor S/H Circuits .....                                     | 121        |

| 7.4. Results and Comparison with SPICE .....                                                                | 125        |

| 7.4.1. Comparison of the Analytic Results with SPICE.....                                                   | 125        |

|                                                                                                                                         |            |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------|

| 7.4.2. Reduction of Charge Sharing Effect Noise .....                                                                                   | 127        |

| 7.5. Conclusions.....                                                                                                                   | 128        |

| <b>Chapter Eight: A CMOS Miller Hold Capacitance Sample-and-Hold Circuit to Reduce Charge Sharing Effect and Clock Feedthrough.....</b> | <b>130</b> |

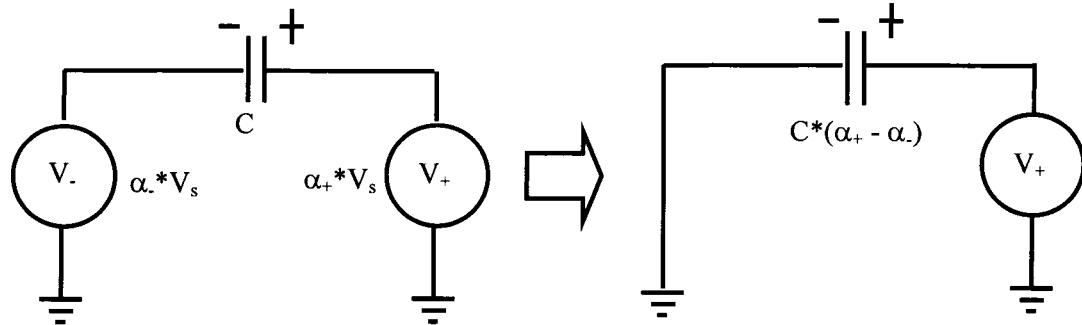

| 8.1. Miller Effect and Charge Sharing Effect .....                                                                                      | 131        |

| 8.1.1. Miller Effect .....                                                                                                              | 131        |

| 8.1.2. The Charge Sharing Effect.....                                                                                                   | 133        |

| 8.2. A Miller Hold Capacitor Circuit for Reducing CSE Reduction and Clock Feedthrough.....                                              | 134        |

| 8.3. Results and Discussion .....                                                                                                       | 138        |

| 8.4. Simulation Results .....                                                                                                           | 139        |

| 8.5. Conclusions.....                                                                                                                   | 142        |

| <b>Chapter Nine: Random Transistor Mismatch in CMOS Differential Pairs .....</b>                                                        | <b>144</b> |

| 9.1. MOS Transistor Random Mismatch .....                                                                                               | 146        |

| 9.1.1. Variations in MOS Threshold Voltage.....                                                                                         | 147        |

| 9.1.2. Variations in the MOS Transistor Current Factor .....                                                                            | 148        |

| 9.1.3. Drain Current Mismatch.....                                                                                                      | 150        |

| 9.1.4. Gate-to-Source Voltage ( $V_{GS}$ ) Mismatch.....                                                                                | 151        |

| 9.2. MOS Differential Pair.....                                                                                                         | 152        |

| 9.2.1. Offset Voltage Due to Random Transistor Mismatch in MOS Differential Pairs                                                       | 152        |

| 9.2.2. Common-Mode Rejection Ratio (CMRR) of a CMOS Differential Pair.....                                                              | 157        |

| 9.3. Conclusions.....                                                                                                                   | 159        |

| <b>Chapter Ten: Experiment Data .....</b>                                                                                               | <b>161</b> |

| 10.1. On-Chip Substrate Coupling Noise Test Technique .....                                                                             | 164        |

| 10.2. Experimental Data from the Substrate Coupling Noise Test Circuit.....                                                             | 170        |

| 10.3. Substrate Coupling Noise Reduction Due to Guard Lines and Rings .....                                                             | 173        |

| 10.4. Line-to-Line Capacitive Coupling Measurement Results.....                                                                         | 175        |

| 10.5. Summary.....                                                                                                                      | 179        |

|                                                                            |     |

|----------------------------------------------------------------------------|-----|

| <b>Chapter Eleven: Conclusions.....</b>                                    | 180 |

| 11.1. Measuring Substrate Coupling Noise .....                             | 181 |

| 11.2. Measuring Capacitive Coupling Noise .....                            | 182 |

| <b>Chapter Twelve: Future Work .....</b>                                   | 185 |

| 12.1. Future Work on Modeling Substrate Coupling Noise .....               | 187 |

| 12.1.1. Circuit Optimization.....                                          | 188 |

| 12.1.2. Noise Generator Matrix.....                                        | 189 |

| 12.1.3. Physical Design of the Noise Generator Matrix.....                 | 190 |

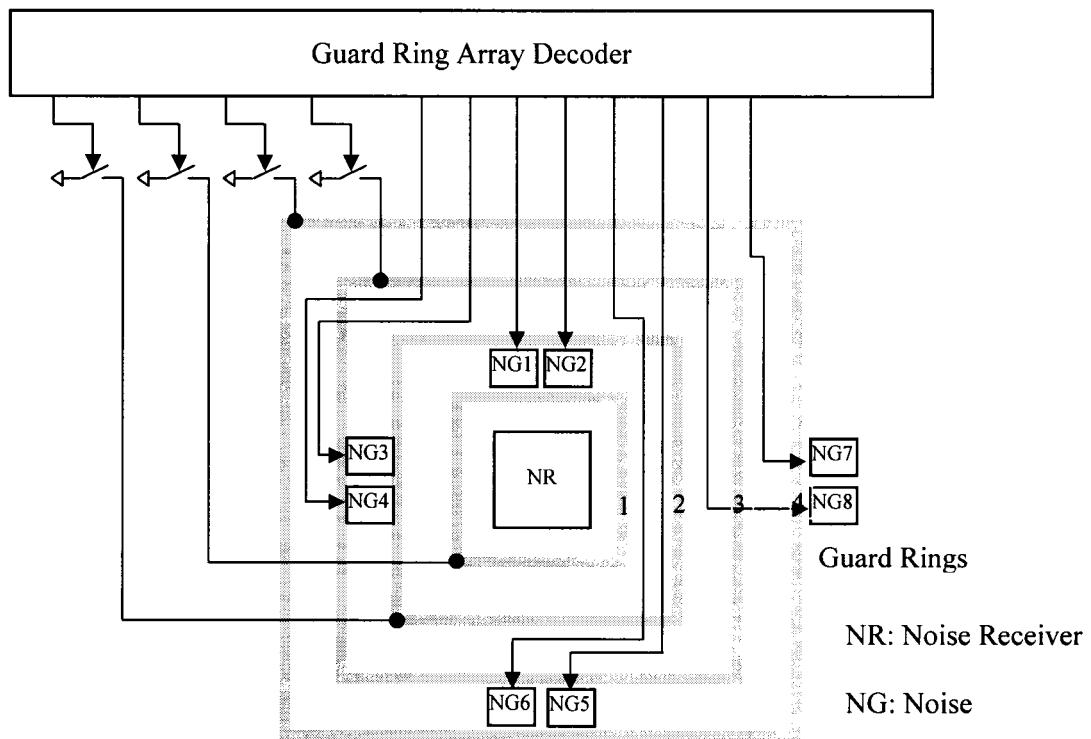

| 12.2. Substrate Coupling Noise Guard Rings .....                           | 192 |

| 12.3. Future Work on Modeling Line-to-Line Capacitive Coupling .....       | 193 |

| 12.4 Conclusions.....                                                      | 194 |

| <b>References.....</b>                                                     | 195 |

| <b>Appendix A: Random Noise Theorems.....</b>                              | 213 |

| A.1. Energy Theorem.....                                                   | 213 |

| A2. Random Pulse Train.....                                                | 214 |

| A.3. Wiener-Khintchine Theorem .....                                       | 215 |

| <b>Appendix B: Formulas of the Line-to-Line Coupling Capacitance .....</b> | 217 |

| B.1. Chang Formula [75] .....                                              | 217 |

| B.2. Elmasry's Formula [76] .....                                          | 218 |

| B.3. Yuan and Trick Formula [78] .....                                     | 218 |

| B.4. Meijs and Fokkema Formula [79].....                                   | 219 |

| Comparison.....                                                            | 219 |

| <b>Appendix C: On-Chip Coupling Noise Test Patterns.....</b>               | 221 |

| <b>Appendix D: IC Package and Pin List .....</b>                           | 225 |

| <b>Appendix E: IC Test Setup .....</b>                                     | 239 |

## List of Figures

|                                                                                                                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-1: Scaling of conventional CMOS Ics.....                                                                                                                                                                         | 3  |

| Figure 1-2: Transistor output impedance.....                                                                                                                                                                              | 5  |

| Figure 1-3: MOSFET Ttransconductance vs effective channel length.....                                                                                                                                                     | 7  |

| Figure 2-1: Bandwidth of an abrupt response function .....                                                                                                                                                                | 15 |

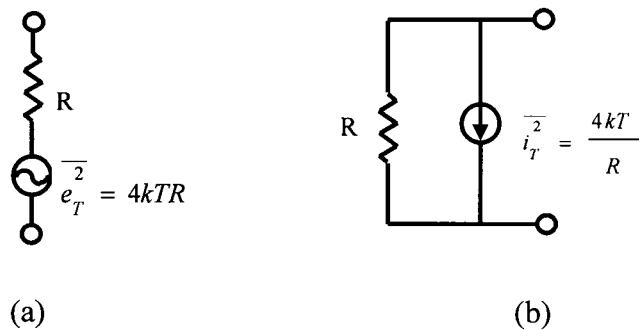

| Figure 2-2: Models of resistor thermal noise in the form of (a) a voltage source, (b) a current source .....                                                                                                              | 19 |

| Figure 2-3: Capacitive shunting of a noisy resistor .....                                                                                                                                                                 | 21 |

| Figure 2-4: Flicker noise spectrum and corner frequency .....                                                                                                                                                             | 22 |

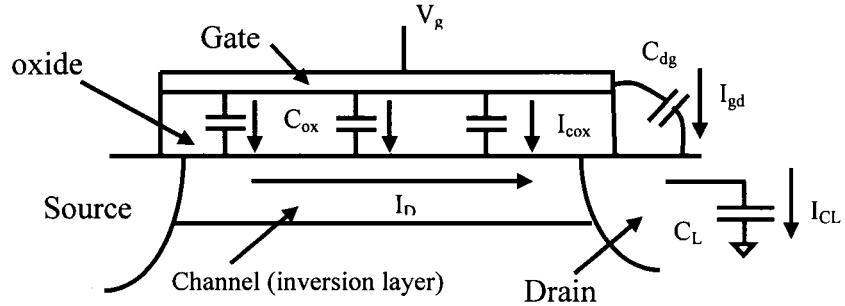

| Figure 2-5: Current flow in a MOSFET .....                                                                                                                                                                                | 27 |

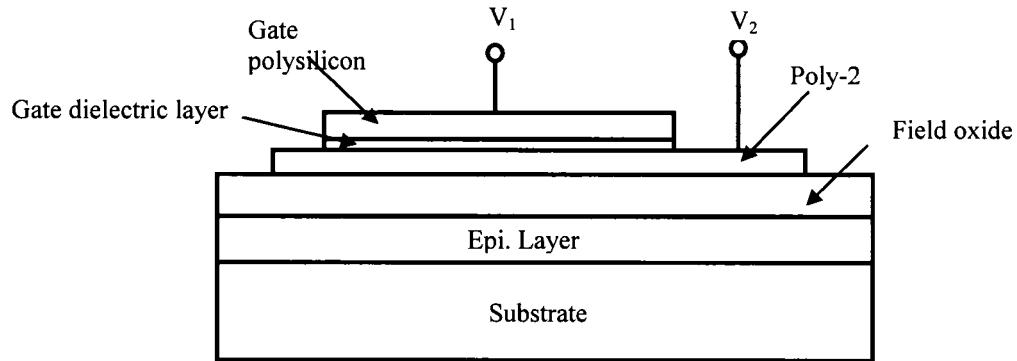

| Figure 3-1: Double polysilicon capacitor (an epitaxial layer is a thin silicon film with a specific doping level, thickness, crystal direction, and is grown on a low receptivity single crystal silicon substrate) ..... | 44 |

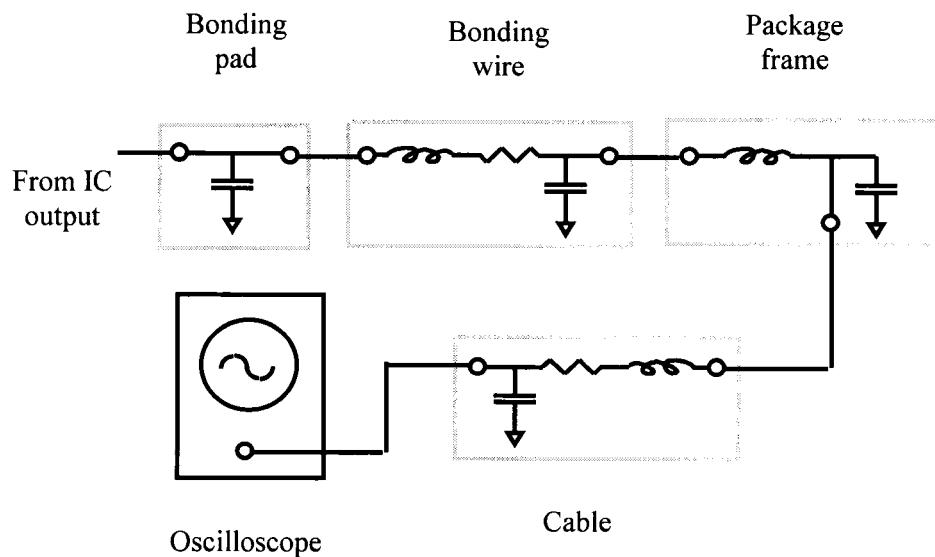

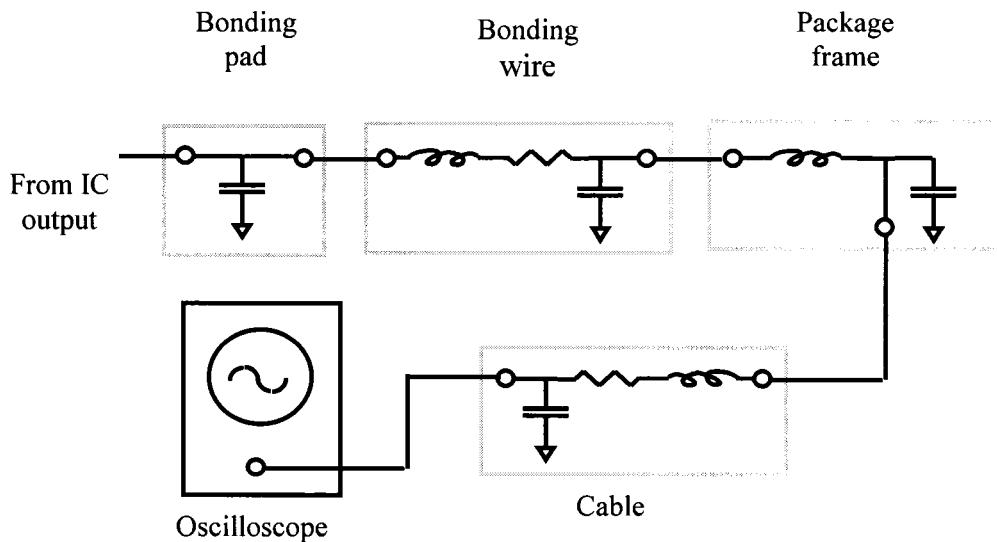

| Figure 4-1: Parasitic impedances along an IC test path.....                                                                                                                                                               | 50 |

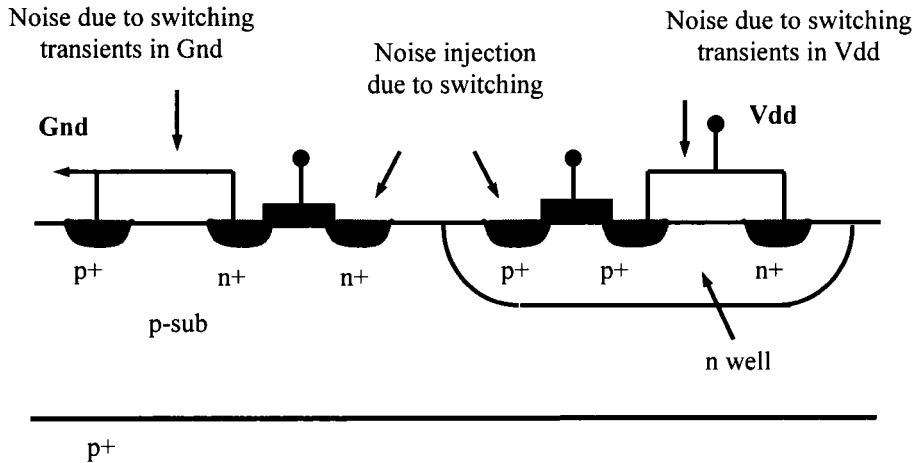

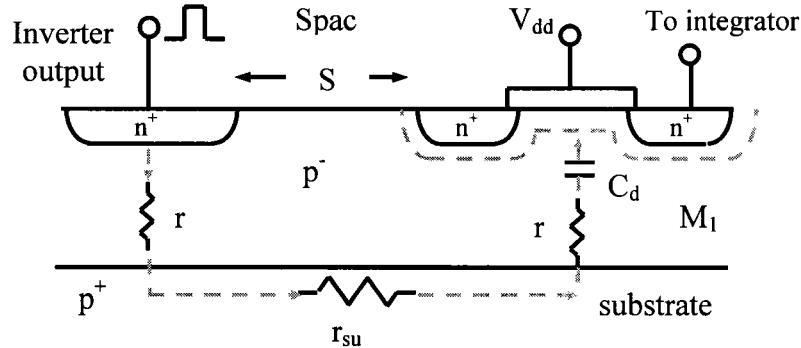

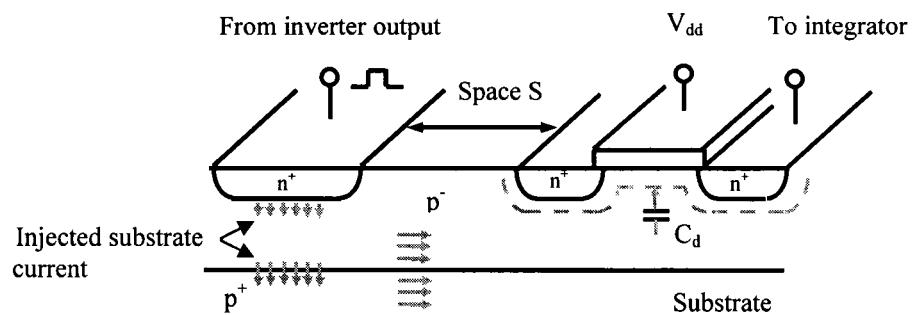

| Figure 4-2: Sources of noise coupling within the substrate.....                                                                                                                                                           | 53 |

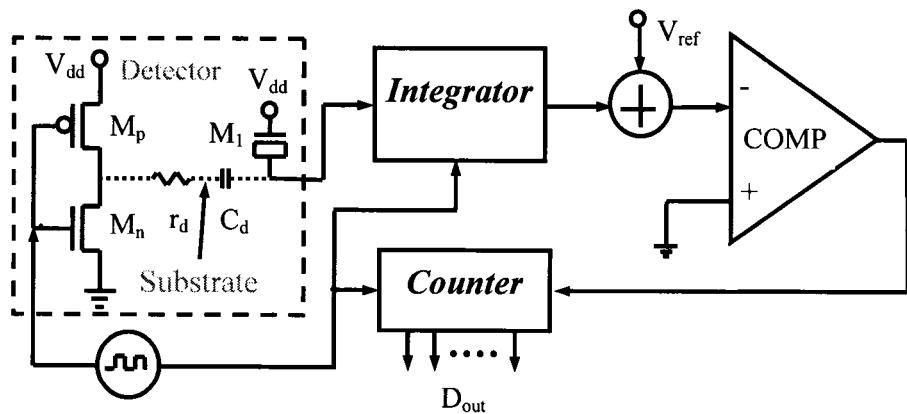

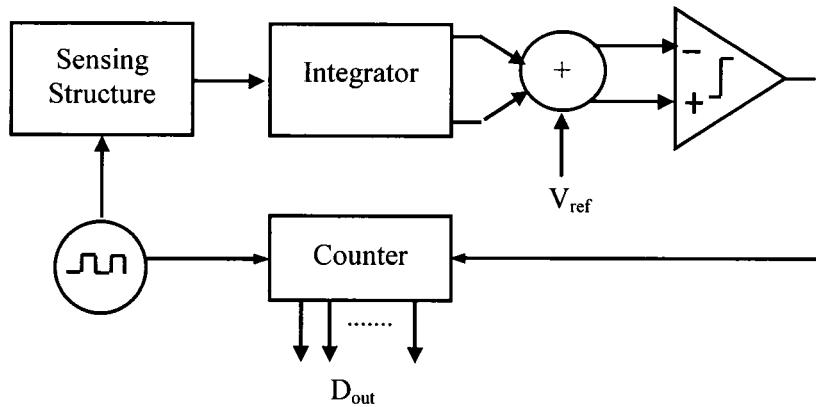

| Figure 4-3: Substrate coupling noise test circuit.....                                                                                                                                                                    | 54 |

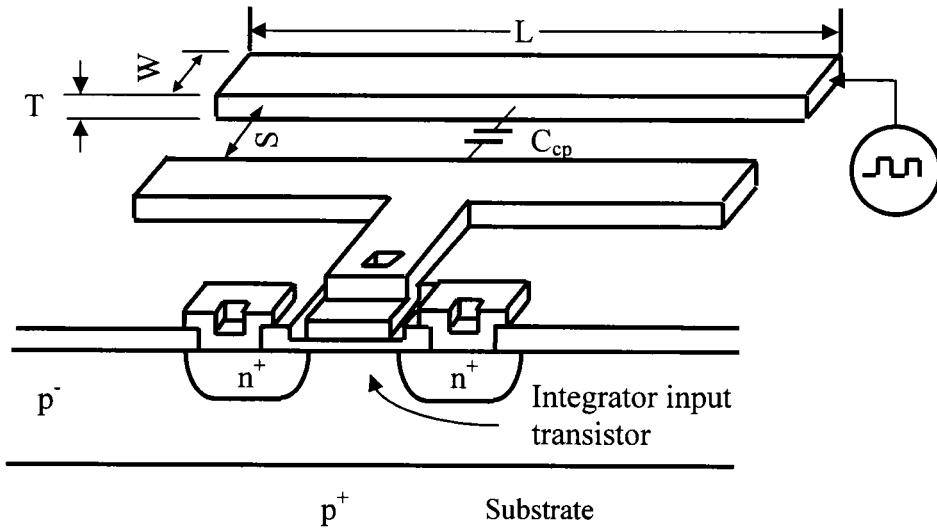

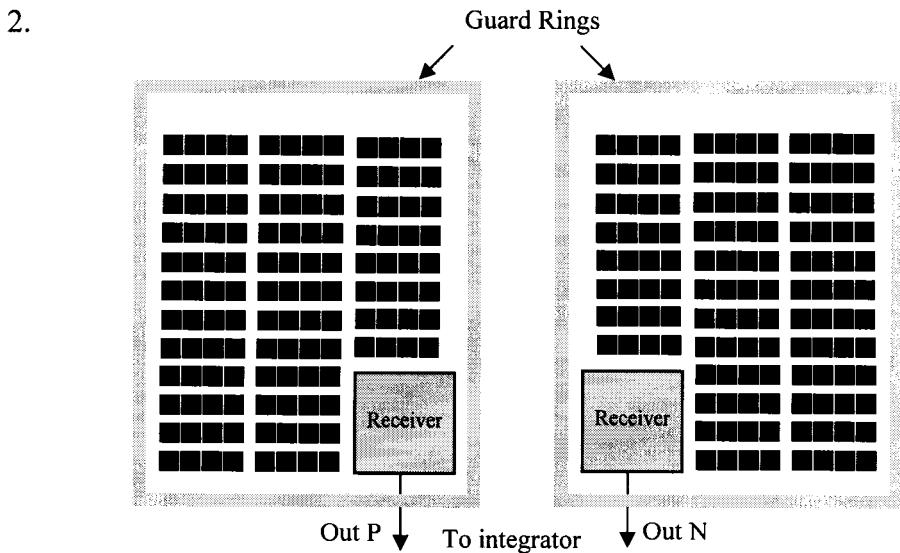

| Figure 4-4: The sensing part of the substrate noise test circuit.....                                                                                                                                                     | 56 |

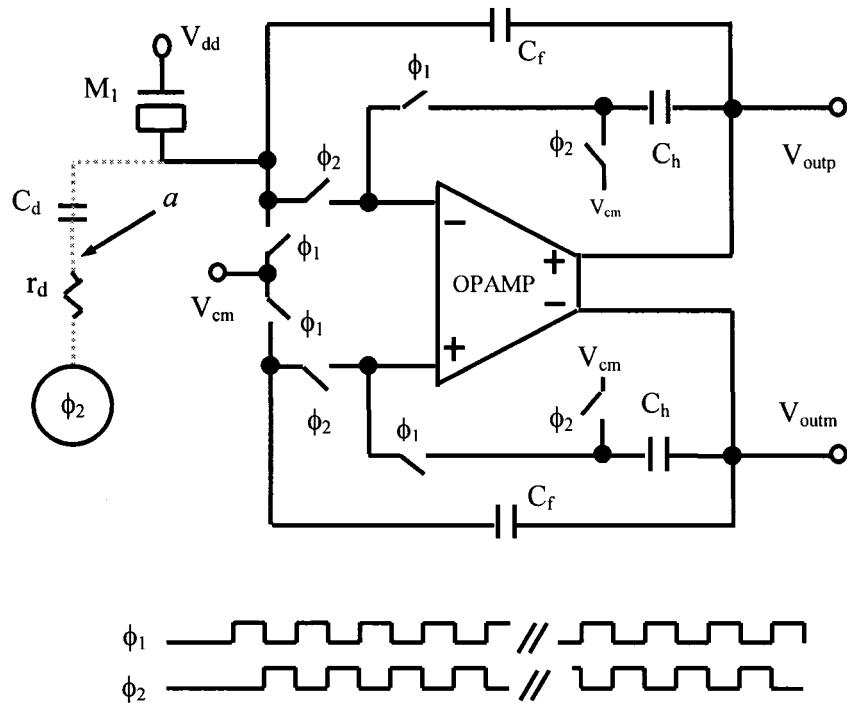

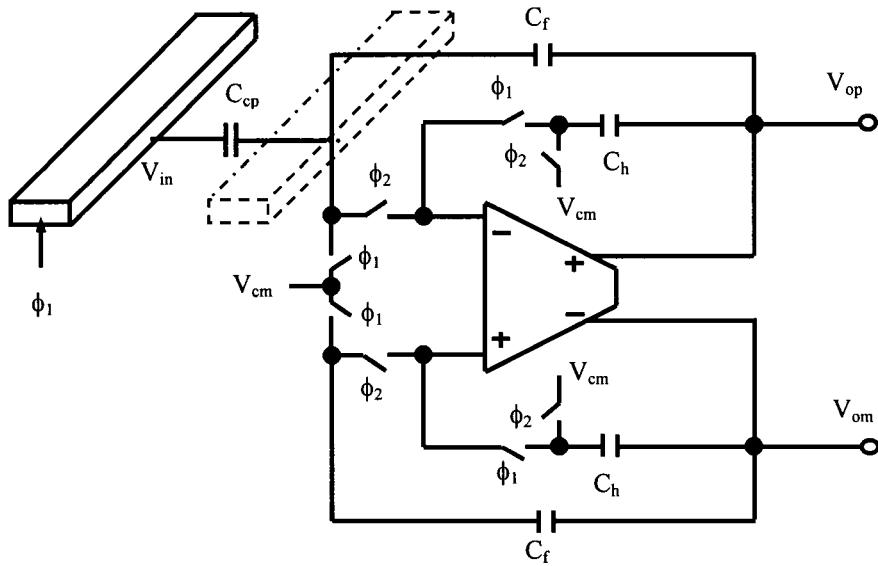

| Figure 4-5: Substrate coupling voltage integrator circuit, a) schematic, b) clock waveforms .....                                                                                                                         | 60 |

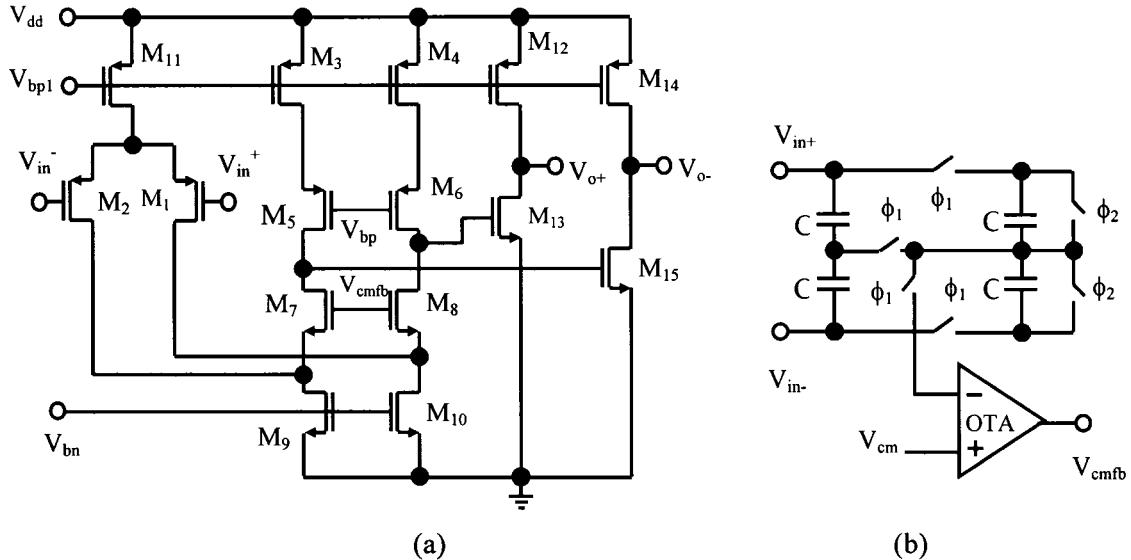

| Figure 4-6: Low power folded-cascode OPAMP, a) schematic, b) common-mode feedback circuit .....                                                                                                                           | 66 |

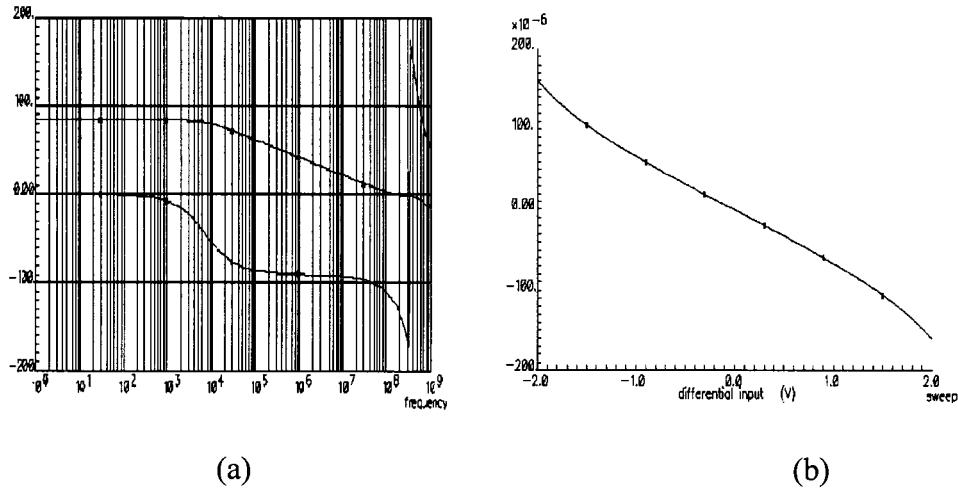

| Figure 4-7: Simulation of OPAMP, a) open loop voltage gain and phase margin, b) output offset voltage.....                                                                                                                | 67 |

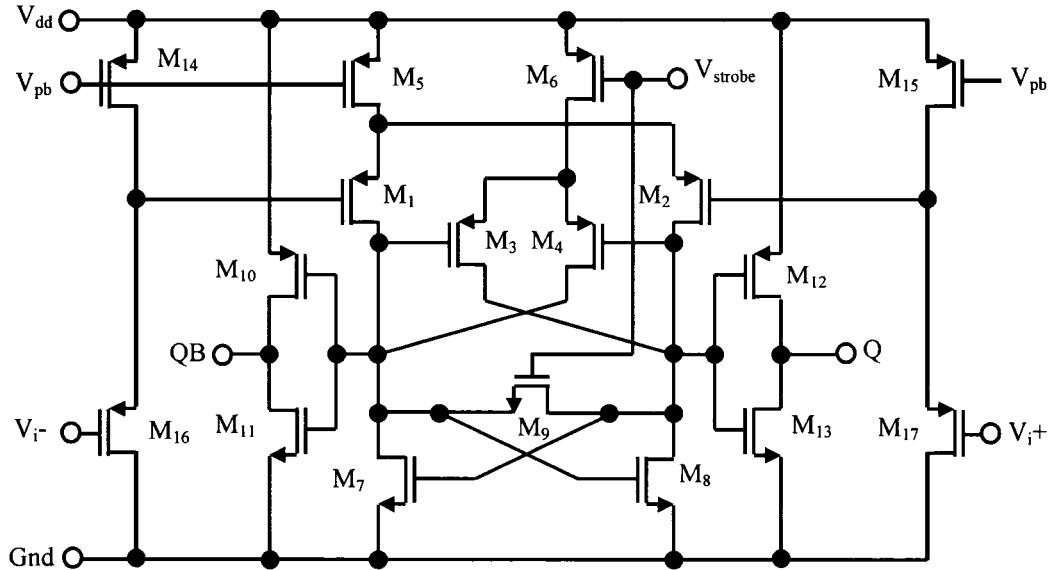

| Figure 4-8: Schematic of the dynamic differential comparator .....                                                                                                                                                        | 69 |

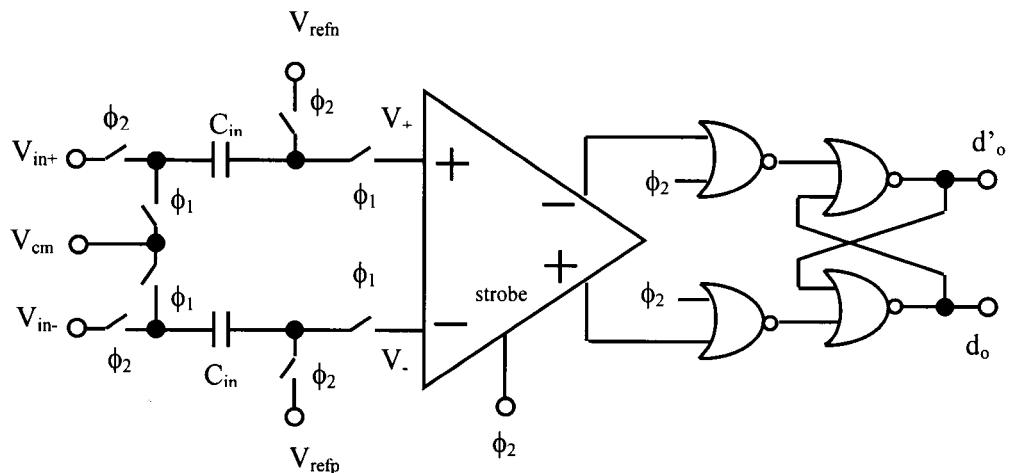

| Figure 4-9: Switched-capacitor comparator block circuit .....                                                                                                                                                             | 70 |

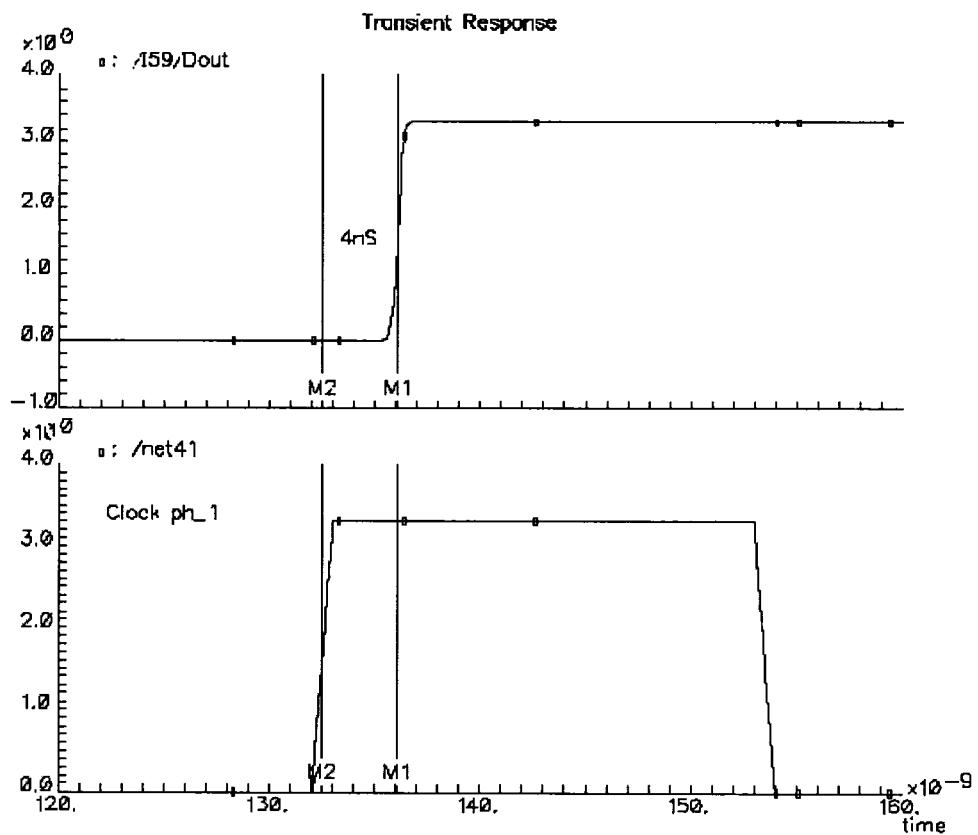

| Figure 4-10: SPICE simulation of propagation delay of the comparator block .....                                                                                                                                          | 71 |

|                                                                                                                                                                                                                                                                                                                    |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

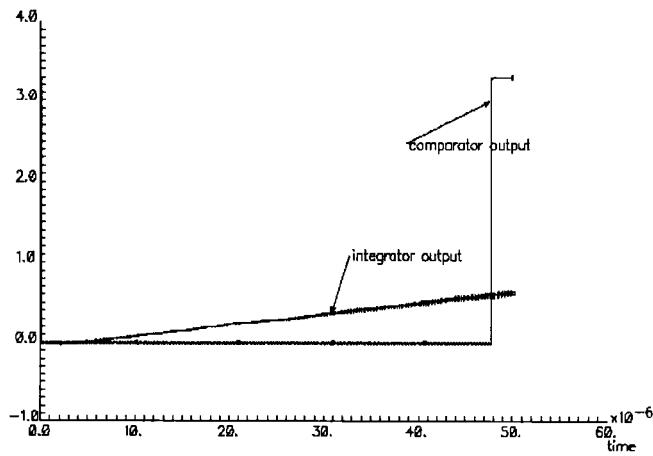

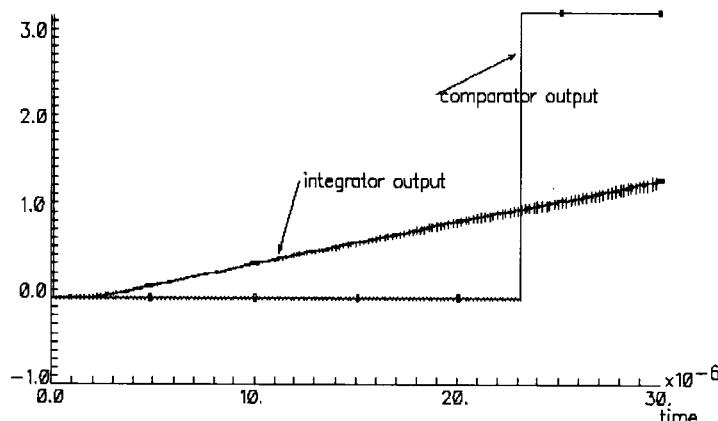

| Figure 4-11: SPICE derived waveforms of the integrator and comparator outputs.<br>$V_{ref} = 600$ mV, $f = 5$ MHz, and the output is 235 .....                                                                                                                                                                     | 73  |

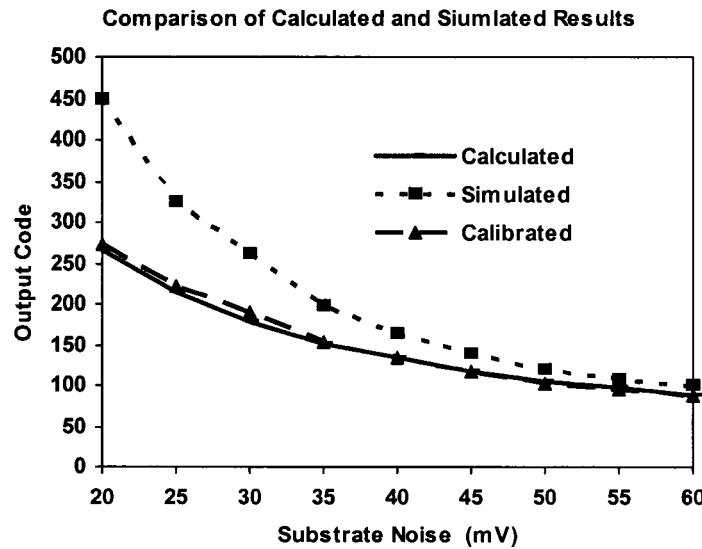

| Figure 4-12: Comparison of calculated, simulated, and calibrated digital codes ....                                                                                                                                                                                                                                | 74  |

| Figure 5-1: Parasitic impedances along an IC test path.....                                                                                                                                                                                                                                                        | 77  |

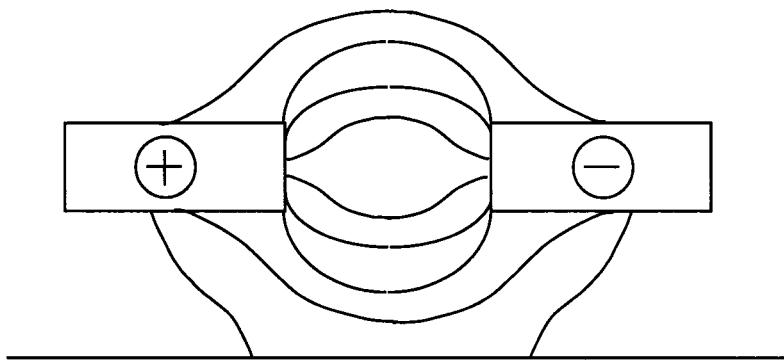

| Figure 5-2: Electric field coupling flux between parallel lines.....                                                                                                                                                                                                                                               | 79  |

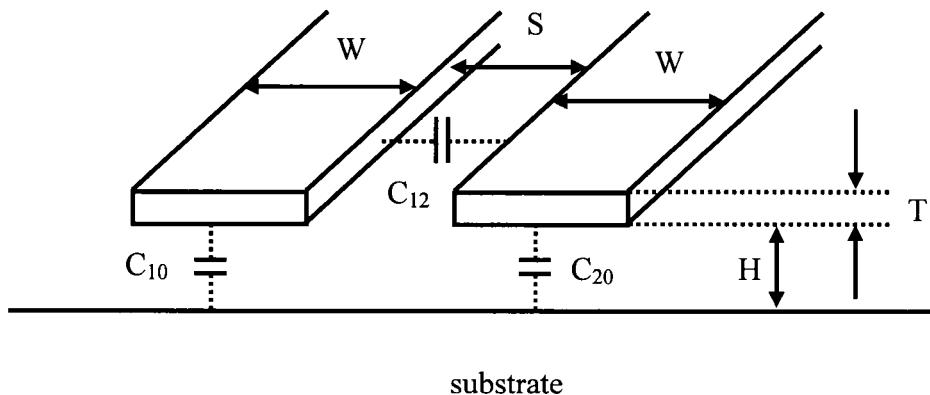

| Figure 5-3: A two line system with parasitic capacitances.....                                                                                                                                                                                                                                                     | 80  |

| Figure 5-4: Capacitive coupling test circuit.....                                                                                                                                                                                                                                                                  | 81  |

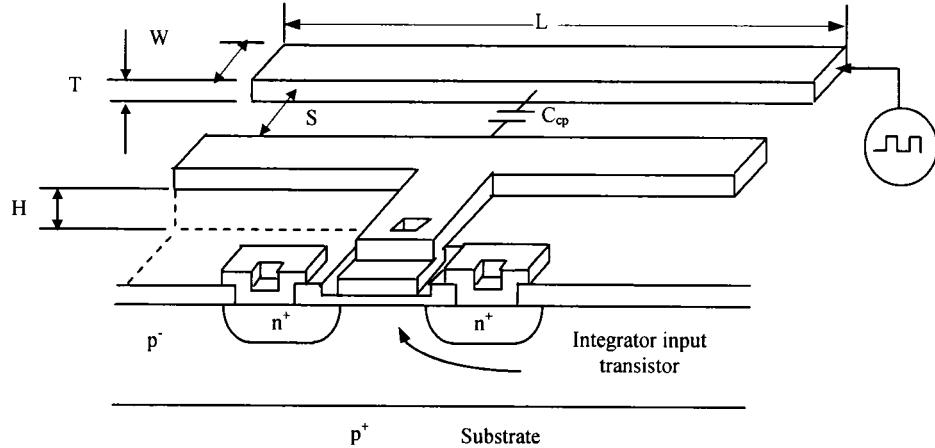

| Figure 5-5: Structure for sensing capacitive coupling .....                                                                                                                                                                                                                                                        | 82  |

| Figure 5-6: Switched capacitor voltage integrator circuit.....                                                                                                                                                                                                                                                     | 84  |

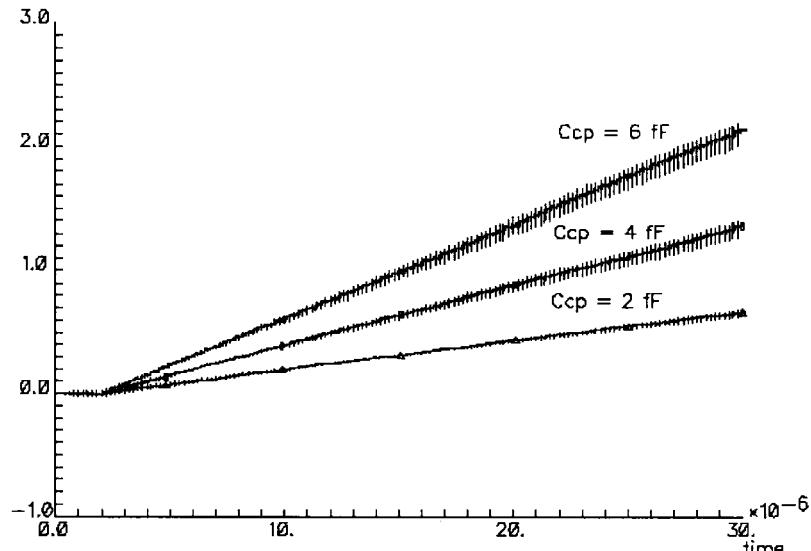

| Figure 5-7: SPICE simulation of the integrator differential and comparator outputs .....                                                                                                                                                                                                                           | 88  |

| Figure 5-8: comparator output with $V_{dd} = 3.3$ volts, $V_{ref} = 1$ volt, $C_f = 800$ fF .....                                                                                                                                                                                                                  | 89  |

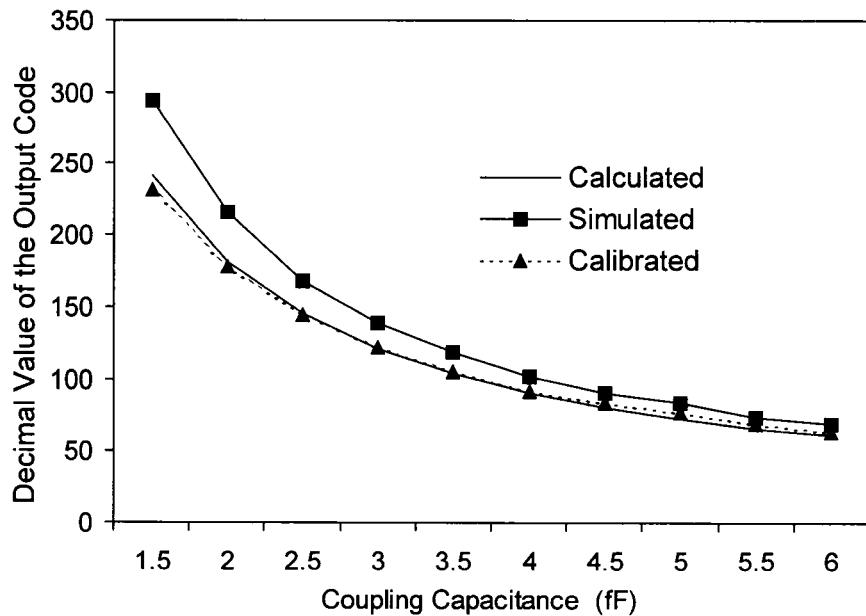

| Figure 5-9: Comparison of calculated, simulated, and calibrated digital codes .....                                                                                                                                                                                                                                | 90  |

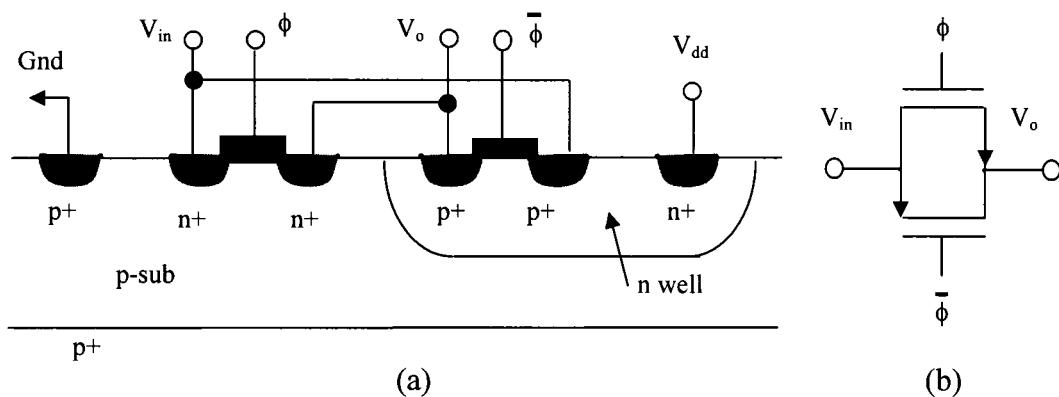

| Figure 6-1: CMOS TG analog switch: (a) device cross section, (b) circuit symbol                                                                                                                                                                                                                                    | 92  |

| Figure 6-2: Current flow in a MOSFET .....                                                                                                                                                                                                                                                                         | 94  |

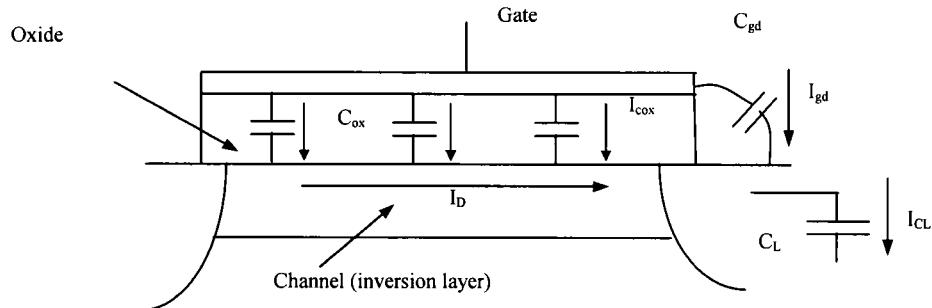

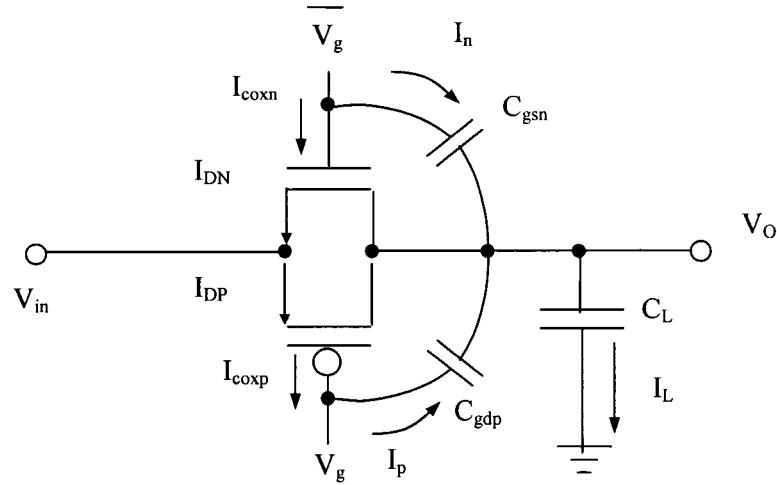

| Figure 6-3: An analog TG switch with an S/H capacitor, $C_L$ .....                                                                                                                                                                                                                                                 | 96  |

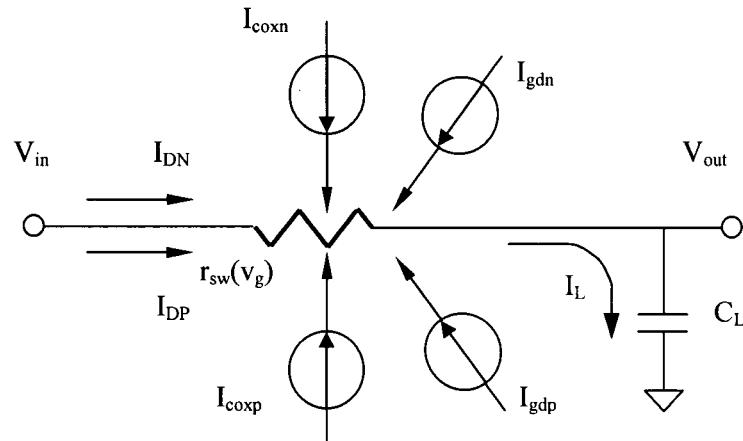

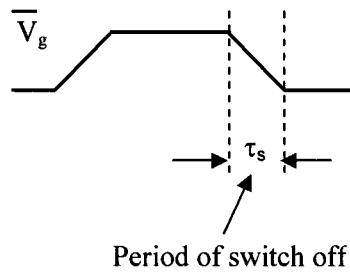

| Figure 6-4: Model of an analog TG switch during switched off .....                                                                                                                                                                                                                                                 | 97  |

| Figure 6-5: Region map when turning off the TG switch ( $W_n = W_p$ , and $L_n = L_p$ , and $V_{TN} =  V_{TP}  = V_{th}$ ) .....                                                                                                                                                                                   | 99  |

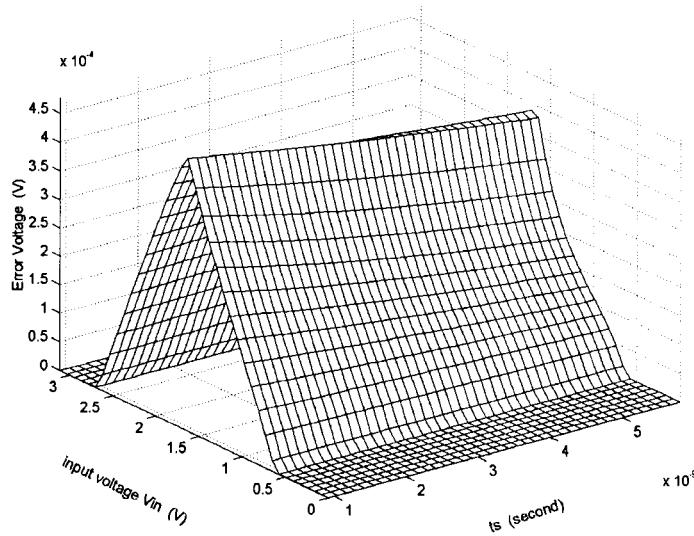

| Figure 6-6: Clock feedthrough error of an analog TG switch generated during the full conduction region ( $W_n = W_p = 10$ $\mu\text{m}$ , $L_n = L_p = 0.35$ $\mu\text{m}$ , $k_n = 40$ mA/V <sup>2</sup> , $ k_p  = 10$ mA/V <sup>2</sup> , $C_L = 1$ pF, and $C_{OZN} = C_{OXP} = 3$ fF/ $\mu\text{m}^2$ ) ..... | 103 |

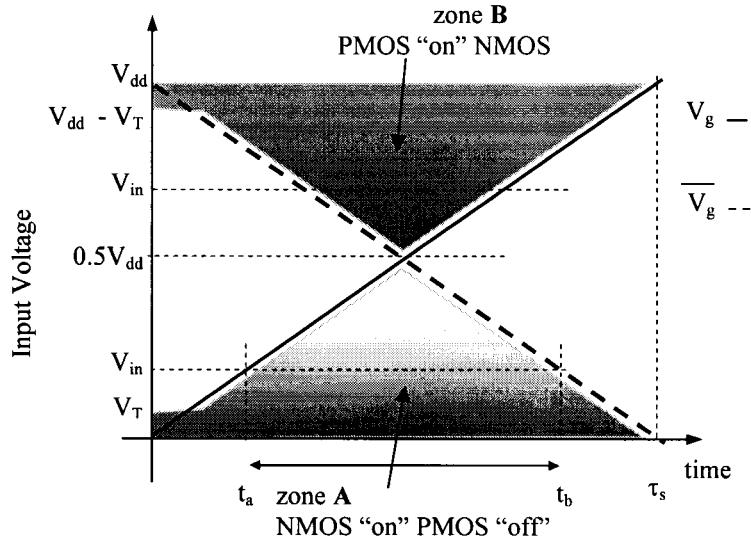

| Figure 6-7: Zones in the half conduction region for a symmetric TG switch ( $V_{TN} =  V_{TP}  = V_{th}$ , $W_n = W_p$ , and $L_n = L_p$ ).....                                                                                                                                                                    | 106 |

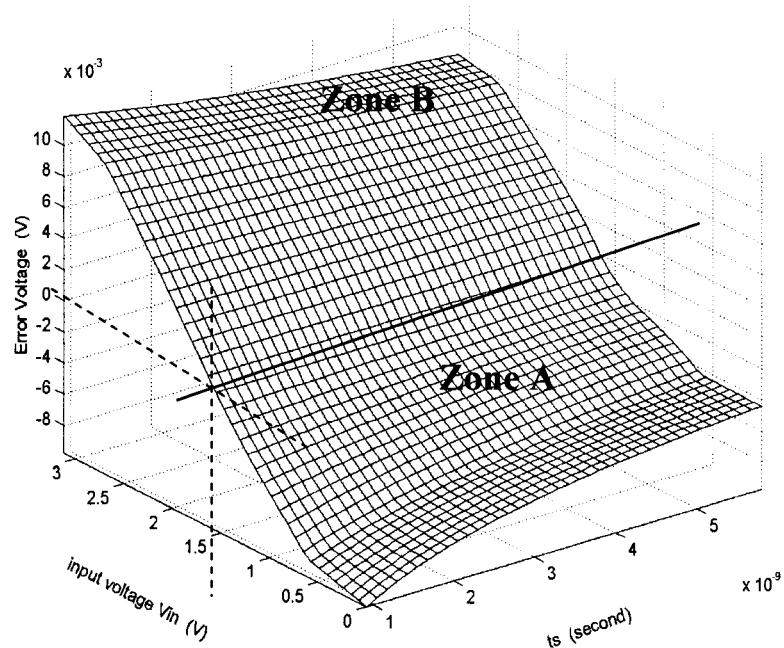

| Figure 6-8: Clock feedthrough error of a TG switch during the half conduction region ( $V_{dd} = 3.3$ volts, $W_n = W_p$ , and $L_n = L_p$ ) .....                                                                                                                                                                 | 108 |

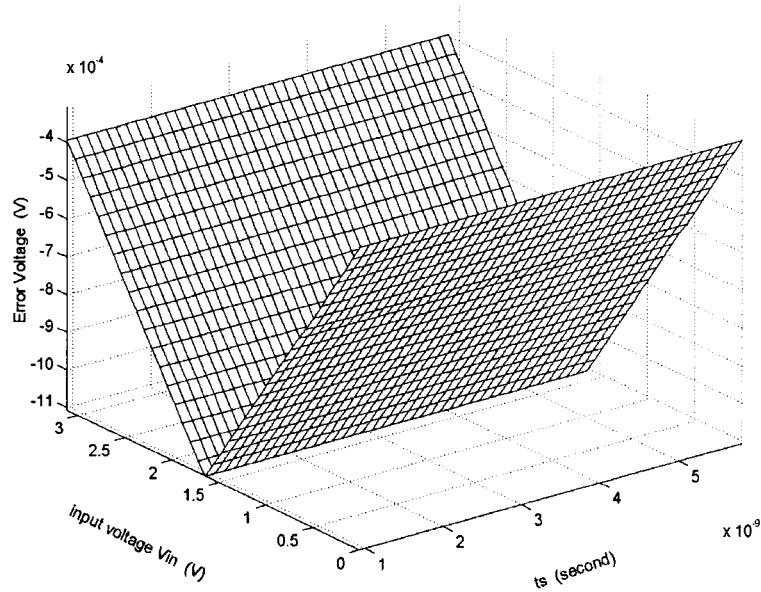

| Figure 6-9: Clock feedthrough error of a TG switch during the subthreshold/cutoff region ( $V_{dd} = 3.3$ volts, $W_n = W_p$ , and $L_n = L_p$ ) .....                                                                                                                                                             | 110 |

|                                                                                                                                                                                                                                                                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

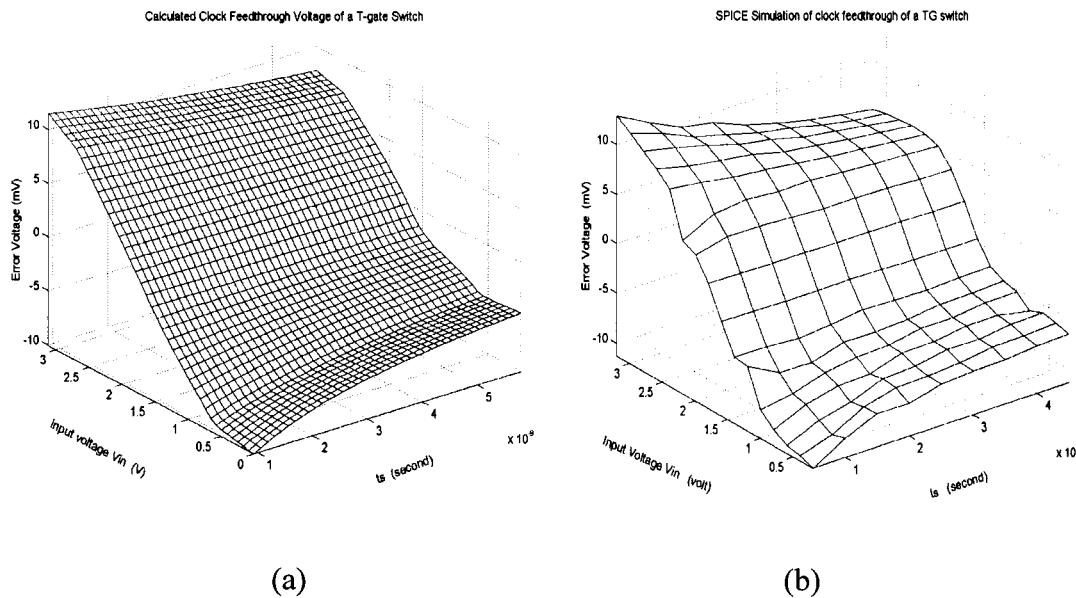

| Figure 6-10: Clock feedthrough voltage of a TG switch a) analytically determined, b) SPICE simulation ( $V_{dd} = 3.3$ volts, $V_{TN} =  V_{TP}  = 0.6$ volts, $W_n = W_p = 10$ $\mu\text{m}$ , $L_N = L_P = 0.35$ $\mu\text{m}$ , $k_n = 40$ mA/V <sup>2</sup> , $ k_P  = 10$ mA/V <sup>2</sup> , $C_L = 1$ pF, and $C_{OxN} = C_{OxP} = 3$ fF/ $\mu\text{m}^2$ )..... | 112 |

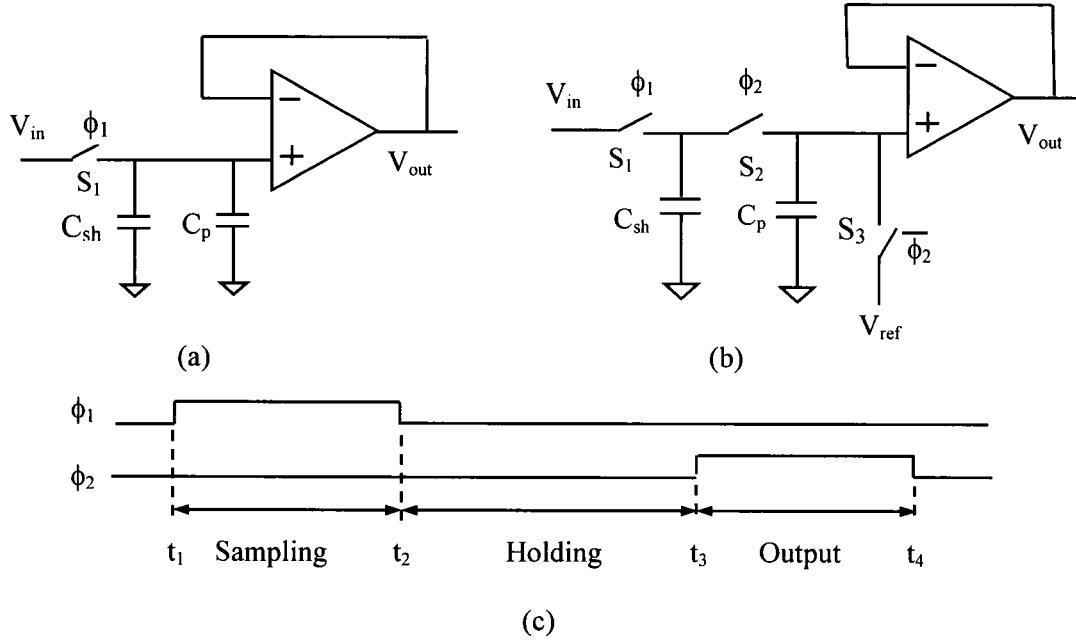

| Figure 7-1: S/H circuit, a) an open loop architecture, b) a different open loop architecture with amplifier offset compensation, c) typical timing of a S/H circuit.....                                                                                                                                                                                                | 117 |

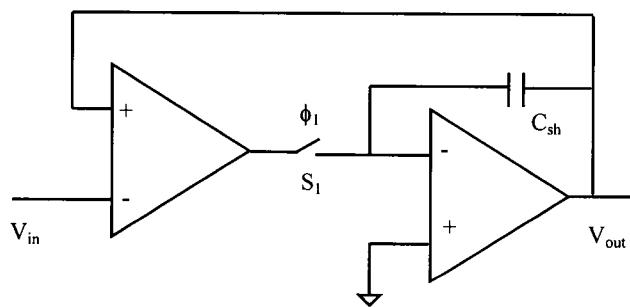

| Figure 7-2: Closed-loop sample-and-hold circuit architecture .....                                                                                                                                                                                                                                                                                                      | 118 |

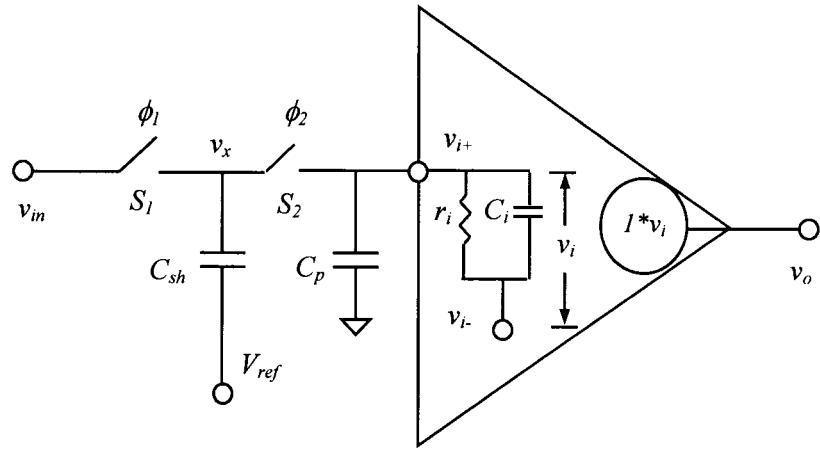

| Figure 7-3: A general open-loop CMOS switched capacitor S/H circuit .....                                                                                                                                                                                                                                                                                               | 120 |

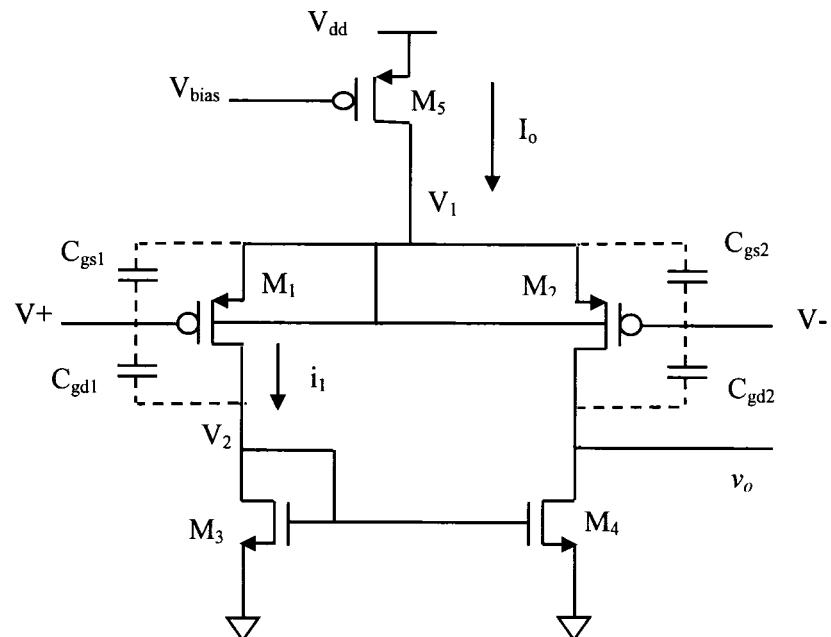

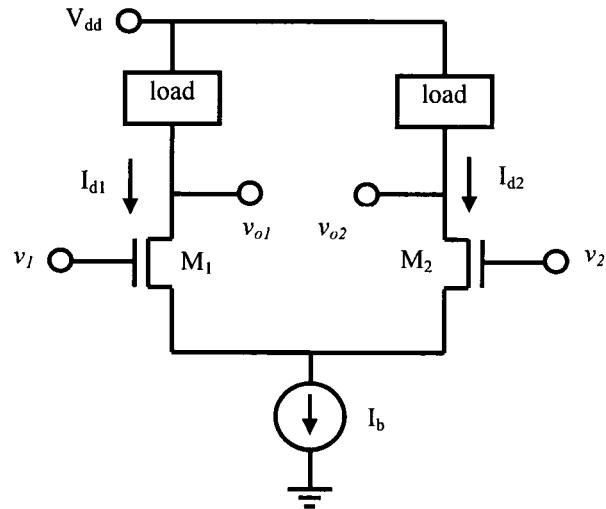

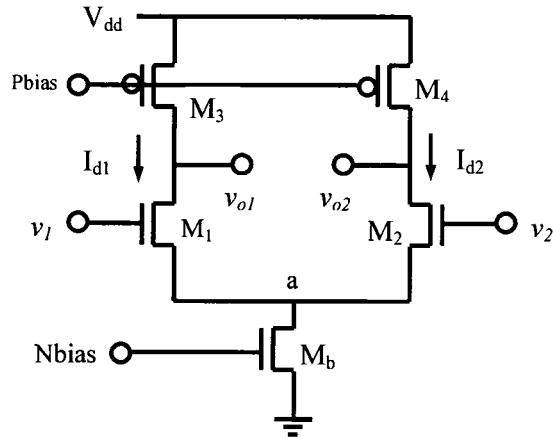

| Figure 7-4: A typical input stage of a CMOS OPAMP .....                                                                                                                                                                                                                                                                                                                 | 122 |

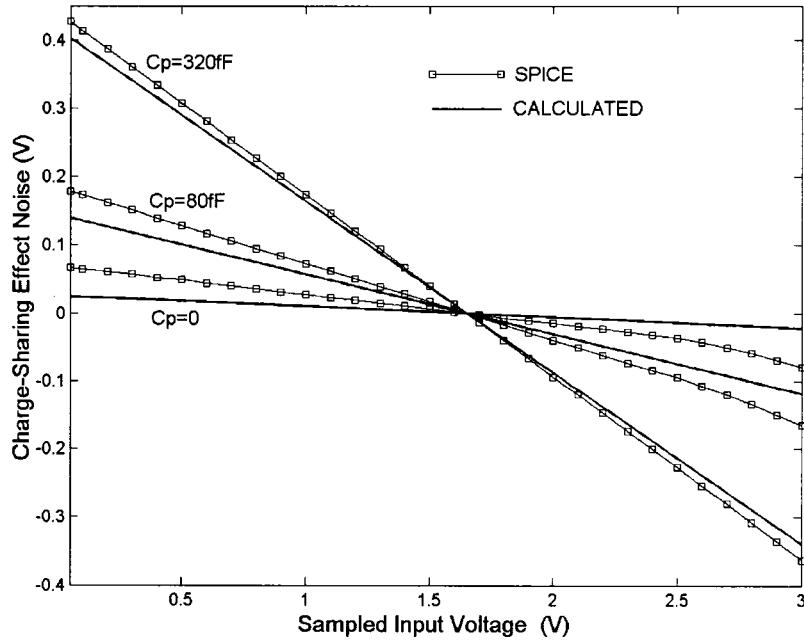

| Figure 7-5: Charge share effect in a S/H circuit shown in Fig. 6-1b ( $C_{sh} = 1$ pF, $V_{ref} = 1.65$ volts, $V_{dd} = 3.3$ volts, $W_L/L_I = 80$ $\mu\text{m}/0.4$ $\mu\text{m}$ , and $I_O = 100$ $\mu\text{A}$ for the amplifier input stage) .....                                                                                                                | 126 |

| Figure 7-6: A fixed amplifier input voltage S/H circuit to reduce the charge sharing effect noise .....                                                                                                                                                                                                                                                                 | 128 |

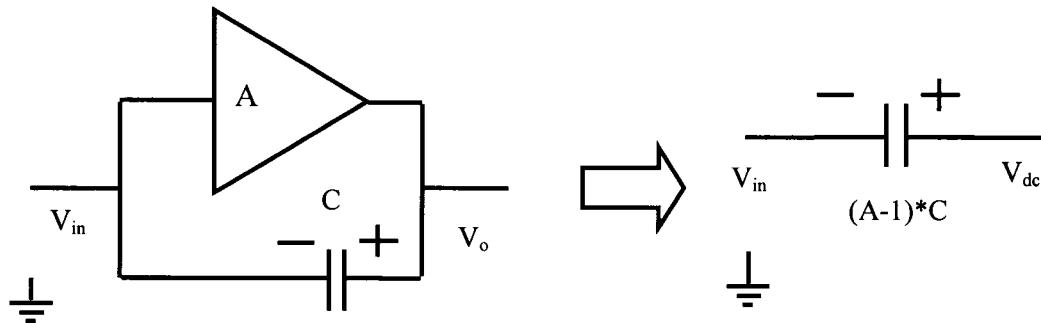

| Figure 8-1: Diagram of principle describing Miller effect .....                                                                                                                                                                                                                                                                                                         | 132 |

| Figure 8-2: A typical Miller capacitor configuration.....                                                                                                                                                                                                                                                                                                               | 133 |

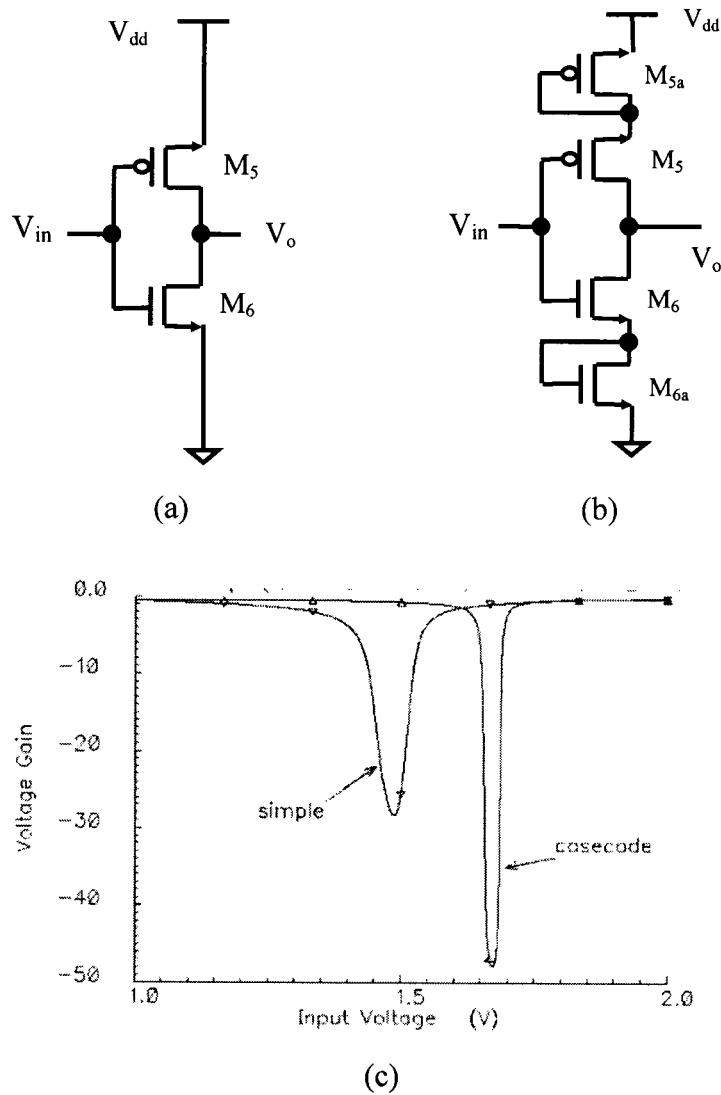

| Figure 8-3: Gain and circuit of two compact amplifiers, a) voltage gain, b) simple inverter amplifier, c) cascode inverter amplifier.....                                                                                                                                                                                                                               | 135 |

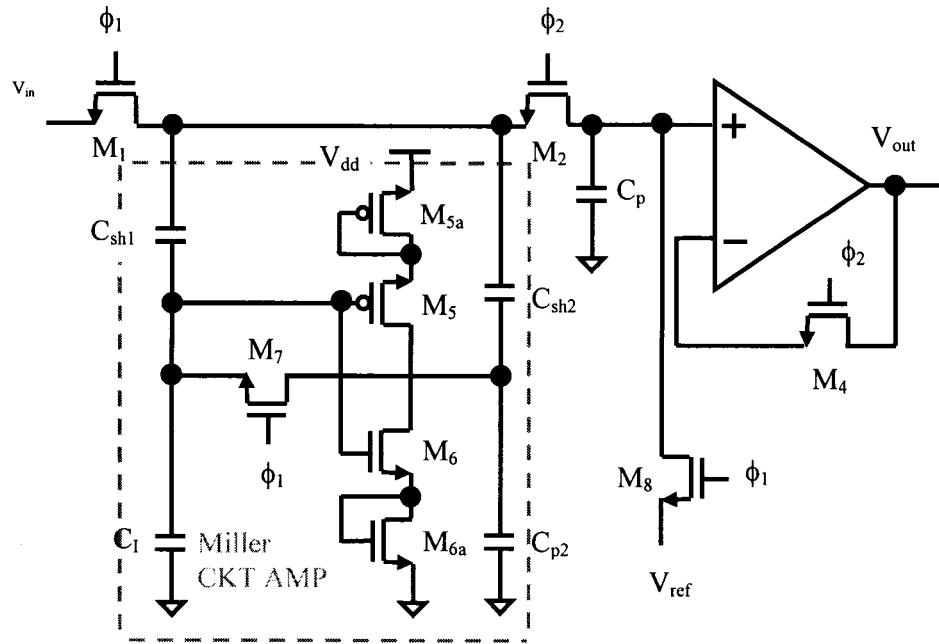

| Figure 8-4: The proposed Miller hold capacitor S/H circuit.....                                                                                                                                                                                                                                                                                                         | 137 |

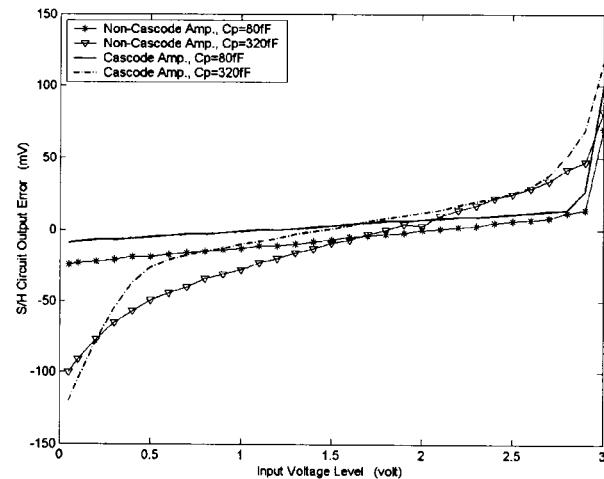

| Figure 8-5: Output error of circuits with and without the Miller feedback circuit                                                                                                                                                                                                                                                                                       | 140 |

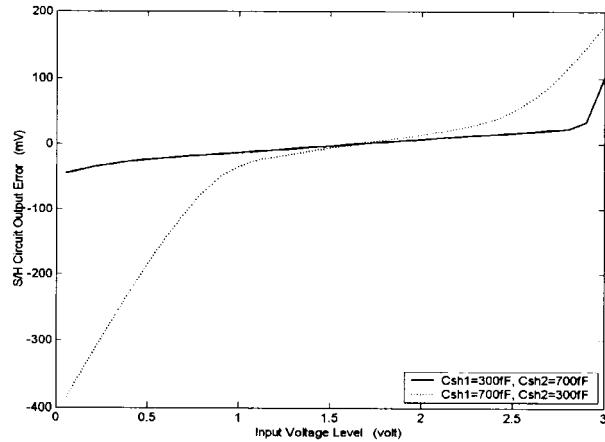

| Figure 8-6: Simulated output error of the proposed circuit with different S/H capacitance ratios .....                                                                                                                                                                                                                                                                  | 141 |

| Figure 8-7: Output error of a Miller capacitance S/H circuit with a simple inverting amplifier and cascode inverting amplifier.....                                                                                                                                                                                                                                     | 142 |

| Figure 9-1: An N type CMOS differential pair stage .....                                                                                                                                                                                                                                                                                                                | 145 |

| Figure 9-2: A standard CMOS differential pair amplifier stage .....                                                                                                                                                                                                                                                                                                     | 153 |

|                                                                                                                                                                                                                 |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

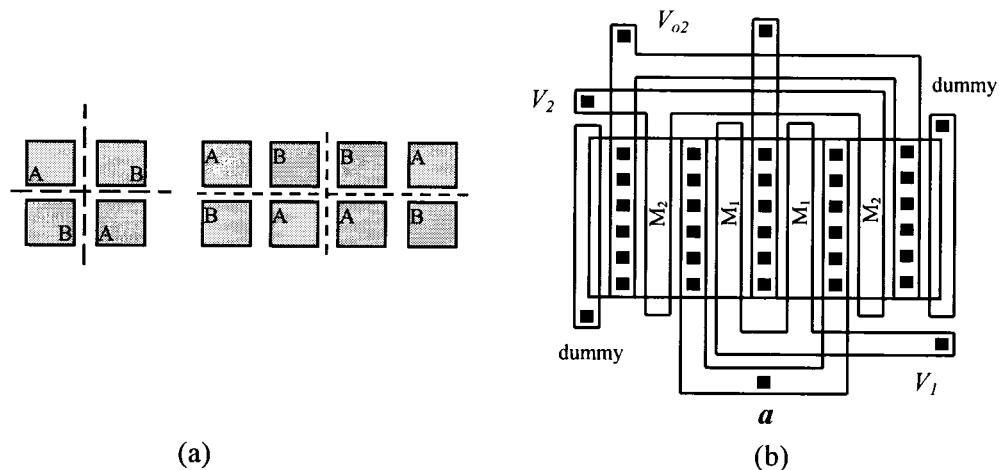

| Figure 9-3: The common-centroid layout technique for improving component matching, a) examples for matching components A and B, b) application to layout of M1 and M2 of a MOS differential pair.....           | 153 |

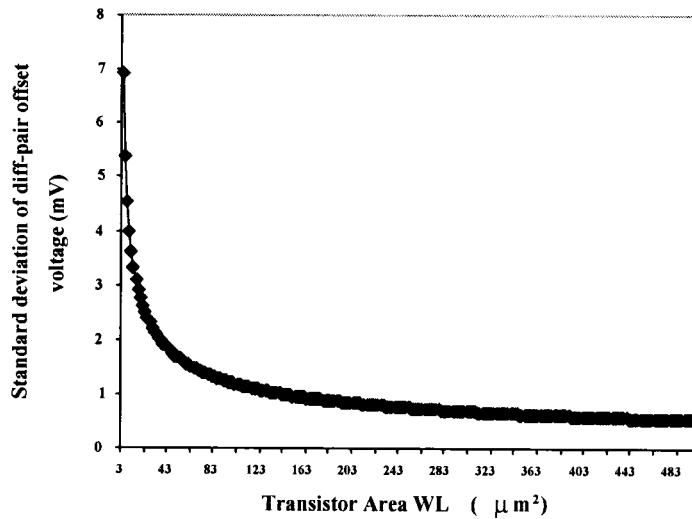

| Figure 9-4: Mismatch of input offset voltage of an NMOS differential amplifier (pair) for different transistor sizes for a 0.5 $\mu$ m CMOS process ( $A_{VT} = 12$ mV* $\mu$ m, and $A_K = 1.5\% \mu$ m) ..... | 156 |

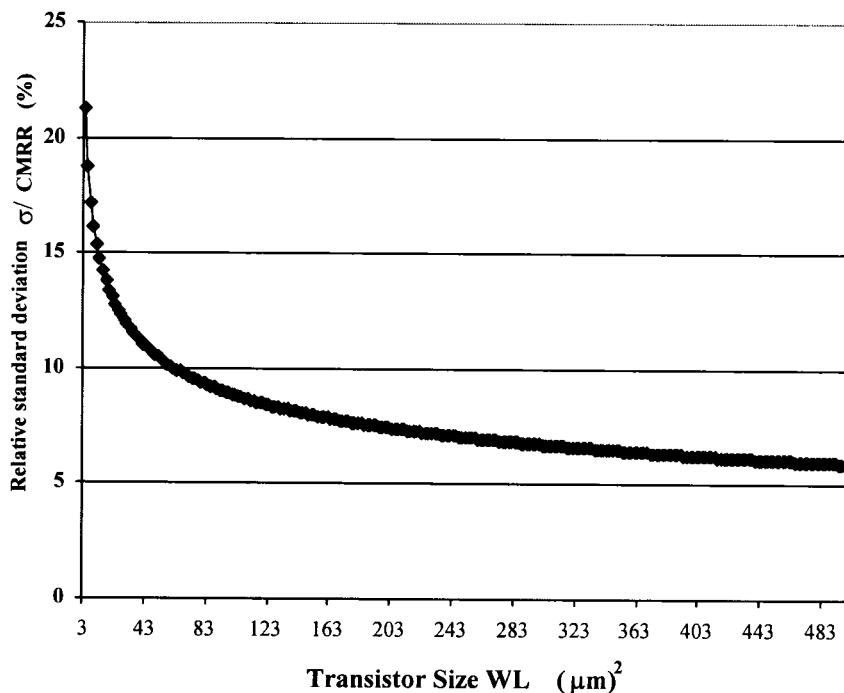

| Figure 9-5: Variation of CMRR for an NMOS differential pair amplifier for a 0.5 $\mu$ m CMOS process. ....                                                                                                      | 158 |

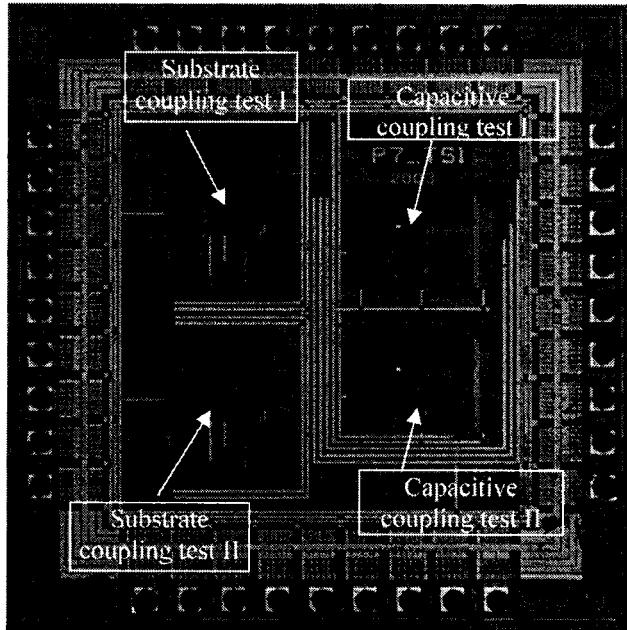

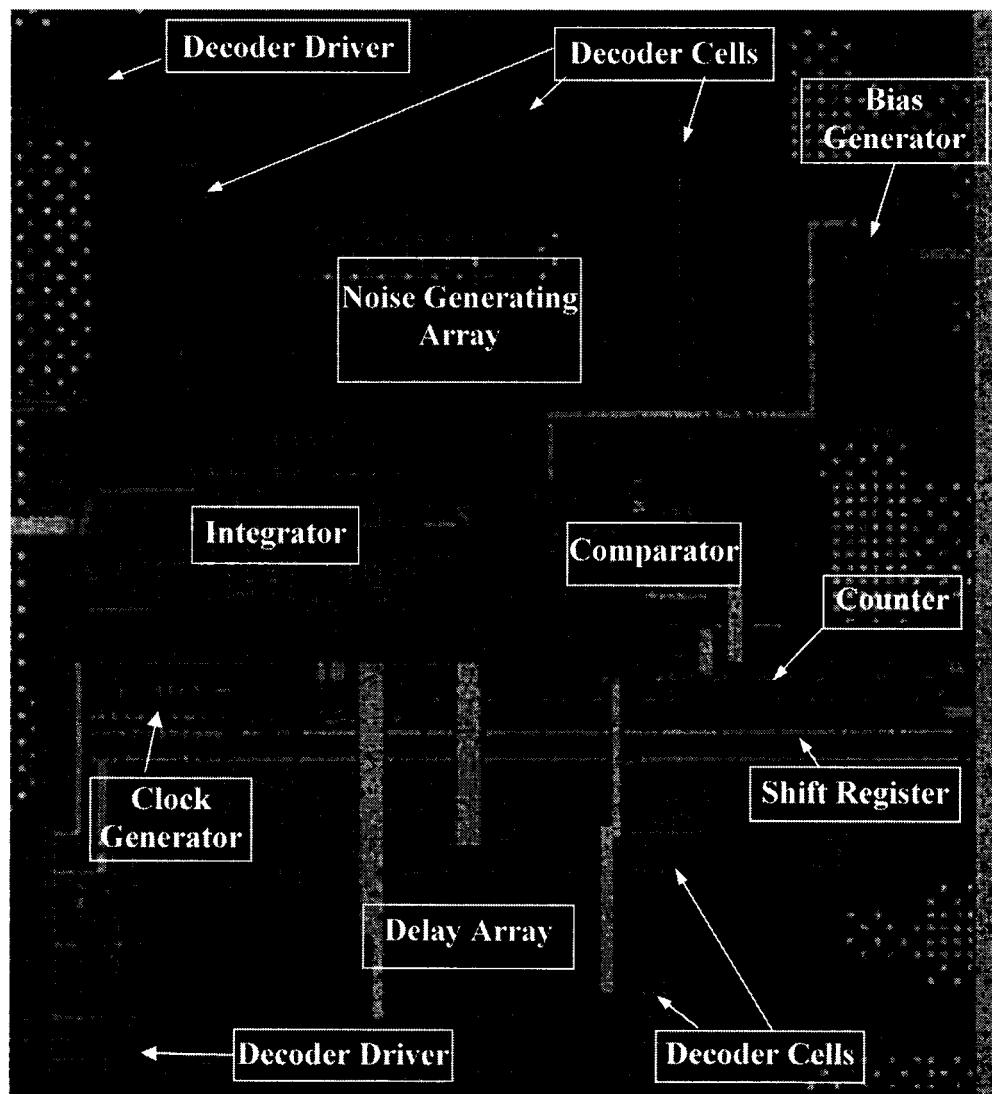

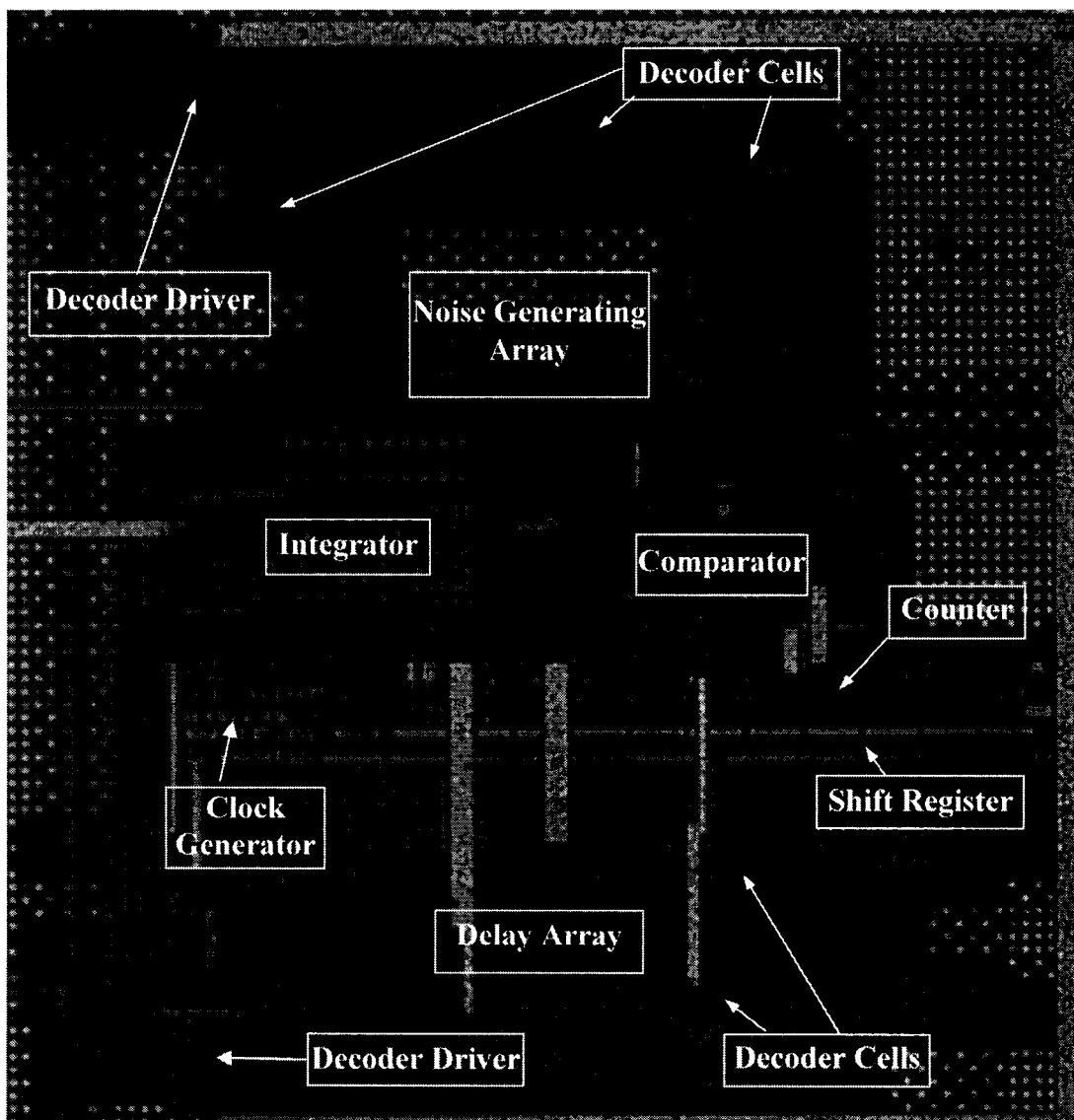

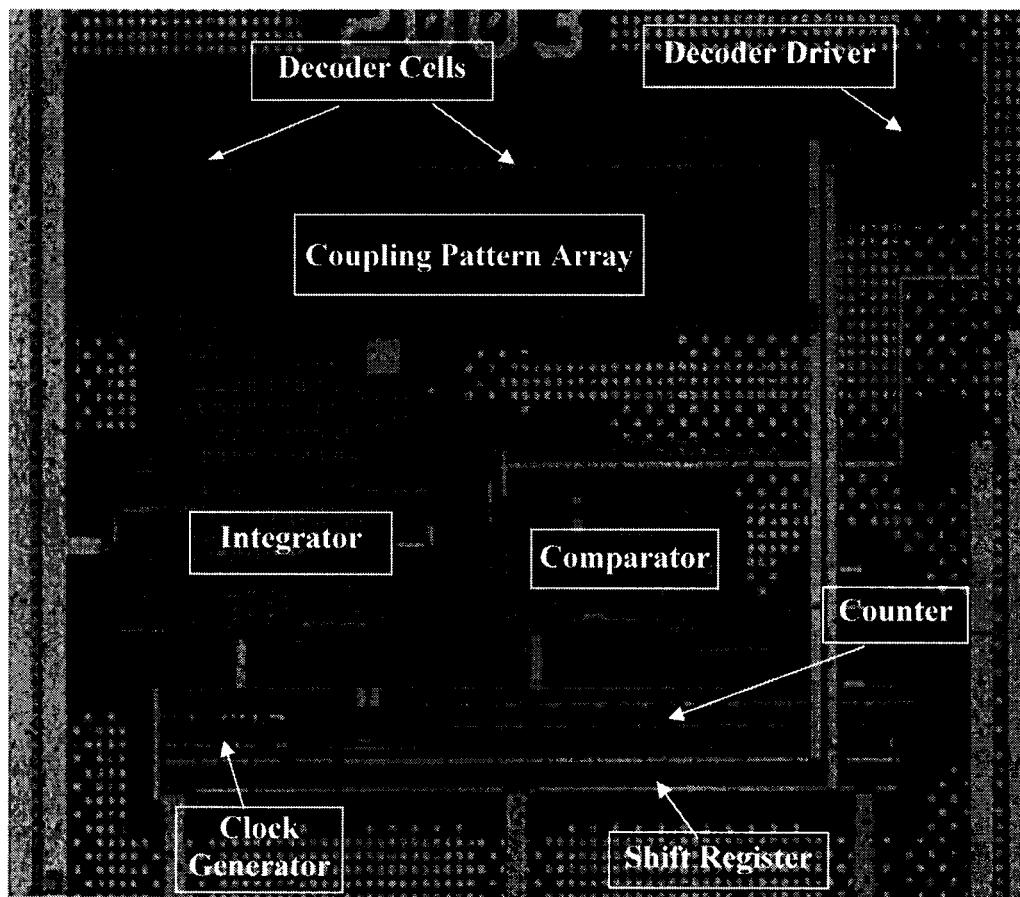

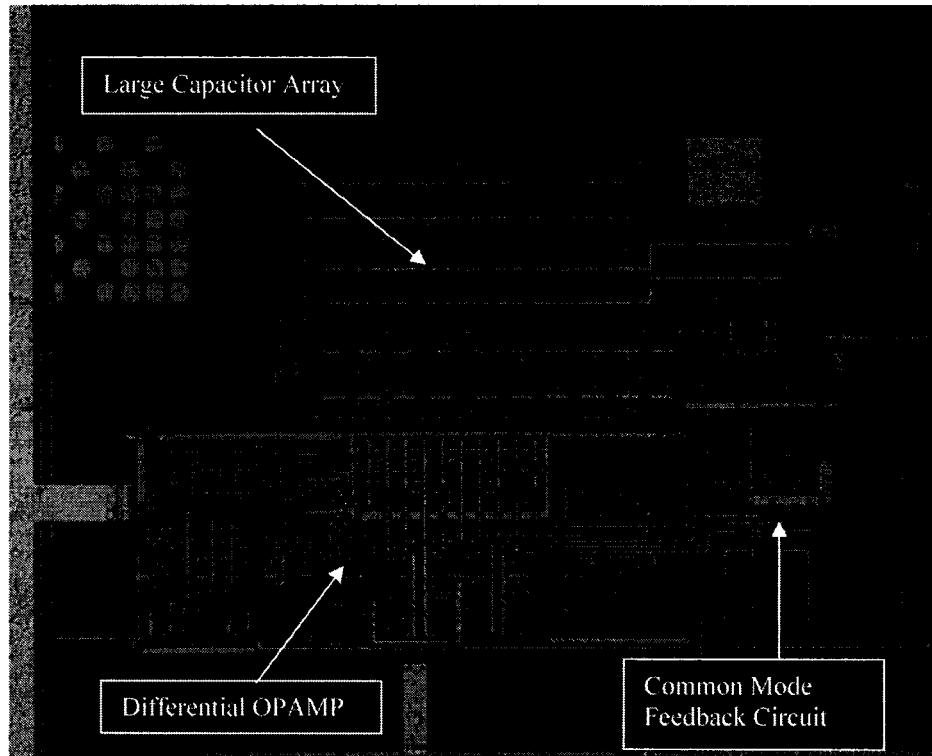

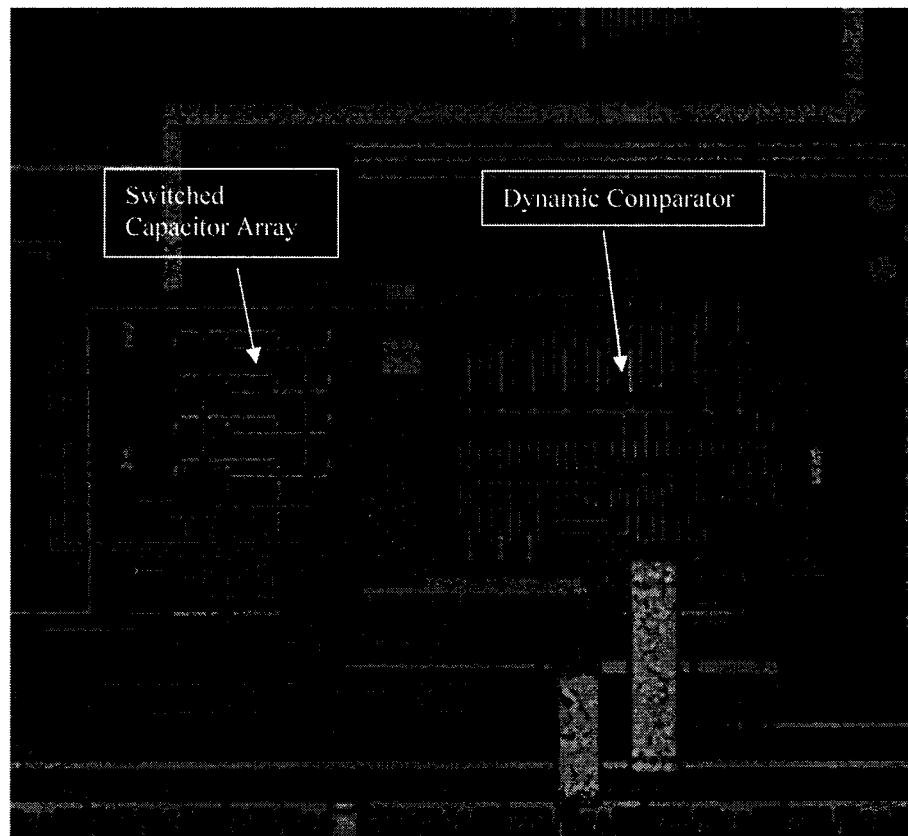

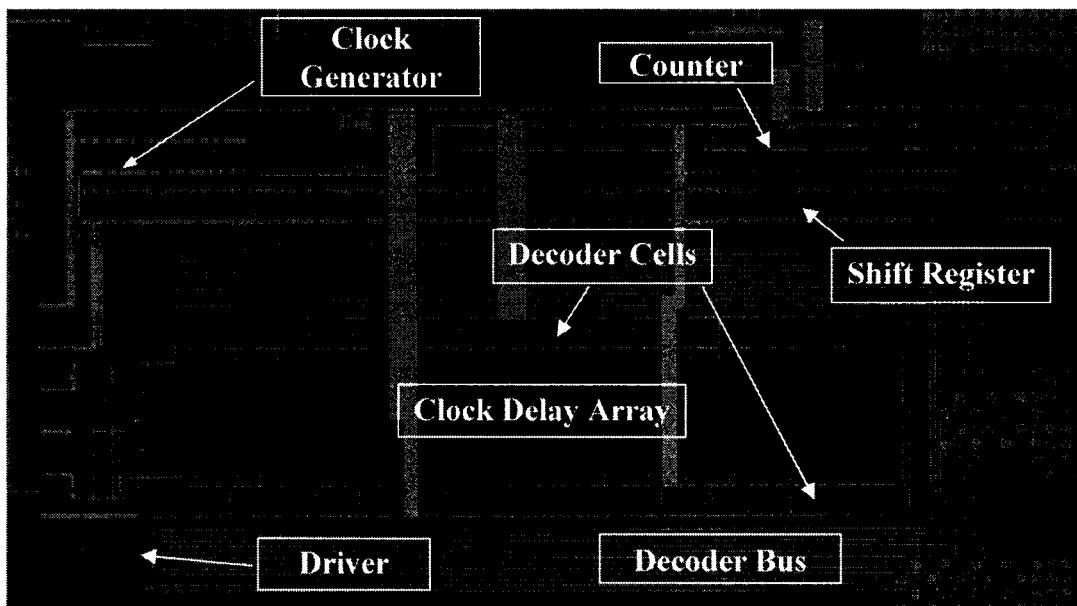

| Figure 10-1: Microphotograph of the substrate and capacitive coupling test circuits .....                                                                                                                       | 163 |

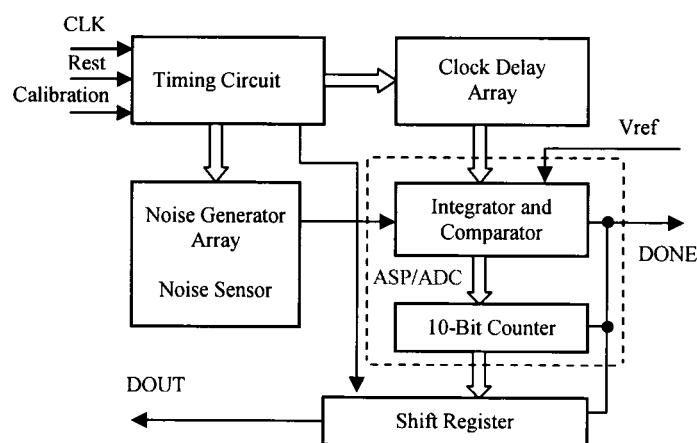

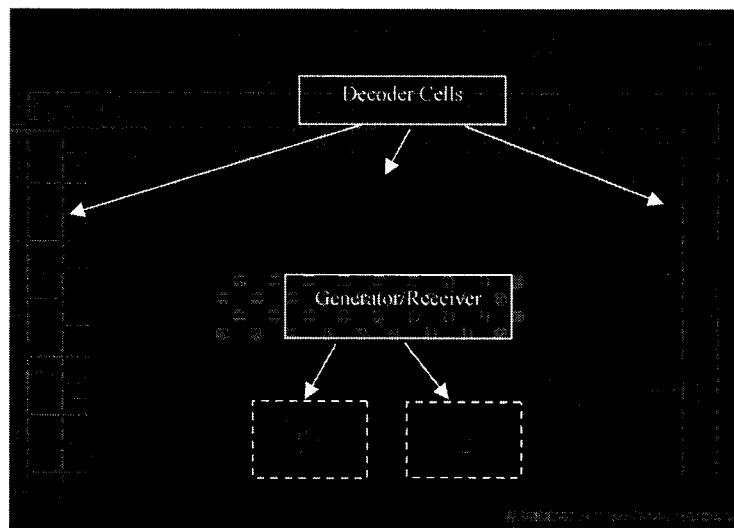

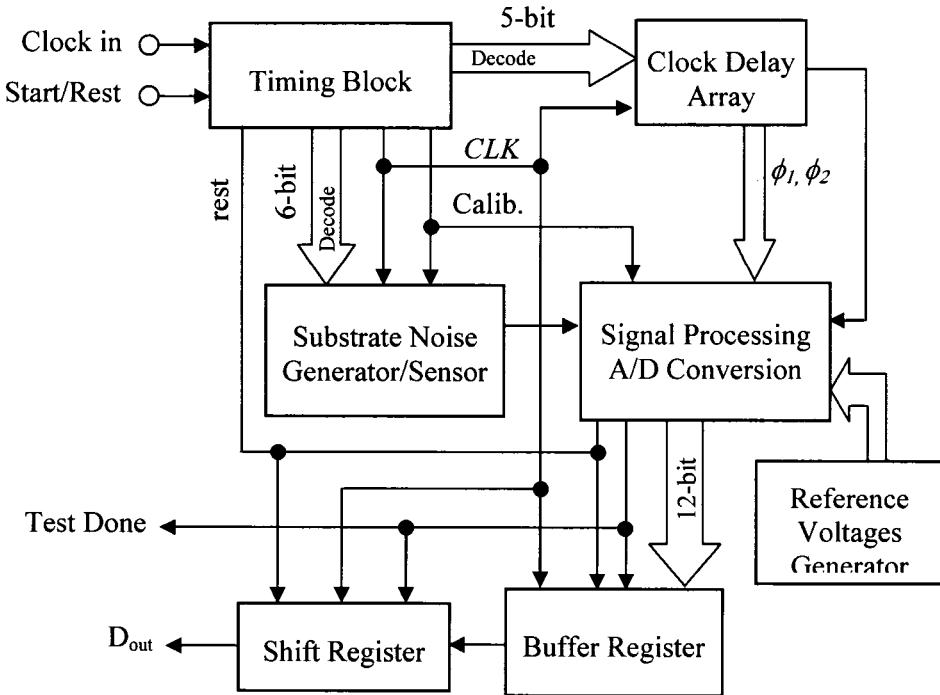

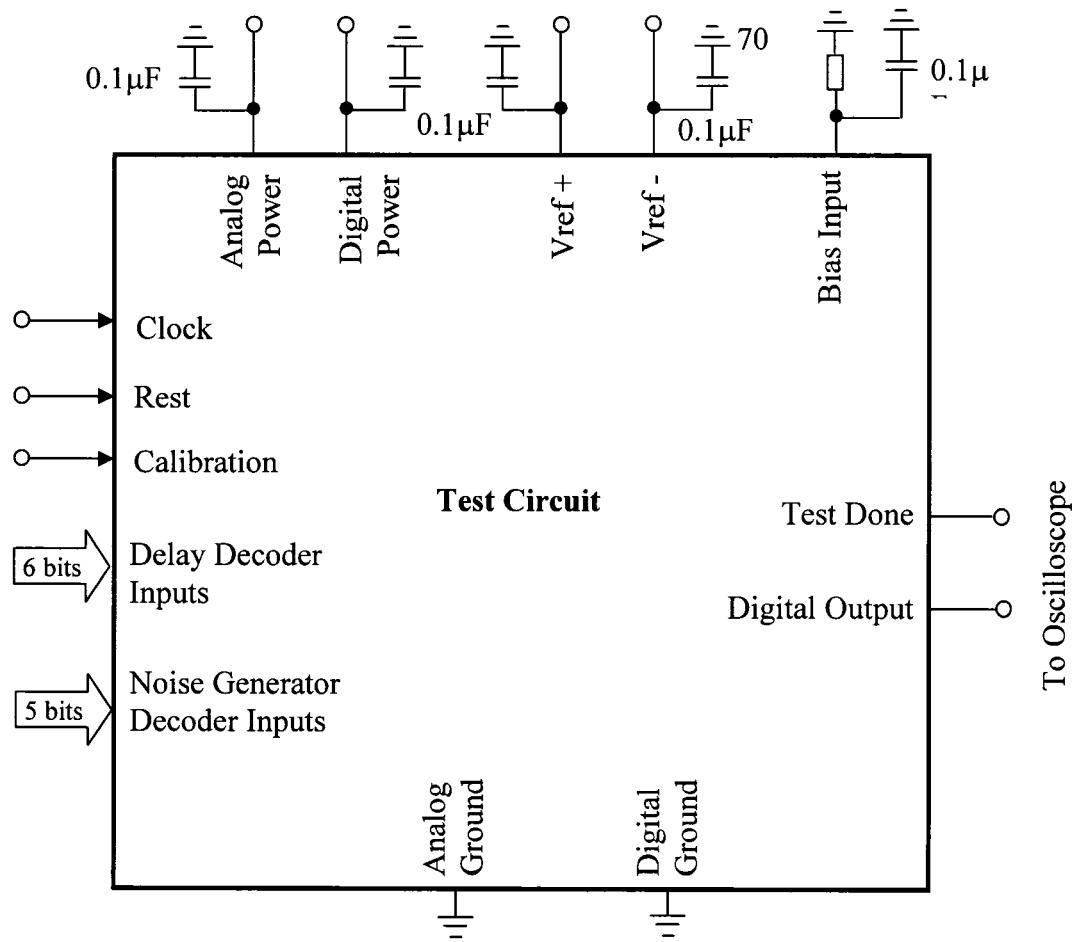

| Figure 10-2: Block diagram of the noise coupling test circuit.....                                                                                                                                              | 164 |

| Figure 10-3: On-chip noise generator/receiver and analog-to-digital converter ...                                                                                                                               | 165 |

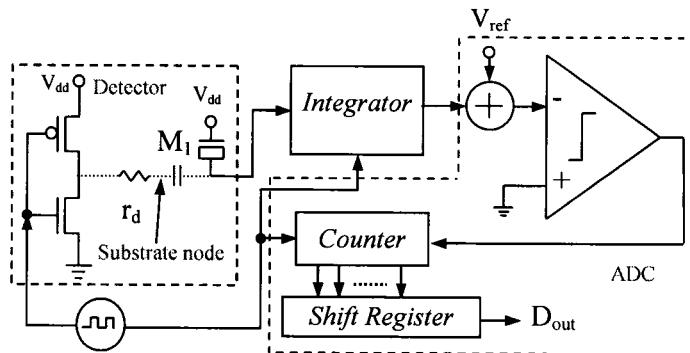

| Figure 10-4: Measured output waveforms of the substrate coupling noise test circuit .....                                                                                                                       | 166 |

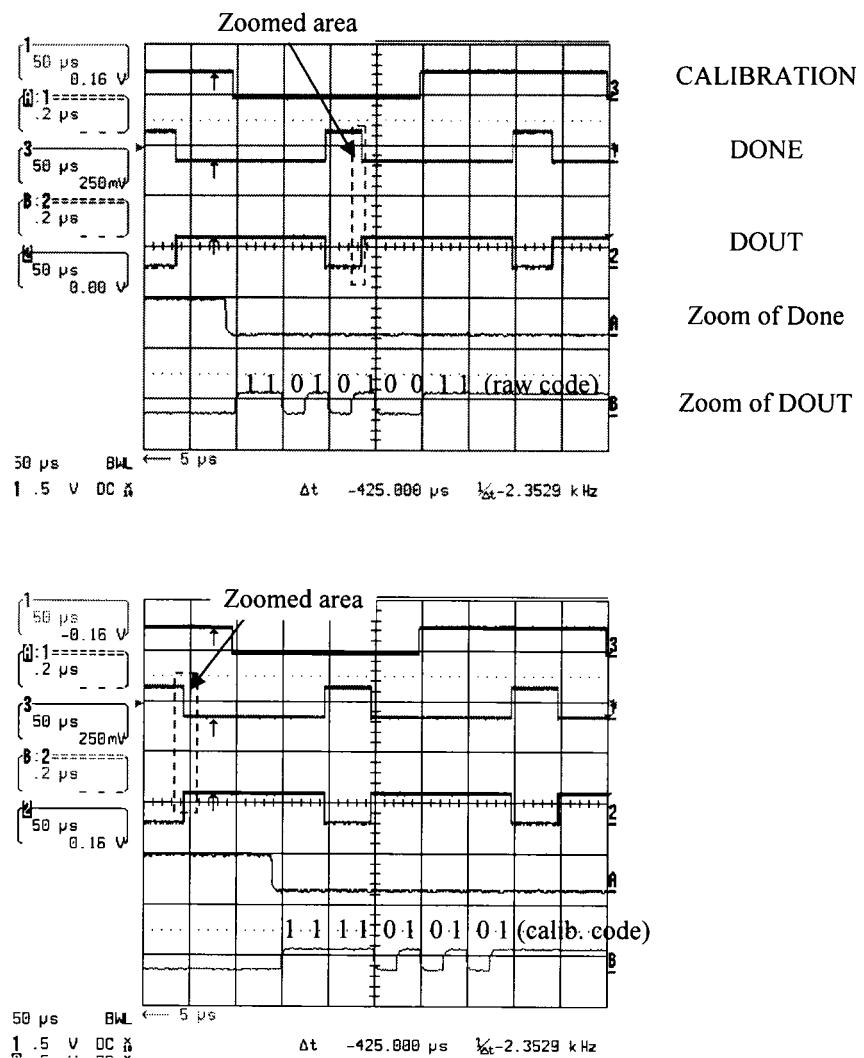

| Figure 10-5: Microphotograph of the substrate coupling noise test circuit I.....                                                                                                                                | 168 |

| Figure 10-6: Operation of the substrate coupling noise generator/receiver pair ...                                                                                                                              | 169 |

| Figure 10-7: Microphotograph of the substrate coupling noise generator array ...                                                                                                                                | 169 |

| Figure 10-8: A closer look at the noise generator array.....                                                                                                                                                    | 170 |

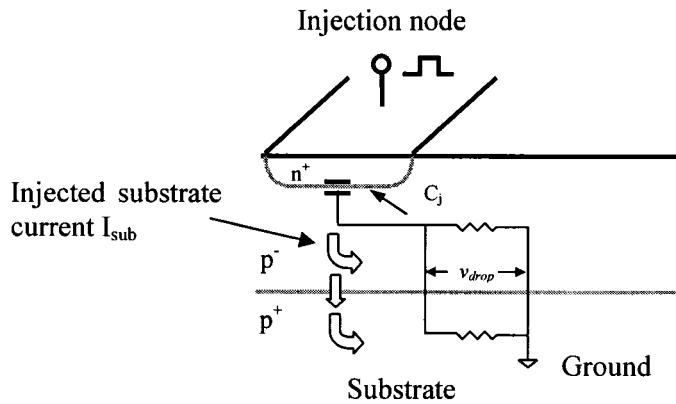

| Figure 10-9: The effect of feedback on the PN junction capacitance due to the voltage drop caused by the substrate resistance .....                                                                             | 171 |

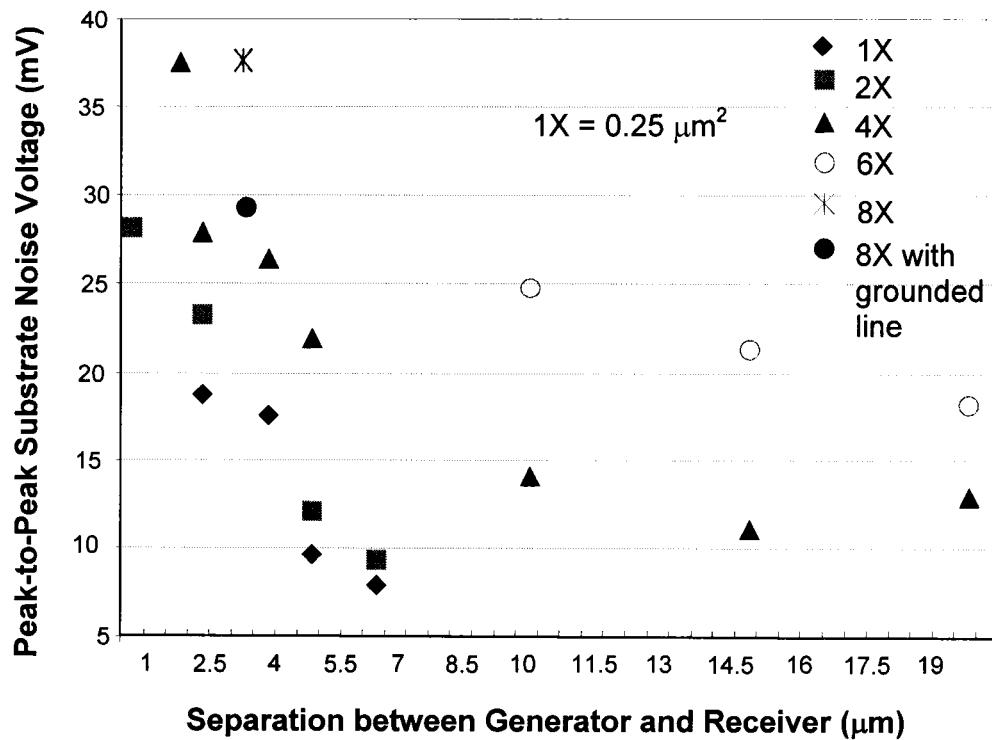

| Figure 10-10: Measured substrate coupling noise voltage as a function of the noise generator size and distance from the noise receiver.....                                                                     | 172 |

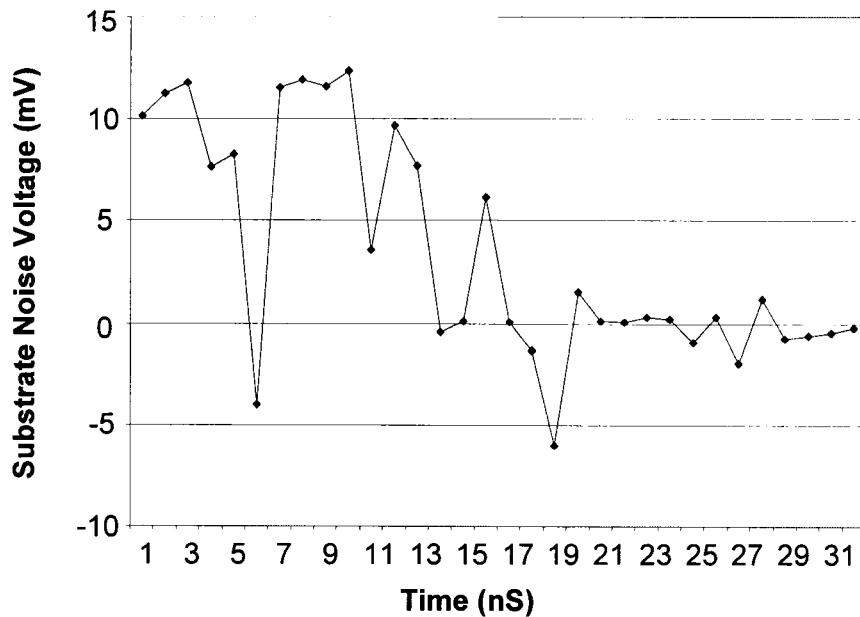

| Figure 10-11: Reconstructed substrate noise waveform determined from 32 test points .....                                                                                                                       | 173 |

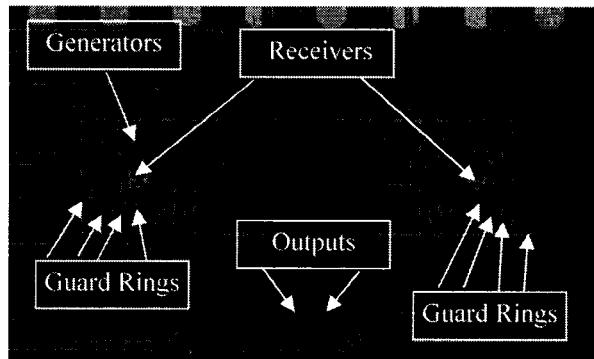

| Figure 10-12: Microphotograph of the structures for evaluating the reduction in noise caused by guard rings .....                                                                                               | 174 |

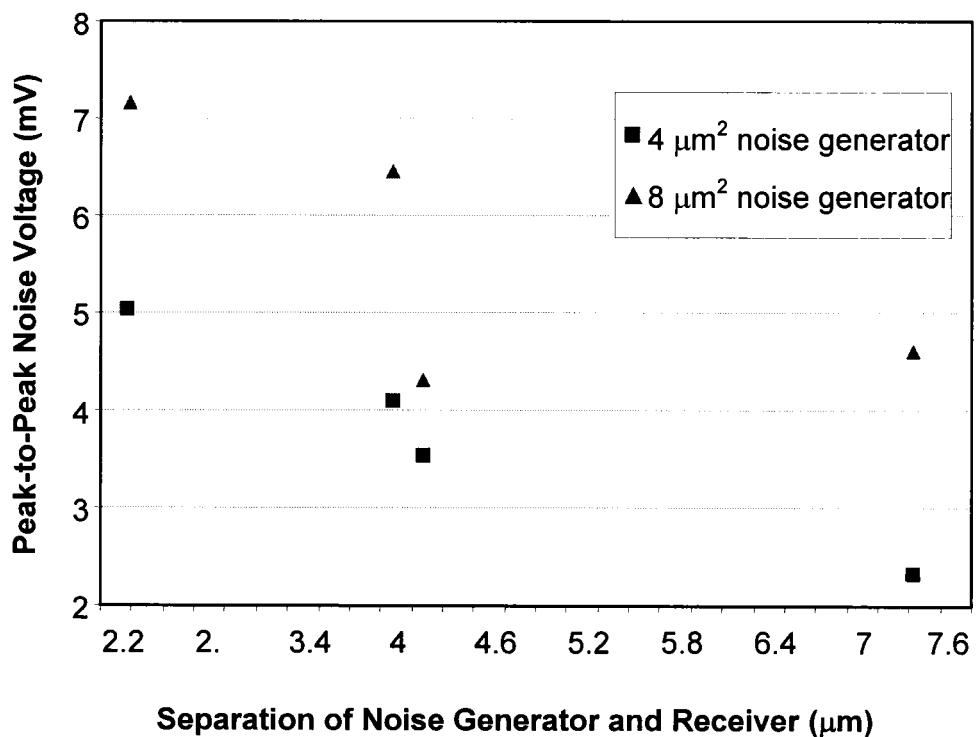

| Figure 10-13: Measured reduction in substrate noise with guard rings.....                                                                                                                                       | 175 |

|                                                                                                                                                            |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 10-14: Test structure for sensing line-to-line capacitive coupling noise voltage.....                                                               | 176 |

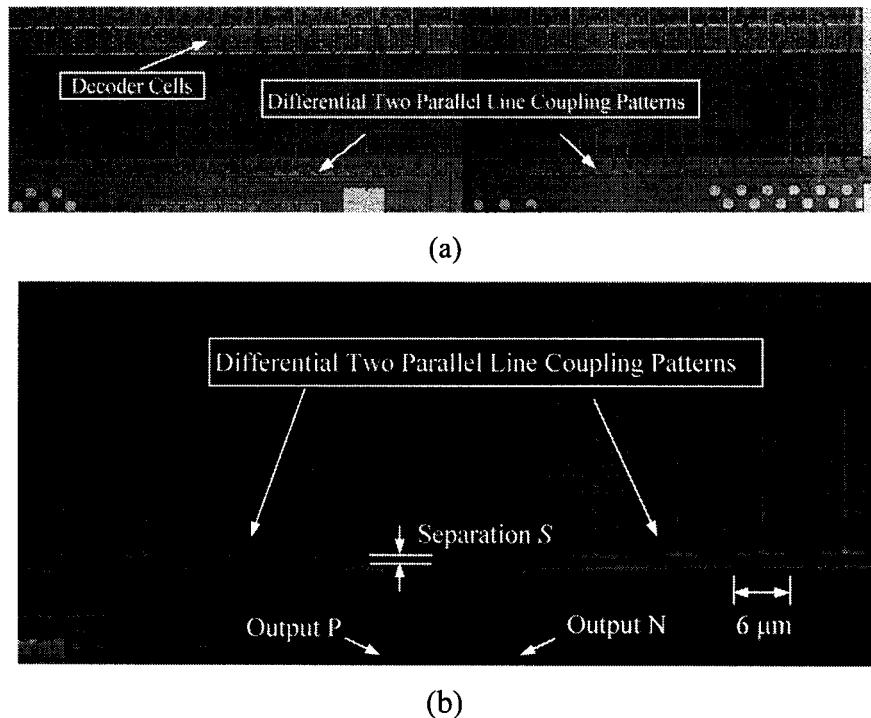

| Figure 10-15: Microphotographs of (a) capacitive coupling circuit structures (b) detailed view of differential two-parallel-line coupling structures ..... | 177 |

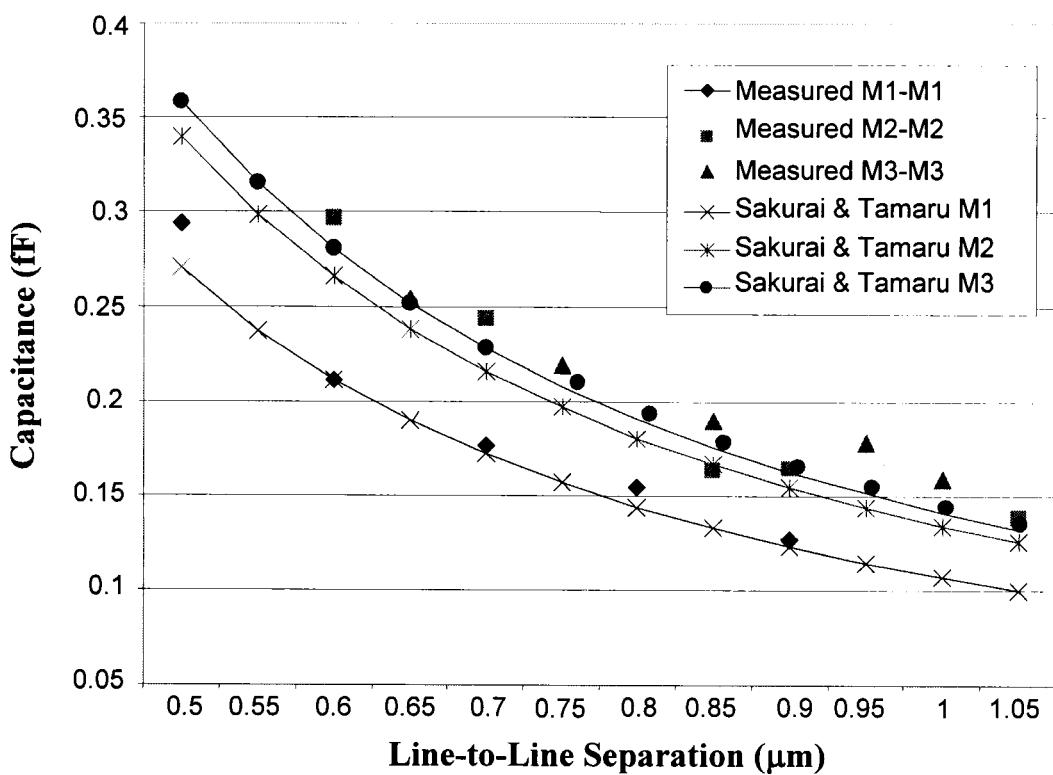

| Figure 10-16: Comparison of measured and analytic line-to-line coupling capacitance .....                                                                  | 178 |

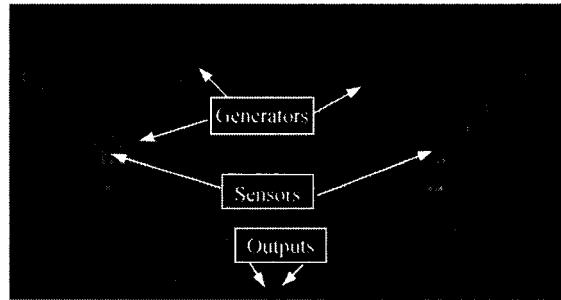

| Figure 12-1: Block diagram of the proposed substrate noise waveform measuring circuit.....                                                                 | 189 |

| Figure 12-2: Proposed floorplan of a substrate coupling noise generator/receiver circuit.....                                                              | 190 |

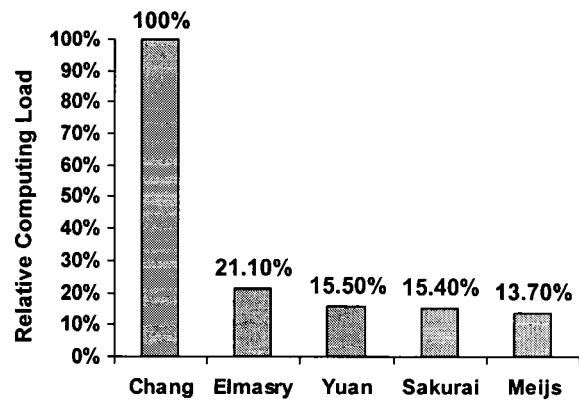

| Figure B-1: Comparison of different capacitive coupling models.....                                                                                        | 220 |

| Figure C.1: Physical layout of the noise generators in substrate coupling noise test circuit II.....                                                       | 222 |

| Figure C.2: The two-parallel-line capacitive coupling test structure.....                                                                                  | 224 |

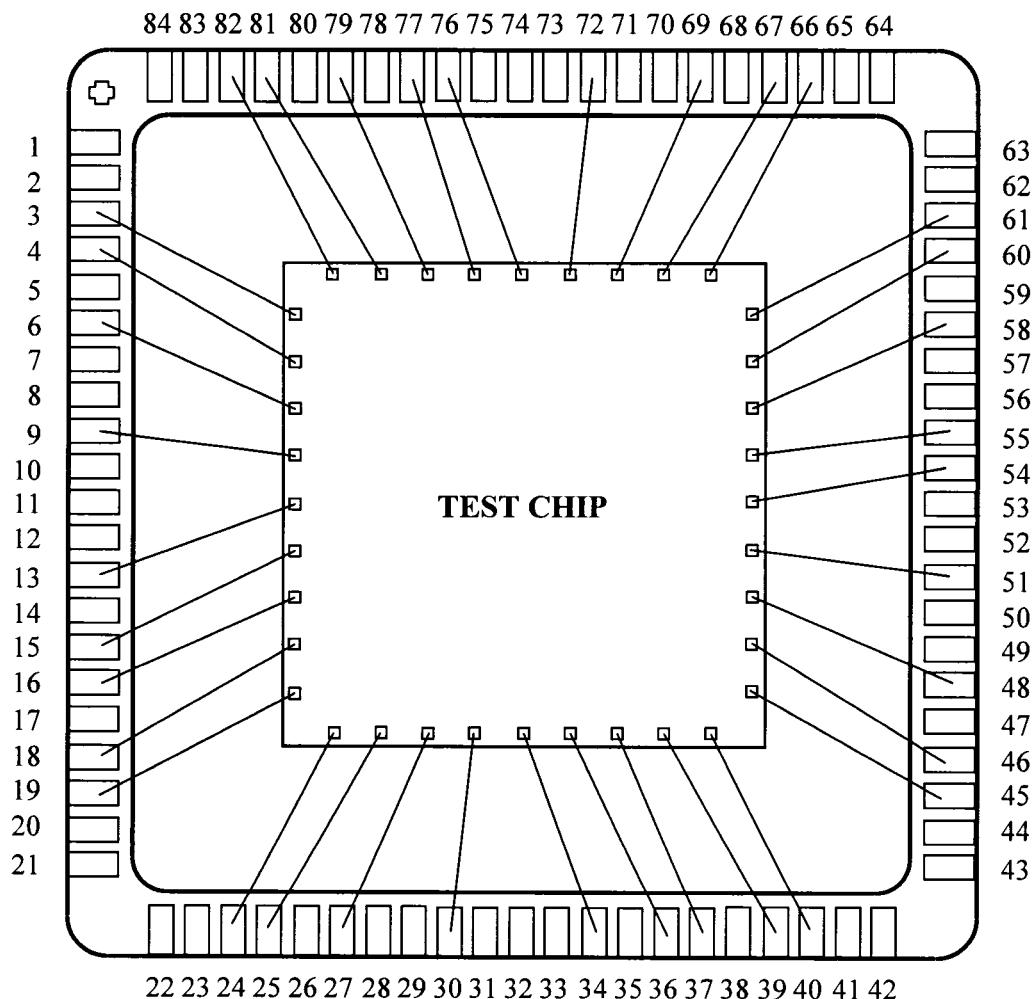

| Figure D.1: Diagram of the 84-pin CPGA IC package.....                                                                                                     | 225 |

| Figure D.2: I/O pin connections for circuit test setup.....                                                                                                | 227 |

| Figure D.3: Photograph of the packaged test circuit.....                                                                                                   | 228 |

| Figure D.4: Microphotograph of the substrate coupling noise test circuit I .....                                                                           | 229 |

| Figure D.5: Microphotograph of noise generating circuit within the substrate coupling noise test circuit I .....                                           | 230 |

| Figure D.6: Microphotograph of the substrate coupling noise test circuit II used to evaluate the reduction in noise caused by the guard rings .....        | 231 |

| Figure D.7: Microphotograph of the noise generating circuit of the substrate coupling noise test circuit II .....                                          | 232 |

| Figure D.8: Microphotograph of the capacitive coupling noise test circuit I .....                                                                          | 233 |

| Figure D.9: Microphotograph of the integrator used in the substrate coupling noise test circuits .....                                                     | 234 |

|                                                                                                                                                                                                                                                                                                                                 |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure D.10: Microphotograph of the integrator used in the capacitive coupling noise test circuit I (due to the larger coupling noise voltage, the voltage gain of the integrator used in the capacitive coupling noise test circuit I is set smaller, see the larger capacitance array on the top of the microphotograph)..... | 235 |

| Figure D.11: Microphotograph of the comparator circuit used to compare the integrated coupling noise voltage and the reference voltages.....                                                                                                                                                                                    | 236 |

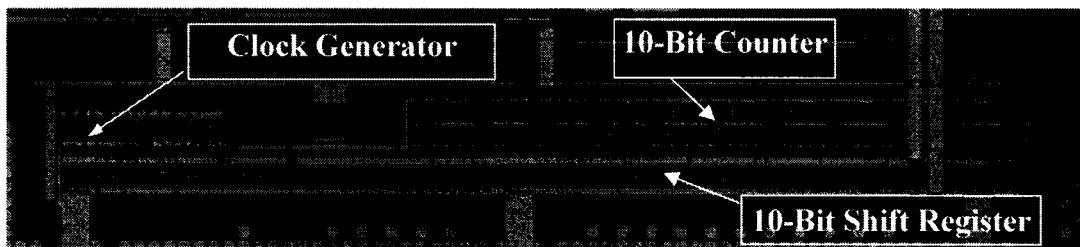

| Figure D.12: Microphotograph of the digital section of the substrate coupling noise test circuits .....                                                                                                                                                                                                                         | 237 |

| Figure D.13: Microphotograph of the digital section of the line-to-line capacitive coupling noise test circuit I .....                                                                                                                                                                                                          | 238 |

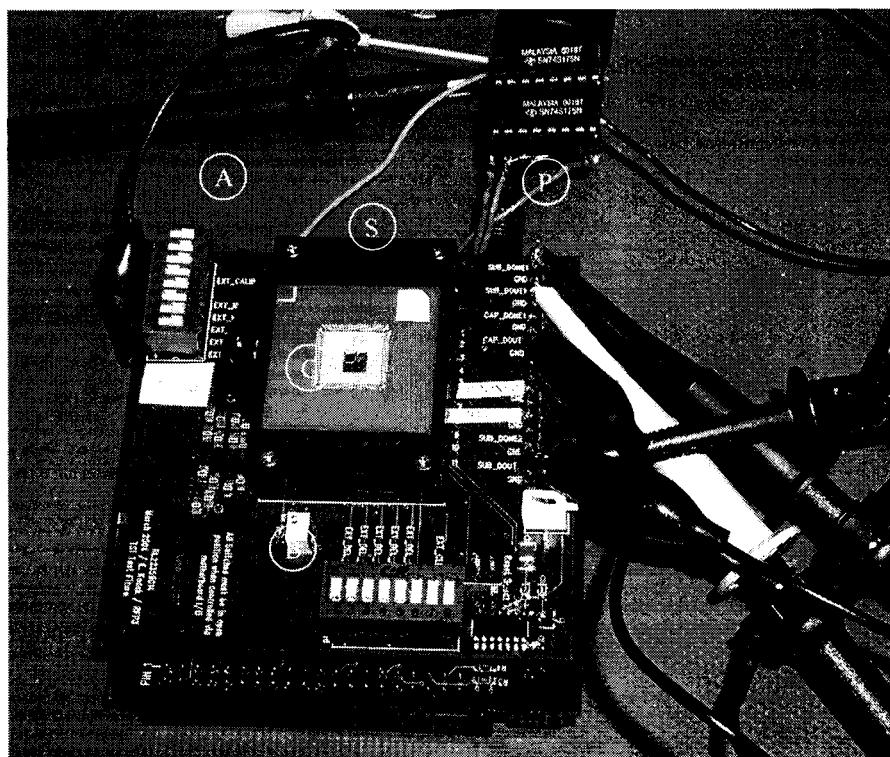

| Figure E.1: Photograph of the test board and test setup .....                                                                                                                                                                                                                                                                   | 241 |

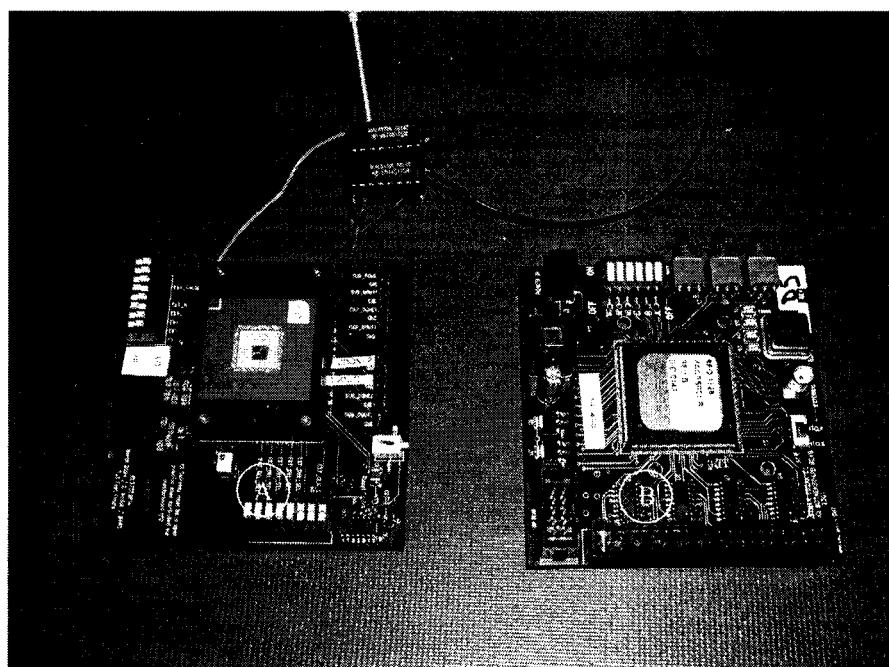

| Figure E.2: Photograph of the test board (A) and “daughter” board (B) which acts as the interface board between the test board (A) and the Kodak automatic data acquisition system (not shown).....                                                                                                                             | 242 |

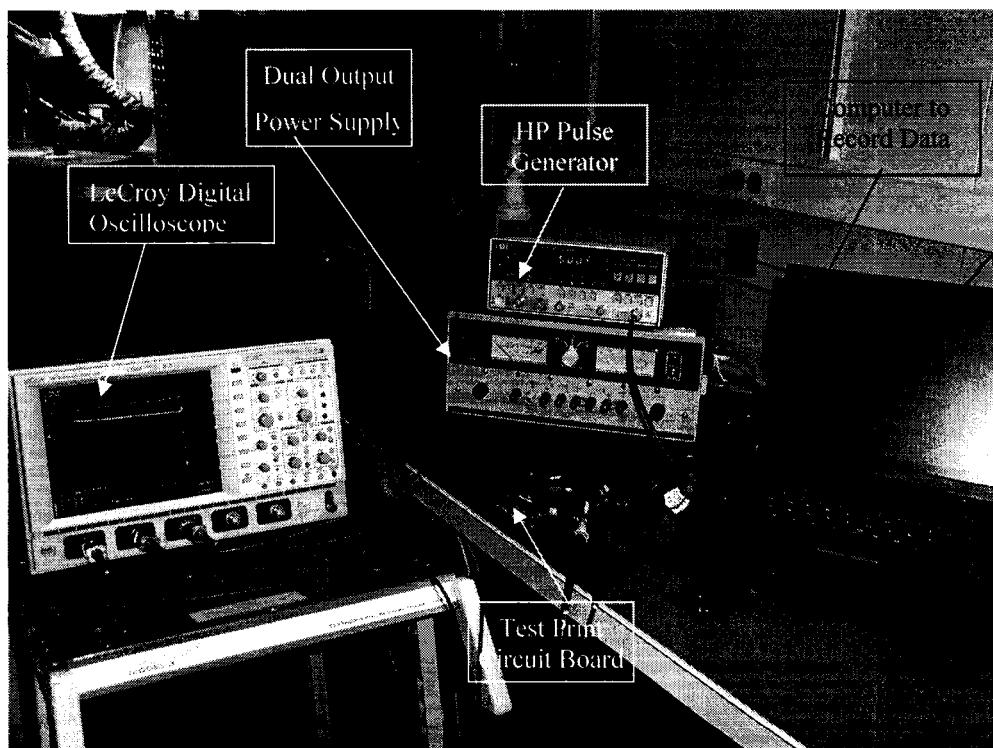

| Figure E.3: Photograph of the test setup .....                                                                                                                                                                                                                                                                                  | 243 |

## List of Tables

|                                                                                     |     |

|-------------------------------------------------------------------------------------|-----|

| Table 1-1: Summary of 2000/2001 SIA Roadmap .....                                   | 4   |

| Table 9-1: Matching Parameters of a 2.5 $\mu$ m and a 0.6 $\mu$ m CMOS Process..... | 149 |

| Table 12-1: Matrix of substrate coupling noise generators .....                     | 191 |

| Table C-1: Noise generators of the substrate coupling noise test circuit I. ....    | 221 |

| Table C-2: Noise generators within the substrate coupling noise test circuit II ... | 222 |

| Table C-3: List of the two-parallel-line capacitive coupling structures .....       | 223 |

| Table D-1: Descriptions of the 36 pin names of the test circuit .....               | 226 |

| Table E-1: Equipment use during the IC test process.....                            | 242 |

## **Chapter One: Introduction**

From Bell Labs inventing the transistor in 1947 to today's deep submicrometer CMOS processes and systems-on-a-chip integration, the semiconductor industry has experienced a rapid pace of improvement during the past four decades. Texas Instrument built the first integrated circuit in 1961, Gordon Moore in 1965 predicted exponential growth (biannual doubling) known as "Moore's Law," and Intel in 1971 invented the SRAM and EPROM and introduced the microprocessor 4004. With reduced feature sizes and power supply voltages, and higher levels of integration, characterizing noise in integrated circuits has become increasingly difficult and important. In this chapter, the development of microelectronics is briefly reviewed in sections 1.1 and 1.2. Difficulties in modeling and testing analog ICs (integrated circuits) are also discussed in section 1.3. The cause for the emergence of mixed-signal ICs is reviewed and noise measurement in mixed-signal ICs is discussed in sections 1.4 and 1.5, respectively. Each chapter in this research proposal is introduced at the end of this chapter.

### **1.1. Development of the Integrated Circuit**

The first transistor, the point-contact transistor, was invented by Bardeen and Brattain of Bell Telephone Laboratories in 1947 [1]. The first field-effect transistor (FET) was reported by Shockley in 1952 [2]. Metal Oxide Silicon (MOS) devices began taking a major role after the invention of the planar silicon process around 1960. Although the first MOS calculator was introduced in 1965, the commercial use of a MOS device was only limited to a few applications until 1967 due to silicon material and quality control problems. Even then, single-polarity p-type transistors were favored until the emergence of MOS silicon-gate transistor technology about 1971. The use of both polarity devices on the same substrate was invented by at least two people in the early 1960s. P. K. Weimer of RCA filed a patent on May 31<sup>st</sup>, 1962 [3]. Frank Wanlass of Fairchild Semiconductor Research and Development filed a patent on June 18<sup>th</sup>, 1963 that covered the CMOS concept [4]. The first microprocessor was developed in 1974. Since then, the performance, density, die size, and speed of ICs have experienced a dramatic growth due to rapid technological advances. During the past two decades, processor clock frequencies have been increasing at an average rate of about 1.25X per year. Transistor counts have been increasing at a steady rate of about 1.4X per year, while die size has been increasing at about 1.15X per year [5].

## 1.2. IC Generations and Scaling of Semiconductor Processing Technologies

These trends were clearly defined by Gordon Moore in 1960s and captured as Moore's Law. The current version of Moore's law is that succeeding generations will support a four times increase in circuit complexity, and new generations will emerge on an approximately two or three year interval. The associated observations are that the linear dimensions of device features change by a factor of 0.7 and the economically viable die size grows by a factor of 1.6 [6]. The minimum feature size stated in micrometers is the unit that is most frequently used to label a technology generation (or technology node). An individual device generation has been observed to have a reasonably well-defined life cycle that covers about 17 years. Usually, the first three to five years are university research, the second three to five years are industrial research, the third period of about four years is industrial development, and the last four to five years are the volume manufacturing phase. The first year of volume manufacture is the reference point for a generation.

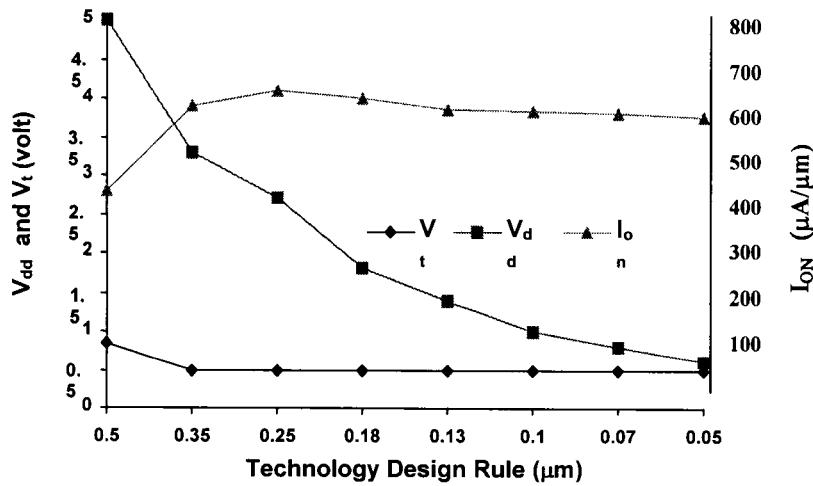

Figure 1-1: Scaling of conventional CMOS ICs

Scaling of CMOS technologies has defied all predictions of technology limitations, and continues beyond the deep submicrometer minimum feature size. The scaling of conventional MOSFETs, however, is facing several problems arising from reduced power supply voltages and a rapidly decreasing gate oxide thickness.

Table 1-1: Summary of 2000/2001 SIA Roadmap <sup>a</sup>

| Year                              | Unit                            | 1993  | 1995  | 1999  | 2001  | 2003 | 2005 | 2008 | 2011 | 2014 | 2016 |

|-----------------------------------|---------------------------------|-------|-------|-------|-------|------|------|------|------|------|------|

| Feature Size                      | <i>Nanometers</i>               | 500   | 350   | 180   | 130   | 100  | 80   | 70   | 50   | 34   | 22   |

| Internal Clock (high performance) | <i>GHz</i>                      | 0.2   | 0.3   | 0.75  | 1.68  | 2.31 | 5.17 | 6.74 | 11.5 | 19.3 | 28.7 |

| Logic transistors                 | <i>Million/cm<sup>2</sup></i>   | 2     | 4     | 6.6   | 13    | 24   | 44   | 109  | 269  | 664  |      |

| Microprocessor                    | <i>Million transistors/chip</i> | 5.2   | 12    | 23.8  | 47.6  | 95.2 | 190  | 539  | 1523 | 4308 |      |

| DRAM size                         | <i>Gbit</i>                     | 0.016 | 0.064 | 0.256 | 0.512 | 1    | 2    | 6    | 16   | 48   |      |

| SRAM size                         | <i>Mbit</i>                     | 1     | 4     | 16    | 64    | 256  |      |      |      |      |      |

| Voltage                           | <i>V<sub>dd</sub></i>           | 5     | 3.3   | 2.5   | 1.2   | 1.0  | 0.9  | 0.7  | 0.6  | 0.5  | 0.4  |

### 1.3. Difficulties in Characterizing Analog Circuit Technologies

Different from digital ICs, the design of analog integrated circuits is tightly dependent upon the manufacture process parameters. The accuracy of modeling these process related parameters directly affects the performance and yield of analog ICs. In the following subsections, difficulties in device characterization for analog circuits are discussed.

---

<sup>a</sup> <http://public.itrs.net/Files/2001ITRS/ORTCTables.pdf>

### 1.3.1. Subthreshold characteristics of MOSFET's are difficult to model

In sampled data circuits, subthreshold conduction of switches in the off state, particularly at high temperatures, may lead to significant leakage, thereby corrupting the stored information. This effect also becomes important in determining the lower bound on the speed of dynamic latches in mixed-signal and digital circuits. A difficulty in subthreshold modeling is DC and AC slope discontinuity in the vicinity of strong inversion as  $V_{GS}$  increases. Substantial dynamic errors are exhibited in the time-domain simulation of circuits in which MOSFETs operate between the linear and saturation regions. This issue remains unresolved in most mainstream device models.

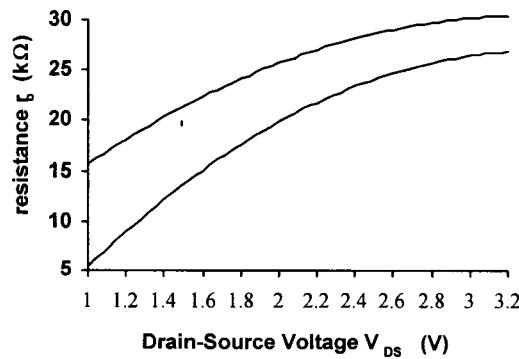

### 1.3.2. Modeling of output resistance of short-channel MOS transistors

Another troublesome effect is the output resistance of short-channel MOS transistors and, in particular, the variation of the output resistance with the drain-to-source voltage in the saturation region. This effect causes the intrinsic gain  $gm_{ro}$  to behavior nonlinearly, thereby creating nonlinearity in the amplifiers.

Figure 1-2: Transistor output impedance

### 1.3.3. Modeling of the capacitance of the well-to-substrate

A rarely available process parameter is the capacitance of the well-to-substrate. If the source and n-well of a PMOS (or p-well of a NMOS) device are connected to avoid the body effect, the n-well capacitance must be considered. The capacitance of the resistor made from the well may also be important.

### 1.3.4. Linearity of Passive Devices

Linearity of both passive and active devices plays a critical role in many analog circuits. Nonlinear terms appear in the device values as  $x \approx x_0 \cdot (1 + \alpha_1 V + \alpha_2 V^2)$ .  $x_0$  is the ideal device value, and  $\alpha_1$  and  $\alpha_2$  are coefficients of the nonlinear terms. The coefficients  $\alpha_1$  and  $\alpha_2$  are measured for different types of resistors and capacitors available in a process. The linearity of polysilicon resistors, however, typically improves with the length [8].

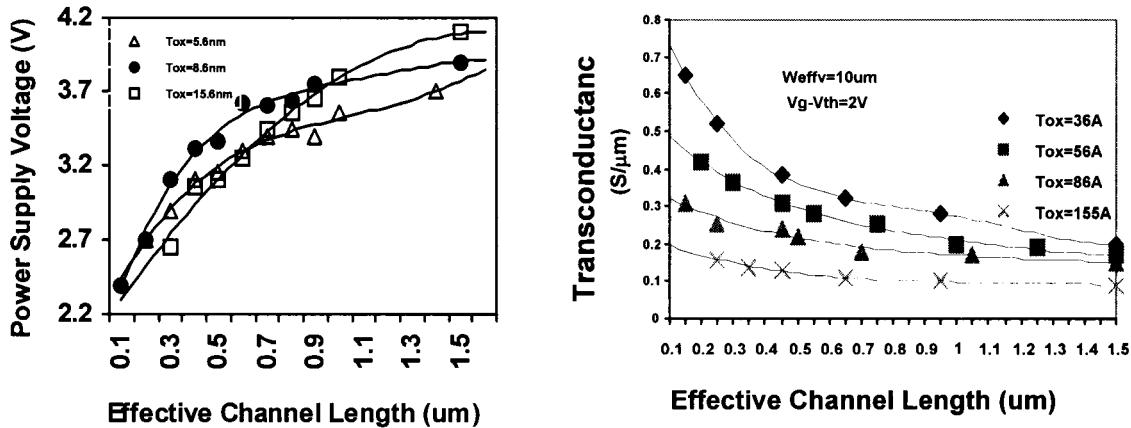

### 1.3.5. Modeling of MOSFET Transconductance

MOS transistors are voltage controlled current devices. The transconductance is an important parameter of a MOSFET. With the scaling of process feature sizes, the effective transconductance of a MOSFET is strongly affected. Modeling of the MOSFET effective transconductance has become significantly more difficult. Experimentally derived MOSFET current versus the effective channel length and gate oxide thickness is shown in Fig. 1.3. The data are in good agreement with the theoretical model [9].

Figure 1-3: MOSFET Transconductance vs effective channel length

#### 1.4. Fabricating Analog and Digital circuits on the Same Substrate: Mixed-Signal ICs

The evolution of scaled digital processes has shifted the boundary between the digital and analog parts of a system [10]. Although large electronic systems can be constructed almost entirely with digital techniques, many systems still require analog parts. Storage media, transmission media, and physical sensors are fundamentally analog in nature. The analog circuits will remain irreplaceable components of a System-On-a-Chip (SOC). In addition to analog-to-digital (A/D) and digital-to-analog (D/A) conversion circuits, analog circuits are required to perform a variety of critical tasks to interface digital circuits with the external world, such as amplification, prefiltering, demodulation, signal conditioning for

line transmission, storage, display, generation of absolute values (voltages, currents, frequencies), and to implement compatible on-chip sensors.

As CMOS technology continues to benefit from both scaling and the enormous momentum of the digital market, mixed-signal integrated circuits emerged around the early 1980's. With an increase in circuit size, the basic environment for a system-on-a-chip has become available. Many systems are integrated on a single IC in different areas, like medical audiometric system [11], telecommunication systems [12] [13], and imaging system [14] [15]. Analog-to-digital and digital-to-analog converters are commonly required in mixed-signal SOCs.

### **1.5. Analog and Mixed-Signal Circuit Noise Testing**

A typical strategy for testing a mixed-signal IC involves, when possible, first individually testing the digital and analog components (these are test cells built on the same substrate). This effort is followed by certain system tests to evaluate the at-speed interaction among components. In this case, the digital parts are tested with standard methods, aided by software for automation test pattern generation, scan chains, and built-in self-test (BIST), which has become a mature and cost effective technology. Testing the analog parts and the combined system is less well understood [16]. Unlike digital signals, analog signals require significantly greater precision in the signal magnitude. Noise added at the input of an analog circuit is seen at the circuit output. Noise directly affects the performance and accuracy of

the test results of an analog circuit. Measuring noise in an analog circuit is important for improving circuit performance and reducing failure in mixed-signal ICs. Due to the generation mechanisms in ICs, these noise voltages are usually weak, making noise testing quite difficult.

### **1.6. Topics Presented in This Research Proposal**

In this research proposal, some noise analysis and techniques for testing noise signals in mixed-signal ICs are presented. The research presented in this proposal focuses on the development of accurate noise signal measurement techniques for different types of noise sources in mixed-signal CMOS ICs. Basic noise sources and non-ideal factors in mixed-signal ICs are reviewed in Chapters 2 and 3, respectively.

In Chapter 4, a technique to accurately measure substrate coupling noise is proposed. On chip A/D conversion is used to minimize the signal contamination due to the parasitic impedances along an IC test path. An on chip circuit calibration is also used to further extend the accuracy.

A circuit used to test capacitive coupling noise between conductive lines is presented in Chapter 5. Capacitive coupling between different conductive layers can be accurately measured without the signal contamination from bonding wire to package fame and external test circuit.

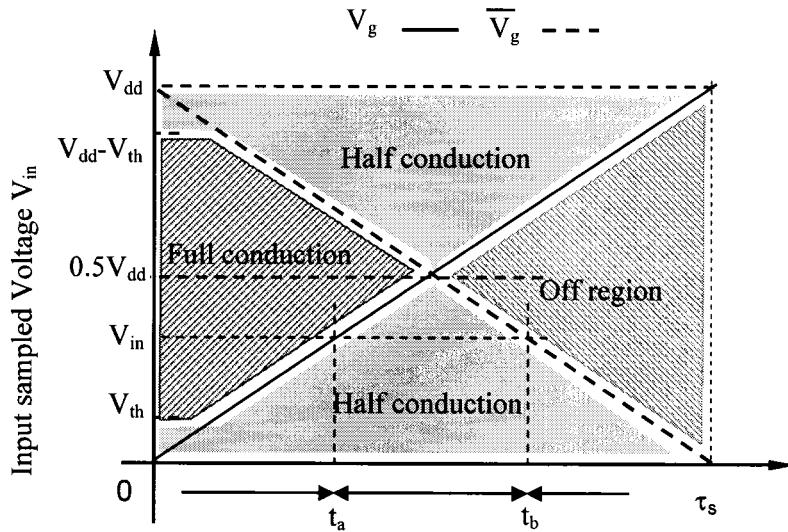

In Chapter 6, an analysis of clock feedthrough in CMOS analog transmission gate (TG) switches is presented in this chapter in details. A model of clock feedthrough in analog transmission gate switches is established in the voltage/current domain. In this analysis, a region map is developed for the TG switch during the period when both devices are turned off. In the first region, full conduction (or strong inversion), both the PMOS and NMOS transistors operate in the linear region. The second region is a half conduction region where one MOSFET is in the linear region and the other transistor is either in the subthreshold region and/or the off state. In the third region, both of the MOSFETs are in the subthreshold/cutoff. The region map is further divided into zones. From these region and zone maps, the sign and relative magnitude of clock feedthrough noise can be efficiently estimated for different signal levels.

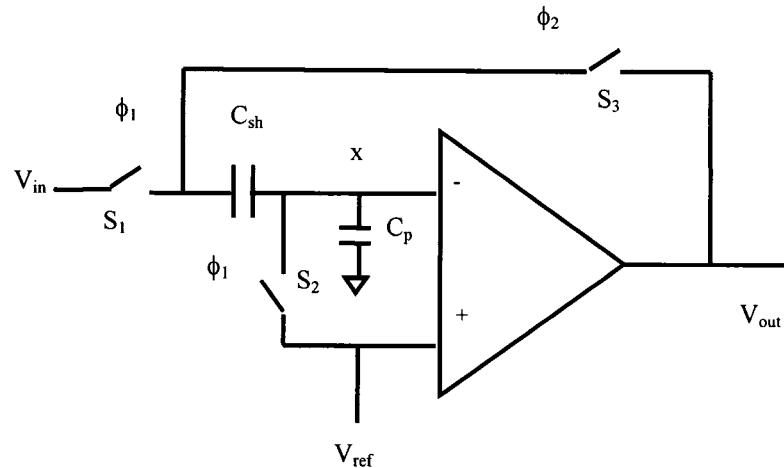

The parasitic capacitance affects the performance of the analog circuits, particularly switched-capacitor circuits. The charge sharing effect in CMOS switched-capacitor sample-and-hold (S/H) circuit is used as an example noise problem in Chapter 7.

A circuit technique based on the Miller effect to reduce the charge sharing effect noise and clock feedthrough noise in S/H circuit is proposed in Chapter 8. A compact cascode amplifier is used in the Miller feedback circuit. A ten times reduction in CSE and clock feedthrough is achieved. The S/H capacitor is split into two, Csh1 and Csh2, in the circuit. One of these S/H capacitors effectively reduces

the CSE while the other capacitor reduces clock feedthrough. Transistor mismatch affecting CMOS operational amplifiers is presented in Chapter 9.

The experimental data obtained from the test chip is presented and discussed in Chapter 10. A summary of this research is offered in Chapter 11. Future research in modeling substrate coupling and line-to-line capacitive coupling in mixed-signal ICs is described and suggested in Chapter 12.

## **Chapter Two: Noise Sources in Mixed-Signal CMOS ICs**

Noise in various forms exists in all kinds of electronic systems such as integrated circuits. The noise can be random or fixed pattern, signal related or signal independent, and semiconductor process dependent or independent. In this chapter, common noise sources in mixed-signal CMOS ICs are reviewed. Noise in integrated circuits and electronic devices is briefly described in section 2.1. Random noise and some related characteristics are reviewed in section 2.2. Major types of random noise sources in CMOS ICs are described in section 2.3. Substrate noise, capacitive coupling, clock feedthrough, charge sharing effect, and power/ground noise are each reviewed in section 2.4.

### **2.1. Noise in Integrated Circuits and Electronic Devices**

Noise can be described as any signal appearing at the output of an IC that is not predicted by a DC and AC input error analysis [17]. Noise can be random or repetitive, internal or external, current or voltage, narrow band or wide band, and high frequency or low frequency.

With the development in IC process technologies, many new challenges in analog and mixed-signal circuits have emerged due to the demands of modern electronic systems. With the extension of CMOS process technologies into the

UDSM (ultra-deep submicrometer) regime and the increasing popularity of battery-powered mobile electronic systems, the demand for low-voltage mixed-signal IC circuits has greatly increased. In addition, the drive to reduce system costs is forcing the integration of analog and digital circuitry onto a single die. Both of these changes have a significant impact on mixed-signal circuit performance. With the scaling of the power supply voltage, both the SNR (signal-to-noise ratio) and the dynamic range of an analog circuit have decreased. Integrating sensitive analog circuitry and noisy digital circuitry onto the same substrate further degrades the performance of the analog circuit due to noise injection through the substrate, the power supply, and/or the power distribution network, as well as capacitive coupling between conducting wires. In low voltage CMOS analog and mixed-signal integrated circuits, many noise mechanisms generate low frequency noise such as 1/f noise, wideband white noise such as shot noise, and thermal noise. These types of noise, as described in [18], together with other types of noise that are commonly found in mixed-signal CMOS ICs are reviewed in the following sections.

## 2.2. Random Noise

Electronic devices and circuits exhibit random fluctuations in the voltage (or current) at the terminals. Since the terminals exhibit unpredictable instantaneous values, these fluctuations are known as stochastic processes and are characterized in terms of the average or statistical properties. These fluctuations are usually

referred to as random noise [18]. The noise is inherent in the devices or circuits and can not be eliminated. The mean value and power spectral density are principal statistical quantities to characterize the random noise. The most important noise sources (thermal noise, shot noise, and 1/f noise) in electronic devices and circuits exhibit normal or Gaussian distributions [18] in the frequency domain as shown in (2-1).

$$F(x) = \frac{1}{\sqrt{2\pi\sigma^2}} \exp\left\{-\frac{(x - \bar{x})^2}{2\sigma^2}\right\} \quad , \quad (2.1)$$

where  $\bar{x}$  is the mean and  $\sigma^2 \equiv x^2(t) - \bar{x}^2$  is the variance of the process  $x(t)$ .

The mean value at  $t = t_1$  is

$$\bar{x}(t_1) = \lim_{N \rightarrow \infty} \frac{1}{N} \sum_{i=1}^N x^{(i)}(t_1) = \int_{-\infty}^{\infty} x_1 p_1(x_1, t_1) dx_1 \quad , \quad (2.2)$$

where  $p_1(x_1, t_1)$  is the possibility density function.

The mean-square value at  $t = t_1$  is

$$\bar{x^2}(t_1) = \lim_{N \rightarrow \infty} \frac{1}{N} \sum_{i=1}^N [x^{(i)}(t_1)]^2 = \int_{-\infty}^{\infty} x_1^2 p_1(x_1, t_1) dx_1 \quad . \quad (2.3)$$

The overbar in these or the following expressions denotes an ensemble average, the symbol  $E\{\cdot\}$  is the expected value, and  $N$  is the number of functions in the process ensemble.

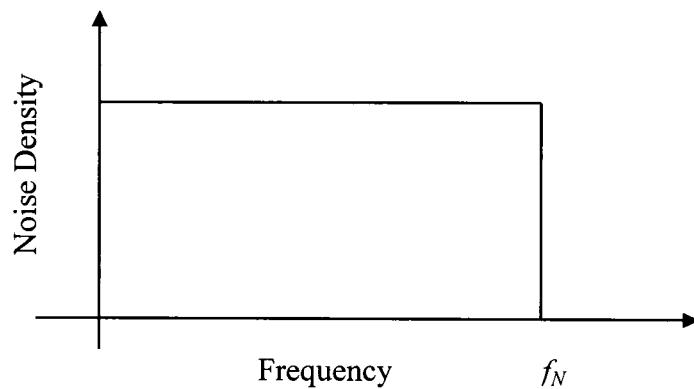

### 2.2.1. Noise Bandwidth

The evaluation of the noise response of a circuit is often difficult except in the case of a simple transfer function. If the frequency response curve is transformed to a normalized transfer function with a step response function (see Fig. 2-1), the analysis becomes much simpler. The normalized frequency  $f_N$  of a circuit can be expressed as

$$f_N = \frac{1}{A_{v0}^2} \int_0^{\infty} |A_v(jf)|^2 df \quad , \quad (2.4)$$

where  $A_{v0}$  is the DC gain of the circuit,  $A_v(f)$  is the gain as a function of frequency, and  $f_N$  is the normalized noise bandwidth of a circuit.

Figure 2-1: Bandwidth of an abrupt response function

### 2.2.2. Noise Factor and Noise Figure

The noise factor (F) and noise figure (NF) are commonly used figures of merit for specifying the noise performance of a circuit. The noise factor is the ratio of the total output noise power to the noise power attributable to the source resistance.

$$F = \frac{(S/N)_{IN}}{(S/N)_{OUT}} \quad , \quad (2.5)$$

and

$$NF = 10 \log(F) = 10 \log \left( \frac{(S/N)_{IN}}{(S/N)_{OUT}} \right) \quad , \quad (2.6)$$

where S is the signal and N is the noise in units of power or voltage square.

### 2.3. Major Types of Random Noise in CMOS ICs

Many random noise sources exist in CMOS ICs. These noise sources have different characteristics and affect circuits differently. In the following subsections, the major types of random noise in CMOS ICs are reviewed.

#### 2.3.1. Shot (Schottky) Noise

Random generation and the flow of mobile charge carriers in a material produce a current. This current is identified with “shot noise.” Shot noise is a white noise that exhibits a uniform spectral density over all frequencies. In semiconductors,

shot noise is related to charge crossing a potential barrier. It is the dominant noise mechanism in transistors and operational amplifiers at medium and high frequencies [19]. Assume electrons flow from A to B in a material with a permittivity of  $\epsilon$ . The current pulse due to a single electron as observed from an external circuit is

$$i_e(t) = \frac{qv(t)}{d} \quad , \quad (2.7)$$

where  $v(t)$  is the instantaneous velocity and  $d$  is the separation between A and B. The Fourier transform of a single current pulse is [18]

$$F(\omega) = \frac{q}{2\pi d} \int_0^{t_a} v(t) e^{-j\omega t} dt \quad , \quad (2.8)$$

where  $t_a$  is the arrival time of an electron emitted at  $t = 0$ . If the transit time of an electron is sufficiently small such that  $\omega t_a \ll 1$ ,

$$F(\omega) = \frac{q}{2\pi d} \int_0^{t_a} v(t) e^{-j\omega t} dt = \frac{q}{2\pi} \quad , \quad (2.9)$$

and the power density spectral is

$$S(\omega) = 4\pi \bar{N} |F(\omega)|^2 \quad , \quad (2.10a)$$

$$\bar{I} = q\bar{N} \quad . \quad (2.10b)$$

The associated current is

$$\overline{i_N^2(f)} = S(\omega)\Delta\omega = 2q\bar{I}\Delta f \quad , \quad (2.11)$$

where  $\bar{I}$  is the DC current, and  $\Delta f$  is the noise bandwidth.

The noise described by (2.7) - (2.11) is referred to as shot noise. Because the power density spectrum is constant, shot noise is characterized as a white noise.

### 2.3.2. Thermal (Johnson) Noise

Thermal noise (or Johnson noise or Nyquist noise) describes fluctuations in the voltage across a dissipative circuit element (such as a resistor or transistor). These fluctuations are most often caused by thermal motion of the charge carriers. The charge neutrality of an electrical resistance is satisfied when the entire volume is considered, but locally the random thermal motion of the carriers sets up fluctuating charge gradients or a fluctuating *ac* voltage. A resistor  $R$  can be modeled as an ideal resistor in series with a noise voltage source  $v_n$  [18],

$$v_n^2 = \frac{4hf \cdot R(f) \cdot \Delta f}{e^{\frac{\hbar\omega}{kT}} - 1} \approx 4kT \cdot R(f) \cdot \Delta f \quad , \quad (2.12)$$

or in parallel with a noise current generator of mean square value,

$$i_n^2 = \frac{4hf\Delta f}{R(f) \cdot (e^{\frac{\hbar\omega}{kT}} - 1)} \approx \frac{4kT\Delta f}{R(f)} \quad , \quad (2.13)$$

where  $k$  is the Boltzmann constant,  $T$  is the absolute temperature,  $R$  is the MOS transistor channel resistance, and  $\Delta f$  is the frequency range of interest (the MOS transistor cut-off frequency  $f_T$  or the amplifier bandwidth).

The power spectral density of the thermal noise of a MOS transistor channel resistance is

$$R(f) = \frac{md}{Ne^2 \tau_0 A} \quad , \quad (2.14)$$

$$S(f) = \frac{4NVe^2 \tau_0 kT}{md^2 (1 + \omega_0^2 \tau_0^2)} \approx \frac{4kT}{R(f)} \quad , \quad (2.15)$$

where  $A$  is the area of the channel cross-section of a MOS transistor,  $V$  is the volume of the channel, and  $\tau_0$  is the mean scattering time of the channel electrons.

Figure 2-2: Models of resistor thermal noise in the form of (a) a voltage source, (b) a current source

Thermal noise is also a white noise where the power is distributed uniformly over the entire frequency range. The thermal noise of a submicrometer MOS transistor does not satisfy the long-channel approximation  $\overline{i_n^2} = 4kT \cdot [2/(3g_m)]$  [20]. More accurate models of the channel noise are described in [21] and [22]. The thermal noise generated in the substrate or body also affects the MOSFET threshold voltage. Due to the distributed nature of the body resistance, this effect exists in differential circuits as well.

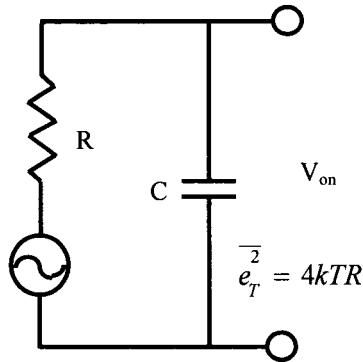

### 2.3.3. KTC Noise

KTC noise is called “KT over C noise”. It originates from the thermal noise. As shown by (2-12), the thermal noise of a resistor will become infinite when the resistance R becomes infinite. The thermal noise voltage, however, can not become infinite because there is always a capacitor shunting the resistor, thereby limiting the voltage [18]. In Fig. 2-3, the output noise voltage is determined by the bandwidth of the circuit. The high-frequency cut-off is determined by the RC time constant. The output noise voltage  $v_{no}$  is

$$v_{no}(f) = \frac{v_m}{\sqrt{1 + \omega^2 C^2 R^2}} \quad . \quad (2.16)$$

The power in the output noise signal is

$$P_{no} = \int_0^{\infty} v_{no}^2(f) df = \int_0^{\infty} \frac{4kTR\Delta f}{1 + \omega^2 C^2 R^2} = \frac{kT}{C} \quad . \quad (2.17)$$

Figure 2-3: Capacitive shunting of a noisy resistor

KTC noise is one of the dominant noise sources in switched capacitor circuits.

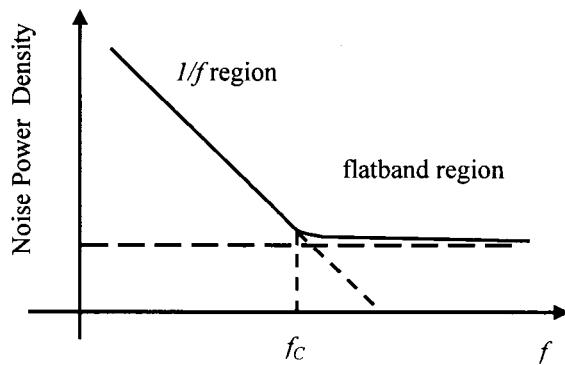

#### 2.3.4. *I/f* (Flicker) Noise

Flicker noise is associated with the combination-recombination of carriers in a transistor caused by contamination and defects in the silicon lattice structure. This noise type is also called 1/f noise because the noise amplitude increases as the frequency decreases.

$$\overline{v_n^2} = \frac{K_F}{C_{ox} \cdot f}. \quad (2.18)$$

To determine the noise, the technology constant KF is measured for both PMOS and NMOS devices. The dependence on f and Cox is of the form (Cox)<sup>a</sup>\*f<sup>b</sup> [19].